集成电路导线结构及其制造方法与流程

1.本发明涉及半导体的技术领域,特别涉及一种集成电路导线结构及其制造方法。

背景技术:

2.随着半导体技术的发展,对于集成电路的体积和面积要求越趋严格。其中,为了实现更高效的操作速度和达到更低的耗能,半导体结构的尺寸便成了关键所在。

3.然而,在形成半导体的导电结构常会有技术上的限制,例如光阻的高度过高容易倒塌,而难以形成特定尺寸或外型的导电结构。

4.因此,如何能克服技术上的难题,形成特定尺寸的导电结构,是目前业界亟欲投入研发资源解决的问题。

技术实现要素:

5.有鉴于此,本发明的一目的在于提出一种集成电路导线结构的制造方法,第一导电结构及第二导电结构可以共同形成高长径比的集成电路导线结构。

6.在本发明的一个或多个实施方式中,集成电路导线结构的制造方法包括提供基板及位于基板上的第一介电层;在第一介电层上形成第一蚀刻遮罩;通过第一蚀刻遮罩蚀刻第一介电层,以形成沟槽;在沟槽中形成第一导电结构,并在第一导电结构及第一介电层上形成导电层;在导电层上形成对准第一导电结构的第二蚀刻遮罩;以及通过第二蚀刻遮罩蚀刻导电层,以形成接触第一导电结构的第二导电结构。

7.在本发明的一些实施方式中,制造方法进一步包括:在基板与第一介电层之间形成第一蚀刻终止层。

8.在本发明的一些实施方式中,第一介电层包括第一介电子层及第二介电子层,第二介电子层位于第一介电子层上。

9.在本发明的一些实施方式中,制造方法进一步包括:在第一介电子层及第二介电子层之间形成第二蚀刻终止层。

10.在本发明的一些实施方式中,形成沟槽包括:在第二介电子层形成第二子沟槽;以及在第一介电子层形成第一子沟槽连通第二子沟槽以形成沟槽。

11.在本发明的一些实施方式中,第一子沟槽的宽度小于第二子沟槽的宽度。

12.在本发明的一些实施方式中,第一导电结构包括第一导电子结构及第二导电子结构,第二导电子结构位于第一导电子结构上,且第二导电子结构的宽度大于第一导电子结构的宽度。

13.本发明的另一目的在提供一种用于集成电路的导线结构。

14.在本发明的一些实施方式中,一种集成电路导线结构包括基板、第一介电层、第二介电层、第一导电结构及第二导电结构。第一介电层位于基板上。第一导电结构位于第一介电层内。第二介电层位于第一介电层上,第二导电结构位于第二介电层内。第一导电结构包括第一导电子结构及第二导电子结构,第二导电子结构位于第一导电子结构上,且第二导

电结构接触第一导电结构的第二导电子结构。

15.在本发明的一些实施方式中,第二导电子结构的宽度大于第一导电子结构的宽度。

16.在本发明的一些实施方式中,第一导电结构具有第一上底部及第一下底部,第一上底部的宽度大于第一下底部的宽度,且第二导电结构具有第二上底部及第二下底部,第二上底部的宽度小于第二下底部的宽度,第一上底部接触第二下底部

17.综上所述,本发明的集成电路导线结构及其制造方法,具有相连接的第一导电结构及第二导电结构,因此可以形成具有高长径比的集成电路导线结构。再者,本发明的第一集成电路导线结构具有上下接触的第一导电子结构及第二导电子结构,其中第二导电子结构的宽度大于第一导电子结构的宽度,可以改进现有半导体领域中的导线互连构造。

附图说明

18.为描述获得本发明上述或其它的优点和特征,将通过参考其具体实施方式对上述简要描述的原理进行更具体的阐释,而具体实施方式被展现在附图中。这些附图仅例示性地描述本发明,因此不被认为是对范围的限制。通过附图,本发明的原理会被清楚解释,且附加的特征和细节将被完整描述,其中:

19.图1为根据本发明一些实施方式的集成电路导线结构的制造方法流程图;以及

20.图2至图7可表示为图1中制造方法的各个步骤的示意性剖面图。

21.主要附图标记说明:

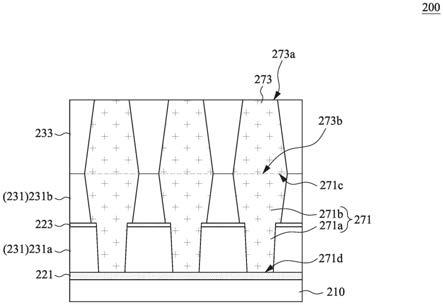

22.100-制造方法,110、120、130、140、150、160-步骤,200-集成电路导线结构,210-基板,221-第一蚀刻终止层,223-第二蚀刻终止层,231-第一介电层,231a-第一介电子层,231b-第二介电子层,232-沟槽,232a-第一子沟槽,232b-第二子沟槽,233-第二介电层,251-第一蚀刻遮罩,251a、253a-开口,253-第二蚀刻遮罩,271-第一导电结构,271a-第一导电子结构,271b-第二导电子结构,271c-第一上顶部,271d-第一下底部,272-导电层,273-第二导电结构,273a-第二上顶部,273b-第二下底部。

具体实施方式

23.本发明可以以许多不同的形式实施。代表性实施例在附图中示出,并且将在本文中详细描述。本发明包含原理的示例或说明,并且本发明的实施例将不受限于所示的实施例。

24.请参考图1。图1为根据本发明一些实施方式的集成电路导线结构的制造方法100的流程图。制造方法100始于步骤110,其中步骤110包括提供基板及位于基板上的第一介电层。接着制造方法100进行到步骤120,步骤120包括在第一介电层上形成第一蚀刻遮罩。接着制造方法100进行到步骤130,步骤130包括通过第一蚀刻遮罩蚀刻第一介电层,以形成沟槽。接着制造方法100进行到步骤140,步骤140包括在沟槽中形成第一导电结构,并在第一导电结构及第一介电层上形成导电层。接着制造方法100进行到步骤150,步骤150包括在导电层上形成对准第一导电结构的第二蚀刻遮罩。最后制造方法100进行到步骤160,步骤160包括通过第二蚀刻遮罩蚀刻导电层,以形成接触第一导电结构的第二导电结构。

25.图2至图7可表示为图1中制造方法100的各个步骤的示意性剖面图。请参考图2,图

2可用以表示步骤110及步骤120,其中第一介电层231位于基板210上。其中,基板210可以包含掺杂或未掺杂的半导体材料(诸如硅),或者绝缘体上半导体(soi)基板的有源层。基板210也可以包含其他半导体材料,诸如锗;化合物半导体,包括碳化硅、砷化镓、磷化镓、氮化镓、磷化铟、砷化铟及/或锑化铟;合金半导体,包括sige、gaasp、alinas、algaas、gainas、gainp及/或gainasp;或其组合。第一介电层231为层间介电质(interlayer dielectric;ild)可包括磷硅酸盐玻璃(psg)、硼硅酸盐玻璃(bsg)、硼掺杂的磷硅酸盐玻璃(bpsg)、氟掺杂的硅酸盐玻璃(fsg)或原硅酸四乙酯(teos)等。可以使用旋涂、可流动化学气相沉积(fcvd)、等离子体增强化学气相沉积(pecvd)、低压化学气相沉积(lpcvd)等形成第一介电层231,本发明不以此为限。

26.在本发明的一些实施方式中,制造方法100进一步包括在基板210与第一介电层231之间形成第一蚀刻终止层221,第一蚀刻终止层221可以由碳化硅、氮化硅、氧氮化硅、碳氮化硅等形成,并且可以使用合适的沉积工艺(诸如化学气相沉积(chemical vapor deposition,cvd)、物理气相沉积(physical vapor deposition,pvd)或其组合等)形成,本发明不以此为限。

27.在本发明的一些实施方式中,第一介电层231包括第一介电子层231a及第二介电子层231b,第二介电子层231b位于第一介电子层231a上。此外,制造方法100还可以包括在第一介电子层231a及第二介电子层231b之间形成第二蚀刻终止层223,其中第一蚀刻终止层221与第二蚀刻终止层223大致相同,在此不再重复赘述。此外,第一介电子层231a及第二介电子层231b可以是由相同的材料所制成,但也可以是由不同的材料所制成,本发明并不以此为限。

28.在步骤120中,第一蚀刻遮罩251形成在第一介电层231上。第一蚀刻遮罩251可以是图案化的硬遮罩或图案化的光阻,其中第一蚀刻遮罩251具有开口251a以至少部分露出第一介电层231。

29.请参考图3及图4,图3及图4可用以表示步骤130,其中通过第一蚀刻遮罩251(如图2)蚀刻第一介电层231,以形成沟槽232。开口251a(如图2)露出第一介电层231的部分会被移除,第一蚀刻遮罩251遮蔽第一介电层231的部分则会被保留。也即,第一蚀刻遮罩251可定义沟槽232的尺寸及形状。

30.在图3中,沟槽232的第二子沟槽232b形成在第二介电子层231b中。接着,在图4中,沟槽232的第一子沟槽232a形成在第一介电子层231a中,其中第一子沟槽232a连通第二子沟槽232b以共同形成沟槽232。除此之外,第一子沟槽232a的宽度小于第二子沟槽232b的宽度。此外,也可以是先形成第一子沟槽232a再形成第二子沟槽232b,本发明并不以此为限。

31.具体而言,可以通过第一蚀刻遮罩251以非等向性蚀刻在第二介电子层231b中形成第二子沟槽232b,并移除第一蚀刻遮罩251。接下来,使用诸如光微影和非等向性蚀刻等任何合适的方法在第一介电层231中形成第一子沟槽232a。其中,非等向性蚀刻可例如为干式蚀刻,可例如是等离子体蚀刻(plasma etch)或反应性离子蚀刻(reactive ion etch,rie),本发明并不以此为限。

32.请参考图5,图5可用以表示步骤140及步骤150。在步骤140中,第一导电结构271形成于沟槽232(如图4)中,并在第一导电结构271及第一介电层231上形成导电层272,其中第一导电结构271及导电层272可以是一体成形的。在步骤150中,第二蚀刻遮罩253形成在导

电层272上,其中第二蚀刻遮罩253对准第一导电结构271,例如第二蚀刻遮罩253从上方遮蔽第一导电结构271。第二蚀刻遮罩253可以是图案化的硬遮罩或图案化的光阻,并具有开口253a,但本发明并不以此为限。具体而言,第一导电结构271及导电层272可以借由化学气相沉积、物理气相沉积、镀敷(例如,电镀或无电镀敷)或其他合适的方法形成,本发明不以此为限。

33.在本发明的一些实施方式中,第一导电结构271包括第一导电子结构271a及第二导电子结构271b,第二导电子结构271b位于第一导电子结构271a上,且第二导电子结构271b的宽度大于第一导电子结构271a的宽度。第一导电结构271是由传导性材料所构成,传导性材料可以是钨、铝、铜、钛、钽、氮化钛或其合金。在本发明的一些实施方式中,第一导电子结构271a及第二导电子结构271b是由相同的传导性材料所构成,但第一导电子结构271a及第二导电子结构271b也可以是由不同的传导性材料所构成,本发明并不以此为限。

34.请参考图6,图6可用以表示步骤160,步骤160包括通过第二蚀刻遮罩253(如图5)及其开口253a(如图5)蚀刻导电层272(如图5),以形成接触第一导电结构271的第二导电结构273,其中第二导电结构273从上方接触第二导电子结构271b。具体而言,可以利用第二蚀刻遮罩253配合非等向性蚀刻工艺形成第二导电结构273,第二蚀刻遮罩253及其开口253a可定义第二导电结构273尺寸及形状。此外,第二导电结构273是由传导性材料所制成,其中第一导电结构271及第二导电结构273是由相同的传导性材料所制成,但第一导电结构271及第二导电结构273(例如第二导电子结构271b)也可以不同的传导性材料所制成,但本发明并不以此为限。

35.请参考图7,在步骤160结束后,可以在第一介电层231上形成第二介电层233,其中第二介电层233环绕第二导电结构273。第一介电层231与第二介电层233可以是由相同的材料所制成,但第一介电层231与第二介电层233也可以是由不同的介电材料所制成,本发明并不以此为限。

36.请再参考图7,图7绘示为一种半导体的集成电路导线结构200包括基板210、第一介电层231、第二介电层233、第一导电结构271及第二导电结构273。第一介电层231位于基板210上。第二介电层233位于第一介电层231上,第一导电结构271位于第一介电层231内,且第二导电结构273位于第二介电层233内,其中第二导电结构273接触第一导电结构271以形成高长径比的导电线路结构(例如长径比大于10),且第二导电结构273的宽度与第二导电子结构271b的宽度大致相同。由于集成电路导线结构200的各个元件和其制造方法已经详细介绍再先前段落,故在此不再重复赘述。

37.在本发明的一些实施方式中,第一导电结构271包括第一导电子结构271a及第二导电子结构271b,第二导电子结构271b位于第一导电子结构271a上,且第一导电结构271接触第一导电结构271的第二导电子结构271b。此外,第二导电子结构271b的宽度大于第一导电子结构271a的宽度。在一些实施方式中,第一导电子结构271a可以是导通孔(via),但本发明不以此为限。

38.具体而言,第一导电结构271具有第一上顶部271c及第一下底部271d,且第一上顶部271c的宽度大于第一下底部271d的宽度。第二导电结构273具有第二上顶部273a及第二下底部273b,且第二上顶部273a的宽度小于第二下底部273b的宽度。此外,第一导电结构271的第一上顶部271c接触第二导电结构273的第二下底部273b。

39.综上所述,本发明的集成电路导线结构及其制造方法,具有相连接的第一导电结构及第二导电结构,因此可以形成具有高长径比的集成电路导线结构。再者,本发明的第一集成电路导线结构具有上下接触的第一导电子结构及第二导电子结构,其中第二导电子结构的宽度大于第一导电子结构的宽度,可以改进现有半导体领域中的导线互连构造。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1