一种基于纳米电流通道的相变存储器

1.本发明属于相变存储技术领域,更具体地,涉及一种基于纳米电流通道的相变存储器。

背景技术:

2.随着信息时代的到来,存储器在生活中占据了越来越重要的地位,目前存储器的研究一直朝着高速度、低功耗、高稳定性的方向发展。其中,利用材料相变性能制作的相变存储器(pcram)在半导体市场中有着巨大的潜力。

3.相变存储器的基本原理在于:相变材料可以在晶态与非晶态之间进行可逆转换,利用材料的不同状态之间呈现的巨大阻值差异来实现“1”和“0”数据存储。通常使用的相变材料为硫系化合物,通过控制施加脉冲电流的幅值和脉宽就可以很轻松地控制硫系化合物在晶态和非晶态之间的转换,并通过对电阻的测量读取出存储在相变存储器中的二进制数据。相变存储器具有读写速度快、存储密度高、与传统cmos工艺相兼容等优点。

4.在目前所有新型存储器技术中,相变存储器的定位是取代dram,虽然目前其速度已达到了dram速度的量级,但其功耗还需要进一步降低,特别是在进一步提高集成度如3d存储的情况下,降低相变存储单元的功耗也有利于减小单元间的热串扰。

5.由于相变存储器是利用电流的热效应实现器件内部温度的变化,从而实现相变材料在晶态与非晶态之间的可逆变换,因此pcram单元的写入电流与参与相变的材料量成比例,单元尺寸越小,单元的写入功耗越小。另外,在器件单元尺寸不变的情况下,严格控制写入电流的产热效率(提高相变区域的电流密度、改善相变材料的发热效率及降低其熔化温度等)和散热条件也有利于减小器件功耗。

6.目前减小相变存储单元功耗的方法主要分为两类,一类是采用新型高发热效率、低熔化温度的低功耗相变材料,另一类是改变器件结构。其中,改变器件结构最直接的方法是通过减小器件尺寸来减少相变材料的量同时提高电流密度,如限制型相变存储单元结构等,但这种方法需要更高的工艺制程,工艺成本高、难度大。其他的改变器件结构的方法,如边接触型、非对称结构、环状电极结构、增加二维材料热阻层等,都是在不提高工艺制程的前提下,通过尽量减小参与相变的材料量或减少器件的散热来实现降低相变单元的写入功耗的,但这些方法都需要对器件结构和工艺进行大的改变,存在工艺成本较高、难度较大的问题。

技术实现要素:

7.针对现有技术的缺陷,本发明提供了一种基于纳米电流通道的相变存储器,其目的在于解决通过改变现有器件的结构来降低写入功耗的工艺成本高、难度大的问题,并提高接触区域的电流密度,提高产热效率,提高热利用效率,使得相变存储器能够在不减小单元尺寸、不提高工艺制程的条件下减小写入功耗。

8.本发明提供了一种基于纳米电流通道的相变存储器,包括设置在相变层与电极层

之间的纳米电流通道层,纳米电流通道层为含有贯穿该层膜厚的金属纳米晶粒的绝缘绝热层,金属纳米晶粒直接连通电极层和相变层,电流仅通过金属纳米晶粒所形成的纳米电流通道从所述电极层到达所述相变层,相变层仅通过金属纳米晶粒与电极层接触,有效减小了相变层与电极层之间的接触面积,提高了相变层中的电热利用效率,降低了器件功耗。

9.由于金属纳米晶粒所形成的纳米电流通道减小了相变层与电极层的接触面积,提高了局部电流密度,从而提高了产热效率;同时,纳米电流通道层的绝缘绝热材料部分可阻止热量从相变层向电极层散失,起到热阻效果。因此,纳米电流通道层的加入能显著降低相变存储器功耗。

10.其中,纳米电流通道层为由绝缘绝热材料和嵌入于绝缘绝热材料中的金属纳米晶粒共同形成的薄膜结构,且所述金属纳米晶粒贯穿该层形成纳米电流通道。

11.更进一步地,相变存储器还包括:第一电极层,第二电极层和相变材料层;第一电极层与相变材料邻接,相变材料层与纳米电流通道层邻接,第二电极层与纳米电流通道层邻接;纳米电流通道层为含有贯穿整层的金属纳米晶粒的绝缘层单层。

12.其中,金属纳米晶粒的材料为fe、pt、w、cu、zn、al、ni、ti、au、ag单质金属材料中的至少一种,或由单质金属材料fe、pt、w、cu、zn、al、ni、ti、au、ag任意两种及以上形成的合金材料,或由单质金属材料fe、pt、w、cu、zn、al、ni、ti、au、ag生成的导电性良好的化合物。

13.更进一步地,纳米电流通道层的金属纳米晶粒相比于绝缘绝热材料具有较高的电导率。

14.更进一步地,绝缘绝热材料具有较低的热导率,绝缘绝热材料为氧化硅、氮化硅、氧化铝、氮化铝、氧化锌、氧化钨、氧化钛、氮化硼和碳化硅中的任意一种。

15.更进一步地,纳米电流通道层的厚度为1nm~30nm。

16.更进一步地,金属纳米晶粒在绝缘层中的尺寸为1nm~30nm,所述金属纳米晶粒在垂直于薄膜方向上的尺寸不小于纳米电流通道层的厚度。

17.更进一步地,相变层材料层包括硫系化合物,所述硫系化合物包括s、se和te中任意一种或与其他非硫系材料形成的合金化合物,其中所述非硫系材料包括ge、sb、ga、bi、in、sn、pb、ag、n和o中的一种或多种。

18.其中,相变材料层包括gete、gesb、ge2sb2te5、ge1sb2te4,sb2te3、aginsbte,以及含硫系化合物的超晶格相变材料或异质结构相变材料,包括(gete)/(sb2te3),(gete)/(bi2te3),(sb2te3)/(tite2)、gete/sb、(ge

‑

sb

‑

te)/(sb

‑

te)或(ge

‑

sb

‑

te)/c。

19.其中,相变材料层包括对硫系化合物掺杂改性形成的化合物,其中掺杂元素包括c,n,o,cu,cr,sc,ti中至少一种。

20.其中,相变材料层包括单元素相变材料sb或te。

21.更进一步地,相变材料层的厚度为20nm~200nm。

22.更进一步地,第一电极的材料和第二电极的材料包括金属单质au、ta、pt、al、w、ti、cu、ir及其金属合金和金属化合物,如tiw,tin。

23.其中,第一电极的材料和第二电极的材料的厚度为20nm~300nm。

24.与采用更先进制程制作尽可能小的相变存储单元相比,本发明能够突破工艺限制,在较宽松的工艺制程下进一步缩小电极与相变材料的有效接触面积,大大提高接触区域的电流密度,提高产热效率;同时纳米电流通道层中低热导率的绝缘绝热材料能有效减

少热量散失,提高热利用效率;随着有效接触面积的减小,相变区域的体积也相应减少,相变所需要的总能量也更低,从而使得相变存储器能够在不减小单元尺寸、不提高工艺制程的条件下减小写入功耗。

25.另外,与其他改变器件结构的方法(如边接触型、非对称结构、环状电极结构、增加二维材料热阻等)相比,本发明不需要太多地改变器件的结构,只需要加一层纳米电流通道层而已,而纳米电流通道层的制备方法也非常简单,与相变层的制备方法兼容,在大大降低器件功耗的同时,具有工艺简单的优势。

附图说明

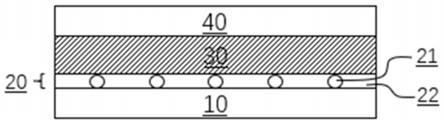

26.图1为传统相变存储器示范性结构剖视图;

27.图2为本发明实施例1提供的具有纳米电流通道层相变存储器示范性结构剖视图;

28.图3(a)~(i)分别为本发明实施例3中表示含有纳米电流通道的器件结构制备工艺流程;

29.图4(a)为本发明实施例4中所做的含有ag晶粒的纳米电流通道层(绝缘部分的材料为sio2)的tem图像;

30.图4(b)为本发明实施例4中所做的含ag晶粒的纳米电流通道层的相变存储器件与无该层的相同结构相变器件的v

‑

r关系曲线,其中所施加电压reset脉冲的脉宽为50ns;

31.图5(a)为本发明实施例5中所做的含有au晶粒的纳米电流通道层(绝缘绝热部分的材料为sio2)的tem图像;

32.图5(b)为本发明实施例5中所做的含au纳米电流通道层的相变存储器件与无该层的相同结构相变器件的v

‑

r关系曲线,其中所施加电压reset脉冲的脉宽为50ns;

33.图6为本发明实施例6中几种原子在sio2中1200k条件下运行4ps的均方位移msd;

34.图7为本发明实施例6中几种原子在sio2中1200k条件下运行10ps后的径向分布函数。

具体实施方式

35.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

36.本发明提供了一种基于纳米电流通道的相变存储器,具体是在相变存储器中的电极与相变层之间插入一层纳米电流通道层,该纳米电流通道层是由高电导率的金属或金属化合物在低电导率低热导率的绝缘绝热材料中生长聚集形成纳米晶粒,纳米晶粒在一定工艺条件下生长可以贯穿绝缘层而形成导电的纳米电流通道。该纳米电流通道层用以限制电流的路径,使得电流在流经该层时从高电导率纳米晶粒进入相变层,电流被限制在纳米电流通道中,该纳米级导电通道大大减小了相变层与电极层之间的接触面积,并极大地提高了局部接触部位的电流密度,提高了电流在相变层中的产热效率。同时,纳米电流通道层中高电导率纳米晶粒之外的部分为低电导率低热导率的绝缘绝热材料,其低热导率阻止了相变层中的热量向电极层散失,从而起到了热阻的效果,提高了相变层的电热利用效率,有利于进一步降低器件的写入功耗。

37.作为本发明的一个实施例,本发明提供的一种使用纳米电流通道的相变存储器的结构依次包括:

38.第一电极层,与相变材料邻接;

39.相变材料层;

40.纳米电流通道层,纳米电流通道层邻接相变材料,且是含有贯穿整层的金属纳米晶粒的绝缘层单层;

41.第二电极,与纳米电流通道层邻接。

42.其中,纳米电流通道层是由绝缘绝热材料和嵌入于绝缘绝热材料中的金属纳米晶粒共同形成的薄膜结构,金属纳米晶粒贯穿该层形成纳米电流通道。

43.其中,金属纳米晶粒的材料包含金属单质,金属化合物以及金属合金。

44.优选的,金属纳米晶粒材料为fe、pt、w、cu、zn、al、ni、ti、au、ag单质金属材料中的至少一种,或由单质金属材料fe、pt、w、cu、zn、al、ni、ti、au、ag任意两种及以上形成的合金材料,或由单质金属材料fe、pt、w、cu、zn、al、ni、ti、au、ag生成的导电性良好的化合物。

45.绝缘绝热材料为氧化硅、氮化硅、氧化铝、氮化铝、氧化锌、氧化钨、氧化钛、氮化硼、碳化硅中的至少一种。绝缘绝热材料需要具有较低的热导率。

46.其中,纳米电流通道层的厚度在1nm~30nm。金属纳米晶粒在绝缘层中的尺寸为1nm~30nm,金属纳米晶粒在垂直于薄膜方向上的尺寸不小于纳米电流通道层的厚度。

47.相变层材料包括硫系化合物及单元素相变材料。

48.优选的,硫系化合物包括s、se、te其中一种与其他非硫系材料形成的合金化合物,其中所述非硫系材料包括ge、sb、ga、bi、in、sn、pb、ag、n、o中的一种或多种。

49.优选的,硫系化合物包括gete、gesb、ge2sb2te5、ge1sb2te4,sb2te3、aginsbte。

50.更优选的,硫系化合物包括对上述合金化合物掺杂改性形成的化合物,其中掺杂元素包括c,n,o,cu,cr,sc,ti中至少一种。

51.相变材料还包括含硫系化合物的超晶格相变材料或异质结构相变材料,包括(gete)/(sb2te3),(gete)/(bi2te3),(sb2te3)/(tite2)、gete/sb、(ge

‑

sb

‑

te)/(sb

‑

te)、(ge

‑

sb

‑

te)/c。

52.相变层材料还包括单元素相变材料,如sb或te。

53.按照本发明的又一方面,本发明还提供了一种纳米电流通道层材料筛选、匹配及制备方法。其特征在于,通过vasp,materials studio,lammps等软件通过第一性原理以及分子动力学计算金属原子在绝缘绝热材料中的均方位移,形成能,径向分布函数等用以筛选与绝缘绝热材料相匹配的金属单质及金属合金。

54.按照本发明的再一方面,本发明提供一种纳米电流通道层及含有纳米电流通道层的相变存储器的制备方法,其特征在于,采用磁控溅射法、化学气相沉积法、等离子增强化学气相沉积法、物理气相沉积法、激光脉冲沉积法、蒸发法、电化学生长法、离子注入法、分子束外延法、原子气相沉积法及原子层沉积法中任意一种。

55.本发明还提供了一种基于纳米电流通道的相变存储器的制备方法,其目的在于不减小器件尺寸的情况下增大局部的电流密度从而使材料能够完成相变,达到减小器件所需功耗的目的。

56.为了更进一步的说明本发明实施例提供的基于纳米电流通道的相变存储器,以下

结合具体实施例详述如下:

57.实施例1:

58.按照本发明的第1实施例,传统相变存储器示范性结构剖视图以图1示出。

59.底电极10形成于sio2衬底上,底电极10的材料选自w,pt,au,al,cu,ti,ta等金属材料及其合金的导电材料。相变材料层30形成于底电极10上,相变层材料30包括硫系化合物。优选的,硫系化合物包括s、se、te其中一种与其他非硫系材料形成的合金化合物,其中非硫系材料包括ge、sb、ga、bi、in、sn、pb、ag、n、o中的一种或多种;优选的,硫系化合物包括gete、gesb、ge2sb2te5、ge1sb2te4,sb2te3、aginsbte;更优选的,硫系化合物包括对上述合金化合物掺杂改性形成的化合物,其中掺杂元素包括c,n,o,cu,cr,sc,ti中至少一种。相变材料还包括含硫系化合物的超晶格相变材料或异质结构相变材料,包括(gete)/(sb2te3),(gete)/(bi2te3),(sb2te3)/(tite2)、gete/sb、(ge

‑

sb

‑

te)/(sb

‑

te)、(ge

‑

sb

‑

te)/c。所述相变层材料还包括单元素相变材料,如sb、te。上电极40形成于相变材料层30上,上电极40的材料选自w,pt,au,al,cu,ti,ta等金属材料及其合金的导电材料。

60.按照本发明的第1实施例,具有纳米电流通道层相变存储器示范性结构剖视图以图2示出。底电极10形成于sio2衬底上,底电极10的材料选自w,pt,au,al,cu,ti,ta等金属材料及其合金的导电材料。纳米电流通道20形成于底电极10上,纳米电流通道20由绝缘绝热材料22以及嵌于绝缘绝热材料层中间的导电纳米晶粒21构成,其中,纳米电流通道层20的厚度在1nm~30nm。导电纳米粒子在绝缘层中的尺寸为1nm~30nm,导电纳米粒子21在垂直于薄膜方向上的尺寸不小于纳米电流通道层20的厚度。与绝缘绝热材料22相比,导电纳米晶粒21具有更小的电阻率,相变材料层30形成于纳米电流通道20上,相变层材料30包括硫系化合物。优选的,所述硫系化合物包括s、se、te其中一种与其他非硫系材料形成的合金化合物,其中非硫系材料包括ge、sb、ga、bi、in、sn、pb、ag、n、o中的一种或多种;优选的,硫系化合物包括gete、gesb、ge2sb2te5、ge1sb2te4,sb2te3、aginsbte;更优选的,硫系化合物包括对上述合金化合物掺杂改性形成的化合物,其中掺杂元素包括c,n,o,cu,cr,sc,ti中至少一种。相变材料还包括含硫系化合物的超晶格相变材料或异质结构相变材料,包括(gete)/(sb2te3),(gete)/(bi2te3),(sb2te3)/(tite2)、gete/sb、(ge

‑

sb

‑

te)/(sb

‑

te)、(ge

‑

sb

‑

te)/c。相变层材料还包括单元素相变材料,如sb、te。上电极40形成于相变材料层30上,上电极40的材料选自w,pt,au,al,cu,ti,ta等金属材料及其合金的导电材料。

61.实施例1图中所示为最简单的三层相变存储单元结构,并不仅仅限于三层结构,也可以是t型结构、限制型结构;还可以是附加选通管的相变存储器单元结构。

62.实施例2:

63.按照本发明的第2实施例,具有纳米电流通道层相变存储器结构以及传统的相变存储器结构写入过程进行有限元仿真。

64.该仿真采用实施例1中的最简单的三层相变存储单元结构。仿真使用的材料参数在表1(有限元分析使用的具体各种材料的热学与电学参数)中列出,两种单元结构的上下电极材料均为pt,单元间绝缘材料为sio2以及相变层材料为ge2sb2te5,上下电极、绝缘层、相变层的厚度均为100nm,单元器件的直径为100nm,在有纳米电流通道层的结构中,设定纳米电流通道层的厚度为5nm,该层绝缘绝热部分采用sio2材料,使用ag作为纳米电流通道,其直径为6nm。分别对两种结构模型施加幅值为60ua,脉宽为50ns的reset电流脉冲。

[0065][0066][0067]

表1

[0068]

对比在两种不同结构中施加相同的reset电流脉冲后相变层的最高温度和电流密度最大值。结果显示,含有纳米电流通道层的单元中相变层达到的最高温度为963k,电流密度最大为5*109a/m2,且电流密度最大处在纳米电流通道附近。在普通单元结构中,相变层中达到的最高温度为845k。电流密度最大为9*108a/m2,且电流密度在ge2sb2te5中分布较为均匀。由此分析得知,含有纳米电流通道层结构的器件单元在相同的电流脉冲作用下能够达到的最高温度高于普通的小孔结构,这表明纳米电流通道层结构能够在更低的功耗下完成相变存储器的reset操作,具有低功耗优势。

[0069]

实施例3:

[0070]

按照本发明的第3实施例,含有纳米电流通道层的t型相变存储单元制备工艺流程如下:

[0071]

(1)选取sio2/si(100)基片,将sio2/si(100)基片在丙酮溶液中用40w的功率超声15分钟,用于清洗表面、灰尘颗粒和有机杂质,再去离子水冲洗;

[0072]

(2)将处理后的基片在乙醇溶液中用40w的功率超声15分钟,用去离子水冲洗,高纯n2气吹干表面和背面,得到待溅射基片。

[0073]

(3)如图3(a)所示,使用磁控溅射法将底电极10生长于衬底00上,该底电极10使用pt材料,制备时通入高纯氩气作为溅射气体,溅射气压为0.5pa,电源功率为35w,该底电极10厚度通常为20nm~300nm。

[0074]

(4)如图3(b)所示,利用物理气相沉积(pecvd)方法在底电极50层上沉积绝缘层60,绝缘层60为sio2,厚度为100纳米。

[0075]

(5)如图3(c)所示,利用匀胶机在绝缘层60上均匀平铺一层光刻胶61。

[0076]

(6)如图3(d)所示,利用电子束曝光系统(ebl)在绝缘层60上形成带250nm直径的圆形小孔的光刻胶掩膜61。

[0077]

(7)如图3(e)所示,利用等离子体刻蚀技术(icp)刻蚀绝缘层60,由于被光刻胶61覆盖的部分受到保护,不会被刻蚀,而没有光刻胶61覆盖的部分暴露在外会被刻蚀掉,直到露出底电极10。

[0078]

(8)如图3(f)所示,使用磁控溅射,离子注入及退火等工艺制备纳米电流通道层20。其中金属纳米晶粒21在纳米电流通道层20中生长聚集,形成导电通道。本实施例中,纳米电流通道层中绝缘绝热材料选用sio2,金属导电材料选用ag。

[0079]

(9)利用去胶液去除光刻胶61,最终获得如图3(g)所示的最终效果。

[0080]

(10)利用紫外光刻系统在小孔上套刻出100μm

×

100μm的方形孔结构。该方形孔与icp刻蚀出的圆形小孔中心对准(图中未示出)。

[0081]

(11)如图3(h)所示,在方形孔内利用磁控溅射沉积出相变材料层30,相变材料层30的相变材料包括硫系化合物。硫系化合物包括s、se、te相变层材料30包括硫系化合物。优选的,硫系化合物包括s、se、te其中一种与其他非硫系材料形成的合金化合物,其中非硫系材料包括ge、sb、ga、bi、in、sn、pb、ag、n、o中的一种或多种;优选的,所述硫系化合物包括gete、gesb、ge2sb2te5、ge1sb2te4,sb2te3、aginsbte;更优选的,硫系化合物包括对上述合金化合物掺杂改性形成的化合物,其中掺杂元素包括c,n,o,cu,cr,sc,ti中至少一种。相变材料还包括含硫系化合物的超晶格相变材料或异质结构相变材料,包括(gete)/(sb2te3),(gete)/(bi2te3),(sb2te3)/(tite2)、gete/sb、(ge

‑

sb

‑

te)/(sb

‑

te)、(ge

‑

sb

‑

te)/c。相变层材料还包括单元素相变材料,如sb、te。其中一种与其他非硫系材料形成的合金化合物,其中非硫系材料包括ge、sb、ga、bi、in、sn、pb;本实施例使用的相变材料以ge2sb2te5为例。制备时通入高纯氩气作为溅射气体,溅射气压为0.5pa,电源功率为35w,靶和基片的距离180mm,该相变材料层30的厚度为100nm。

[0082]

(12)利用磁控溅射沉积上电极层40,上电极层同样为pt金属电极材料。完成之后利用剥离工艺去除紫外光刻的光刻胶,最终的效果图如图3(i)所示的结构。

[0083]

实施例4:

[0084]

对含有ag纳米电流通道层薄膜进行微观测试,得到sio2‑

ag高分辨图像,纳米电流通道层的厚度为5nm,在图像4(a)中明显能够看到sio2中有团簇生成,团簇直径为10nm,能够贯穿sio2层,通过成分分析可以看出形成的团簇为ag。这表明ag晶粒能够在sio2中聚集生长,使得纳米电流通道层导通,电流可以通过ag纳米晶粒从下电极层传导至相变层。

[0085]

图4(b)为本发明的实施例4中含有上述ag纳米电流通道层的器件和对照组传统结构器件reset的v

‑

r关系曲线。除了上述5nm的ag纳米电流通道层外,两个器件在其它层的材料和结构上都完全相同。其中,相变层材料均为ge2sb2te5(gst),厚度为100nm。器件单元直径为250nm,绝缘层材料为sio2,厚度为100nm,上下电极材料为tin,厚度为100nm。

[0086]

器件的reset测试方法如下:通过b1500a半导体测试仪对两者分别施加脉宽为50ns,上升沿和下降沿分别为10ns,电压逐步增加的reset脉冲。结果显示,含有ag

‑

sio2纳米电流通道层的器件的reset电压为0.6v,所需的功耗为3.3*10

‑5j,而传统器件结构reset电压为1.6v,所需的功耗为2.1*10

‑4j,两者对比可以得出含有ag纳米晶粒的电流通道层能有效降低器件相变过程中所需的功耗。

[0087]

实施例5:

[0088]

改变纳米电流通道层中的金属材料,对含有au纳米晶粒的电流通道层薄膜进行微观测试,得到sio2‑

au高分辨透射电镜图像,纳米电流通道层的厚度为3nm,在图像5(a)中明显能够看到sio2中有团簇生成,团簇直径在3nm,能够贯穿sio2层,通过成分分析可以看出形成的团簇为au。这表明含au能够在sio2中聚集生长,使得纳米电流通道层导通,电流可以通过au纳米晶粒从下电极层传导至相变层。

[0089]

图5(b)为本发明的实施例5中含有上述au纳米电流通道层的器件和对照组传统结构器件reset的v

‑

r关系曲线。除了上述5nm厚的au纳米电流通道层外,两个器件在其它层的材料和结构上都完全相同。其中,相变层材料均为ge2sb2te5(gst),厚度为100nm。器件单元直径为250nm,绝缘层材料为sio2,厚度为100nm。上下电极材料为tin,厚度为100nm。

[0090]

器件的reset测试方法如下:通过b1500a半导体测试仪对两者分别施加脉宽为

50ns,上升沿和下降沿分别为10ns,电压逐步增加的reset脉冲。结果显示,含有au

‑

sio2纳米电流通道层的器件的reset电压为0.5v,所需的功耗为1.25*10

‑4j,而传统器件结构reset电压为1.6v,所需的功耗为2.1*10

‑4j,两者对比可以得出含有au纳米晶粒的电流通道层能有效降低器件相变过程中所需的功耗。

[0091]

实施例6:

[0092]

按照本发明的第6实施例,如图6和图7所示,对纳米电流通道中的绝缘绝热材料和纳米电流通道材料进行选择和匹配,以确保选定的金属导电材料能在绝缘绝热材料中很容易地生长并聚集成晶粒。两种材料的选择及匹配方法如下:

[0093]

(1)首先选定绝缘绝热材料,绝缘绝热材料需要有较大的电阻率和较低的热导率,大电阻率保证电流不会在整层导通,只会通过纳米电流通道进入相变层,低热导率可以使得该层除纳米电流通道之外的部分对相变层内的产热起到保温的效果,减少擦写过程中的热量散失,进一步降低功耗。该材料的选择也可以根据实验条件确定。本实施例中选择sio2作为纳米电流通道层中的绝缘绝热材料。

[0094]

(2)建立晶体sio2模型,使用vasp软件对晶体sio2模型升温至5000k,使其融化,再降温至300k运行2ps得到非晶sio2模型。

[0095]

(3)形成能计算:在非晶sio2中掺入计划选择的某一种纳米电流通道材料的原子,对其进行结构优化,计算其结构能量,通过公式e

f

=e

nx@绝缘绝热材料

‑

e

绝缘绝热材料

‑

ne

x

计算形成能,其中e

nx@绝缘绝热材料

表示n个原子在绝缘绝热材料(sio2)中的体系的总能量,e

绝缘绝热材料

表示绝缘绝热材料(sio2)的能量,ne

x

表示n个掺入原子的总原子势。通常情况下,形成能为正表示选定的元素原子可以在选定的绝缘绝热材料(本实施例中为sio2)中生长并聚集成晶粒,正的形成能数值越大,表明越容易聚集成晶粒并形成纳米电流通道。

[0096]

(4)均方位移msd计算:在非晶sio2中随机掺入计划选择的某一种纳米电流通道材料的原子,对其进行结构优化,在1200k下运行4ps的分子动力学计算,统计其均方位移msd。均方位移大小表示选定的元素原子在选定的绝缘绝热材料(本实施例中为sio2)中迁移的难易程度。在相同时间内均方位移数值越大,表明原子在选定的绝缘绝热材料中运动越剧烈,即越容易实现迁移。

[0097]

(5)径向分布函数的计算:在非晶sio2中随机掺入计划一定比例(原子数之比,本实施例中为12%)的某一种纳米电流通道材料的原子,对其进行结构优化,在1200k下运行10ps的分子动力学计算,统计其掺入原子间的径向分布函数。径向分布函数的峰值的大小反应其聚集程度,峰值越大,表示原子在选定的绝缘绝热材料中聚集程度越高,越容易生长成核,并形成大的晶粒。

[0098]

(6)综合考虑原子在sio2中的形成能和均方位移以及径向分布函数筛选出适合在sio2中生长聚集的材料。

[0099]

表2是计算得到的几种纳米电流通道材料的原子在sio2中的形成能,图6是这些材料原子1200k时在sio2中的均方位移msd。

[0100][0101]

表2

[0102]

根据形成能对比可以看出,ag和au在sio2中的形成能为正,相比于al、ti和w更容

易聚集生长;ag、au在sio2中的均方位移比al、w、ti高,说明ag、au相比于al、w、ti更容易在sio2中迁移;在图7径向分布函数中能够发现au和ag对应的峰值较高,聚集程度较为明显。因此,ag、au相比于其他材料更容易在sio2中形成金属纳米晶粒,进而形成纳米电流通道。

[0103]

实施例7:纳米电流通道层的制备工艺方法1

[0104]

纳米电流通道层制备方法,其特征在于,可以采用溅射法,具体溅射方式为以下四种中任意一种:(1)金属靶材与绝缘绝热材料靶材共溅射。(2)金属靶材与绝缘绝热材料靶材交替溅射。(3)将金属片直接放置在绝缘绝热材料靶材上进行掺杂溅射。(4)将绝缘绝热材料片直接放置在金属靶材上进行掺杂溅射。

[0105]

本实施例以含ag晶粒的sio2纳米电流通道层为例,使用磁控溅射的方法溅射纳米电流通道层,具体制备方法包括以下步骤:

[0106]

(a)在溅射腔内放入sio2靶和ag靶,并将真空度抽至10

‑4pa;

[0107]

(b)使用高纯ar气作为溅射气体,设定ar气流稳定为10sccm,并将溅射气压调节至0.5pa,靶和基片的距离120mm;

[0108]

(c)设定交流溅射电源功率为200w,接sio2靶位,溅射100s,生长2nmsio2后关闭交流电源,设定直流溅射电源功率为30w,接ag靶位,溅射10s,生长1nmag后关闭直流电源,再次打开交流电源溅射100ssio2,生长2nmsio2后关闭电源;

[0109]

(d)将溅射得到的基片放入真空退火炉中,退火炉以15℃/min的速度升温至400℃,并在400℃下保温30min。使金属ag在sio2中生长并团聚形成贯穿sio2层厚度的纳米金属晶粒,如图4(a)。

[0110]

步骤(d)中的退火温度及保温时间,可以根据sio2层和ag层的厚度比来优化,如厚度比越大,需要的退火温度越高、保温时间越长,优化的目标是使金属ag在sio2中生长并团聚形成贯穿sio2层厚度的纳米金属晶粒。

[0111]

实施例8:纳米电流通道层的制备工艺方法2

[0112]

纳米电流通道层制备方法,其特征在于,可以采用溅射法,具体溅射方式为以下四种中任意一种:(1)金属靶材与绝缘绝热材料靶材共溅射。(2)金属靶材与绝缘绝热材料靶材交替溅射。(3)将金属片直接放置在绝缘绝热材料靶材上进行掺杂溅射。(4)将绝缘绝热材料片直接放置在金属靶材上进行掺杂溅射。

[0113]

本实施例以含au晶粒的sio2纳米电流通道层为例,使用磁控溅射的方法溅射纳米电流通道层30,具体制备方法包括以下步骤:

[0114]

(a)在sio2靶材表面刻蚀环处放8片1cm*0.5cm大小的au片,并将真空抽至10

‑4pa;

[0115]

(b)使用高纯ar气作为溅射气体,设定ar气流稳定为10sccm,并将溅射气压调节至0.5pa,靶和基片的距离120mm;

[0116]

(c)设定交流溅射电源功率为200w,溅射200s;

[0117]

(d)将溅射得到的基片放入真空退火炉中,退火炉以15℃/min的速度升温至400℃,并在400℃下保温30min。使金属au在sio2层中生长并团聚形成贯穿sio2层厚度的纳米金属晶粒,如图5(a)。

[0118]

步骤(d)中的退火温度及保温时间,可以根据au片的数量(或au片覆盖刻蚀环的面积大小)优化,如au片数量越少(覆盖刻蚀环的面积越小),需要的退火温度越高、保温时间越长,优化的目标是使金属au在sio2层中生长并团聚形成贯穿sio2层厚度的纳米金属晶粒。

[0119]

本实施例中的共溅射方法,也可以通过提高溅射过程中基片的温度来替代后续的退火工艺。基片温度的提高有利于增加金属原子的迁移动能,促进金属原子的聚集及其晶粒的生长,目标同样是形成贯穿纳米电流通道层厚度的纳米金属晶粒。

[0120]

本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1