印刷配线板及印刷配线板的制造方法与流程

1.本发明涉及一种印刷配线板及印刷配线板的制造方法。

背景技术:

2.已知一种印刷配线板,该印刷配线板具有:基膜,其具有绝缘性;导电图案,其层叠于该基膜;以及绝缘层,其层叠于上述基膜及导电图案。

3.作为用于形成上述绝缘层的绝缘层形成材料,例如使用具有固化性树脂层的干膜。具体而言,上述绝缘层通过在将导电图案层叠于基膜一个面的状态下从基膜的层叠有导电图案的面侧一边对干膜进行加热一边进行按压而形成(参照日本特开2015-229734号公报)。

4.专利文献1:日本特开2015-229734号公报

技术实现要素:

5.但是,上述印刷配线板有时产生导电图案的一部分在绝缘层的外表面侧露出的不良情况。另外,该不良情况容易在形成有导电图案的导电图案形成区域的外侧端部(在导电图案形成区域中导电图案形成区域与没有形成导电图案的区域的边界附近)产生。

6.具体而言,绝缘层形成材料在导电图案形成区域的外侧端部由于导电图案和基膜表面之间的阶梯差而流动至基膜侧(没有形成导电图案的侧),由此容易产生上述不良情况。

7.本发明就是基于上述情况而提出的,课题在于,提供能够防止导电图案向绝缘层的外表面侧露出的印刷配线板及印刷配线板的制造方法。

8.为了解决上述课题而提出的本发明涉及的印刷配线板具有:基膜,其具有绝缘性;导电图案,其层叠于上述基膜,包含平行地配置的多个配线;以及绝缘层,其层叠于上述基膜及导电图案,在该印刷配线板,上述绝缘层具有在俯视观察时与上述导电图案的形成区域重叠的第1区域、和在俯视观察时不与上述导电图案的形成区域重叠的第2区域,上述第2区域具有从上述第1区域连续而从上述基膜表面起的厚度逐渐减小的倾斜部,在与上述第1区域及第2区域的边界面垂直的厚度方向剖面,在将从上述倾斜部的顶部至向下到上述基膜表面的垂线的垂足的长度设为h1,将从上述倾斜部的底部至向下到上述基膜表面的垂线的垂足的长度设为h2,将上述顶部及底部间的上述基膜的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值为0.01以上1.0以下。

9.另外,为了解决上述课题而提出的本发明涉及的印刷配线板的制造方法具有:第1层叠工序,在具有绝缘性的基膜对包含平行地配置的多个配线的导电图案进行层叠;以及第2层叠工序,在上述第1层叠工序之后在上述基膜及导电图案对绝缘层进行层叠,在该印刷配线板的制造方法,上述绝缘层具有在俯视观察时与上述导电图案的形成区域重叠的第1区域、和在俯视观察时不与上述导电图案的形成区域重叠的第2区域,上述第2区域具有从上述第1区域连续而从上述基膜表面起的厚度逐渐减小的倾斜部,在与上述第1区域及第2

区域的边界面垂直的厚度方向剖面,在将从上述倾斜部的顶部至向下到上述基膜表面的垂线的垂足的长度设为h1,将从上述倾斜部的底部至向下到上述基膜表面的垂线的垂足的长度设为h2,将上述顶部及底部间的上述基膜的平面方向距离设为w的情况下,在上述第2层叠工序,将由(h1-h2)/w表示的厚度的变化率的平均值控制于0.01以上1.0以下。

10.发明的效果

11.本发明涉及的印刷配线板能够防止导电图案向绝缘层的外表面侧露出。本发明涉及的印刷配线板的制造方法能够制造防止了导电图案向绝缘层的外表面侧露出的印刷配线板。

附图说明

12.图1是表示本发明的一个实施方式涉及的印刷配线板的示意性俯视图。

13.图2是图1的印刷配线板的a-a线部分剖面图。

14.图3是图2的印刷配线板的局部放大图。

15.图4是表示图1的印刷配线板的制造方法的流程图。

16.图5是表示与图1的印刷配线板不同的实施方式涉及的印刷配线板的示意性俯视图。

17.图6是图5的印刷配线板的b-b线部分剖面图。

18.图7是图6的印刷配线板的局部放大图。

19.图8是表示与图1及图5的印刷配线板不同的实施方式涉及的印刷配线板的示意性俯视图。

20.图9是图8的印刷配线板的c-c线部分剖面图。

21.图10是图9的印刷配线板的局部放大图。

22.图11是表示与图1、图5及图8的印刷配线板不同的实施方式涉及的印刷配线板的示意性俯视图。

23.图12是图11的印刷配线板的d-d线部分剖面图。

24.图13是图12的印刷配线板的局部放大图。

25.图14是表示图1、图5、图8及图11的印刷配线板不同的实施方式涉及的印刷配线板的示意性俯视图。

26.图15是图14的印刷配线板的局部放大图。

27.图16是图15的印刷配线板的e-e线部分端面图。

具体实施方式

28.[本发明的实施方式的说明]

[0029]

首先,列举本发明的实施方式进行说明。

[0030]

本发明涉及的印刷配线板具有:基膜,其具有绝缘性;导电图案,其层叠于上述基膜,包含平行地配置的多个配线;以及绝缘层,其层叠于上述基膜及导电图案,在该印刷配线板,上述绝缘层具有在俯视观察时与上述导电图案的形成区域重叠的第1区域、和在俯视观察时不与上述导电图案的形成区域重叠的第2区域,上述第2区域具有从上述第1区域连续而从上述基膜表面起的厚度逐渐减小的倾斜部,在与上述第1区域及第2区域的边界面垂

直的厚度方向剖面,在将从上述倾斜部的顶部至向下到上述基膜表面的垂线的垂足的长度设为h1,将从上述倾斜部的底部至向下到上述基膜表面的垂线的垂足的长度设为h2,将上述顶部及底部间的上述基膜的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值为0.01以上1.0以下。

[0031]

对于该印刷配线板,在与第1区域及第2区域的边界面垂直的厚度方向剖面,在将从上述倾斜部的顶部至向下到上述基膜表面的垂线的垂足的长度设为h1,将从上述倾斜部的底部至向下到上述基膜表面的垂线的垂足为止的长度设为h2,将上述顶部及底部间的上述基膜的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值处于上述范围内,因此能够防止导电图案向绝缘层的外表面侧露出。

[0032]

可以是在上述多个配线的宽度方向的外侧还具有以与这些配线电绝缘状态且与这些配线平行地配置的1个或多个伪配线。如上所述,在上述多个配线的宽度方向的外侧还具有以与这些配线电绝缘状态且与这些配线平行地配置的1个或多个伪配线,从而容易地将上述倾斜部的厚度的变化率控制于上述范围内,能够更可靠地防止上述导电图案向绝缘层的外表面侧露出。

[0033]

可以是上述多个配线中的在上述第2区域侧配置的1个或多个配线的厚度小于在上述第1区域的中心侧配置的1个或多个配线的厚度。如上所述,上述多个配线中的在上述第2区域侧配置的1个或多个配线的厚度小于在上述第1区域的中心侧配置的1个或多个配线的厚度,从而容易地将上述倾斜部的厚度的变化率控制于上述范围内,能够更可靠地防止上述导电图案向绝缘层的外表面侧露出。

[0034]

可以是上述多个配线包含:1个或多个第1配线,其具有第1厚度;以及1个或多个第2配线,其与上述1个或多个第1配线相比靠上述第2区域侧配置,具有小于上述第1厚度的第2厚度。如上所述,上述多个配线包含:1个或多个第1配线,其具有第1厚度;以及1个或多个第2配线,其与上述1个或多个第1配线相比靠上述第2区域侧配置,具有小于上述第1厚度的第2厚度,从而能够容易且可靠地将上述倾斜部的厚度的变化率控制于上述范围内。

[0035]

可以是上述导电图案具有镀敷引线,上述印刷配线板还具有以与上述镀敷引线电绝缘状态且与该镀敷引线并排地配置的1个或多个伪引线。如上所述,上述导电图案具有镀敷引线,上述印刷配线板还具有以与上述镀敷引线电绝缘状态且与该镀敷引线并排地配置的1个或多个伪引线,从而能够容易地防止上述镀敷引线向绝缘层的外表面侧露出。

[0036]

可以是上述导电图案具有焊盘部,上述印刷配线板还具有以与上述焊盘部电绝缘状态且以将该焊盘部包围的方式配置的1个或多个伪配线。如上所述,上述导电图案具有焊盘部,上述印刷配线板还具有以与上述焊盘部电绝缘状态且以将该焊盘部包围的方式配置的1个或多个伪配线,从而能够容易地防止上述焊盘部向绝缘层的外表面侧露出。

[0037]

可以是上述导电图案具有连接配线,该连接配线以t字状连接于上述多个配线中的至少1个配线的端部,在上述配线及连接配线的连接部分,上述连接配线的与连接于上述配线的一侧相反侧的侧缘和与该侧缘相对的侧缘之间的宽度是均匀的。如上所述,上述导电图案具有连接配线,该连接配线以t字状连接于上述多个配线中的至少1个配线的端部,在上述配线及连接配线的连接部分,上述连接配线的与连接于上述配线的一侧相反侧的侧缘和与该侧缘相对的侧缘之间的宽度是均匀的,从而能够抑制上述配线及连接配线的连接部分的厚度变得大于其他部分的厚度的情况。由此,能够防止因上述连接部分和基膜表面

之间的阶梯差引起上述连接部分在绝缘层的外表面侧露出的情况。

[0038]

本发明涉及的印刷配线板的制造方法具有:第1层叠工序,在具有绝缘性的基膜对包含平行地配置的多个配线的导电图案进行层叠;以及第2层叠工序,在上述第1层叠工序之后在上述基膜及导电图案对绝缘层进行层叠,在该印刷配线板的制造方法,上述绝缘层具有在俯视观察时与上述导电图案的形成区域重叠的第1区域、和在俯视观察时不与上述导电图案的形成区域重叠的第2区域,上述第2区域具有从上述第1区域连续而从上述基膜表面起的厚度逐渐减小的倾斜部,在与上述第1区域及第2区域的边界面垂直的厚度方向剖面,在将从上述倾斜部的顶部至向下到上述基膜表面的垂线的垂足的长度设为h1,将从上述倾斜部的底部至向下到上述基膜表面的垂线的垂足的长度设为h2,将上述顶部及底部间的上述基膜的平面方向距离设为w的情况下,在上述第2层叠工序,将由(h1-h2)/w表示的厚度的变化率的平均值控制于0.01以上1.0以下。

[0039]

该印刷配线板的制造方法在上述第2层叠工序将由(h1-h2)/w表示的倾斜部的厚度的变化率的平均值控制于上述范围内,因此能够防止导电图案向绝缘层的外表面侧露出。

[0040]

可以是在上述第2层叠工序,通过感光性干膜的固化而层叠上述绝缘层。如上所述,在上述第2层叠工序,通过感光性干膜的固化而层叠上述绝缘层,从而能够容易且可靠地制造防止了上述导电图案向绝缘层的外表面侧露出的印刷配线板。

[0041]

此外,在本发明,“平行”是指两者所成的角度为5

°

以下、优选为3

°

以下的情况。“导电图案的形成区域”是指密集地配置有构成导电图案的导体的区域,具体而言是指相邻的导体彼此以50μm以下、优选30μm以下的间隔进行配置的区域。“厚度的变化率的平均值”是指,任意的10个点的厚度的变化率的平均值。连接配线“以t字状连接于”配线的端部是指以配线的端部不从连接配线的另一侧(连接侧的相反侧)凸出的状态进行连接。“宽度是均匀的”是指最大宽度和最小宽度的差为4μm以下、优选为2μm以下的情况。

[0042]

[本发明的实施方式的详细内容]

[0043]

以下,参照附图对本发明的各实施方式涉及的印刷配线板及印刷配线板的制造方法详细进行说明。

[0044]

[第一实施方式]

[0045]

<印刷配线板>

[0046]

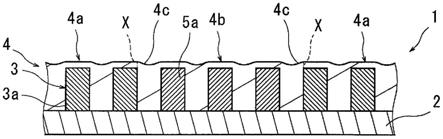

图1及图2的印刷配线板1具有:基膜2,其具有绝缘性;导电图案3,其层叠于基膜2,包含平行地配置的多个配线3a;以及绝缘层4,其层叠于基膜2及导电图案3。绝缘层4具有在俯视观察时与导电图案3的形成区域重叠的第1区域4a、和在俯视观察时不与导电图案3的形成区域重叠的第2区域4b。第2区域4b具有从第1区域4a连续而从基膜2表面起的厚度逐渐减小的倾斜部4c。

[0047]

该印刷配线板1在多个配线3a的宽度方向的外侧具有以与这些配线3a电绝缘状态且与这些配线3a平行地配置的多个伪配线(以下,还称为“第1伪配线5a”)。多个第1伪配线5a在导电图案3的形成区域外与导电图案3的形成区域相邻地配置。此外,“多个配线的宽度方向的外侧”是指,平行地配置的多个配线组的并排方向的外侧,也可以是该印刷配线板的外缘侧及中心侧的任意者。

[0048]

如图2及图3所示,对于该印刷配线板1,在与第1区域4a及第2区域4b的边界面x垂

直的厚度方向剖面中,在将从倾斜部4c的顶部4e、即倾斜部4c的上端至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部4c的底部4f、即倾斜部4c的下端至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部4e及底部4f间的基膜2的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值为0.01以上1.0以下。

[0049]

对于该印刷配线板1,在与第1区域4a及第2区域4b的边界面x垂直的厚度方向剖面,在将从倾斜部4c的顶部4e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部4c的底部4f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部4e及底部4f间的基膜2的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值处于上述范围内,倾斜部4c的倾斜充分平缓。因此,对于该印刷配线板1,导电图案3中的导电图案3的形成区域的外侧端部的边缘被绝缘层4适当地包覆,能够防止导电图案3向绝缘层4的外表面侧露出。

[0050]

该印刷配线板1在多个配线3a的宽度方向的外侧具有以与多个配线3a电绝缘状态且与多个配线3a平行地配置的多个第1伪配线5a,因此在使用例如感光性干膜而形成绝缘层4时,容易对熔融的感光性干膜从多个配线3a侧向第2区域4b侧的流动进行拦截。其结果,能够容易地将倾斜部4c的厚度的变化率控制于上述范围内,更可靠地防止多个配线3a向绝缘层4的外表面侧露出。

[0051]

(基膜)

[0052]

基膜2以合成树脂作为主成分,具有电绝缘性。基膜2是用于形成导电图案3的基材层。基膜2也可以具有挠性。在基膜2具有挠性的情况下,该印刷配线板1作为柔性印刷配线板而构成。此外,“主成分”是指质量换算中含有比例最大的成分,例如是指含量为50质量%以上的成分。

[0053]

作为上述合成树脂,例如举出聚酰亚胺、聚对苯二甲酸乙二醇酯、液晶聚合物、氟树脂等。

[0054]

在该印刷配线板1为柔性印刷配线板的情况下,作为基膜2的平均厚度的下限,优选为5μm,更优选为10μm。另一方面,作为基膜2的平均厚度的上限,优选为50μm,更优选为40μm。如果基膜2的平均厚度小于上述下限,则基膜2的绝缘强度有可能不充分。相反,如果基膜2的平均厚度超过上述上限,则该印刷配线板1有可能不必要地变厚、挠性有可能不充分。此外,本说明书中“平均厚度”是指任意的10个点的厚度的平均值。

[0055]

(导电图案)

[0056]

导电图案3为由具有导电性的导体构成的层,包含平行地配置的多个配线3a。多个配线3a例如形成线圈图案。另外,导电图案3也可以包含多个配线3a以外的例如焊盘部3b等的图案。

[0057]

多个配线3a例如是层叠于基膜2的晶种层和层叠于该晶种层的电镀层的层叠体。另外,多个配线3a也可以设为如下结构,即,具有:芯体,其由上述晶种层及电镀层构成;以及包覆层,其通过镀敷而层叠于该芯体的外表面。作为上述晶种层的主成分,例如举出铜、镍、银等。上述晶种层例如通过无电解镀而形成。另外,上述晶种层可以是在基膜2的表面涂敷含有金属颗粒的油墨并使金属颗粒烧结而成的金属颗粒烧结体层,也可以是上述烧结体层及无电解镀敷层的层叠体。另外,上述电镀层通过电镀而形成。作为上述电镀层的主成分,举出铜、镍、银等。

[0058]

作为多个配线3a的平均厚度的上限,优选为90μm,更优选为70μm。如果上述平均厚度超过上述上限,则有可能违反该印刷配线板1的薄型化的要求。另一方面,作为多个配线3a的平均厚度的下限,优选为5μm,更优选为10μm。如果上述平均厚度小于上述下限,则电阻有可能变大。另外,作为上述平均厚度的下限,例如可以为30μm,也可以为40μm。通常,如果配线的厚度变厚,则该配线在绝缘层的外表面侧容易露出,该印刷配线板1在将多个配线3a的平均厚度的下限设为上述值的情况下,也能够充分防止多个配线3a向绝缘层4的外表面侧露出。

[0059]

作为多个配线3a的平均宽度的下限,优选为5μm,更优选为10μm。另一方面,作为多个配线3a的平均宽度的上限,优选为50μm,更优选为30μm。如果上述平均宽度小于上述下限,则有可能不容易进行多个配线3a的形成。另外,如果上述平均宽度小于上述下限,则有可能无法将多个配线3a的厚度设得充分大。相反,如果上述平均宽度超过上述上限,则有可能难以得到希望的配线密度。此外,“平均宽度”是指任意的10个点的宽度的平均值。

[0060]

多个配线3a优选以相同间距进行配置。作为相邻的配线3a间的平均间距的下限,优选为10μm,更优选为20μm。另一方面,作为上述平均间距的上限,优选为100μm,更优选为60μm。如果上述平均间距小于上述下限,则有可能不容易进行多个配线3a的形成。相反,如果上述平均间距超过上述上限,则有可能难以得到希望的配线密度。

[0061]

作为相邻的配线3a间的平均间隔的下限,优选为5μm,更优选为10μm。另一方面,作为上述平均间隔的上限,优选为50μm,更优选为30μm。如果上述平均间隔小于上述下限,则有可能不容易进行多个配线3a的形成。相反,如果上述平均间隔超过上述上限,则有可能难以得到希望的配线密度。此外,“平均间隔”是指任意的10个点的间隔的平均值。

[0062]

(伪配线)

[0063]

多个第1伪配线5a与导电图案3设置于相同的层。多个第1伪配线5a在基膜2和绝缘层4之间与多个配线3a并排地配置。

[0064]

多个第1伪配线5a例如与多个配线3a相同地,是层叠于基膜2的晶种层和层叠于该晶种层的电镀层的层叠体。另外,多个第1伪配线5a也可以设为如下结构,即,具有:芯体,其由上述晶种层及电镀层构成;以及包覆层,其通过镀敷而层叠于该芯体的外表面。该印刷配线板1在多个配线3a的宽度方向的外侧设置多个第1伪配线5a,由此能够更可靠地对熔融的感光性干膜从第1区域4a向第2区域4b侧的流动进行拦截。在设置多个第1伪配线5a的情况下,作为这些第1伪配线5a的根数的下限,优选为2根,更优选为3根。另外,作为多个第1伪配线5a的根数的上限,例如可以设为5根。

[0065]

多个第1伪配线5a的平均厚度优选为与多个第1伪配线5a相邻的1个或多个配线3a的平均厚度以下。作为使多个第1伪配线5a的平均厚度小于上述多个配线3a的平均厚度的具体结构,例如举出设为使多个配线3a具有上述芯体及包覆层的结构,设为使多个伪配线3a由上述芯体构成的结构(即,上述晶种层及电镀层的层叠体)。在设为使多个配线3a具有上述芯体及包覆层的结构、设为使多个伪配线3a由上述芯体构成的结构的情况下,多个第1伪配线5a的宽度小于多个配线3a。在该情况下,作为多个配线3a和多个第1伪配线5a的平均厚度的差,例如可以设为3μm以上12μm以下。另外,作为多个配线3a和多个第1伪配线5a的平均宽度的差,例如可以设为6μm以上24μm以下。该印刷配线板1通过将多个第1伪配线5a的平均厚度设为与这些第1伪配线5a相邻的1个或多个配线3a的平均厚度以下,从而减小多个第

1伪配线5a和基膜2的表面之间的阶梯差,容易防止多个第1伪配线5a向绝缘层4的外表面侧露出。此外,该印刷配线板1从可靠地防止多个第1伪配线5a向绝缘层4的外表面侧露出的观点出发,也可以使位于与第1区域4a相反侧的1个或多个第1伪配线5a的平均厚度小于位于第1区域4a侧的1个或多个第1伪配线5a的平均厚度。

[0066]

多个第1伪配线5a优选与多个配线3a以相同间距进行配置。如上所述,通过将多个第1伪配线5a与多个配线3a以相同间距进行配置,从而实现绝缘层4整体的厚度的均匀化,容易防止多个配线3a向绝缘层4的外表面侧露出。另外,作为相邻的配线3a及第1伪配线5a的平均间隔,可以设为与相邻的配线3a间的平均间隔相同。

[0067]

(绝缘层)

[0068]

绝缘层4层叠于导电图案3、多个第1伪配线5a、以及基膜2的没有层叠导电图案3及多个第1伪配线5a的区域。绝缘层4主要是防止因导电图案3与其他部件等接触引起的损伤及短路。因此,绝缘层4优选除了有意地设置的开口、切口以外将导电图案3的外表面全面地进行包覆。

[0069]

绝缘层4可以使用阻焊剂、覆盖层等而形成,其中优选通过感光性干膜的固化而形成。在使用感光性干膜的情况下,从多个配线3a的外表面侧一边对感光性干膜进行加热一边进行按压,由此,该感光性干膜流动,一边对多个配线3a的外表面进行包覆一边对多个配线3a间的间隙进行填埋。另外,该感光性干膜的平均厚度优选小于多个配线3a的平均厚度。通过将感光性干膜的平均厚度设为小于多个配线3a的平均厚度,从而能够减小绝缘层4的厚度而促进该印刷配线板的薄型化。另外,通常,在感光性干膜的平均厚度小于多个配线的平均厚度的情况下,如果感光性干膜向导电图案的形成区域外过度地流动,则多个配线的外表面有可能在绝缘层的外表面侧露出,但该印刷配线板1能够通过多个第1伪配线5a而抑制感光性干膜的流动,因此能够防止多个配线3a的露出。在使用与多个配线3a相比平均厚度小的感光性干膜的情况下,作为在多个配线3a的与基膜2相反侧的面层叠的绝缘层4的平均厚度的下限,优选为5μm,更优选为15μm。另外,作为上述平均厚度的上限,优选为40μm,更优选为35μm。

[0070]

在使用与多个配线3a相比平均厚度小的感光性干膜的情况下,从防止多个配线3a向绝缘层4外表面侧的露出的观点出发,作为多个配线3a的平均厚度和上述感光性干膜的平均厚度的差的上限,优选为10μm,更优选为7μm。另一方面,从实现该印刷配线板1的薄型化的观点出发,作为多个配线3a的平均厚度和上述感光性干膜的平均厚度的差的下限,优选为1μm,更优选为3μm。

[0071]

如上所述,绝缘层4具有在俯视观察时与导电图案3的形成区域重叠的第1区域4a、和在俯视观察时不与导电图案3的形成区域重叠的第2区域4b。绝缘层4的除了第1区域4a以外的区域作为第2区域4b而构成。另外,在俯视观察时,第1区域4a的外缘与导电图案3的形成区域的外缘一致。即,在俯视观察时,第1区域4a及第2区域4b的边界面x与位于导电图案3的形成区域的最外侧的导体的侧缘一致。另外,在该边界面x,多个配线3a除了有意的开口及切口以外在绝缘层4的外表面侧不露出。

[0072]

倾斜部4c将与第1区域4a的边界面x作为端缘而形成于第2区域4b。对于倾斜部4c,在与边界面x垂直的厚度方向剖面,将与第1区域4a的边界面x的位置设为顶部4e,在第2区域4b侧厚度逐渐减小。在本实施方式,倾斜部4c的底部4f例如形成于相邻的配线3a及第1伪

配线5a的中间位置。此外,倾斜部4c在中途可以包含厚度大致均匀的区域,例如也可以是从边界面x朝向第2区域4b侧的恒定区域的厚度大致均匀。

[0073]

在与第1区域4a及第2区域4b的边界面x垂直的厚度方向剖面,在将从倾斜部4c的顶部4e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部4c的底部4f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部4e及底部4f间的基膜2的平面方向距离设为w的情况下,作为由(h1-h2)/w表示的厚度的变化率的平均值的下限,如上所述为0.01,优选为0.1。另一方面,作为上述变化率的平均值的上限,如上所述为1.0,优选为0.5。如果上述变化率小于上述下限,则有可能不容易进行绝缘层4的薄膜化。相反,如果上述变化率超过上述上限,则多个配线3a特别是位于导电图案3的最外部的配线3a有可能在绝缘层4的外表面侧露出。

[0074]

<印刷配线板的制造方法>

[0075]

接着,参照图4对图1的印刷配线板1的制造方法的一个例子进行说明。该印刷配线板的制造方法具有:第1层叠工序,在具有绝缘性的基膜2,对包含平行地配置的多个配线3a的导电图案3进行层叠;以及第2层叠工序,在上述第1层叠工序之后,在基膜2及导电图案3对绝缘层4进行层叠。在该印刷配线板的制造方法,绝缘层4具有在俯视观察时与导电图案3的形成区域重叠的第1区域4a、和在俯视观察时不与导电图案3的形成区域重叠的第2区域4b,第2区域4b具有从第1区域4a连续而从基膜2表面起的厚度逐渐减小的倾斜部4c。

[0076]

(第1层叠工序)

[0077]

在上述第1层叠工序,在基膜2的表面,与导电图案3同时地对多个第1伪配线5a进行层叠。上述第1层叠工序例如使用半加成法对包含多个配线3a的导电图案3及多个第1伪配线5a进行层叠。具体而言,上述第1层叠工序具有如下工序:在基膜2的表面对晶种层进行层叠;在该晶种层层叠工序之后,在上述晶种层的表面形成具有导电图案3及多个第1伪配线5a的反转形状的抗蚀图案;对上述抗蚀图案形成工序之后的晶种层的表面进行电镀;以及在上述电镀工序之后将与上述抗蚀图案及上述晶种层的抗蚀图案重叠的区域去除。此外,在上述抗蚀图案形成工序,也可以针对多个配线3a及多个第1伪配线5a的全部或一部分,形成具有芯体的反转形状的抗蚀图案。在该情况下,上述第1层叠工序还具有在上述除去工序之后在上述芯体对包覆层进行层叠的工序。上述晶种层层叠工序例如可以通过无电解镀而进行,也可以通过对包含金属颗粒的油墨进行涂敷,使该金属颗粒烧结而进行,也可以通过上述金属颗粒的烧结及无电解镀这两者而进行。另外,上述包覆工序例如可以通过无电解镀而进行,也可以通过电镀而进行。

[0078]

(第2层叠工序)

[0079]

在上述第2层叠工序,通过感光性干膜的固化而层叠绝缘层4。在上述第2层叠工序,优选将与多个配线3a的平均厚度相比平均厚度小的感光性干膜从导电图案3及多个第1伪配线5a的外表面侧进行热层压。通过将上述感光性干膜从导电图案3及多个第1伪配线5a的外表面侧一边进行加热一边进行按压,由此该感光性干膜流动,一边对多个配线3a的外表面及多个第1伪配线5a的外表面进行包覆,一边对多个配线3a间的间隙及多个第1伪配线5a间的间隙进行填埋。由此,能够减小绝缘层4的厚度而促进该印刷配线板的薄型化。该印刷配线板的制造方法能够通过多个第1伪配线5a而抑制感光性干膜的流动,因此在使用了与多个配线3a的平均厚度相比平均厚度小的感光性干膜的情况下,也能够防止多个配线3a

向绝缘层4的外表面侧露出。

[0080]

在使用与多个配线3a相比平均厚度小的感光性干膜的情况下,作为多个配线3a的平均厚度和上述感光性干膜的平均厚度的差的下限,优选为1μm,更优选为3μm。另一方面,作为上述差的上限,优选为10μm,更优选为7μm。如果上述差小于上述下限,则有可能难以促进该印刷配线板1的薄型化。相反,如果上述差超过上述上限,则有可能难以防止多个配线3a向绝缘层4的外表面侧露出。

[0081]

在上述第2层叠工序,在与第1区域4a及第2区域4b的边界面x垂直的厚度方向剖面,在将从倾斜部4c的顶部4e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部4c的底部4f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部4e及底部4f间的基膜2的平面方向距离设为w的情况下,将由(h1-h2)/w表示的厚度的变化率的平均值控制于0.01以上1.0以下。作为上述变化率的下限,优选为0.1。作为上述变化率的上限,优选为0.5。如果上述变化率小于上述下限,则有可能不容易进行绝缘层4的薄膜化。相反,如果上述变化率超过上述上限,则多个配线3a、特别是位于导电图案3的最外部的配线3a有可能在绝缘层4的外表面侧露出。

[0082]

该印刷配线板的制造方法在上述第2层叠工序将由(h1-h2)/w表示的倾斜部4c的厚度的变化率的平均值控制于上述范围内,因此能够防止导电图案3、特别是多个配线3a向绝缘层4的外表面侧露出。

[0083]

该印刷配线板的制造方法在上述第2层叠工序将绝缘层4通过感光性干膜的固化而层叠,因此能够容易且可靠地制造防止了导电图案3向绝缘层4的外表面侧露出的印刷配线板。另外,根据该结构,能够减薄绝缘层4的厚度而促进该印刷配线板1的薄型化。

[0084]

[第二实施方式]

[0085]

<印刷配线板>

[0086]

图5及图6的印刷配线板11具有:基膜2,其具有绝缘性;导电图案13,其层叠于基膜2,包含平行地配置的多个配线13a;以及绝缘层14,其层叠于基膜2及导电图案13。绝缘层14具有在俯视观察时与导电图案13的形成区域重叠的第1区域14a、和在俯视观察时不与导电图案13的形成区域重叠的第2区域14b。第2区域14b具有从第1区域14a连续而从基膜2表面起的厚度逐渐减小的倾斜部14c。作为该印刷配线板11的基膜2,可以设为与图1的印刷配线板1的基膜2相同的结构,因此标注相同标号而省略说明。

[0087]

对于该印刷配线板1,多个配线13a中的在第2区域14b侧配置的1个或多个配线13a(在本实施方式,与第2区域14b相邻的1个配线13a)的厚度小于在第1区域14a的中心侧配置的多个配线13a的厚度。另外,该印刷配线板11在厚度小的1个或多个配线13a的宽度方向的外侧不具有伪配线。

[0088]

如图6及图7所示,对于该印刷配线板11,在与第1区域14a及第2区域14b的边界面x垂直的厚度方向剖面,在将从倾斜部14c的顶部14e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部14c的底部14f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部14e及底部14f间的基膜2的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值为0.01以上1.0以下。

[0089]

对于该印刷配线板11,多个配线13a中的在第2区域14b侧配置的1个或多个配线13a的厚度小于在第1区域14a的中心侧配置的多个配线13a的厚度,因此容易将倾斜部14c

的厚度的变化率控制于上述范围内,能够更可靠地防止多个配线13a向绝缘层14的外表面侧露出。更详细地,该印刷配线板11通过将在第1区域14a的中心侧配置的多个配线13a和在第2区域14b侧配置的1个或多个配线13a之间的阶梯差、以及在第2区域14b侧配置的1个或多个配线13a和基膜2表面之间的阶梯差都设得小,从而能够防止因感光性干膜的流动引起多个配线13a向绝缘层14的外表面侧露出的情况。

[0090]

(导电图案)

[0091]

导电图案13为由具有导电性的导体构成的层,包含平行地配置的多个配线13a。多个配线13a例如形成线圈图案。另外,导电图案13也可以包含多个配线13a以外的例如焊盘部13b等的图案。

[0092]

如图7所示,多个配线13a包含:多个第1配线13c,其具有第1厚度;以及1个或多个第2配线13d(本实施方式为1个第2配线13d),其与多个第1配线13c相比靠第2区域14b侧配置,具有小于第1厚度的第2厚度。多个配线13a由多个第1配线13c及1个或多个第2配线13d这2种配线构成。多个配线13a具有多个第1配线13c在宽度方向相邻地设置的第1配线组和1个或多个第2配线13d在宽度方向相邻地设置的第2配线组,第2配线组配置于第1配线组的第2区域14b侧。另外,对于该印刷配线板11,在比第2配线组靠外侧(第2区域14b侧),在基膜2的表面没有层叠其他配线及伪配线。对于该印刷配线板11,多个配线13a包含多个第1配线13c和与多个第1配线13c相比靠第2区域14b侧配置的1个或多个第2配线13d,由此能够容易且可靠地对倾斜部14c的厚度的变化率进行控制。

[0093]

多个第1配线13c例如具有:晶种层,其层叠于基膜2;芯体13e,其由层叠于该晶种层的电镀层构成;以及包覆层13f,其通过镀敷而层叠于该芯体13e的外表面。另一方面,1个或多个第2配线13d由层叠有上述晶种层及电镀的芯体13e构成。作为上述晶种层、电镀层及包覆层的具体结构,可以设为与图1的印刷配线板1相同。

[0094]

作为多个第1配线13c的平均厚度的上限,优选为90μm,更优选为70μm。另外,作为多个第1配线13c的平均厚度的下限,优选为10μm,更优选为15μm。如果上述平均厚度小于上述下限,则电阻有可能变大。相反,如果上述平均厚度超过上述上限,则有可能违反该印刷配线板11的薄型化的要求。

[0095]

作为多个第1配线13c的平均宽度的下限,优选为15μm,更优选为20μm。另一方面,作为多个第1配线13c的平均宽度的上限,优选为50μm,更优选为30μm。如果上述平均宽度小于上述下限,则有可能不容易进行多个第1配线13c的形成。另外,如果上述平均宽度小于上述下限,则有可能无法将多个第1配线13c的厚度设得充分大。相反,如果上述平均厚度超过上述上限,则有可能难以得到希望的配线密度。

[0096]

1个或多个第2配线13d与多个第1配线13c相比,厚度小与包覆层13f的厚度对应量。另外,1个或多个第2配线13d与多个第1配线13c相比,宽度小与包覆层13f的厚度的2倍对应量。作为包覆层13f的平均厚度的下限,优选为1μm,更优选为3μm。另一方面,作为包覆层13f的平均厚度的上限,优选为15μm,更优选为12μm。如果包覆层13f的平均厚度小于上述下限,则相对于多个第1配线13c和1个或多个第2配线13d之间的阶梯差,1个或多个第2配线13d和基膜2表面之间的阶梯差有可能变得过大。相反,如果包覆层13f的平均厚度超过上述上限,则多个第1配线13c和1个或多个第2配线13d之间的阶梯差有可能变得过大。

[0097]

多个配线13a优选以相同间距进行配置。作为相邻的第1配线13c间的平均间隔的

下限,优选为5μm,更优选为10μm。另一方面,作为上述平均间隔的上限,优选为50μm,更优选为30μm。如果上述平均间隔小于上述下限,则有可能不容易进行多个配线13a的形成。相反,如果上述平均间隔超过上述上限,则有可能难以得到希望的配线密度。

[0098]

(绝缘层)

[0099]

绝缘层14层叠于导电图案13及基膜2的没有层叠导电图案13的区域。绝缘层14主要防止因导电图案13与其他部件等接触引起的损伤及短路。因此,绝缘层14优选除了有意地设置的开口、切口以外将导电图案13的外表面全面地进行包覆。

[0100]

绝缘层14可以与图1的印刷配线板1相同地,由阻焊剂、覆盖层等构成,优选通过感光性干膜的固化而形成。另外,该感光性干膜的平均厚度优选小于多个配线13a的平均厚度。作为多个配线13a的平均厚度和上述感光性干膜的平均厚度的差,可以设为与图1的印刷配线板1相同。另外,作为在多个第1配线13c的与基膜相反侧的面层叠的绝缘层14的平均厚度,可以设为与在图1的印刷配线板1的多个配线3a的与基膜2相反侧的面层叠的绝缘层4的平均厚度相同。

[0101]

如上所述,绝缘层14具有在俯视观察时与导电图案13的形成区域重叠的第1区域14a、和在俯视观察时不与导电图案13的形成区域重叠的第2区域14b。绝缘层14的除了第1区域14a以外的区域作为第2区域14b而构成。另外,在俯视观察时第1区域14a的外缘与导电图案13的形成区域的外缘一致。在第1区域14a及第2区域14b的边界面x,多个配线13a除了有意的开口及切口以外在绝缘层14的外表面侧不露出。

[0102]

倾斜部14c将与第1区域14a的边界面x作为端缘而形成于第2区域14b。对于倾斜部14c,在与边界面x垂直的厚度方向剖面,将与第1区域14a的边界面x的位置设为顶部14e,在第2区域14b侧厚度逐渐减小。在本实施方式,倾斜部14c的底部14f位于该印刷配线板11的外缘。

[0103]

在与第1区域14a及第2区域14b的边界面x垂直的厚度方向剖面,作为由(h1-h2)/w表示的厚度的变化率的平均值,可以设为与图1的印刷配线板1相同。

[0104]

<印刷配线板的制造方法>

[0105]

接着,对图5的印刷配线板11的制造方法的一个例子进行说明。该印刷配线板的制造方法具有:第1层叠工序,在具有绝缘性的基膜2对包含平行地配置的多个配线13a的导电图案13进行层叠;以及第2层叠工序,在上述第1层叠工序之后在基膜2及导电图案13对绝缘层14进行层叠。在该印刷配线板的制造方法,绝缘层14具有在俯视观察时与导电图案13的形成区域重叠的第1区域14a、和在俯视观察时不与导电图案13的形成区域重叠的第2区域14b,第2区域14b具有从第1区域14a连续而从基膜2表面起的厚度逐渐减小的倾斜部14c。

[0106]

(第1层叠工序)

[0107]

在上述第1层叠工序,例如与图4的印刷配线板的制造方法相同地,使用半加成法对包含多个配线13a的导电图案13进行层叠。在上述第1层叠工序,以多个配线13a中的在第2区域14b侧配置的1个或多个配线13a的厚度小于在第1区域14a的中心侧配置的多个配线13a的厚度的方式对多个配线13a进行层叠。在上述第1层叠工序,通过在图4的印刷配线板的制造方法中说明的上述的包覆工序,仅在构成多个第1配线13c的多个芯体13e对包覆层13f进行层叠。具体而言,在上述包覆工序,仅对构成多个第1配线13c的多个芯体13e连接镀敷引线(未图示),仅在这些芯体13e对包覆层13f进行层叠。

[0108]

(第2层叠工序)

[0109]

在上述第2层叠工序,通过感光性干膜的固化而层叠绝缘层14。在上述第2层叠工序,与图4的印刷配线板的制造方法相同地层叠绝缘层14。该印刷配线板的制造方法将多个第1配线13c和1个或多个第2配线13d之间的阶梯差、以及1个或多个第2配线13d和基膜2表面之间的阶梯差都设得小,由此能够防止因感光性干膜的流动引起多个配线13a向绝缘层14的外表面侧露出的情况。

[0110]

在上述第2层叠工序,在与第1区域14a及第2区域14b的边界面x垂直的厚度方向剖面,在将从倾斜部14c的顶部14e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部14c的底部14f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部14e及底部14f间的基膜2的平面方向距离设为w的情况下,将由(h1-h2)/w表示的厚度的变化率的平均值控制于0.01以上1.0以下。作为上述变化率的优选的下限值及优选的上限值,与图4的印刷配线板的制造方法相同。

[0111]

[第三实施方式]

[0112]

<印刷配线板>

[0113]

图8及图9的印刷配线板21具有:基膜2,其具有绝缘性;导电图案23,其层叠于基膜2,包含平行地配置的多个配线(未图示);以及绝缘层24,其层叠于基膜2及导电图案23。导电图案23具有镀敷引线23a。绝缘层24具有在俯视观察时与导电图案23的形成区域重叠的第1区域24a、和在俯视观察时不与导电图案23的形成区域重叠的第2区域24b。第2区域24b具有从第1区域24a连续而从基膜2表面起的厚度逐渐减小的倾斜部24c。作为该印刷配线板21的基膜2,可以设为与图1的印刷配线板1的基膜2相同的结构,因此标注相同标号而省略说明。

[0114]

该印刷配线板21具有以与镀敷引线23a电绝缘状态且与该镀敷引线23a并排地配置的1个或多个伪引线25a。

[0115]

如图9及图10所示,对于该印刷配线板21,在与第1区域24a及第2区域24b的边界面x垂直的厚度方向剖面,在将从倾斜部24c的顶部24e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部24c的底部24f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部24e及底部24f间的基膜2的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值为0.01以上1.0以下。

[0116]

对于该印刷配线板21,导电图案23具有镀敷引线23a,具有以与镀敷引线23a电绝缘状态且与该镀敷引线23a并排地配置的1个或多个伪引线25a,由此例如在使用感光性干膜而形成绝缘层24时,容易对熔融的感光性干膜从镀敷引线23a侧向第2区域24b侧的流动进行拦截。其结果,能够容易地防止镀敷引线23a向绝缘层24的外表面侧露出。

[0117]

(导电图案)

[0118]

导电图案23是由具有导电性的导体构成的层,包含平行地配置的多个配线。导电图案23除了具有镀敷引线23a以外,还可以设为具有例如与图1的印刷配线板1相同的结构。

[0119]

镀敷引线23a与导电图案23所包含的1个或多个上述配线电连接,例如用于形成这些配线的包覆层。作为镀敷引线23a的具体结构,不特别限定,可以设为例如与图7的芯体13e相同的结构。另外,作为镀敷引线23a的根数,不特别限定,在本实施方式,形成有平行的2根镀敷引线23a。作为2根镀敷引线23a的平均厚度、平均宽度及平均间距,可以设为与图7

的第2配线13d相同。

[0120]

(伪引线)

[0121]

1个或多个伪引线25a配置于导电图案23的形成区域外。1个或多个伪引线25a与导电图案23设置于相同的层。1个或多个伪配线25a在基膜2和绝缘层24之间与镀敷引线23a相邻地配置。在本实施方式,在2根镀敷引线23a的宽度方向的两外侧配置有各1根伪引线25a。此外,该印刷配线板21更可靠地防止镀敷引线23a向绝缘层24的外表面侧露出,因此,也可以在2根镀敷引线23a的两外侧分别配置有2个以上的伪引线25a。

[0122]

1个或多个伪引线25a的平均厚度优选为镀敷引线23a的平均厚度以下。在将1个或多个伪引线25a的平均厚度及镀敷引线23a的平均厚度设得均匀的情况下,例如也可以将1个或多个伪引线25a及镀敷引线23a设为与图7的芯体13e相同的结构。

[0123]

1个或多个伪引线25a及镀敷引线23a优选以相同间距进行配置。由此,实现绝缘层24的厚度的均匀化,容易防止镀敷引线23a向绝缘层24的外表面侧露出。另外,作为相邻的镀敷引线23a及伪引线25a的平均间隔,可以设为与图1的印刷配线板1的相邻的配线3a及伪引线5a的平均间隔相同。

[0124]

(绝缘层)

[0125]

绝缘层24层叠于导电图案23、1个或多个伪引线25a、以及基膜2的没有层叠导电图案23及1个或多个伪引线25a的区域。绝缘层24主要防止因导电图案23与其他部件等接触引起的损伤及短路。因此,绝缘层24优选除了有意地设置的开口、切口以外将导电图案3的外表面全面地进行包覆。

[0126]

绝缘层24也可以与图1的印刷配线板1相同地,由阻焊剂、覆盖层等构成,优选通过感光性干膜的固化而形成。作为在镀敷引线23a的与基膜2相反侧的面层叠的绝缘层24的平均厚度,可以设为与在图1的印刷配线板1的多个配线3a的与基膜2相反侧的面层叠的绝缘层4的平均厚度相同。

[0127]

如上所述,绝缘层24具有在俯视观察时与导电图案23的形成区域重叠的第1区域24a、和在俯视观察时不与导电图案23的形成区域重叠的第2区域24b。绝缘层24的除了第1区域24a以外的区域作为第2区域24b而构成。另外,在俯视观察时第1区域24a的外缘与导电图案23的形成区域的外缘一致。在第1区域24a及第2区域24b的边界面x,镀敷引线23a除了有意的开口及切口以外在绝缘层24的外表面侧不露出。

[0128]

倾斜部24c将与第1区域24a的边界面x作为端缘而形成于第2区域24b。对于倾斜部24c,在与边界面x垂直的厚度方向剖面,将与第1区域24a的边界面x的位置设为顶部24e,在第2区域24b侧厚度逐渐减小。在本实施方式,倾斜部24c的底部24f例如形成于相邻的镀敷引线23a及伪引线25a的中间位置。

[0129]

在与第1区域24a及第2区域24b的边界面x垂直的厚度方向剖面,作为由(h1-h2)/w表示的厚度的变化率的平均值,可以设为与图1的印刷配线板1相同。

[0130]

<印刷配线板的制造方法>

[0131]

接着,对图8的印刷配线板21的制造方法的一个例子进行说明。该印刷配线板的制造方法具有:第1层叠工序,其在具有绝缘性的基膜2对包含平行地配置的多个配线的导电图案23进行层叠;以及第2层叠工序,在上述第1层叠工序之后在基膜2及导电图案23对绝缘层24进行层叠。在该印刷配线板的制造方法,绝缘层24具有在俯视观察时与导电图案23的

形成区域重叠的第1区域24a、和在俯视观察时不与导电图案23的形成区域重叠的第2区域24b,第2区域24b具有从第1区域24a连续而从基膜2表面起的厚度逐渐减小的倾斜部24c。

[0132]

(第1层叠工序)

[0133]

上述第1层叠工序具有:在基膜2的表面对构成导电图案23的多个配线的芯体、镀敷引线23a、以及1个或多个伪引线25a同时进行层叠的工序(芯体层叠工序);以及在通过上述芯体层叠工序所层叠的希望的芯体对包覆层进行层叠的工序(包覆层层叠工序)。在上述第1层叠工序,将1个或多个伪引线35a以与镀敷引线23a电绝缘状态且与镀敷引线23a并排地进行层叠。上述芯体层叠工序可以与图4的印刷配线板的制造方法相同地,使用半加成法进行。

[0134]

(第2层叠工序)

[0135]

在上述第2层叠工序,将绝缘层24通过感光性干膜的固化而层叠。在上述第2层叠工序,与图4的印刷配线板的制造方法相同地层叠绝缘层24。该印刷配线板的制造方法在使用感光性干膜对绝缘层24进行层叠时,能够容易地对熔融的感光性干膜从镀敷引线23a侧向第2区域24b侧的流动进行拦截,防止镀敷引线23a向绝缘层24的外表面侧露出

[0136]

在上述第2层叠工序,在与第1区域24a及第2区域24b的边界面x垂直的厚度方向剖面,在将从倾斜部24c的顶部24e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部24c的底部24f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部24e及底部24f间的基膜2的平面方向距离设为w的情况下,将由(h1-h2)/w表示的厚度的变化率的平均值控制于0.01以上1.0以下。作为上述变化率的优选的下限值及优选的上限值,与图4的印刷配线板的制造方法相同。

[0137]

[第四实施方式]

[0138]

<印刷配线板>

[0139]

图11及图12的印刷配线板31具有:基膜2,其具有绝缘性;导电图案33,其层叠于基膜2,包含平行地配置的多个配线(未图示);以及绝缘层34,其层叠于基膜2及导电图案33。导电图案34具有焊盘部33c。绝缘层34具有在俯视观察时与导电图案33的形成区域重叠的第1区域34a、和在俯视观察时不与导电图案33的形成区域重叠的第2区域34b。第2区域34b具有从第1区域34a连续而从基膜2表面起的厚度逐渐减小的倾斜部34c。该印刷配线板31的导电图案33及绝缘层34层叠于基膜2的两面。作为该印刷配线板31的基膜2,可以设为与图1的印刷配线板1的基膜2相同的结构,因此标注相同标号而省略说明。

[0140]

该印刷配线板31具有以与焊盘部33c电绝缘状态且将焊盘部33c包围的方式配置的多个伪配线(以下,还称为“第2伪配线35a”)。

[0141]

如图12及图13所示,对于该印刷配线板31,在与第1区域34a及第2区域34b的边界面x垂直的厚度方向剖面,在将从倾斜部34c的顶部34e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部34c的底部34f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部34e及底部34f间的基膜2的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值为0.01以上1.0以下。

[0142]

对于该印刷配线板31,导电图案33具有焊盘部33c部,该印刷配线板31具有以与焊盘部33c电绝缘状态且将该焊盘部33c包围的方式配置的多个第2伪配线35a,由此在使用例如感光性干膜而形成绝缘层34时,容易对熔融的感光性干膜从焊盘部33c侧向第2区域34b

侧的流动进行拦截。其结果,能够容易地防止焊盘部33c向绝缘层34的外表面侧露出。

[0143]

(导电图案)

[0144]

导电图案33是由具有导电性的导体构成的层,包含平行地配置的多个配线。导电图案33除了具有焊盘部33c以外,还可以设为例如具有与图1的印刷配线板1相同的结构。

[0145]

在本实施方式,焊盘部33c是在通孔33b的基膜2的表面侧设置的通孔焊盘。焊盘部33c例如是通过在基膜2的两面层叠了芯体33d之后,形成将该芯体33d贯通的贯通孔,对该贯通孔实施与上述的包覆层相同的镀敷而形成的。因此,焊盘部33c包含在芯体33d及基膜2的两面侧设置的镀敷层。焊盘部33c俯视观察为圆环状。作为焊盘部33c的平均厚度,不特别限定。但是,通常焊盘部33c的平面面积大,因此在实施了镀敷时镀敷厚度容易变大。因此,与图7的第1配线13c相比,焊盘部33c的平均厚度容易变大。

[0146]

(伪配线)

[0147]

多个第2伪配线35a配置于导电图案33的形成区域外。多个第2伪配线35a与导电图案33设置于相同的层。在本实施方式,多个第2伪配线35a配置于基膜2的两面。多个第2伪配线35a在基膜2和绝缘层34之间与焊盘部33c相邻地配置。第2伪配线35a以与焊盘部33c的间隔遍及长度方向的整个区域而均匀的方式将焊盘部33c包围。因此,在本实施方式,各第2伪配线35a以形成有用于供与焊盘部33c连接的配线33a经过的开口的c字状形成。该印刷配线板31以将焊盘部33c包围的方式设置多个第2伪配线35a,由此能够更可靠地对熔融的感光性干膜从焊盘部33c侧向第2区域34b侧的流动进行拦截。特别是,对于该印刷配线板31,即使在焊盘部33c的厚度变得较大的情况下,通过具有多个第2伪配线35a也能够充分地对熔融的感光性干膜的流动进行抑制。在设置多个第2伪配线35a的情况下,作为这些第2伪配线35a的根数的下限,优选为2根,更优选为3根。另一方面,作为多个第2伪配线35a的根数的上限,例如可以设为5根。

[0148]

多个第2伪配线35a例如是层叠于基膜2的晶种层和层叠于该晶种层的电镀层的层叠体。另外,多个第2伪配线35a也可以设为如下结构,即,具有:芯体,其由上述晶种层及电镀层构成;以及包覆层,其通过镀敷而层叠于该芯体的外表面。在多个第2伪配线35a由上述晶种层及电镀层的层叠体构成的情况下,作为这些第2伪配线35a的平均厚度及平均宽度,可以设为与图7的第2配线13d相同。另外,在多个第2伪配线35a由上述芯体及包覆层构成的情况下,作为这些第2伪配线35a的平均厚度及平均宽度,可以设为与图7的第1配线13c相同。

[0149]

多个第2伪配线35a的平均厚度优选为焊盘部33c的平均厚度以下。在将多个第2伪配线35a的平均厚度设为小于焊盘部33c的平均厚度的情况下,作为焊盘部33c和多个第2伪配线35a的平均厚度的差,例如可以设为3μm以上12μm以下。该印刷配线板31通过将多个第2伪配线35a的平均厚度设为焊盘部33c的平均厚度以下,从而容易防止多个第2伪配线35a(更详细地,在与焊盘部33c离得最远的位置配置的第2伪配线35a)向绝缘层34的外表面侧露出。

[0150]

多个第2伪配线35a优选以相同间距进行配置。另外,优选焊盘部33c和与该焊盘部33c相邻的第2伪配线35a的间隔、及相邻的第2伪配线35a彼此的间隔是相同的。由此,实现绝缘层34的厚度的均匀化,容易防止焊盘部33c向绝缘层34的外表面侧露出。作为上述间距,可以设为与图1的印刷配线板1的相邻的配线3a间的平均间距相同。另外,作为焊盘部

33c和与该焊盘部33c相邻的第2伪配线35a的间隔、及相邻的第2伪配线35a彼此的间隔,可以设为与图1的印刷配线板1的相邻的配线3a间的平均间隔相同。

[0151]

(绝缘层)

[0152]

绝缘层34层叠于导电图案33、多个第2伪配线35a、以及基膜2的没有层叠导电图案33及多个第2伪配线35a的区域。绝缘层34主要防止因导电图案33与其他部件等接触引起的损伤及短路。因此,绝缘层34优选除了有意地设置的开口、切口以外将导电图案33的外表面全面地进行包覆。

[0153]

绝缘层34可以与图1的印刷配线板1相同地,由阻焊剂、覆盖层等构成,优选通过感光性干膜的固化而形成。作为在焊盘部33c的与基膜2相反侧的面层叠的绝缘层34的平均厚度,可以设为与在图1的印刷配线板1的多个配线3a的与基膜2相反侧的面层叠的绝缘层4的平均厚度相同。

[0154]

如上所述,绝缘层34具有在俯视观察时与导电图案33的形成区域重叠的第1区域34a、和在俯视观察时不与导电图案33的形成区域重叠的第2区域34b。绝缘层34的除了第1区域34a以外的区域作为第2区域34b而构成。另外,在俯视观察时第1区域34a的外缘与导电图案33的形成区域的外缘一致。在第1区域34a及第2区域34b的边界面x,焊盘部33c除了有意的开口及切口以外在绝缘层34的外表面侧不露出。

[0155]

倾斜部34c将与第1区域34a的边界面x作为端缘而形成于第2区域34b。对于倾斜部34c,在与边界面x垂直的厚度方向剖面,将与第1区域34a的边界面x的位置设为顶部34e,在第2区域34b侧厚度逐渐减小。在本实施方式,倾斜部34c的底部34f例如形成于焊盘部33c及与焊盘部33c相邻的伪引线35a的中间位置。

[0156]

在与第1区域34a及第2区域34b的边界面x垂直的厚度方向剖面,作为由(h1-h2)/w表示的厚度的变化率的平均值,可以设为与图1的印刷配线板1相同。

[0157]

<印刷配线板的制造方法>

[0158]

接着,对图11的印刷配线板31的制造方法的一个例子进行说明。该印刷配线板的制造方法具有:第1层叠工序,其在具有绝缘性的基膜2对包含平行地配置的多个配线的导电图案33进行层叠;以及第2层叠工序,在上述第1层叠工序之后,在基膜2及导电图案33对绝缘层34进行层叠。在该印刷配线板的制造方法,绝缘层34具有在俯视观察时与导电图案33的形成区域重叠的第1区域34a、和在俯视观察时不与导电图案33的形成区域重叠的第2区域34b,第2区域34b具有从第1区域34a连续而从基膜2表面起的厚度逐渐减小的倾斜部34c。

[0159]

(第1层叠工序)

[0160]

上述第1层叠工序在基膜2的表面对多个第2伪配线35a和具有焊盘部33c的导电图案33同时进行层叠。在上述第1层叠工序,将多个第2伪配线35a以与焊盘部33c电绝缘状态且将焊盘部33c包围的方式进行层叠。上述第1层叠工序具有如下工序:通过半加成法对焊盘部33c的芯体33d及多个第2伪配线35a的芯体进行层叠;在焊盘部33c的芯体33d形成贯通孔;以及对上述贯通孔实施镀敷、及根据需要对多个第2伪配线35a的芯体实施镀敷。

[0161]

(第2层叠工序)

[0162]

在上述第2层叠工序,将绝缘层34通过感光性干膜的固化而层叠。在上述第2层叠工序,与图4的印刷配线板的制造方法相同地层叠绝缘层34。该印刷配线板的制造方法在使

用感光性干膜对绝缘层34进行层叠时,能够容易地对熔融的感光性干膜从焊盘部33c侧向第2区域34b侧的流动进行拦截,防止焊盘部33c向绝缘层33的外表面侧露出。

[0163]

在上述第2层叠工序,在与第1区域34a及第2区域34b的边界面x垂直的厚度方向剖面,在将从倾斜部34c的顶部34e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部34c的底部34f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部34e及底部34f间的基膜2的平面方向距离设为w的情况下,将由(h1-h2)/w表示的厚度的变化率的平均值控制于0.01以上1.0以下。作为上述变化率的优选的下限值及优选的上限值,与图4的印刷配线板的制造方法相同。

[0164]

[第五实施方式]

[0165]

<印刷配线板>

[0166]

图14~图16的印刷配线板41具有:基膜2,其具有绝缘性;导电图案43,其层叠于基膜2,包含平行地配置的多个配线43a;以及绝缘层44,其层叠于基膜2及导电图案43。导电图案43具有连接配线43b,该连接配线43b以t字状连接于多个配线43a中的至少1个配线43a的端部。连接配线43b沿该印刷配线板41的外缘而配置。绝缘层44具有在俯视观察时与导电图案43的形成区域重叠的第1区域44a、和在俯视观察时不与导电图案43的形成区域重叠的第2区域44b。第2区域44b具有从第1区域44a连续而从基膜2表面起的厚度逐渐减小的倾斜部44c。作为该印刷配线板41的基膜2,可以设为与图1的印刷配线板1的基膜2相同的结构,因此标注相同标号而省略说明。

[0167]

如图15所示,该印刷配线板41在配线43a及连接配线43b的连接部分c,连接配线43b的与连接于配线43a的一侧相反侧的侧缘(以下,还称为“第1侧缘43c”)和与该第1侧缘43c相对的侧缘(以下,还称为“第2侧缘43d”)之间的宽度w是均匀的。

[0168]

如图16所示,对于该印刷配线板41,在与第1区域44a及第2区域44b的边界面x垂直的厚度方向剖面,在将从倾斜部44c的顶部44e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部44c的底部44f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部44e及底部44f间的基膜2的平面方向距离设为w的情况下,由(h1-h2)/w表示的厚度的变化率的平均值为0.01以上1.0以下。

[0169]

对于该印刷配线板41,导电图案43具有以t字状连接于多个配线43a中的至少1个配线43a的端部的连接配线43b,在配线43a及连接配线43b的连接部分c处,连接配线43b的第1侧缘43c和与该第1侧缘43c相对的第2侧缘43d之间的宽度w是均匀的,由此能够抑制连接部分c的镀敷厚度变得大于其他部分的情况。其结果,该印刷配线板41如图16所示,能够抑制连接部分c的厚度变得大于其他部分的情况。由此,能够防止因连接部分c和基膜2表面之间的阶梯差引起连接部分c在绝缘层2的外表面侧露出的情况。

[0170]

(导电图案)

[0171]

导电图案43是由具有导电性的导体构成的层,包含平行地配置的多个配线43a、和以t字状连接于至少1个配线43a的端部的连接配线43b。多个配线43a与图1的印刷配线板1相同地,可以是晶种层及电镀层的层叠体,也可以是在由上述晶种层及电镀层的层叠体构成的芯体层叠了包覆层的结构。

[0172]

连接配线43b与图1的印刷配线板1相同地,可以是晶种层及电镀层的层叠体,也可以是在由上述晶种层及电镀层的层叠体构成的芯体层叠了包覆层的结构。连接配线43b在

具有与多个配线43a相同的层叠构造的情况下,容易实现与多个配线43a的厚度的均匀化。另外,在多个配线43b为在上述芯体层叠了包覆层的结构、与这些配线43b连接的连接配线43b为上述晶种层及电镀层的2层层叠体(即,没有层叠包覆层的结构)的情况下,容易减小连接配线43b的厚度而减小连接配线43b和基膜2表面之间的阶梯差。

[0173]

在本实施方式,连接配线43b对平行地配置的多个配线43a的端部间进行连接。如图15所示,连接配线43b具有均匀的宽度。连接配线43b具有如下结构,即,在与多个配线43a的连接部分c处在配线43a侧凹陷、且在相邻的配线43a间的区域处在与配线43a相反侧凸出的曲拱构造沿长度方向连续的结构。由此,连接配线43b和多个配线43a以y字状连接。连接配线43b设置为从第1侧缘43c向下的垂线与第1侧缘43c的另一侧的侧缘大致正交。这样,在配线43a及连接配线43b的连接部分c处,连接配线43b的第1侧缘43c和与该第1侧缘43c相对的第2侧缘43d之间的宽度w被确保得均匀。此外,“配线及连接配线的连接部分”是指在将配线向连接配线侧延长的情况下该配线和连接配线交叉的部分。

[0174]

(绝缘层)

[0175]

绝缘层44层叠于导电图案43、及基膜2的没有层叠导电图案43的区域。绝缘层44主要防止因导电图案43与其他部件等接触引起的损伤及短路。因此,绝缘层44优选除了有意地设置的开口、切口以外将导电图案43的外表面全面地进行包覆。

[0176]

绝缘层44可以与图1的印刷配线板1相同地,由阻焊剂、覆盖层等构成,优选通过感光性干膜的固化而形成。作为在多个配线43a的与基膜2相反侧的面层叠的绝缘层44的平均厚度,可以设为与在图1的印刷配线板1的多个配线3a的与基膜2相反侧的面层叠的绝缘层4的平均厚度相同。

[0177]

如上所述,绝缘层44具有在俯视观察时与导电图案43的形成区域重叠的第1区域44a、和在俯视观察时不与导电图案43的形成区域重叠的第2区域44b。绝缘层44的除了第1区域44a以外的区域作为第2区域44b而构成。另外,在俯视观察时,第1区域44a的外缘与导电图案43的形成区域的外缘一致。在第1区域44a及第2区域44b的边界面x,多个配线43a及连接配线43b除了有意的开口及切口以外在绝缘层44的外表面侧不露出。

[0178]

倾斜部44c将与第1区域44a的边界面x作为端缘而形成于第2区域44b。对于倾斜部44c,在与边界面x垂直的厚度方向剖面,将与第1区域44a的边界面x的位置设为顶部44e,在第2区域44b侧厚度逐渐减小。在本实施方式,倾斜部44c的底部44f位于该印刷配线板41的外缘。

[0179]

在与第1区域44a及第2区域44b的边界面x垂直的厚度方向剖面,作为由(h1-h2)/w表示的厚度的变化率的平均值,可以设为与图1的印刷配线板1相同。

[0180]

<印刷配线板的制造方法>

[0181]

接着,对图14的印刷配线板41的制造方法的一个例子进行说明。该印刷配线板的制造方法具有:第1层叠工序,在具有绝缘性的基膜2对包含平行地配置的多个配线43a的导电图案43进行层叠;以及第2层叠工序,在上述第1层叠工序之后,在基膜2及导电图案43对绝缘层44进行层叠。在该印刷配线板的制造方法,绝缘层44具有在俯视观察时与导电图案43的形成区域重叠的第1区域44a、和在俯视观察时不与导电图案43的形成区域重叠的第2区域44b,第2区域44b具有从第1区域44a连续而从基膜2表面起的厚度逐渐减小的倾斜部44c。

[0182]

(第1层叠工序)

[0183]

上述第1层叠工序在基膜2的表面对多个配线43a及以t字状连接于多个配线43a中的至少1个配线43a的端部的连接配线43b进行层叠。在上述第1层叠工序,在配线43a及连接配线43b的连接部分c处,以连接配线43b的与连接于配线43a的一侧相反侧的侧缘(第1侧缘43c)和与该第1侧缘43c相对的侧缘(第2侧缘43d)之间的宽度w均匀的方式对多个配线43a及连接配线43b进行层叠。上述第1层叠工序例如可以与图4的印刷配线板的制造方法的第1层叠工序相同地,使用半加成法而进行。

[0184]

(第2层叠工序)

[0185]

在上述第2层叠工序,通过感光性干膜的固化而层叠绝缘层44。在上述第2层叠工序,与图4的印刷配线板的制造方法相同地层叠绝缘层44。该印刷配线板的制造方法在上述第1层叠工序能够抑制配线43a及连接配线43b的连接部分c的隆起,因此当在上述第2层叠工序使用感光性干膜对绝缘层44进行层叠时,能够防止该隆起部分在绝缘层44的外表面侧露出的情况。

[0186]

在上述第2层叠工序,在与第1区域44a及第2区域44b的边界面x垂直的厚度方向剖面,在将从倾斜部44c的顶部44e至向下到基膜2表面的垂线的垂足的长度设为h1,将从倾斜部44c的底部44f至向下到基膜2表面的垂线的垂足的长度设为h2,将顶部44e及底部44f间的基膜2的平面方向距离设为w的情况下,将由(h1-h2)/w表示的厚度的变化率的平均值控制于0.01以上1.0以下。作为上述变化率的优选的下限值及优选的上限值,与图4的印刷配线板的制造方法相同。

[0187]

[其他实施方式]

[0188]

应当认为本次公开的实施方式在所有方面都是例示,并不是限制性的内容。本发明的范围并不限定于上述实施方式的结构,而是由权利要求书示出,意在包含与权利要求书等同的含义以及范围内的全部变更。

[0189]

例如,该印刷配线板可以将上述第一实施方式至第五实施方式的结构根据需要进行组合使用。另外,在上述第一实施方式及第二实施方式,对多个配线形成线圈图案的结构进行了说明,但多个配线的配置图案不限定于线圈图案。并且,该印刷配线板可以仅在基膜的一个面侧层叠导电图案及绝缘层,也可以在基膜的两面侧层叠导电图案及绝缘层。

[0190]

在上述各实施方式,作为多个配线的具体结构,对晶种层及电镀层的层叠体、或在该层叠体包覆了包覆层的结构进行了说明,但多个配线的具体的层构造不限定于上述实施方式所记载的结构。另外,上述晶种层及电镀层的结构也不受限定,例如电镀层可以是2层以上的层叠体。并且,上述焊盘部也并非一定是通孔焊盘。

[0191]

该印刷配线板可以在多个配线的宽度方向的外侧仅具有1个伪配线(第1伪配线)。另外,该印刷配线板也可以仅具有将焊盘部包围的1个伪配线(第2伪配线)。

[0192]

该印刷配线板也可以使多个配线中的在第2区域侧配置的1个或多个配线的厚度小于在第1区域的中心侧配置的1个配线的厚度。例如,该印刷配线板的多个配线也可以包含:1个第1配线,其具有第1厚度;以及1个或多个第2配线,其与该第1配线相比靠第2区域侧配置,具有小于第1厚度的第2厚度。

[0193]

该印刷配线板的制造方法也可以在上述第2层叠工序使用感光性干膜以外的材料对绝缘层进行层叠。例如,在上述第2层叠工序,也可以使用感光性干膜以外的树脂膜来形

成绝缘层。在上述第1层叠工序,也可以使用半加成法以外的方法在基膜对导电图案进行层叠。

[0194]

工业实用性

[0195]

如上所述,本发明的实施方式涉及的印刷配线板能够防止导电图案向绝缘层的外表面侧露出,因此适于防止导电图案的损伤及短路。

[0196]

标号的说明

[0197]

1、11、21、31、41 印刷配线板

[0198]

2 基膜

[0199]

3、13、23、33、43 导电图案

[0200]

3a、13a、33a、43a 配线

[0201]

3b、13b、33c 焊盘部

[0202]

4、14、24、34、44 绝缘层

[0203]

4a、14a、24a、34a、44a 第1区域

[0204]

4b、14b、24b、34b、44b 第2区域

[0205]

4c、14c、24c、34c、44c 倾斜部

[0206]

4e、14e、24e、34e、44e 顶部

[0207]

4f、14f、24f、34f、44f 底部

[0208]

5a 第1伪配线

[0209]

13c 第1配线

[0210]

13d 第2配线

[0211]

13e、33d 芯体

[0212]

13f 包覆层

[0213]

23a 镀敷引线

[0214]

25a 伪引线

[0215]

33b 通孔

[0216]

35a 第2伪配线

[0217]

43b 连接配线

[0218]

43c 第1侧缘

[0219]

43d 第2侧缘

[0220]

x 边界面

[0221]

c 连接部分

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1