用于制造具有改进的检测参数的背照式光学传感器的方法与流程

1.本发明总体上涉及用于制造背照式(bsi)光学传感器的方法,并且更具体地涉及用于制造具有改进的检测参数、例如减少的串扰和增强的光子检测效率(pde)的bsi光学传感器的方法。特别地,本发明提供了用于将bsi光学传感器的感测元件隔离并且可以向传感元件施加共用偏压的方法。

背景技术:

2.光学传感器已经达到了微型化和检测精度的水平,使得光学传感器被用在许多领域中。

3.例如,目前在自动驾驶系统、例如adas(高级驾驶员辅助系统)中使用光学传感器来提供距离测量。在这种类型的光学传感器中存在所谓的飞行时间(tof)装置,该飞行时间(tof)装置设计成通过对电磁波(例如激光脉冲)从目标物体返回所需的时间进行测量来检测目标物体的距离。tof装置采用灵敏度非常高的感测元件,这是因为该感测元件是单光子雪崩二极管(spad)。spad的主要部件是:在击穿电压以上运行的雪崩光电二极管(盖革模式);淬灭电阻;第一电极(阴极)和第二电极(阳极)。因为由光电二极管的空间电荷区域的碰撞电离导致的倍增过程,由入射光子在光电二极管区域(例如反向偏压的p-n结)中产生的偏压高于击穿电压(倍增区域)的电子空穴对可以触发雪崩。通过这种方式,响应于入射光子流而产生了宏观电流。

4.spad的使用不限于汽车市场,而是广泛地应用于其他市场、例如医疗市场中。已经采用spad阵列(经常被称为硅光电倍增器或sipm)来取代光子计数应用、例如正电子发射断层扫描(pet)技术中的光电倍增管(pmt)技术,以观察体内的代谢过程。spad技术在cmos技术中的实施进一步增强了sipm技术的优势,从而提供了在皮秒时间内的高动态范围光子计数。

5.再次参考汽车市场,lidar(光检测和测距)技术例如采用近红外(nir)光检测来对发射的激光脉冲的飞行时间进行测量。为了对nir波长范围敏感,spad阵列光学传感器在850nm至910nm范围内的电磁波谱中必须具有大于10%的光检测效率(pde)。使用传统的前照式(fsi)cmos光学传感器很难实现这一点,这是因为nir光子的穿透距离很深,nir光子在半导体基板(例如硅基板)中被吸收地很深,结果是产生的电子/空穴对有很少的机会被收集在雪崩光电二极管区域中。相反地,通过配置成使所有的感测元件接近背侧表面布置的背照式(bsi)cmos光学传感器可以实现上述要求,入射光子从该背侧表面撞击,并且因为这个原因,产生的电子/空穴对中的大部分电子/空穴对有更多的机会被收集在雪崩光电二极管区域中。

6.在spad阵列中产生的主要缺点是在相邻的感测元件之间的串扰。串扰可能由于一个感测元件中的寄生(spurious)雪崩而产生,该寄生雪崩由另一个感测元件中的雪崩导致,从而在没有光的情况下也产生寄生输出电流脉冲(暗电流)。为了对从一个spad传播至相邻的spad的光子的存在进行限制,从而限制触发第二雪崩的可能性、(串扰)以及因此限

制暗计数率(dcr),必须将单独的感测元件彼此隔离。可以使用不同的隔离结构。通常,隔离结构可以以从前面刻蚀到邻近于感测元件区域的基板中的沟槽形式形成。沟槽形成时,通常用介电材料来填充该沟槽。例如,根据美国专利9,741,759,沟槽隔离结构具有从半导体基板的背侧朝向前侧形成的深沟槽隔离(dti)结构的形式。根据同一美国专利,沟槽隔离结构填充有共形地(conformally)形成在沟槽内壁上的第一隔离材料和共形地形成为填充沟槽隔离结构的第二传导材料。此外,根据同一美国专利,沟槽隔离结构可以通过将电压施加装置连接至沟槽隔离结构来施加电压。通常,使用这种隔离方式会产生问题,因为沟槽隔离结构将感测元件彼此隔离,却使得不可能将所有感测元件连接至共用偏压。例如,在sipm的情况下,每个感测元件(spad)的阳极电极被连接至某个电位(例如地电位)以便在结上被反向偏压。当spad被彼此隔离时,不可能将spad的阳极电极连接至共用电位。克服这个问题的唯一方式是单独地对每个spad进行偏压,例如通过增加单个接触部将每个spad连接至同一电位来对每个spad进行偏压,但这将导致使用阵列布局的额外空间,从而降低填充因子,该填充因子限定为感测元件的感测面积与总面积的比率,并且因此降低光子检测效率(pde)。

7.因此,需要提供在不影响填充因子的情况下具有改进的特征参数、例如减少的串扰和改进的光子检测效率(pde)的bsi光学传感器。

技术实现要素:

8.因此,本发明的总目的是克服当试图通过实施光学隔离结构来减少串扰时产生的上述技术问题,该光学隔离结构将光学传感器的感测元件彼此隔离,从而禁止每个敏感元件被连接至共用的偏压。

9.此外,本发明的具体目的是提供用于制造具有改进的检测参数的背照式(bsi)cmos光学传感器的方法,所述方法包括在保持所有的感测元件连接至共用偏压时在相邻的感测元件之间形成隔离结构的步骤。

10.通过本发明实现了这些和其他目的,因为本发明涉及如在所附权利要求中限定的制造光学传感器的方法。

11.根据本发明的第一实施方式,制造背照式(bsi)cmos光学传感器的方法包括以下步骤:围绕像素阵列的每个感测元件以沟槽网格结构的形式形成隔离结构,该隔离结构包括从光学传感器的前侧表面形成的第一隔离结构(例如浅沟槽隔离(sti)结构或locos隔离结构或注入区域)和深沟槽隔离(dti)结构,该深沟槽隔离(dti)结构在已从背侧将硅基板减薄之后从光学传感器背侧表面刻蚀并且到达前侧第一隔离结构的相应的底部表面;使用第一绝缘材料和适于减少串扰的第二不透明材料(例如金属)来填充背侧dti结构;从背侧对光学传感器的背侧表面进行平面化,从而将与每个感测元件相对应的硅表面暴露;在背侧表面上沉积附加的低电阻率层,从而将暴露的硅表面连接并且提供施加至像素阵列的所有感测元件的共用的电压施加结构。优选地,附加的低电阻率层包括非晶体硅材料,该非晶体硅材料具有对uv和可见光进行过滤的优点,从而允许仅nir光被检测到。根据本发明的第二实施方式,制造背照式(bsi)cmos光学传感器的方法包括以下步骤:围绕像素阵列的每个感测元件以交错的沟槽排的形式形成隔离结构,每个沟槽排包括被填充有硅基板的间隙间隔开的沟槽部分,该沟槽部分相对于属于平行的沟槽排中的沟槽部分是交错布置的;所述隔离结构包括从光学传感器的前侧表面形成的第一隔离结构(例如浅沟槽隔离(sti)结构

或locos隔离结构或注入区域)和第二深沟槽隔离(dti)结构,该深沟槽隔离(dti)结构从光学传感器被减薄的背侧表面刻蚀并且到达前侧第一隔离结构的相应的底部表面;用适于减少串扰的不透明材料来填充背侧dti结构;对光学传感器的背侧表面进行平面化,从而将与每个感测元件相对应的以及与硅间隙相对应的硅背侧表面暴露,所述暴露的硅背侧表面提供施加至像素阵列的所有感测元件的共用的电压施加结构。

附图说明

12.为更好地理解本发明,现在将参考附图(未按比例)对优选实施方式进行描述,优选实施方式仅以示例的方式示出而不应被理解为限制性的,在附图中:

13.·

图1示出了已知半导体光学传感器的像素阵列的示意图,其中,感测元件以并联的方式连接至共用偏压;

14.·

图2示出了已知半导体光学传感器的像素阵列的示意图,其中,感测元件由隔离结构(实心条)分开;

15.·

图3示出了已知半导体光学传感器的像素阵列的示意图,其中,感测元件由隔离结构(实心条)分开并且通过包括在每个感测元件中的单个接触部而连接至共用偏压;

16.·

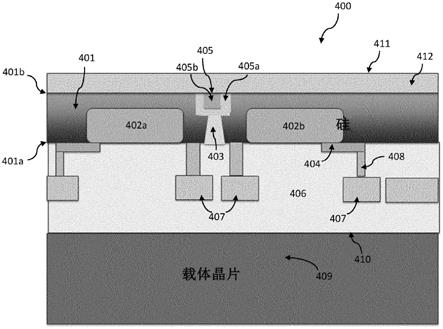

图4示出了根据第一实施方式的使用要求保护的方法获得的半导体bsi光学传感器的横截面视图;

17.·

图5示出了对根据第一实施方式制造半导体bsi光学传感器的方法进行说明的流程图;

18.·

图6示出了根据第二实施方式的使用要求保护的方法获得的半导体bsi光学传感器的俯视图和横截面视图;

19.·

图7示出了对根据第二实施方式制造半导体bsi光学传感器的方法进行说明的流程图。

具体实施方式

20.提出以下讨论以使本领域技术人员能够制造和使用本发明。在不脱离本发明所要求保护的范围的情况下,对各实施方式的各种修改对于本领域技术人员来说是明显的。因此,本发明并非意在被限制于所示和所描述的实施方式,而是被给予与本文中公开的和所附权利要求中限定的原理和特征一致的最宽范围。

21.如将在下文中详细讨论的,本发明的方面提供制造bsi光学传感器的方法,该bsi光学传感器构造成使像素阵列(例如sipm)的所有感测元件(例如spad)通过隔离结构而被间隔开从而减少串扰,所述单个元件以不影响填充因子的方式连接至从光学传感器背侧提供的共用电压施加结构。

22.图1至图3示意性地示出了光学传感器的3种不同的像素阵列,所述3种不同的像素阵列包括根据已知的布局而设计的多个感测元件。

23.例如,图1中所描绘的示意图示出了在cmos技术中实现的光学传感器的像素阵列100,该像素阵列100包括多个感测元件110(例如spad),所述多个感测元件110以二维矩阵的方式布置并且具有连接至电位v1的第一电极(110a)以及连接至共用的电位节点v2(115)的第二电极(110b)。特别地,每个感测元件构造成包括光电二极管有源区(110c),该光电二

极管有源区(110c)以其最简单的形式在p-n(或n-p)反向偏压结中实施成使得n(或p)区域消耗电荷载体(例如电子/空穴对),并且因此,入射光子产生了由光电二极管的消耗区域收集的电子/空穴对。p-n结被反向偏压成高于击穿电压,使得电子(以及空穴)在被收集前获得足够的能量以形成其他的对并启动雪崩过程,因此使由入射单光子所产生的信号被放大。使用淬灭电阻(quenching resistor)120来停止雪崩过程。通过这种方式,每个入射光子都可以被检测到,从而产生持续时间为几纳秒的强电流脉冲。在标准方法中,电位v1连续施加至每个第一电极,而电位v2(例如地电位)同时施加至所有的第二电极。因此,像素阵列的所有感测元件以并联的方式连接至共用的偏压v1-v2。

24.为了将spad彼此隔离以期减少串扰,标准方法是采用填充有传导材料(例如金属)或其他不传导材料的沟槽隔离结构(图2中的实心条)。如图2中所示,沟槽隔离结构的形成提供了光学隔离结构,但同时,沟槽隔离结构也将感测元件彼此电隔离,从而使得不可能将所有感测元件连接至共用电位v2。

25.图3中示出了用于克服该问题的标准方法。通过这种方法,附加的接触部310被添加至每个感测元件,从而将电位v2(例如地电位)持续施加至每个感测元件的每个第二电极。向每个感测元件添加接触部310需要使用像素阵列布局更多的硅空间,从而降低了填充因子并且因此降低了pde。

26.为克服上述问题,所提出的解决方案提供了制造根据第一实施方式和第二实施方式的bsi光学传感器的方法。

27.为更好地理解本发明,图4示出了根据所提出的方法的第一优选实施方式所获得的光学传感器的示例。特别地,图4是处于制造处理的特定步骤中的bsi光学传感器400的横截面视图,bsi光学传感器400包括:

28.·

前侧fs表面410和背侧bs表面411;

29.·

半导体基板(例如硅基板)401,该半导体基板401具有面向彼此的第一表面401a和第二表面401b;

30.·

至少第一感测元件402a和第二感测元件402b,所述至少第一感测元件402a和第二感测元件402b形成在所述半导体基板401中并由前侧隔离结构(例如浅沟槽隔离(sti)结构)403间隔开;

31.·

前侧电压施加装置404,该前侧电压施加装置404从所述半导体基板的fs表面401a电连接至所述至少第一感测元件或第二感测元件;

32.·

形成为多层的绝缘层406,该绝缘层406包括至少第一互连层407和金属接触部408;

33.·

载体半导体基板409,该载体半导体基板409附接至所述光学传感器的前侧表面410;

34.·

背侧深沟槽隔离(dti)结构405,该背侧深沟槽隔离(dti)结构405围绕至少第一感测元件和第二感测元件、从所述bs表面401b刻蚀并到达fs隔离结构403的底侧,所述bs dti结构填充有将沟槽侧壁和底部覆盖的第一绝缘材料405a(例如氧化硅)和将所述bs dti结构内部填充的第二传导材料405b(例如钨);

35.·

附加的低电阻率层412(例如非晶硅层),该低电阻率层412沉积在bs表面401b上并且从半导体第二表面将至少第一感测元件402a和第二感测元件402b连接。

36.根据本发明的第一优选实施方式,bsi光学传感器400是根据在图5的流程图a中所示的制作处理步骤来制造的。根据该优选的实施方式,制作处理包括以下制造步骤:501)执行标准cmos前侧制造处理,该标准cmos前侧制造处理包括形成以多层隔离结构的形式布置的fs隔离结构(例如浅沟槽隔离结构(sti))、多个互连层和多个接触部/过孔结构的步骤;502)将载体晶片附接至所述多层隔离结构的前侧表面;503)从背侧表面将半导体基板部分地减薄;504)通过光刻/刻蚀处理步骤从背侧形成bsi深沟槽隔离(dti)结构,该bsi深沟槽隔离(dti)结构到达fs隔离结构的底侧处并且具有网格形式、围绕每个感测元件区域;505)沉积第一隔离层以将dti结构的沟槽侧壁和底壁覆盖,并沉积诸如钨、钨钛(ti/w)或铝之类的第二传导材料以将bsi dti结构的内部填充;506)对背侧表面进行平面化(例如通过化学机械抛光、cmp)以将背侧表面上的所有多余传导材料移除,并且通过沉积非晶硅层、对所述非晶硅层进行掺杂(例如通过注入)以及对所述非晶硅层进行退火(例如通过热激光退火、lta或微波退火或不影响下层的其他方法)以将非晶硅层转化为低电阻率层来形成低电阻率层。最终,在低电阻率层的顶部上可以施加适当的arc层,以改进近红外(nir)辐射的传输。

37.本发明的优点通过上述内容是清楚的。特别地,需要强调的是,通过上述方法,光学传感器像素阵列(例如spad阵列)的所有的所述至少第一感测元件和第二感测元件通过将低电阻率层与置于光学传感器的前侧(图4中未示出)中的一个或非常少的接触部进行接触而被连接至同一背侧电位(例如地电位)。使用非晶硅层作为附加的低电阻率材料也是有利的,因为非晶硅层在近红外(nir)检测的情况下有助于过滤uv/可见辐射。

38.根据本发明的第二实施方式,bsi深沟槽隔离(dti)结构以交错的沟槽排的形式制造,从而确保像素阵列的相邻感测元件之间的光学隔离,同时保持所述感测元件之间的电气连续性。为更好的理解,图6示出了根据所提出的方法的第二实施方式获得的bsi光学传感器的示例。特别地,图6的顶部部分表示bsi光学传感器600的俯视图,并且底部部分表示bsi光学传感器600的沿着图6的顶部部分中所显示的方向bb’截取的横截面视图。根据该第二实施方式获得的光学传感器包括:

39.·

前侧fs表面610和背侧bs表面611;

40.·

半导体基板601,该半导体基板601具有面向彼此的第一表面601a和第二表面601b;

41.·

至少第一感测元件602a和第二感测元件602b,所述至少第一感测元件602a和第二感测元件602b形成在所述半导体基板中并且由fs隔离结构(例如浅沟槽隔离(sti)结构)603间隔开;

42.·

前侧电压施加装置604,该前侧电压施加装置604从所述半导体基板的fs表面601a电连接至所述至少第一感测元件或第二感测元件;

43.·

形成为多层的绝缘层606,该绝缘层606包括至少第一互连层607和金属接触部608;

44.·

载体半导体基板609,该载体半导体基板609附接至所述光学传感器的前侧表面610;

45.·

背侧bs深沟槽隔离(dti)结构,该背侧bs深沟槽隔离(dti)结构围绕所述至少第一感测元件和第二感测元件、以交错的沟槽排605的形式形成、从所述背侧表面601b刻蚀并

到达fs隔离结构603的底侧,所述bs dti结构填充有第一绝缘材料605a(例如氧化硅)和第二传导材料605b(例如钨、钨钛或铝),第一绝缘材料605a将沟槽的侧壁和底部覆盖,第二传导材料605b将所述bs dti结构的内部填充。

46.根据本发明的第二实施方式,bsi光学传感器600是根据由图7中的流程图b所示的制造处理步骤来制造的。根据该方法,制造处理包括以下制造步骤:701)执行标准前侧制造处理,该标准前侧制造处理包括形成以多层隔离结构的形式布置的fs隔离结构(例如浅沟槽隔离结构(sti))、多个互连层和多个接触部/过孔结构的步骤;702)将载体晶片附接至所述多层隔离结构的前侧表面;703)从背侧硅表面将硅基板部分地移除;704)通过光刻/刻蚀处理步骤从背侧形成bsi深沟槽隔离(dti)结构,该bsi深沟槽隔离(dti)结构到达fs隔离结构的底侧处、具有被间隙间隔开的交错的沟槽排的形式、并且围绕每个感测元件区域;705)沉积第一隔离层以将dti结构的沟槽侧壁和底壁覆盖并且沉积诸如钨、钨钛或铝之类的第二传导材料以将bsi dti结构的内部填充;706)对背侧表面进行平面化(例如通过化学机械抛光,cmp)从而将背侧表面上的所有多余导电层移除。

47.本发明的优点通过上述内容是清楚的。特别地,需要强调的是,所提出的解决方案包括:以彼此平行延伸并围绕相邻感测元件的交错的沟槽排的形式构造背侧深沟槽隔离结构,所述交错的沟槽排包括被填充有硅基板的间隙间隔开的沟槽部分,从而通过这些硅间隙确保像素阵列(例如spad)的感测元件之间的电气连续性,并同时形成阻碍串扰的光学屏障。根据上述的方法,光电二极管区域中暴露的硅基板充当感测元件的第二电极,并且可以向每个第二电极(图7)施加共用电位。

48.最后,明显的是,可以对本发明进行多种修改和改变,所有这些修改和改变都落入如所附权利要求中限定的本发明的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1