半导体集成电路装置及半导体集成电路装置的制造方法与流程

1.本公开涉及一种包括采用了纳米片fet(场效应晶体管:field effect transistor)的标准单元(以下看情况也简称为单元)的半导体集成电路装置的版图构造及其制造方法。

背景技术:

2.标准单元方式是在半导体衬底上形成半导体集成电路的一种已知方法。标准单元方式指的是以下方式,即事先将具有特定逻辑功能的基本单元(例如反相器、锁存器、触发器、全加器等)作为标准单元准备好,然后将多个标准单元布置在半导体衬底上,再用布线将这些标准单元连接起来,这样来设计lsi芯片。

3.lsi的基本构成要素即晶体管通过缩小栅极长度(按比例缩小:scaling)而实现了集成度的提高、工作电压的降低以及工作速度的提高。但是,近年来,出现的问题是过度地按比例缩小会引起截止电流,截止电流又会引起功耗显著增大。为解决该问题,人们已开始积极对立体构造晶体管进行研究,即将晶体管构造从现有的平面型变为立体型。纳米片fet(纳米线fet)作为其中之一备受瞩目。

4.专利文献1公开了一种半导体集成电路装置的版图构造,其在采用了纳米片fet的标准单元中,布置有对电路的逻辑功能不做贡献的虚设焊盘。

5.专利文献1:国际公开第2018/025580号公报

技术实现要素:

[0006]-发明要解决的技术问题-[0007]

专利文献1中公开了一种形成纳米片fet的沟道部的纳米片以及与纳米片的两端相连且形成源极部或漏极部的焊盘。然而,在专利文献1中,并未对用于抑制形成在标准单元中的晶体管的性能偏差的版图构造及其制造方法进行详细研究。

[0008]

本公开的目的在于:提供一种半导体集成电路装置的版图构造及其制造方法,其用于在采用了纳米片fet的标准单元的版图构造中,抑制形成在标准单元中的晶体管的性能偏差。

[0009]-用以解决技术问题的技术方案-[0010]

第一方面的公开是一种半导体集成电路装置,包括第一标准单元和第二标准单元,所述第一标准单元和所述第二标准单元沿第一方向排列布置。所述第一标准单元包括第一栅极布线、第一虚设栅极布线、第一焊盘、第一纳米片以及第一虚设纳米片,所述第一虚设栅极布线形成为在所述第一栅极布线的、位于所述第一方向的所述第二标准单元侧与所述第一栅极布线相邻,所述第一焊盘设在所述第一栅极布线与所述第一虚设栅极布线之间,所述第一纳米片形成为与所述第一栅极布线在俯视时重合且与所述第一焊盘相连,所述第一虚设纳米片形成为与所述第一虚设栅极布线在俯视时重合且与所述第一焊盘相连。所述第二标准单元包括第二栅极布线、第二虚设栅极布线以及第二焊盘,所述第二虚设栅

极布线形成为在所述第二栅极布线的、位于所述第一方向的所述第一标准单元侧与所述第二栅极布线相邻且形成为与所述第一虚设栅极布线相邻,所述第二焊盘设在所述第二栅极布线与所述第二虚设栅极布线之间。

[0011]

根据本公开,第一焊盘设在第一栅极布线与第一虚设栅极布线之间,该第一虚设栅极布线形成为在第一栅极布线的、位于第一方向的第二标准单元侧与第一栅极布线相邻。第一焊盘与第一纳米片和第一虚设纳米片相连,该第一纳米片形成为与第一栅极布线在俯视时重合,该第一虚设纳米片形成为与第一虚设栅极布线在俯视时重合。

[0012]

即,第一焊盘形成在作为沟道部发挥作用的第一纳米片与不作为沟道部发挥作用的第一虚设纳米片之间。因此,第一焊盘通过使形成第一纳米片和第一虚设纳米片的层叠半导体部外延生长而形成。这样一来,第一焊盘与下述焊盘以相同方式形成,该焊盘形成在作为沟道部发挥作用的纳米片彼此之间。因此,因为能够抑制晶体管的制造精度的偏差和晶体管的性能偏差,所以能够提高半导体集成电路装置的可靠性和成品率。

[0013]

第二方面的公开是一种半导体集成电路装置,包括第一标准单元和第二标准单元,所述第一标准单元和所述第二标准单元沿第一方向相邻布置。在所述第一标准单元与所述第二标准单元的单元交界,形成有第一虚设栅极布线。所述第一标准单元包括第一栅极布线、第一焊盘、第一纳米片以及第一虚设纳米片,所述第一栅极布线形成为沿所述第一方向与所述第一虚设栅极布线相邻,所述第一焊盘设在所述第一虚设栅极布线与所述第一栅极布线之间,所述第一纳米片形成为与所述第一栅极布线在俯视时重合且与所述第一焊盘相连,所述第一虚设纳米片形成为与所述第一虚设栅极布线在俯视时重合且与所述第一焊盘相连。所述第二标准单元包括第二栅极布线、第二焊盘、第二纳米片以及第二虚设纳米片,所述第二栅极布线形成为沿所述第一方向与所述第一虚设栅极布线相邻,所述第二焊盘设在所述第一虚设栅极布线与所述第二栅极布线之间,所述第二纳米片形成为与所述第二栅极布线在俯视时重合且与所述第二焊盘相连,所述第二虚设纳米片形成为与所述第一虚设栅极布线在俯视时重合且与所述第二焊盘相连且形成为与所述第一虚设纳米片分开。

[0014]

根据本公开,在沿第一方向相邻布置的第一标准单元与第二标准单元的单元交界,形成有第一虚设栅极布线。第一焊盘设在第一虚设栅极布线与第一栅极布线之间,该第一栅极布线形成为沿第一方向与第一虚设栅极布线相邻。第一焊盘与第一纳米片和第一虚设纳米片相连,该第一纳米片形成为与第一栅极布线在俯视时重合,该第一虚设纳米片形成为与第一虚设栅极布线在俯视时重合。第二焊盘设在第一虚设栅极布线与第二栅极布线之间,该第二栅极布线形成为沿第一方向与第一虚设栅极布线相邻。第二焊盘与第二纳米片和第二虚设纳米片相连,该第二纳米片形成为与第二栅极布线在俯视时重合,该第二虚设纳米片形成为与第一虚设栅极布线在俯视时重合且形成为与第一虚设纳米片分开。

[0015]

即,第一焊盘形成在作为沟道部发挥作用的第一纳米片与不作为沟道部发挥作用的第一虚设纳米片之间。第二焊盘形成在作为沟道部发挥作用的第二纳米片与和第一虚设纳米片分开且不作为沟道部发挥作用的第二虚设纳米片之间。因此,第一焊盘通过使形成第一纳米片和第一虚设纳米片的层叠半导体部外延生长而形成。第二焊盘通过使形成第二纳米片和第二虚设纳米片的层叠半导体部外延生长而形成。这样一来,第一焊盘和第二焊盘分别与下述焊盘以相同方式形成,该焊盘形成在作为沟道部发挥作用的纳米片彼此之间。因此,因为能够抑制晶体管的制造精度的偏差和晶体管的性能偏差,所以能够提高半导

体集成电路装置的可靠性和成品率。

[0016]

因为第一标准单元和第二标准单元沿第一方向相邻布置,所以能够实现半导体集成电路装置的小面积化。

[0017]

第三方面的公开是一种半导体集成电路装置的制造方法,所述半导体集成电路装置包括第一标准单元和第二标准单元,所述第一标准单元和所述第二标准单元沿第一方向相邻布置,所述半导体集成电路装置的制造方法包括以下步骤:在半导体衬底上交替层叠互不相同的两种半导体,形成层叠半导体;在所述层叠半导体的上部,在所述第一标准单元与所述第二标准单元的单元交界的位置形成第一牺牲栅极构造体,在所述第一标准单元的形成位置形成第二牺牲栅极构造体,在所述第二标准单元的形成位置形成第三牺牲栅极构造体;除去俯视时形成在所述第一牺牲栅极构造体与所述第二牺牲栅极构造体之间以及所述第一牺牲栅极构造体与所述第三牺牲栅极构造体之间的所述层叠半导体,由此分别在所述第一牺牲栅极构造体、所述第二牺牲栅极构造体以及所述第三牺牲栅极构造体的下部形成第一层叠半导体部、第二层叠半导体部以及第三层叠半导体部;通过使所述第一层叠半导体部和所述第二层叠半导体部外延生长,在所述第一层叠半导体部与所述第二层叠半导体部之间形成第一焊盘,通过使所述第一层叠半导体部和所述第三层叠半导体部外延生长,在所述第一层叠半导体部与所述第三层叠半导体部之间形成第二焊盘;除去所述第一牺牲栅极构造体、所述第二牺牲栅极构造体以及所述第三牺牲栅极构造体;除去所述第二层叠半导体部的一部分或全部,以免所述第一焊盘与所述第二焊盘通过所述第二层叠半导体部电连接。

[0018]

根据本公开,第一层叠半导体部和第二层叠半导体部形成为沿第一方向相邻。第一层叠半导体部和第三层叠半导体部形成为沿第一方向相邻。第一焊盘通过使第一层叠半导体部和第二层叠半导体部外延生长而形成。第二焊盘通过使第一层叠半导体部的侧面和第三层叠半导体部外延生长而形成。并且,除去第一层叠半导体部的一部分或全部,以免第一焊盘与第二焊盘电连接。

[0019]

即,第一焊盘和第二焊盘分别通过使形成为沿第一方向相邻的层叠半导体部外延生长而形成。因此,第一焊盘和第二焊盘与下述焊盘以相同方式形成,该焊盘形成在包括作为沟道部发挥作用的半导体层的层叠半导体部之间。因此,因为能够抑制晶体管的制造精度的偏差和晶体管的性能偏差,所以能够提高半导体集成电路装置的可靠性和成品率。

[0020]-发明的效果-[0021]

根据本公开,能够实现一种版图构造及其制造方法,其用于在采用了纳米片fet的标准单元的版图构造中,抑制形成在标准单元中的晶体管的性能偏差。

附图说明

[0022]

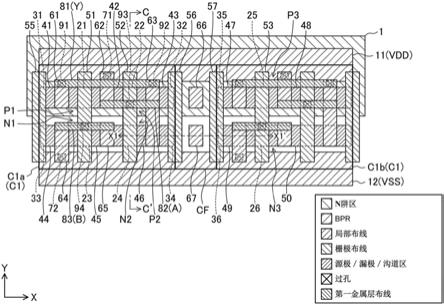

图1是示出第一实施方式所涉及的半导体集成电路装置的版图构造之例的俯视图;

[0023]

图2是示出第一实施方式所涉及的标准单元的版图构造之例的剖视图;

[0024]

图3是图1所示的标准单元c1的电路图;

[0025]

图4是用于说明第一实施方式所涉及的半导体集成电路装置的制造方法的图;

[0026]

图5是用于说明第一实施方式所涉及的半导体集成电路装置的制造方法的图;

[0027]

图6是用于说明第一实施方式所涉及的半导体集成电路装置的制造方法的图;

[0028]

图7是用于说明第一实施方式所涉及的半导体集成电路装置的制造方法的图;

[0029]

图8是示出第一实施方式所涉及的标准单元的版图构造的另一例的俯视图;

[0030]

图9是示出第二实施方式所涉及的半导体集成电路装置的版图构造之例的俯视图;

[0031]

图10是用于说明第二实施方式所涉及的半导体集成电路装置的制造方法的图;

[0032]

图11是用于说明第二实施方式所涉及的半导体集成电路装置的制造方法的图;

[0033]

图12是用于说明第二实施方式所涉及的半导体集成电路装置的制造方法的图;

[0034]

图13是用于说明第二实施方式所涉及的半导体集成电路装置的制造方法的图。

具体实施方式

[0035]

下面参照附图对实施方式进行说明。在以下实施方式中,半导体集成电路装置包括多个标准单元(在本说明书中,看情况简称为单元),该多个标准单元中至少一部分标准单元包括纳米片fet(field effect transistor)。

[0036]

在本说明书中,将形成在纳米片的两端且构成成为晶体管的源极或漏极的端子的半导体层部称为“焊盘”。

[0037]

在之后的实施方式的俯视图和剖视图中,有时会省略各绝缘膜等的图示。在之后的实施方式的俯视图和剖视图中,有时用简化的直线状形状示出纳米片及其两侧的焊盘。在本说明书中,像“同一尺寸”等意为尺寸等相同的表述包括制造上的偏差范围。

[0038]

在本说明书中,看情况将晶体管的源极和漏极称为晶体管的“节点”。即,晶体管的一节点是指晶体管的源极或漏极,晶体管的两个节点是指晶体管的源极和漏极。

[0039]

在以下实施方式中,“vdd”、“vss”用于表示电压或电源本身。

[0040]

在以下实施方式及其变形例中,有时用相同的符号表示相同的部件等并省略其说明。

[0041]

(第一实施方式)

[0042]

图1和图2是示出第一实施方式所涉及的半导体集成电路装置的版图构造之例的图,图1是俯视图,图2是俯视纵向剖视图。具体而言,图2是沿图1所示的c-c’线剖开的剖面。

[0043]

需要说明的是,在下述说明中,在图1等俯视图中,将附图横向设为x方向,将附图纵向设为y方向,将与衬底面垂直的方向设为z方向。在图1等俯视图中,以包围单元的方式表示的实线示出单元框(标准单元c1和填充单元cf的外缘)。

[0044]

在图1中,多个标准单元沿x方向排列布置,而构成单元列。具体而言,在标准单元c1彼此之间布置有填充单元cf。需要说明的是,有时将布置在附图左侧的标准单元c1称为标准单元c1a,将布置在附图右侧的标准单元c1称为标准单元c1b。

[0045]

标准单元c1包括纳米片fet,且具有逻辑功能(二输入“与非”电路)。填充单元cf不包括纳米片fet,且不具有逻辑功能。

[0046]

在本公开中,将像标准单元c1那样,在单元中具有“与非”门、“或非”门等逻辑功能的单元看情况称为“逻辑单元”。将像填充单元cf那样,由于不具有逻辑功能而对电路块的逻辑功能不做贡献且布置在逻辑单元之间的单元看情况称为“填充单元”。

[0047]

在本公开中,标准单元c1等中包括作为晶体管的沟道部发挥作用的纳米片和不作

为晶体管的沟道部发挥作用的纳米片。尤其是将不作为晶体管的沟道部发挥作用的纳米片称为“虚设纳米片”。

[0048]

在本公开中,标准单元c1等中包括形成晶体管的栅极布线和不形成晶体管的栅极布线。尤其是将不形成晶体管的栅极布线称为“虚设栅极布线”。

[0049]

如图1和图2所示,在标准单元c1和填充单元cf中,从y方向的中央部到附图上端,形成有沿x方向和y方向扩大的n阱区1。在标准单元c1和填充单元cf中,在y方向两端,分别设有沿x方向延伸的电源布线11、12。电源布线11、12均为形成在埋入式布线层中的埋入式电源布线(bpr:buried power rail)。电源布线11形成在n阱区1,且供给电源电压vdd。电源布线12供给电源电压vss。

[0050]

图3是图1所示的标准单元c1的电路图。如图3所示,在标准单元c1中,具有晶体管p1、p2、n1、n2,且构成有输入a、b、输出y的二输入“与非”电路。

[0051]

(标准单元c1的构成)

[0052]

下面举出标准单元cla为例说明标准单元c1的构成。需要说明的是,在图1中,标准单元c1b的纳米片25、26、虚设纳米片35、36、焊盘47~50、栅极布线53、虚设栅极布线57以及晶体管p3、n3分别相当于标准单元c1(c1a)的纳米片21、23、虚设纳米片31、33、焊盘41、42、44、45、栅极布线51、虚设栅极布线55以及晶体管p1、n1。

[0053]

在标准单元c1中,在电源布线11、12的上层,形成有沿x方向和y方向扩展的片状纳米片21~24和片状虚设纳米片31~34。纳米片21、22和虚设纳米片31、32沿x方向排列而成。纳米片23、24和虚设纳米片33、34沿x方向排列而成。

[0054]

纳米片21、23与栅极布线51在俯视时重合。纳米片22、24与栅极布线52在俯视时重合。虚设纳米片31、33与虚设栅极布线55在俯视时重合。虚设纳米片32、34与虚设栅极布线56在俯视时重合。

[0055]

虚设纳米片31、33分别从虚设栅极布线55的附图右端延伸至虚设栅极布线55的附图中央部(标准单元c1的附图左侧的单元框附近)。虚设纳米片32、34分别从虚设栅极布线56的附图左端延伸至虚设栅极布线56的附图中央部(标准单元c1的附图右侧的单元框附近)。

[0056]

在虚设纳米片31与纳米片21之间、纳米片21、22之间、纳米片22与虚设纳米片32之间,分别形成有p型半导体掺杂而成的焊盘41~43。在虚设纳米片33与纳米片23之间、纳米片23、24之间、纳米片24与虚设纳米片34之间,分别形成有n型半导体掺杂而成的焊盘44~46。

[0057]

纳米片21~24分别构成晶体管p1、p2、n1、n2的沟道部。焊盘41、42构成晶体管p1的节点。焊盘42、43构成晶体管p2的节点。焊盘44、45构成晶体管n1的节点。焊盘45、46构成晶体管n2的节点。

[0058]

在标准单元c1中,形成有沿y方向和z方向延伸的栅极布线51、52和虚设栅极布线55、56。虚设栅极布线55、56分别布置在标准单元c1的x方向两端。虚设栅极布线55、栅极布线51、52以及虚设栅极布线56沿x方向以相等的中心间距布置。栅极布线51形成晶体管p1、n1的栅极,栅极布线52形成晶体管p2、n2的栅极。

[0059]

即,由纳米片21、焊盘41、42以及栅极布线51构成晶体管p1。由纳米片22、焊盘42、43以及栅极布线52构成晶体管p2。由纳米片23、焊盘44、45以及栅极布线51构成晶体管n1。

由纳米片24、焊盘45、46以及栅极布线52构成晶体管n2。

[0060]

如图2所示,纳米片22、24分别由两片片状半导体层(纳米片)构成。就各纳米片22、24而言,两片纳米片布置为俯视时重合,且沿z方向分开。纳米片21、23和虚设纳米片31~34采用与纳米片22、24相同的构造,省略图示。即,晶体管p1、p2、n1、n2分别包括两片纳米片。

[0061]

如图1所示,在焊盘41~46的上层,形成有沿y方向延伸的局部布线61~65。局部布线61与焊盘41相连。局部布线62与焊盘42相连。局部布线63与焊盘43、46相连。局部布线64与焊盘44相连。局部布线65与焊盘45相连。

[0062]

局部布线62延伸至与电源布线11在俯视时重合的位置,且通过接触孔71与电源布线11相连。局部布线64延伸至与电源布线12在俯视时重合的位置,且通过接触孔72与电源布线12相连。

[0063]

在局部布线61~65的上层的第一金属布线层中,形成有沿x方向延伸的布线81~83。布线81通过接触孔91与局部布线61相连,且通过接触孔92与局部布线63相连。布线82通过接触孔93与栅极布线52相连。布线83通过接触孔94与栅极布线51相连。需要说明的是,布线81~83分别相当于图3中的输出y和输入a、b。

[0064]

如上所述,纳米片21~24分别作为晶体管p1、p2、n1、n2的沟道部发挥作用。另一方面,虚设纳米片31~34的一端分别与焊盘41、43、44、46相连,另一端不与焊盘相连。因此,虚设纳米片31~34均不作为晶体管的沟道部发挥作用。

[0065]

此处,焊盘42形成在纳米片21、22之间,焊盘45形成在纳米片23、24之间。另一方面,焊盘41形成在虚设纳米片31与纳米片21之间,焊盘43形成在纳米片22与虚设纳米片32之间,焊盘44形成在虚设纳米片33与纳米片23之间,焊盘46形成在纳米片24与虚设纳米片34之间。即,焊盘42、45形成在作为沟道部发挥作用的纳米片彼此之间。另一方面,焊盘41、43、44、46形成在作为沟道部发挥作用的纳米片与不作为沟道部发挥作用的虚设纳米片之间。因此,在标准单元c1中,包括形成在作为沟道部发挥作用的纳米片彼此之间的焊盘和形成在作为沟道部发挥作用的纳米片与不作为沟道部发挥作用的虚设纳米片之间的焊盘。

[0066]

需要说明的是,如上所述,标准单元c1b也以与标准单元c1a同样方式构成。即,晶体管p3由纳米片25、焊盘47、48以及栅极布线53构成。晶体管n3由纳米片26、焊盘49、50以及栅极布线53构成。焊盘47形成在作为晶体管p3的沟道部发挥作用的纳米片25与不作为晶体管的沟道部发挥作用的虚设纳米片35之间。焊盘49形成在作为晶体管n3的沟道部发挥作用的纳米片26与不作为晶体管的沟道部发挥作用的虚设纳米片36之间。

[0067]

(填充单元cf的构成)

[0068]

如图1所示,填充单元cf布置在标准单元c1a、c1b之间。

[0069]

在填充单元cf的x方向两端,形成有虚设栅极布线56、57。填充单元cf与标准单元c1a共用虚设栅极布线56,与标准单元c1b共用虚设栅极布线57。需要说明的是,在填充单元cf中,不包括标准单元c1a的虚设纳米片32、34和标准单元c1b的虚设纳米片35、36。

[0070]

在填充单元cf的x方向的中央部,形成有沿y方向延伸的局部布线66、67。局部布线66、67形成在与局部布线61~65相同的层。

[0071]

(关于第一实施方式所涉及的半导体集成电路装置的制造方法)

[0072]

下面参照图4~图7,说明半导体集成电路装置的制造方法。具体而言,图4~图7示出沿图1的x1-x1’线剖开的剖面。

[0073]

首先,如图4(a)所示,在半导体衬底100上,形成层叠半导体200。层叠半导体200通过使半导体层210和牺牲半导体层220交替层叠而形成。半导体层210和牺牲半导体层220采用互不相同的半导体材料。例如,半导体材料采用硅(si)、锗(ge)、硅锗合金(sige)、碳化硅(sic)、碳化硅锗(sigec)、iii-v化合物半导体或ii-vi化合物半导体等。

[0074]

此处,半导体层210的材料采用硅(si),牺牲半导体层220的材料采用硅锗合金(sige)。通过使硅(si)和硅锗合金(sige)在半导体衬底100上外延生长而交替层叠,由此能够实现层叠半导体200的层叠结构。外延生长通过快速热化学气相沉积(rtcvd:rapid thermal chemical vapor deposition)、低能量等离子体沉积(lepd:low-energy plasma deposition)、超高真空化学气相沉积(uhvcvd:ultra-high vacuum chemical vapor deposition)、常压化学气相沉积(apcvd:atmospheric pressure chemical vapor deposition)以及分子束外延(mbe:molecular beam epitaxy)等方法实现。

[0075]

然后,如图4(b)所示,对层叠半导体200进行图案成形。图案成形通过公知的光刻和蚀刻实现。这样一来,在附图左侧形成层叠半导体部201,在附图右侧形成层叠半导体部202。

[0076]

然后,如图5(a)所示,在半导体衬底100上和层叠半导体部201、202的上部,形成牺牲栅极构造体301~304。具体而言,牺牲栅极构造体301~304分别形成在图1的栅极布线52、虚设栅极布线56、57以及栅极布线53的形成位置。牺牲栅极构造体302、303形成为分别覆盖层叠半导体部201的附图右侧的侧面和层叠半导体部202的附图左侧的侧面。

[0077]

牺牲栅极构造体301~304例如采用多晶硅、非晶硅、金属(例如,钨、钛、钽、铝、镍、钌、钯以及铂)、以多种金属为材料的合金等作为材料。牺牲栅极构造体301~304可以是将上述材料形成层状而得到的构造物。可以在牺牲栅极构造体301~304的表面,使用氧化硅、氮化硅等绝缘材料形成间隔物。

[0078]

牺牲栅极构造体301~304例如通过化学气相沉积(cvd:chemical vapor deposition)、等离子体增强化学气相沉积(pecvd:plasma enhanced chemical vapor deposition)、物理气相沉积(pvd:physical vapor deposition)、溅射、原子层沉积(ald:atomic layer deposition)等方法成膜。并且,牺牲栅极构造体301~304通过公知的光刻和蚀刻形成在规定的位置。

[0079]

然后,如图5(b)所示,除去被牺牲栅极构造体301~304覆盖的部分以外的层叠半导体部201、202。具体而言,通过反应性离子蚀刻(rie:reactive ion etching)等各向异性蚀刻,除去被牺牲栅极构造体301~304覆盖的部分以外的层叠半导体部201、202。这样一来,就在半导体衬底100上形成分别被牺牲栅极构造体301~304覆盖的层叠半导体部203~206。需要说明的是,在下述说明中,将分别包括在层叠半导体部203~206中的半导体层设为半导体层213~216,将分别包括在层叠半导体部203~206中的牺牲半导体层设为牺牲半导体层223~226。

[0080]

此处,层叠半导体部203、206的附图左右两侧的侧面露出。另一方面,层叠半导体部204的附图左侧的侧面露出,附图右侧的侧面被牺牲栅极构造体302覆盖。层叠半导体部205的附图左侧的侧面被牺牲栅极构造体303覆盖,附图右侧的侧面露出。

[0081]

然后,如图6(a)所示,在半导体衬底100上形成作为间隔物的绝缘膜401。具体而言,绝缘膜401形成为覆盖未被牺牲栅极构造体301~304和层叠半导体部203~206覆盖的

半导体衬底100的上表面。绝缘膜401的材料例如采用氧化硅、氮化硅等。绝缘膜401能够通过公知的成膜和蚀刻形成。

[0082]

然后,如图6(b)所示,形成焊盘501~504。具体而言,通过使层叠半导体部203~206外延生长而形成焊盘501~504。需要说明的是,焊盘501~504分别相当于图1中的焊盘45、46、49、50。

[0083]

更具体而言,焊盘501以层叠半导体部203的露出部分(附图左侧的侧面)为基点形成在层叠半导体部203的附图左侧。焊盘502以层叠半导体部203的露出部分(附图右侧的侧面)和层叠半导体部204的露出部分(附图左侧的侧面)为基点形成在层叠半导体部203、204之间。焊盘503以层叠半导体部205的露出部分(附图右侧的侧面)和层叠半导体部206的露出部分(附图左侧的侧面)为基点形成在层叠半导体部205、206之间。焊盘504以层叠半导体部206的露出部分(附图右侧的侧面)为基点形成在层叠半导体部206的附图右侧。

[0084]

此处,因为层叠半导体部204的附图右侧的侧面和层叠半导体部205的附图左侧的侧面分别被牺牲栅极构造体302、303覆盖,所以在牺牲栅极构造体302、303之间不会形成焊盘。

[0085]

用于形成焊盘501~504而进行的外延生长采用添加有杂质的半导体材料。半导体材料例如采用硅。半导体材料中添加的杂质(半导体)如下:p型半导体例如采用硼、铝、镓以及铟等,n型半导体例如采用锑、砷以及磷等。

[0086]

并且,在焊盘501~504的上部,形成绝缘膜402。此外,在牺牲栅极构造体302、303之间形成绝缘膜403。绝缘膜402、403的材料例如采用二氧化硅、硅酸盐玻璃等。绝缘膜402、403通过化学气相沉积、等离子体增强化学气相沉积等方法形成。

[0087]

然后,如图7(a)所示,除去牺牲栅极构造体301~304和牺牲半导体层223~226。具体而言,通过公知的蚀刻除去牺牲栅极构造体301~304。并且,通过从层叠半导体部203~206分别选择性地除去(蚀刻)牺牲半导体层223~226,使半导体层213~216残留在半导体衬底100上。需要说明的是,半导体层213~216分别相当于图1和图2中的纳米片24、虚设纳米片34、36以及纳米片26。

[0088]

然后,如图7(b)所示,在牺牲栅极构造体301~304和牺牲半导体层223~226被除去的部分,形成栅极氧化膜601~604和栅极布线701~704。

[0089]

具体而言,栅极氧化膜601形成为覆盖绝缘膜402的侧面、焊盘501的附图右侧的侧面、焊盘502的附图左侧的侧面、半导体层213的表面(图7(b)中为半导体层213的上表面和下表面)以及半导体衬底100的上表面。栅极氧化膜602形成为覆盖绝缘膜402的侧面、焊盘502的附图右侧的侧面、绝缘膜403的附图左侧的侧面、半导体层214的表面(图7(b)中为半导体层214的上表面、下表面以及附图右侧的侧面)以及半导体衬底100的上表面。栅极氧化膜603形成为覆盖绝缘膜402的侧面、焊盘403的附图右侧的侧面、焊盘503的附图左侧的侧面、半导体层215的表面(图7(b)中为半导体层215的上表面、下表面以及附图左侧的侧面)以及半导体衬底100的上表面。栅极氧化膜604形成为覆盖绝缘膜402的侧面、焊盘503的附图右侧的侧面、焊盘504的附图左侧的侧面、半导体层216的表面(图7(b)中为半导体层216的上表面和下表面)以及半导体衬底100的上表面。

[0090]

栅极氧化膜601~604例如是氧化硅膜、氮化氧化硅膜、highk膜(使用介电常数比氧化硅高的材料形成的膜)。栅极氧化膜601~604例如通过化学气相沉积、等离子体化学气

相沉积、物理气相沉积、溅射、原子层沉积等方法成膜。

[0091]

并且,在半导体衬底100上,形成栅极布线701~704。具体而言,栅极布线701形成在焊盘501、502之间。栅极布线702形成在焊盘502与绝缘膜403之间。栅极布线703形成在绝缘膜403与焊盘503之间。栅极布线704形成在焊盘503、504之间。需要说明的是,栅极布线701~704分别相当于图1和图2的栅极布线52、虚设栅极布线56、57以及栅极布线53。

[0092]

栅极布线701~704由多晶硅、钨、钛、钽、铝、镍、钌、钯以及铂等金属、上述金属的合金等形成。栅极布线701~704例如通过化学气相沉积、等离子体增强化学气相沉积等方法形成。

[0093]

通过上述制造方法,形成相邻的标准单元cia、c1b与填充单元cf的交界附近的晶体管n2、n3。图7(b)之后,通过公知的技术,在晶体管的上层形成过孔和局部布线等布线,实现晶体管间的连接。

[0094]

根据上述构成,标准单元c1a、c1b沿x方向排列布置。标准单元c1a包括栅极布线52、虚设栅极布线56、焊盘46、纳米片24以及虚设纳米片34,虚设栅极布线56形成为在栅极布线52的、位于x方向的附图右侧(标准单元c1b侧)与栅极布线52相邻,焊盘46设在栅极布线52与虚设栅极布线56之间,纳米片24形成为与栅极布线52在俯视时重合且与焊盘46相连,虚设纳米片34形成为与虚设栅极布线56在俯视时重合且与焊盘46相连。标准单元c1b包括栅极布线53、虚设栅极布线57以及焊盘49,虚设栅极布线57形成为在栅极布线53的、位于x方向的附图左侧(标准单元c1a侧)与栅极布线53相邻且形成为与虚设栅极布线56相邻,焊盘49设在虚设栅极布线57与栅极布线53之间。

[0095]

在标准单元c1a的附图右端部,焊盘46形成在作为沟道部发挥作用的纳米片24与不作为沟道部发挥作用的虚设纳米片34之间。焊盘46通过使形成纳米片24和虚设纳米片34的层叠半导体部外延生长而形成。另一方面,形成在作为沟道部发挥作用的纳米片彼此之间的焊盘(例如,焊盘45等)通过从形成在x方向两侧的层叠半导体部外延生长而形成。即,形成在标准单元c1的x方向的端部(右端部)的焊盘和形成在作为沟道部发挥作用的纳米片彼此之间的焊盘都以同样方式形成。这样一来,能抑制上述焊盘的形状偏差。因此,因为能够抑制晶体管的制造精度的偏差和晶体管的性能偏差,所以能够提高半导体集成电路装置的可靠性和成品率。

[0096]

标准单元c1b包括纳米片26和虚设纳米片36,纳米片26形成为与栅极布线53在俯视时重合且与焊盘49相连,虚设纳米片36形成为与虚设栅极布线57在俯视时重合且与焊盘49相连。

[0097]

在标准单元c1b的附图左端部,焊盘49形成在作为沟道部发挥作用的纳米片26与不作为沟道部发挥作用的虚设纳米片36之间。焊盘49通过使形成纳米片26和虚设纳米片36的层叠半导体部外延生长而形成。另一方面,形成在作为沟道部发挥作用的纳米片彼此之间的焊盘(例如,焊盘50等)通过从形成在x方向两侧的层叠半导体部外延生长而形成。即,形成在标准单元c1的x方向的端部(左端部)的焊盘和形成在作为沟道部发挥作用的纳米片彼此之间的焊盘都以同样方式形成。这样一来,能抑制上述焊盘的形状偏差。因此,因为能够抑制晶体管的制造精度的偏差和晶体管的性能偏差,所以能够提高半导体集成电路装置的可靠性和成品率。

[0098]

需要说明的是,在填充单元cf中,也可以不形成局部布线66、67的一部分或全部。

[0099]

图8是示出第一实施方式所涉及的标准单元的版图构造的另一例的俯视图。具体而言,在标准单元c2中,与标准单元c1相比,在附图左端形成有沿x方向延伸的局部布线68a、69a,在附图右端形成有沿x方向延伸的局部布线68b、69b。局部布线68a、68b、69a、69b形成在与局部布线61~65相同的层。

[0100]

通过将图8的标准单元c2沿x方向相邻布置,形成与图1相同的半导体集成电路装置和相同的版图构造。具体而言,共用布置在左侧的标准单元c2的局部布线68b、69b和布置在右侧的标准单元c2的局部布线68a、69a。这样一来,能够得到相同的效果。

[0101]

(第二实施方式)

[0102]

图9是示出第二实施方式所涉及的半导体集成电路装置的版图构造之例的俯视图。在图9中,两个标准单元c3沿x方向相邻布置。与标准单元c1一样,在标准单元c3中,构成有二输入“与非”电路。有时将布置在附图左侧的标准单元c3称为标准单元c3a,将布置在附图右侧的标准单元c3称为标准单元c3b。标准单元c3b的纳米片25、26、虚设纳米片35a、36a、焊盘47~50、栅极布线53、虚设栅极布线56a以及晶体管p3、n3分别相当于标准单元c3(c3a)的纳米片21、23、虚设纳米片31a、33a、焊盘41、42、44、45、栅极布线51、虚设栅极布线55a以及晶体管p1、n1。

[0103]

具体而言,标准单元c3a与标准单元c3b共用形成在标准单元c3a的附图右端的虚设栅极布线56a。标准单元c3a与布置在标准单元c3a的附图左侧的标准单元共用形成在标准单元c3a的附图左端的虚设栅极布线55a,省略图示。

[0104]

在标准单元c3a中,在附图右端部形成有虚设纳米片32a、34a。虚设纳米片32a、34a分别与焊盘43、46相连。虚设纳米片32a、34a分别从虚设栅极布线56a的附图左端朝向附图右侧延伸。虚设纳米片32a、34a分别与虚设栅极布线56a在俯视时重合。

[0105]

在标准单元c3b中,在附图左端部形成有虚设纳米片35a、36a。虚设纳米片35a、36a分别与焊盘47、49相连。虚设纳米片35a、36a分别从虚设栅极布线56a的附图右端朝向附图左侧延伸。虚设纳米片35a、36a分别与虚设栅极布线56a在俯视时重合。

[0106]

虚设纳米片32a、35a沿x方向分开,以免彼此电连接。虚设纳米片34a、36a沿x方向分开,以免彼此电连接。

[0107]

在标准单元c3a中,在附图左端部,形成有虚设纳米片31a、33a。虚设纳米片31a、33a分别与焊盘41、44相连。虚设纳米片31a、33a分别从虚设栅极布线55a的附图右端朝向附图左侧延伸。虚设纳米片31a、33a分别与虚设栅极布线55a在俯视时重合。虚设纳米片31a、33a分别形成为不与以下虚设纳米片电连接,该虚设纳米片是与布置在标准单元c3a的附图左侧的标准单元的虚设栅极布线55a重合布置的虚设纳米片,省略图示。

[0108]

(关于第二实施方式所涉及的半导体集成电路装置的制造方法)

[0109]

下面参照图10~图13,说明半导体集成电路装置的制造方法。具体而言,图10~图13示出图9的沿x2-x2’线剖开的剖面。

[0110]

首先,如图10(a)所示,在半导体衬底100上,形成层叠半导体230。层叠半导体230通过使半导体层240和牺牲半导体层250交替层叠而形成。半导体层240和牺牲半导体层250采用互不相同的半导体材料。具体而言,半导体层240和牺牲半导体层250分别采用与半导体层210和牺牲半导体层220相同的材料。通过与图4(a)相同的方法,在半导体衬底100上形成层叠半导体230。

[0111]

需要说明的是,在图10(a)之后,对层叠半导体230进行图案成形,省略图示。图案成形通过公知的光刻和蚀刻实现。

[0112]

然后,如图10(b)所示,在层叠半导体230上,形成牺牲栅极构造体311~313。具体而言,牺牲栅极构造体311~313分别形成在图9的栅极布线52、虚设栅极布线56a以及栅极布线53的形成位置。牺牲栅极构造体311~313采用与牺牲栅极构造体301~304相同的材料。通过与图5(a)相同的方法,在层叠半导体230的规定的位置,形成牺牲栅极构造体311~313。

[0113]

然后,如图j1(a)所示,除去被牺牲栅极构造体311~313覆盖的部分以外的层叠半导体230。在图11(a)中,通过与图5(b)相同的方法,除去层叠半导体230。这样一来,就在半导体衬底100上形成分别被牺牲栅极构造体311~313覆盖的层叠半导体部231~233。

[0114]

此处,层叠半导体部231~233各自的附图左右两侧的侧面露出。需要说明的是,将分别包括在层叠半导体部231~233中的半导体层设为半导体层241~243。将分别包括在层叠半导体部231~233中的牺牲半导体层设为牺牲半导体层251~253。

[0115]

然后,如图11(b)所示,在半导体衬底100上形成作为间隔物的绝缘膜411。具体而言,绝缘膜411形成为覆盖未被牺牲栅极构造体311~313和层叠半导体部231~233覆盖的半导体衬底100的上表面。绝缘膜411由与绝缘膜401相同的材料形成。在图11(b)中,通过与图6(a)相同的方法,形成绝缘膜411。

[0116]

然后,如图12(a)所示,形成焊盘511~514。具体而言,通过使层叠半导体部231~233外延生长而形成焊盘511~514。在图12(a)中,使用与图6(b)相同的材料进行外延生长。需要说明的是,焊盘511~514分别相当于图9中的焊盘45、46、49、50。

[0117]

更具体而言,焊盘511以层叠半导体部231的露出部分(附图左侧的侧面)为基点形成在层叠半导体部231的附图左侧。焊盘512以层叠半导体部231的露出部分(附图右侧的侧面)和层叠半导体部232的露出部分(附图左侧的侧面)为基点形成在层叠半导体部231、232之间。焊盘513以层叠半导体部232的露出部分(附图右侧的侧面)和层叠半导体部233的露出部分(附图左侧的侧面)为基点形成在层叠半导体部232、233之间。焊盘514以层叠半导体部233的露出部分(附图右侧的侧面)为基点形成在层叠半导体部233的附图右侧。

[0118]

并且,在焊盘511~514的上部,形成绝缘膜412。绝缘膜412采用与绝缘膜402相同的材料。绝缘膜412通过与图6(b)相同的方法形成。

[0119]

然后,如图12(b)所示,除去牺牲栅极构造体311~313和层叠半导体部232的一部分。具体而言,通过公知的蚀刻除去牺牲栅极构造体311~313。然后,对层叠半导体部232的x方向中央部以外的部分进行掩膜处理,通过各向异性蚀刻除去层叠半导体部232的x方向中央部。

[0120]

此处,层叠半导体部232的中央部分被除去,以使左右两端部略微残留。需要说明的是,在下述说明中,在层叠半导体部232中,将附图左侧残留的部分(与焊盘512接触的部分)设为层叠半导体部234,将附图右侧残留的部分(与焊盘513接触的部分)设为层叠半导体部235。将分别包括在层叠半导体部234、235中的半导体层设为半导体层244、245,将分别包括在层叠半导体部234、235中的牺牲半导体层设为牺牲半导体层254、255。

[0121]

然后,如图13(a)所示,除去牺牲半导体层251、253~255。具体而言,通过从层叠半导体部231、233~235分别选择性地除去(蚀刻)牺牲半导体层251、253~255,使半导体层

241、243~245残留在半导体衬底100上。需要说明的是,半导体层241、243~245分别相当于图9中的纳米片24、26和虚设纳米片34a、36a。

[0122]

然后,如图13(b)所示,在层叠半导体部232的一部分、牺牲栅极构造体311~313以及牺牲半导体层251、253~255被除去的部分,形成栅极氧化膜611~613和栅极布线711~713。

[0123]

具体而言,栅极氧化膜611形成为覆盖绝缘膜412的侧面、焊盘511的附图右侧的侧面、焊盘512的附图左侧的侧面、半导体层241的表面(图13(b)中为半导体层241的上表面和下表面)以及半导体衬底100的上表面。栅极氧化膜612形成为覆盖绝缘膜412的侧面、焊盘512的附图右侧的侧面、焊盘513的附图左侧的侧面、半导体层244的表面(图13(b)中为半导体层244的上表面、下表面以及附图右侧的侧面)、半导体层245的上表面、下表面、附图左侧的侧面以及半导体衬底100的上表面。栅极氧化膜613形成为覆盖绝缘膜412的侧面、焊盘513的附图右侧的侧面、焊盘514的附图左侧的侧面、半导体层243的表面(图13(b)中为半导体层243的上表面和下表面)以及半导体衬底100的上表面。

[0124]

栅极氧化膜611~613采用与栅极氧化膜601~604相同的材料。在图13(b)中,通过与图7(b)相同的方法,形成栅极氧化膜611~613。

[0125]

并且,在半导体衬底100上,形成栅极布线711~713。具体而言,栅极布线711形成在焊盘511、512之间。栅极布线712形成在焊盘512、513之间。栅极布线713形成在焊盘513、514之间。栅极布线711~713采用与栅极布线701~704相同的材料。在图13(b)中,通过与图7(b)相同的方法,形成栅极布线711~713。需要说明的是,栅极布线711~713分别相当于图1和图2的栅极布线52、虚设栅极布线56a以及栅极布线53。

[0126]

通过上述制造方法,形成相邻的标准单元c3a、c3b的交界附近的晶体管n2、n3。在图13(b)之后,通过公知的技术,在晶体管的上层形成过孔和局部布线等布线,实现晶体管间的连接。

[0127]

根据上述构成,标准单元c3a、c3b沿x方向相邻布置。在标准单元c3a、c3b的单元交界,形成有虚设栅极布线56a。标准单元c3a包括栅极布线52、焊盘46、纳米片24以及虚设纳米片34a,栅极布线52形成为沿x方向与虚设栅极布线56a相邻,焊盘46设在虚设栅极布线56a与栅极布线52之间,纳米片24形成为与栅极布线52在俯视时重合且与焊盘46相连,虚设纳米片34a形成为与虚设栅极布线56a在俯视时重合且与焊盘46相连。标准单元c3b包括栅极布线53、焊盘49、纳米片26以及虚设纳米片36a,栅极布线53形成为沿x方向与虚设栅极布线56a相邻,焊盘49设在虚设栅极布线56a与栅极布线53之间,纳米片26形成为与栅极布线53在俯视时重合且与焊盘49相连,虚设纳米片36a形成为与虚设栅极布线56a在俯视时重合且与焊盘49相连且形成为与虚设纳米片34a分开。

[0128]

在标准单元c3a的附图右端部,焊盘46形成在作为沟道部发挥作用的纳米片24与不作为沟道部发挥作用的虚设纳米片34a之间。在标准单元c3b的附图左端部,焊盘49形成在作为沟道部发挥作用的纳米片26与不作为沟道部发挥作用的虚设纳米片36a之间。虚设纳米片34a、36a沿x方向分开,以免电连接。

[0129]

焊盘46通过使形成纳米片24和虚设纳米片34a的层叠半导体外延生长而形成。焊盘49通过使形成纳米片26和虚设纳米片36a的层叠半导体外延生长而形成。另一方面,形成在作为沟道部发挥作用的纳米片彼此之间的焊盘(例如,焊盘45等)通过从形成在x方向两

侧的层叠半导体部外延生长而形成。即,形成在标准单元c3的x方向的两端部的焊盘和形成在作为沟道部发挥作用的纳米片彼此之间的焊盘都以同样方式形成。这样一来,能抑制上述焊盘的形状偏差。因此,因为能够抑制晶体管的制造精度的偏差和晶体管的性能偏差,所以能够提高半导体集成电路装置的可靠性和成品率。

[0130]

因为标准单元c3a、c3b沿x方向相邻布置,所以能够实现半导体集成电路装置的小面积化。

[0131]

需要说明的是,在图12(b)中,可以除去层叠半导体部232的全部,也可以除去层叠半导体部234、235中的一者。

[0132]

在上述各实施方式中,在标准单元c1~c3中,构成有二输入“与非”电路,但不限于此,也可以构成有其他电路。

[0133]

在上述各实施方式中,一个纳米片fet中包括的纳米片不限于两片,也可以是一片或三片以上。

[0134]

在上述各实施方式中,纳米片的剖面形状为长方形,但不限于此。例如,也可以是正方形、圆形、椭圆形等。

[0135]

在上述各实施方式中,图示中各纳米片整周被栅极布线覆盖,但各纳米片也可以一部分不被栅极布线覆盖。例如,在图2中,纳米片22的附图左侧的侧面和纳米片24的附图右侧的侧面等可以不被覆盖。

[0136]

在上述各实施方式中,各层叠半导体由两个半导体层和两个牺牲半导体层构成,但不限于此。例如,层叠半导体也可以由两个以上半导体层和两个以上牺牲半导体层构成。此外,半导体层和牺牲半导体层的膜厚可以不同,也可以相同。

[0137]

在上述各实施方式中,在半导体集成电路装置的制造工序中,在半导体衬底100上形成绝缘膜401或绝缘膜411,但也可以不形成绝缘膜401或绝缘膜411。在此情况下,从半导体衬底100进行外延生长。

[0138]-产业实用性-[0139]

在本公开中,在包括采用了纳米片fet的标准单元的半导体集成电路装置的版图构造中,能够抑制形成在标准单元中的晶体管的性能偏差。

[0140]-符号说明-[0141]

c1(c1a、c1b)、c2、c3(c3a、c3b)标准单元

[0142]

cf填充单元

[0143]

11、12电源布线

[0144]

21~25内米片

[0145]

31~36、31a~36a虚设纳米片

[0146]

41~50焊盘

[0147]

51~53栅极布线

[0148]

55~57、55a、56a虚设栅极布线

[0149]

200,230层叠半导体

[0150]

201~206、231~235层叠半导体部

[0151]

210、213~216、241、243~245半导体层

[0152]

220、223~226、251、253~255牺牲半导体层

[0153]

301~304、311~313牺牲栅极构造体

[0154]

501~504、511~514焊盘

[0155]

601~604、611~613栅极氧化膜

[0156]

701~704、711~713栅极布线

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1