电感装置的制作方法

1.本公开涉及一种电子装置,且特别涉及一种电感装置。

背景技术:

2.一般应用于电感装置的封闭回路会降低电感装置的电感值,并且影响电感装置的品质因素(q值)。若封闭回路越接近电感装置内的其余元件,则电感装置的品质因素将被显著地影响。

技术实现要素:

3.本公开内容的一技术实施方式涉及一种电感装置,其包括第一走线、第二走线、第一电容及至少一连接部。第一走线包括至少两个子走线,且至少两个子走线的一端耦接于第一节点。第二走线包括至少两个子走线,且至少两个子走线的一端耦接于第二节点。电容耦接于第一节点及第二节点之间。至少一连接部耦接于第一走线的至少两个子走线的另一端与第二走线的至少两个子走线的另一端,以使第一走线与第二走线形成封闭回路。

4.因此,根据本公开的技术内容,本公开实施例所示的电感装置中的电容可形成一个低频阻隔的功能,以使于电感装置感应的低频信号无法通过而高频信号能直接通过。低频信号举例而言,如2.4ghz主要操作频率,通过电感装置的曲折的电感架构(folded inductor)对主要操作频率的感应信号进行相消,所以曲折的电感架构并不会影响电感操作频率的特性,并且感应在曲折二线上的信号会因反向而相消,而若中央电感架构有高频信号,例如2倍谐波5ghz,则因高频信号电容为导通之故,使得高频信号由曲折的电感架构通过电容而形成一个绕围一圈的感应电感,进而在本公开主张的电感架构感应出相对应2.4ghz十倍以上的5ghz谐波信号。使用者再把此5ghz信号于电路中应用,例如放大信号之后再把操作频率的5ghz谐波进行相消,另其应用放大电路可为熟知电路设计者最佳化调整而定。如此,即可降低对5ghz的电路所产生的不良影响。

5.再者,由于本公开将滤波器设置于电感装置内,因此,不需于电感装置外部设置滤波器,从而避免外部滤波器影响到电路本身的性能或是增加额外的费用。另外,本公开实施例的电感装置中的电容除可形成一个低频滤除的功能(例如滤除二阶谐波)外,还可通过多个电容间的配置以将更高频的信号(例如四阶谐波)通过短路的方式导引滤除,以避免原先电路四阶谐波的不良影响。

附图说明

6.为让本公开的上述和其他目的、特征、优点与实施例能更明显易懂,附图的说明如下:

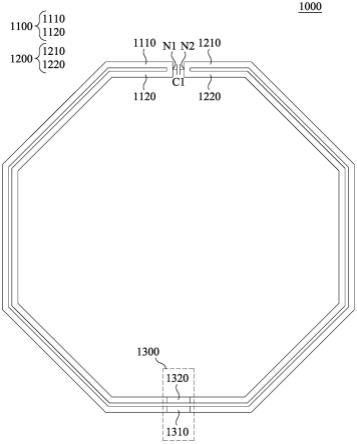

7.图1是依照本公开一实施例示出一种电感装置的示意图。

8.图2是依照本公开一实施例示出一种电感装置的示意图。

9.图3是依照本公开一实施例示出一种如图2所示的电感装置的操作示意图。

10.图4是依照本公开一实施例示出一种如图2所示的电感装置的操作示意图。

11.图5是依照本公开一实施例示出一种电感装置的示意图。

12.图6是依照本公开一实施例示出一种电感装置的示意图。

13.图7是依照本公开一实施例示出一种电感装置的实验数据示意图。

14.根据惯常的作业方式,图中各种特征与元件并未依比例绘制,其绘制方式是为了以最佳的方式呈现与本公开相关的具体特征与元件。此外,在不同附图间,以相同或相似的元件符号来指称相似的元件/部件。

15.符号说明

16.1000、1000a:电感装置

17.1100、1100a:第一走线

18.1110、1110a、1120、1120a:子走线

19.1200、1200a:第二走线

20.1210、1210a、1220、1220a:子走线

21.1300、1300a:连接部

22.1310、1320、1320a:连接件

23.c1、c2:电容

24.l1:曲线

25.n1:第一节点

26.n2:第二节点

具体实施方式

27.图1是依照本公开一实施例示出一种电感装置1000的示意图。为使图1的电感装置1000易于理解,将图1的电感装置1000的结构设计图简化为图2的电感装置1000的示意图。

28.请同时参阅图1及图2,电感装置1000包括第一走线1100、第二走线1200、电容c1及至少一连接部1300。再者,第一走线1100包括至少两个子走线1110、1120。第二走线1200包括至少两个子走线1210、1220。

29.如图所示,至少两个子走线1110、1120的一端(如上端)耦接于第一节点n1。至少两个子走线1210、1220的一端(如上端)耦接于第二节点n2。电容c1耦接于第一节点n1及第二节点n2之间。此外,至少一连接部1300耦接于第一走线1100的至少两个子走线1110、1120的另一端(如下端)与第二走线1200的至少两个子走线1210、1220的另一端(如下端),以使第一走线1100与第二走线1200形成封闭回路。

30.在一实施例中,至少一连接部1300包含第一连接件1310及第二连接件1320。第一连接件1310耦接于第一走线1100的至少两个子走线1110、1120其中一者(如子走线1110)的另一端(如下端)与第二走线1200的至少两个子走线1210、1220其中一者(如子走线1210)的另一端(如下端)。第二连接件1320耦接于第一走线1100的至少两个子走线1110、1120其中另一者(如子走线1120)的另一端(如下端)与第二走线1200的至少两个子走线1210、1220其中另一者(如子走线1220)的另一端(如下端)。

31.于一实施例中,第一走线1100的至少两个子走线1110、1120的每一者包含u型子走线。举例而言,子走线1110、1120皆为u型的子走线。此外,第二走线1200的至少两个子走线

1210、1220的每一者亦包含u型子走线。举例而言,子走线1210、1220皆为u型的子走线。然本公开不以上述实施例为限,在不脱离本公开的构思下,子走线采用其它适当的形状,或其余配置方式,均落入本公开的权利要求内。

32.在一实施例中,第一走线1100包括第一子走线1110及第二子走线1120。再者,第一子走线1110及第二子走线1120皆包括第一端及第二端。如图所示,第一子走线1110的第一端(如上端)与第二子走线1120的第一端(如上端)耦接于第一节点n1。此外,第二走线1200包括第三子走线1210及第四子走线1220。再者,第三子走线1210及第四子走线1220皆包括第一端及第二端。如图所示,第三子走线1210的第一端(如上端)与第四子走线1220的第一端(如上端)耦接于第二节点n2。

33.在一实施例中,第一连接件1310耦接于第一子走线1110的第二端(如下端)与第三子走线1210的第二端(如下端)。在一实施例中,第二连接件1320耦接于第二子走线1120的第二端(如下端)与第四子走线1220的第二端(如下端)。

34.在一实施例中,电容c1与第一连接件1310分别位于电感装置1000的两侧。举例而言,电容c1位于电感装置1000的上侧,而第一连接件1300则位于电感装置1000的下侧。

35.在一实施例中,电容c1与第二连接件1320分别位于电感装置1000的两侧。举例而言,电容c1位于电感装置1000的上侧,而第二连接件1320则位于电感装置1000的下侧。在一实施例中,第一连接件1310与第二连接件1320位于电感装置1000的同一侧。举例而言,第一连接件1310与第二连接件1320均位于电感装置1000的下侧。需说明的是,本公开不以图1及图2所示的结构为限,其仅用以例示性地示出本公开的实现方式之一。

36.图3是依照本公开一实施例示出一种如图2所示的电感装置1000的操作示意图。请先参阅图2,若电感装置1000操作于低频时,配置电容c1处形成如图3所示的断路,因此,本公开实施例所示的电感装置1000中的电容c1可形成一个低频阻隔的功能,以使于电感装置1000感应的低频信号无法通过。

37.图4是依照本公开一实施例示出一种如图2所示的电感装置1000的操作示意图。请先参阅图2,若电感装置1000操作于高频时,配置电容c1处形成如图4所示的短路,而使高频信号能直接通过。在一实施例中,电感可配置于图1至图4示出的电感装置1000内部。

38.图5是依照本公开一实施例示出一种电感装置1000a的示意图。为使图5的电感装置1000a易于理解,将图5的电感装置1000a的结构设计图简化为图6的电感装置1000a的示意图。相较于图2所示的电感装置1000,图6的电感装置1000a的连接部1300a可由电容实作。

39.如图所示,电感装置1000a的连接部1300a包含电容c2。电容c2耦接于第一子走线1110a的第二端(如下端)与第三子走线1210a的第二端(如下端)。此外,电感装置1000a的连接部1300a还包含连接件1320a,且连接件1320a耦接于第二子走线1120a的第二端(如下端)与第四子走线1220a的第二端(如下端)。

40.在一实施例中,电容c1与电容c2分别位于电感装置1000a的两侧。举例而言,电容c1位于电感装置1000a的上侧,而电容c2则位于电感装置1000a的下侧。

41.在一实施例中,电容c1与连接件1320a分别位于电感装置1000a的两侧。举例而言,电容c1位于电感装置1000a的上侧,而连接件1320a则位于电感装置1000a的下侧。在一实施例中,连接件1320a与电容c2位于同一侧。举例而言,连接件1320a与电容c2均位于电感装置1000a的下侧。在一实施例中,电感可配置于图5至图6示出的电感装置1000a内部。需说明的

是,本公开不以图5及图6所示的结构为限,其仅用以例示性地示出本公开的实现方式之一。

42.在一实施例中,电容c1的电容值不同于电容c2的电容值。举例而言,电容c1的电容值大于电容c2的电容值。在一实施例中,依据电感装置1000a感应的信号的频率高低,电感装置1000a中的电容c1与电容c2可同时断路或同时短路,亦或只有电容c1与电容c2其中一者断路,另一者短路。然本公开不以上述实施例为限,在不脱离本公开的构思下,采用电容c2的电容值大于电容c1的电容值的方式,或其余配置方式,均落入本公开的权利要求内。

43.需说明的是,于图5与图6的实施例中,元件标号类似于图1及图2中的元件标号者,具备类似的结构特征,为使说明书简洁,于此不作赘述。此外,本公开不以图5与图6所示的结构为限,其仅用以例示性地示出本公开的实现方式之一。

44.图7是示出依照本公开一实施例的一种电感装置的实验数据示意图。如图所示,采用本公开的架构配置以将电感设置于电感装置1000、1000a内,其品质因素的实验曲线为l1。此外,未采用本公开的架构配置的单一电感的品质因素的实验曲线为l2。由图中可知,于频率约2ghz处,采用本公开的架构配置的电感的品质因素约为9,与未采用本公开的架构配置的单一电感的品质因素相近,由此可知,即便采用本公开的架构配置以将电感设置于电感装置1000、1000a内,对电感的品质因素几乎不会有影响。再者,于频率约4ghz处,本公开的电感装置1000、1000a会形成短路以有效地降低耦合效应。此外,采用本公开的架构的电感装置的谐振频率(harmonic frequency)改善约3db。

45.由上述本公开实施方式可知,应用本公开具有下列优点。本公开实施例所示的电感装置可感应中央电感的高频信号,例如二阶谐波,于额外的电路放大后,以相消原先电路二阶谐波的不良影响。举例而言,通过电感装置的电容主要使用于让高频通过和阻挡低频的技术效果,如此,即可让同一个电感装置相对于高低频有二种不同的信号感应方式。

46.再者,由于本公开将滤波器设置于集成电路(integrated circuit,ic)内,因此,不需于电感装置外部设置滤波器,从而避免外部滤波器影响到电路本身的性能以及其额外的费用。另外,本公开实施例的电感装置中的电容除可形成一个低频滤除的功能(例如滤除二阶谐波)外,还可通过多个电容间的配置以将更高频的信号(例如四阶谐波)通过短路的方式导引滤除,以避免原先电路四阶谐波的不良影响。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1