半导体装置和固体摄像器件的制作方法

半导体装置和固体摄像器件

1.本申请是申请日为2014年9月19日、发明名称为“半导体装置和固体摄像器件”的申请号为201480053552.7的专利申请的分案申请。

技术领域

2.本发明涉及半导体装置和固体摄像器件,且具体地,涉及能够以更简单的方式来提高抗裂性(crack resistance)的半导体装置和固体摄像器件。

背景技术:

3.在现有技术中,已经知晓如下技术:当将两个半导体基板接合在一起且使用贯穿孔来将它们电连接时,为了防止出现裂纹,把引线接合用和探测用焊盘设置在置于下侧的半导体基板中(例如,请参考专利文献1)。这里,所述置于下侧的半导体基板是位于与实施引线接合和探测的那一侧(上侧)相反的一侧处的半导体基板。

4.上述引线接合用和探测用焊盘被设置于下侧的半导体基板上,这是因为:如果该焊盘被设置于上侧的半导体基板上,那么在实施引线接合和在实施探测时作用于该半导体基板上的荷载会集中在该焊盘下面的绝缘膜部分上,这会导致开裂。

5.此外,也曾经提出了这样的技术:当上侧和下侧晶片(半导体基板)的电连接是通过同时将cu电极和绝缘膜接合来实现时,为了使上述cu部分或上述绝缘膜平坦化,在这两个晶片的接合表面中设置有cu虚设焊盘(例如,请参考专利文献2)。

6.引用文献列表

7.专利文献

8.专利文献1:日本专利申请特开jp 2011

‑

35038a

9.专利文献2:日本专利申请特开jp 2012

‑

256736a

技术实现要素:

10.本发明要解决的技术问题

11.然而,在将上述引线接合用和探测用焊盘设置于下侧的半导体基板中的技术中,所述焊盘的开口做得很深,并且需要很长一段的处理时间来形成所述焊盘的所述开口。此外,因为所述焊盘被设置于距上侧(它是用于实施引线接合和探测的那一侧)的半导体基板很深的位置处,所以相应地会更加频繁地出现引线接合不良或探测时的针的接触不良。

12.此外,在设置有cu虚设焊盘的技术中,当将要设置穿透到上述引线接合用焊盘这个部分的开口时,上述两个晶片的接合表面上的所述cu虚设焊盘通过干式蚀刻而被暴露出来。因此,所述cu虚设焊盘充当掩模,并且不可能形成抵达上述引线接合用焊盘的开口。

13.因此,当通过使cu部分和绝缘膜平坦化来使两个晶片彼此接合时,必须在比接合表面更高的位置处设置引线接合用焊盘。然而,在这种情况下,如果该引线接合用焊盘仅仅被制作于上侧晶片(半导体基板)中,那么就会担忧如上所述的在引线接合时出现开裂。

14.本技术考虑了上面的情形,并且旨在以更简单的方式提高抗裂性。

15.解决技术问题所采取的技术方案

16.根据本技术的第一方面的半导体装置包括:第一基板,所述第一基板具有多个布线层;以及第二基板,所述第二基板具有多个布线层,并且所述第二基板被接合至所述第一基板。在所述半导体装置中,在所述第一基板和所述第二基板中的一个基板中设置有焊盘,在所述焊盘与以最靠近另一个基板的方式位于所述另一个基板侧上的布线层之间在各布线层中设置有由金属形成的金属布线,并且在与所述焊盘或所述金属布线相邻的位于所述另一个基板侧上的布线层中,在处于上一层中的所述焊盘或所述金属布线的至少拐角部分处设置有其它的金属布线。

17.所述焊盘可以是引线接合用或探测用焊盘。

18.所述焊盘可以被设置于所述第一基板和所述第二基板中的用于实施引线接合或探测的那一侧的基板中。

19.所述第一基板和所述第二基板可以通过把设置于所述第一基板的表面上的cu布线和设置于所述第二基板的表面上的cu布线接合起来而被接合在一起。

20.在所述金属布线的位于所述第一基板和所述第二基板的接合表面上的接合表面侧表面(bonding

‑

surface

‑

side surface)的中央部分处可以设置有不包含用于形成所述金属布线的材料的区域。

21.在所述焊盘或所述金属布线的至少侧边部分处可以设置有所述其它的金属布线。

22.在构成所述另一个基板且上面层叠有多个布线层的那个基板与所述金属布线之间可以设置有绝缘膜。

23.构成所述另一个基板且上面层叠有多个布线层的那个基板中的与所述金属布线发生接触的那部分的区域可以利用被埋入所述另一个基板中的绝缘体来与所述另一个基板的其它区域电气隔离。

24.在形成有接触部的布线层中,所述焊盘可以由与所述接触部相同的金属形成,所述接触部用于使构成所述一个基板且上面层叠有多个布线层的那个基板与设置于所述一个基板中的布线层中的布线连接。

25.在所述第一基板和所述第二基板的接合之后,所述焊盘可以被形成于停止层这个部分中,所述停止层被设置在所述一个基板内的布线层中、且是通过形成开口而被除去的。

26.所述半导体装置还可以包括:被设置在构成所述一个基板且上面层叠有多个布线层的那个基板中的通孔,所述通孔穿透所述一个基板并且被连接至所述金属布线。所述焊盘可以被设置于所述一个基板的表面的所述通孔上方。

27.所述焊盘可以被设置于所述一个基板中的开口的一部分中,并且是通过利用具有比所述一个基板中的所述开口更窄的开口的金属掩模而被形成的。

28.在所述一个基板中的所述开口的侧面上可以形成有绝缘膜。

29.在所述焊盘中可以埋入有由不同于所述焊盘的金属形成的布线,并且在位于该布线的所述另一个基板侧上的布线层中设置有所述金属布线。

30.在与所述焊盘相邻的位于所述另一个基板侧上的布线层中在所述焊盘的至少拐角部分处,所述布线可以被设置为所述金属布线。

31.在所述布线的表面的中央部分处可以设置有不包含用于形成所述布线的材料的区域。

32.根据本技术的第一方面,设置了第一基板和第二基板,所述第一基板具有多个布线层,所述第二基板具有多个布线层且被接合至所述第一基板。在所述第一基板和所述第二基板中的一个基板中设置有焊盘,在所述焊盘与以最靠近另一个基板的方式位于所述另一个基板侧上的布线层之间在各布线层中设置有由金属形成的金属布线,并且在与所述焊盘或所述金属布线相邻的位于所述另一个基板侧上的布线层中,在处于上一层中的所述焊盘或所述金属布线的至少拐角部分处设置有其它的金属布线。

33.根据本技术的第二方面的半导体装置包括:第一基板,所述第一基板具有多个布线层;以及第二基板,所述第二基板具有多个布线层且被接合至所述第一基板。在所述第一基板中设置有:设置于跟所述第二基板接合的接合表面上的接合用cu焊盘;及穿透多个布线层且使所述接合用cu焊盘与cu布线连接的cu通孔。而且,在所述第二基板中设置有:设置于跟所述第一基板接合的接合表面上且与所述接合用cu焊盘接合的另一个接合用cu焊盘。

34.根据本技术的第二方面,设置了第一基板和第二基板,所述第一基板具有多个布线层,所述第二基板具有多个布线层且被接合至所述第一基板。在所述第一基板中设置有:设置于跟所述第二基板接合的接合表面上的接合用cu焊盘;及穿透多个布线层且使所述接合用cu焊盘与cu布线连接的cu通孔(cu vias)。而且,在所述第二基板中设置有:设置于跟所述第一基板接合的接合表面上且与所述接合用cu焊盘接合的另一个接合用cu焊盘。

35.根据本技术的第三方面的固体摄像器件包括:第一基板,其具有多个布线层;和第二基板,其具有多个布线层,并且被接合至所述第一基板。在所述第一基板和所述第二基板中的一个基板中设置有焊盘,在所述焊盘与以最靠近另一个基板的方式位于所述另一个基板侧上的布线层之间在各布线层中设置有由金属形成的金属布线,并且在与所述焊盘或所述金属布线相邻的位于所述另一个基板侧上的布线层中,在处于上一层中的所述焊盘或所述金属布线的至少拐角部分处设置有其它的金属布线。

36.根据本技术的第三方面,设置了第一基板和第二基板,所述第一基板具有多个布线层,所述第二基板具有多个布线层且被接合至所述第一基板。在所述第一基板和所述第二基板中的一个基板中设置有焊盘,在所述焊盘与以最靠近另一个基板的方式位于所述另一个基板侧上的布线层之间在各布线层中设置有由金属形成的金属布线,并且在与所述焊盘或所述金属布线相邻的位于所述另一个基板侧上的布线层中,在处于上一层中的所述焊盘或所述金属布线的至少拐角部分处设置有其它的金属布线。

37.本发明的有益效果

38.根据本技术的第一方面至第三方面,能够以更简单的方式提高抗裂性。

39.应当注意的是,这里所说明的效果并非是限制性的,而是也可以展现出本申请文件中所说明的任何效果。

附图说明

40.图1是说明了作用于焊盘上的应力和保护用焊盘的图。

41.图2是示出了保护用焊盘的示例的图。

42.图3是示出了半导体装置的构造示例的图。

43.图4是说明了半导体装置的制造步骤的图。

44.图5是说明了半导体装置的制造步骤的图。

45.图6是说明了半导体装置的制造步骤的图。

46.图7是示出了半导体装置的构造示例的图。

47.图8是说明了半导体装置的制造步骤的图。

48.图9是说明了半导体装置的制造步骤的图。

49.图10是说明了半导体装置的制造步骤的图。

50.图11是示出了半导体装置的构造示例的图。

51.图12是说明了半导体装置的制造步骤的图。

52.图13是说明了半导体装置的制造步骤的图。

53.图14是说明了半导体装置的制造步骤的图。

54.图15是说明了半导体装置的制造步骤的图。

55.图16是说明了半导体装置的制造步骤的图。

56.图17是说明了半导体装置的制造步骤的图。

57.图18是说明了半导体装置的制造步骤的图。

58.图19是说明了半导体装置的制造步骤的图。

59.图20是示出了半导体装置的构造示例的图。

60.图21是说明了半导体装置的制造步骤的图。

61.图22是说明了半导体装置的制造步骤的图。

62.图23是说明了半导体装置的制造步骤的图。

63.图24是说明了半导体装置的制造步骤的图。

64.图25是说明了半导体装置的制造步骤的图。

65.图26是说明了半导体装置的制造步骤的图。

66.图27是示出了半导体装置的构造示例的图。

67.图28是说明了半导体装置的制造步骤的图。

68.图29是说明了半导体装置的制造步骤的图。

69.图30是说明了半导体装置的制造步骤的图。

70.图31是说明了半导体装置的制造步骤的图。

71.图32是说明了半导体装置的制造步骤的图。

72.图33是示出了半导体装置的构造示例的图。

73.图34是说明了半导体装置的制造步骤的图。

74.图35是说明了半导体装置的制造步骤的图。

75.图36是说明了半导体装置的制造步骤的图。

76.图37是说明了半导体装置的制造步骤的图。

77.图38是说明了半导体装置的制造步骤的图。

78.图39是示出了固体摄像器件的构造示例的图。

具体实施方式

79.以下,将参照附图来说明本技术适用的实施例。

80.第一实施例

81.本技术的概述

82.本发明涉及一种通过例如将两个半导体基板接合在一起而获得的半导体装置(芯片)。首先,将会说明本技术的概述。

83.如图1所示,例如,当从被接合的上侧半导体基板这一侧对设置于半导体装置中的al(铝)焊盘pd11实施引线接合或探测时,应力如上所述就集中在焊盘pd11上。这样就会担忧的是:在紧邻地处于焊盘pd11下面的绝缘膜部分等中出现开裂。

84.因此,本技术为了在引线接合或探测时保护焊盘pd11的作为撞击力集中地点的下部拐角(拐角)或侧边的目的,如箭头q11和箭头q12所示的那样布置有cu(铜)布线。

85.应当注意的是,箭头q11示出了沿构成半导体装置的半导体基板的法线方向来观看焊盘pd11时的图,并且箭头q12示出了沿着从该图的下部至上部的方向来观看由箭头q11示出的焊盘pd11时的图,即横截面图。

86.在由箭头q11和箭头q12所示出的示例中,由cu形成的焊盘cpd11

‑

1至焊盘cpd11

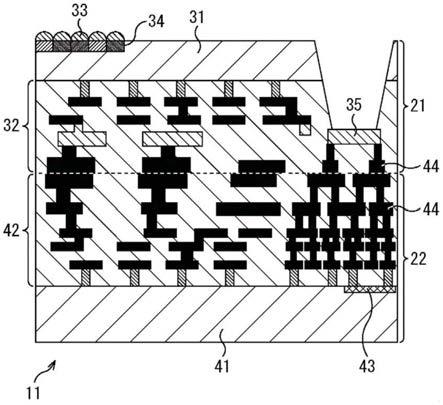

‑

4被设置于焊盘pd11的四个拐角部分处。应当注意的是,当没有特别的需要来区分这些焊盘时,焊盘cpd11

‑

1至焊盘cpd11

‑

4也将会被简称为焊盘cpd11。

87.此外,如箭头q13所示,比焊盘cpd11更大的焊盘cpd21被设置于焊盘cpd11的下面。换言之,例如,如箭头q14所示,焊盘cpd21

‑

1和焊盘cpd21

‑

2被设置于由箭头q12所示出的焊盘cpd11

‑

3和焊盘cpd11

‑

4的下面。

88.如图2中的箭头q21所示,被设置于焊盘pd11下侧的焊盘可以被形成为设置于焊盘pd11的各拐角下面的例如正方形焊盘cpd11

‑

1至正方形焊盘cpd11

‑

4,或可以被形成为其他不同的形状。

89.应当注意的是,图2是从构成半导体装置的半导体基板的法线方向来观看焊盘pd11时的图,并且与图1中的元件对应的图2中的元件将会赋予相同的附图标记,且将适当地省略它们的说明。

90.此外,如箭头q22所示,在焊盘pd11的下面可以设置有用于保护焊盘pd11的各个侧边部分的cu焊盘cpd31(即,cu布线)。这个焊盘cpd31被设置成紧邻地处于焊盘pd11的侧边部分的下面,以致于当从半导体基板的法线方向来观看焊盘pd11时,焊盘cpd31包围着焊盘pd11的各个侧边。换言之,焊盘cpd31被形成为环形,且因此在焊盘pd11的中央部分的底部中不存在用于构成焊盘cpd31的cu。换言之,在焊盘cpd31的中央附近适度地设置有不包含cu的部分。

91.此外,如箭头q23和箭头q24所示,在由沿着焊盘pd11的四条侧边设置着的cu布线封闭起来的空间中,可以设置有其中布置有至少一个cu布线配置的焊盘。

92.例如,在由箭头q23所示出的示例中,在焊盘pd11的下面设置有焊盘cpd32,该焊盘cpd32包括:用于保护焊盘pd11的各个侧边部分的cu布线;以及位于焊盘pd11的中央处且沿着将焊盘pd11的上、下两个侧边连接起来的纵向方向而延伸的cu布线。在焊盘cpd32的中央附近适度地设置有不包含cu(它是用于形成焊盘cpd32的材料)的部分。

93.此外,在由箭头q24所示出的示例中,在焊盘pd11的下面设置有焊盘cpd33,该焊盘cpd33包括:用于保护焊盘pd11的各个侧边部分的cu布线;位于焊盘pd11的中央处且沿着将焊盘pd11的上、下两个侧边连接起来的纵向方向而延伸的cu布线;以及沿着将焊盘pd11的左右两个侧边连接起来的水平方向而延伸的cu布线。在焊盘cpd33的中央附近适度地设置有不包含cu(它是用于形成焊盘cpd33的材料)的部分。

94.此外,可以设置比焊盘pd11更大的矩形焊盘以作为用于保护该焊盘pd11的cu焊盘。

95.在本技术中,在半导体基板的法线方向上在引线接合用或探测用焊盘的下面,即,在半导体基板的接合表面侧上,设置有由cu等形成的、且至少保护所述引线接合用或探测用焊盘的拐角部分或侧边部分的焊盘(布线)。此外,在保护用焊盘的下面也设置有用于保护这些保护用焊盘的拐角部分或侧边部分的焊盘。另外,如上所述的用于保护上一层焊盘的拐角部分或侧边部分的各层焊盘例如以这些保护用焊盘呈放射状扩张的方式而被彼此连结(层叠起来)直到到达与设置有所述用于引线接合等用途的焊盘的半导体基板相接合的半导体基板。

96.于是,所述引线接合用或探测用焊盘的抗裂性能够被提高,这使得能够实施针对于上侧半导体基板的引线接合或探测。结果,能够使焊盘的深度保持得比较浅,并且能够实现缩短焊盘开口形成时间和防止引线接合不良和探针接触不良。

97.应当注意的是,在两个半导体基板相互接合在一起的接合表面上必须使cu焊盘的尺寸大到例如足以覆盖图1中所示的al焊盘pd11的整个区域,以使得焊盘pd11能够被保护着。

98.然而,当在接合表面上存在着大的cu焊盘时,该焊盘会影响为了使接合表面平坦化而对cu部分或绝缘膜部分进行化学机械研磨(cmp:chemical

‑

mechanical polishing)时的平坦化,且因此在cu焊盘部分中发生凹陷。换言之,cu焊盘部分变成凹形的。

99.因为发生了这样的凹陷的部分很难进行接合,所以有必要让接合表面上的cu焊盘的形状是能够防止发生凹陷的形状。

100.因此,优选的是,在处于接合表面上的cu焊盘的接合表面侧的表面上设置有不包含cu的部分(区域)。具体地,通过将接合表面上的cu焊盘的形状设置成例如由图2中的箭头q22所示出的焊盘cpd31的形状,能够减小接合表面上的cu部分的面积,并且能够抑制凹陷的发生。此外,通过将接合表面上的cu焊盘的形状设置成例如图2中的由箭头q23所示出的焊盘cpd32的形状或由箭头q24所示出的焊盘cpd33的形状,能够抑制凹陷的发生,并且能够更加稳固地保护处于焊盘pd11下面的接合表面部分。

101.半导体装置的构造示例

102.接下来,将会说明本技术适用的具体实施例。

103.图3是示出了本技术适用的半导体装置的实施例的构造示例的图。

104.图3中所示的半导体装置11包括由例如互补金属氧化物半导体(cmos:complementary metal

‑

oxide semiconductor)图像传感器构成的摄像器件,并且具有接合在一起的上侧基板21和下侧基板22。应当注意的是,上侧基板21与下侧基板22之间的虚线表示上侧基板21和下侧基板22的接合表面。

105.上侧基板21包括si基板31和配线层32,配线层32被层叠于si基板31上。配线层32包括多个布线层。此外,片上透镜33和彩色滤光片34被设置于该图中的si基板31的上侧上,片上透镜33用于聚集来自被摄对象的光,彩色滤光片34透射由片上透镜33聚集的光中的预定颜色的光。而且,由al形成的引线接合用焊盘35也被设置于配线层32中。

106.下侧基板22包括si基板41和配线层42,配线层42被层叠于si基板41上,并且在配线层42的与si基板41接触的那部分的一部分上设置有绝缘膜43。此外,配线层42包括多个

布线层。

107.此外,在这个示例中,在配线层32和配线层42中的位于引线接合用焊盘35与绝缘膜43之间的各层中,设置有由cu形成的用于保护焊盘35的焊盘,并且这些焊盘利用绝缘膜43而与si基板41绝缘。具体地,在半导体装置11中,焊盘组44被设置于焊盘35与绝缘膜43之间,焊盘组44由多层焊盘(布线)组成且用于保护上一层的cu焊盘或al焊盘35。

108.换言之,在该图中的位于焊盘35下面的布线层中,在焊盘35的至少拐角部分处设置有用于保护焊盘35的cu焊盘。此外,在该图中的位于各层cu焊盘下面的各布线层中,在各个位于上层的cu焊盘的至少拐角部分处设置有由cu形成的、且进一步保护用于保护焊盘35的那些cu焊盘的焊盘。以这种方式,在焊盘35与绝缘膜43之间的各布线层中,用来保护上一层焊盘的焊盘被设置于所述上一层焊盘的至少拐角部分处。换言之,用来保护焊盘35的焊盘被层叠着。

109.各层中的cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上的形状被设定成图2中的由箭头q22所示出的焊盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

110.通过如上所述地设置位于该图中的焊盘35下面的各层cu焊盘,能够提高抗裂性。因此,利用在该图中的焊盘35下面设置有保护用焊盘的简单构造,当从该图的上侧在焊盘35上实施引线接合时,能够防止位于该图中的焊盘35下面的各布线层中的绝缘膜等由于应力而受到损坏。

111.此外,利用这样的构造,引线接合用或探测用金属焊盘能够被设置于上侧基板21上。结果,从si基板31至该金属焊盘的深度能够被设定成比较浅,能够缩短焊盘开口形成时间,并且能够抑制引线接合不良或针接触不良的发生。

112.应当注意的是,关于被设置于上侧基板21中的金属焊盘,可以提前在上侧基板21中制造该焊盘,或可以在形成焊盘开口之后形成金属焊盘层。

113.关于半导体装置的制造方法

114.接下来,将参照图4至图6来说明图3中所示的半导体装置11的制造方法。应当注意的是,与图3中的元件对应的图4至图6中的元件将会被赋予相同的附图标记,且将会适当地省略它们的说明。此外,在图3和图4至图6中,以简化的方式绘制了半导体装置11中的布线结构的一部分,以便能够更容易地理解这些图。因此,在图3和图4至图6中,所述布线结构的一部分可能是不同的部分。

115.如图4中的箭头q31所示,例如,在si基板31上形成布线层l11,在该布线层l11中设置有被连接至诸如晶体管等基本器件的cu布线,然后在位于布线层l11的上层中的布线层l12中进一步形成al布线结构。作为该al布线结构,例如,形成了焊盘35或其它的al布线。

116.接着,如箭头q32所示,在布线层l12的表面上形成厚度为500nm至5000nm的sio2膜和含碳氧化硅(sioc:carbon

‑

containing silicon oxide)膜,以作为层间绝缘膜fl11。应当注意的是,成膜方法可以是化学气相沉积(cvd:chemical vapor deposition)方法或旋涂法中的任一者。

117.进一步,如箭头q33所示,在化学机械研磨(cmp)方法中把形成于布线层l12的表面上的sio2膜和含碳氧化硅(sioc)膜(即,层间绝缘膜fl11)研磨成具有100nm至4000nm的厚度,并由此平坦化。

118.然后,尽管如箭头q34所示的那样在布线层l13中形成被连接至al布线的cu布线结构,但是在这里执行了直到cu的cmp为止的处理。

119.此外,此时,与被设置于布线层l12中的al布线(特别地,诸如焊盘35等金属焊盘部分)连接的cu布线结构51呈现为如下的布局:其中,该结构被设置成紧邻地位于金属焊盘的四个拐角和四个侧边的下面,就像图2中所示的焊盘cpd11或焊盘cpd31一样。

120.对于提高抗裂性,如下的布局也是有效的:该布局中,像图2中也示出的焊盘cpd32或焊盘cpd33一样,至少一个cu布线配置被设置于由四个侧边的cu布线包围起来的空间中。在图2中所示的各示例的任一者中,cu布线结构51可以是所谓的通孔结构(via structure)或布线结构,并且该布线的宽度可以是在0.2μm至50μm的范围中的任何宽度。

121.上侧基板21是通过上述这些步骤而获得的。

122.另一方面,下侧基板22是如图5所示而被制造的。

123.换言之,如箭头q41所示,将绝缘膜43埋入到具有器件的si基板41中。绝缘膜43可以是例如sio2膜或sin膜。此外,绝缘膜43的埋入厚度可以是在10nm至1000nm的范围中的任何厚度。

124.然后,以与上述的关于上侧基板21的方式相同的方式,如箭头q42所示,在布线层l21中形成与si基板41连接的接触部。这里,在埋入有绝缘膜43的部分中,这些接触部并不到达si基板41,而是仅仅将这些接触部的底部设计成到达绝缘膜43的顶部或绝缘膜43的内部。

125.而且,以与上述的关于上侧基板21的方式相同的方式,如箭头q43所示,在布线层l22中形成cu布线结构,所述布线层l22位于布线层l21的上层中且包括数个布线层。在这个示例中,cu布线结构52被形成于该图中的绝缘膜43的上侧上。此外,对用于构成布线层l22的所述多个布线层之中的最上层(即,在该图中的布线层l22的上侧处的那个布线层)执行直到cu的cmp为止的处理。

126.在布线层l22中形成了例如用于构成cu布线结构52的各层cu焊盘(布线)等cu焊盘,且这些cu焊盘像图2中所示的焊盘cpd11或焊盘cpd31那样,在与上侧基板21接合的时候紧邻地位于金属焊盘的四个拐角和四个侧边的下面。

127.下侧基板22是通过上述这些步骤而获得的。

128.然后,如图6中的箭头q51所示,使上侧基板21和下侧基板22彼此面对地相互接合。具体地,把构成上侧基板21的配线层32和构成下侧基板22的配线层42布置成彼此面对,把彼此面对的cu部分接合在一起,并且把彼此面对的绝缘膜部分接合在一起。

129.因此,例如,cu布线结构51和cu布线结构52被接合在一起,且因此形成了图3中所示的cu焊盘组44。

130.应当注意的是,为了上侧基板21和下侧基板22的接合,使用了例如jp 2012

‑

256736a等中所说明的方法。

131.此外,使用例如jp 2007

‑

234725a等中所说明的方法使上侧基板21中的si基板31的厚度减薄,然后如箭头q52所示,在si基板31的表面上形成绝缘膜fl21。应当注意的是,绝缘膜fl21可以是sio2膜或sin膜或者它们的层叠膜。此外,绝缘膜fl21的厚度可以是在10nm至3000nm的范围中的任何厚度。

132.在形成绝缘膜fl21之后,使用一般的光刻和干式蚀刻技术来形成焊盘开口的图

案,且因此如箭头q53所示,已经被形成于上侧基板21的布线结构中的al焊盘35的一部分或整个部分通过该焊盘开口而暴露出来。换言之,用于使焊盘35露出的开口op11被设置于上侧基板21中。因此,与焊盘35的引线接合是能够实施的。

133.随后,在上侧基板21上设置片上透镜(on

‑

chip lens)33和彩色滤光片34,且因此形成了半导体装置11。应当注意的是,在上侧基板21和下侧基板22的接合之后所要执行的步骤取决于应用了本技术的器件;然而,当本技术被应用于固体摄像器件时,在例如jp 2007

‑

234725a中所说明的步骤就被执行。

134.根据上述的半导体装置11,由al等形成的金属焊盘被在该焊盘下面设置的由cu形成的焊盘(金属布线)保护着,且因此当在金属焊盘上实施引线接合或探测时,能够抑制对该焊盘等下面的绝缘膜的损坏。换言之,利用设置了保护用焊盘的简单构造,能够提高半导体装置11的抗裂性。

135.此外,因为由al等形成的金属焊盘能够被设置于实施引线接合或探测的那一侧的基板(即,半导体装置11中的上侧基板21)上,所以能够抑制引线接合不良或针接触不良的发生。此外,当金属焊盘被形成时,能够缩短制造(焊盘开口形成)时所需要的处理时间,且因此能够提高生产力。

136.另外,尽管已经说明了当两个基板被接合(结合)在一起时,用来保护被设置于上侧基板中的金属焊盘的焊盘被层叠于该金属焊盘与下侧基板之间的示例,但是这同样可以适用于将三个以上的基板接合起来的情况。换言之,用来保护被设置于三个以上的接合基板之中的上侧基板上的金属焊盘的焊盘可以被层叠且被设置于该金属焊盘与最下侧基板之间。

137.第二实施例

138.半导体装置的构造示例

139.应当注意的是,尽管已经在第一实施例中说明了被设置于焊盘35下面的cu焊盘(cu布线)是通过在这些cu焊盘与si基板41之间设置绝缘膜43来与si基板41绝缘的示例,但是通过将绝缘体埋入到si基板41的一部分中来实现上述绝缘的设计也是可能的。

140.在这样的情况下,半导体装置11是例如如图7所示而被构造的。应当注意的是,与图3中的元件对应的图7中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

141.图7中所示的半导体装置11与图3中所示的半导体装置11的不同之处在于:该装置在si基板41中没有设置绝缘膜43,但是设置有绝缘膜71

‑

1和另一个绝缘膜71

‑

2。

142.在图7中,绝缘膜71

‑

1和绝缘膜71

‑

2被设置于si基板41中且围绕着如下的局部区域:该局部区域中,被设置于焊盘35下面的cu焊盘(焊盘组44)与si基板41发生接触。因此,si基板41中的与cu焊盘电连接的区域是利用绝缘膜71

‑

1和绝缘膜71

‑

2而与si基板41中的其它区域电气隔离的。

143.关于半导体装置的制造方法

144.接下来,将参照图8至图10来说明图7中所示的半导体装置11的制造方法。应当注意的是,与图7中的元件对应的图8至图10中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。此外,在图7和图8至图10中,以简化的方式绘制了半导体装置11中的布线结构的一部分,以便能够更容易地理解这些图。因此,在图7和图8至图10中,所述布线结

构的一部分可能是不同的部分。

145.如图8中的箭头q61所示,例如,在si基板31上形成布线层l11,该布线层l11中设置有被连接至诸如晶体管等基本器件的cu布线,并且在位于布线层l11的上层中的布线层l12中进一步形成al布线结构。作为该al布线结构,例如,形成了焊盘35或其它的al布线。

146.然后,如箭头q62所示,在布线层l12的表面上形成厚度为500nm至5000nm的sio2膜和含碳氧化硅(sioc)膜,以作为层间绝缘膜fl11。应当注意的是,成膜方法可以是cvd方法或旋涂法中的任一者。

147.进一步,如箭头q63所示,在cmp方法中把形成于布线层l12的表面上的sio2膜和含碳氧化硅(sioc)膜(即,层间绝缘膜fl11)研磨成具有100nm至4000nm的厚度,并由此平坦化。

148.然后,尽管如箭头q64所示出的那样在布线层l13中形成被连接至al布线的cu布线结构,但是在这里执行了直到cu的cmp为止的处理。

149.此外,此时,与被设置于布线层l12中的al布线(特别地,诸如焊盘35等金属焊盘部分)连接的cu布线结构51呈现为如下的布局:其中,该结构被设置成紧邻地位于金属焊盘的四个拐角和四个侧边的下面,就像图2中所示的焊盘cpd11或焊盘cpd31一样。

150.对于提高抗裂性,如下的布局也是有效的:该布局中,像图2中也示出的焊盘cpd32或焊盘cpd33一样,至少一个cu布线配置被设置于由四个侧边的cu布线包围起来的空间中。在图2中所示的各示例的任一者中,cu布线结构51可以是所谓的通孔结构或布线结构,并且该布线的宽度可以是在0.2μm至50μm的范围中的任何宽度。

151.上侧基板21是通过上述这些步骤而获得的。

152.另一方面,下侧基板22是如图9所示而被制造出来的。

153.换言之,如箭头q71所示,将绝缘膜71

‑

1和绝缘膜71

‑

2埋入到具有器件的si基板41中。绝缘膜71

‑

1和绝缘膜71

‑

2可以是例如sio2膜或sin膜。此外,绝缘膜71

‑

1和绝缘膜71

‑

2的埋入厚度可以是在10nm至1000nm的范围中的任何厚度。

154.然后,以与上述的关于上侧基板21的方式相同的方式,如箭头q72所示,在布线层l21中形成与si基板41连接的接触部。

155.进一步,以与上述的关于上侧基板21的方式相同的方式,如箭头q73所示,在布线层l22中形成cu布线结构,所述布线层l22位于布线层l21的上层中且包括数个布线层。在这个示例中,cu布线结构52被形成于该图中的绝缘膜71

‑

1和绝缘膜71

‑

2的上侧上。此外,对用于构成布线层l22的所述多个布线层之中的最上层(即,在该图中的布线层l22的上侧处的那个布线层)执行直到cu的cmp为止的处理。

156.在布线层l22中形成了诸如用于构成cu布线结构52的各层cu焊盘(布线)等cu焊盘,且这些cu焊盘像图2中所示的焊盘cpd11或焊盘cpd31那样,在与上侧基板21接合的时候紧邻地位于金属焊盘的四个拐角和四个侧边的下面。

157.下侧基板22是通过上述这些步骤而获得的。

158.然后,如图10中的箭头q81所示,使上侧基板21和下侧基板22彼此面对地相互接合。具体地,把构成上侧基板21的配线层32和构成下侧基板22的配线层42布置成彼此面对,把彼此面对的cu部分接合在一起,并且把彼此面对的绝缘膜部分接合在一起。

159.应当注意的是,为了上侧基板21和下侧基板22的接合,使用了例如jp 2012

‑

256736a等中所说明的方法。

160.此外,使用例如jp 2007

‑

234725a等中所说明的方法使上侧基板21中的si基板31的厚度减薄,然后如箭头q82所示,在si基板31的表面上形成绝缘膜fl21。应当注意的是,绝缘膜fl21可以是sio2膜或sin膜或者它们的层叠膜。此外,绝缘膜fl21的厚度可以是在10nm至3000nm的范围中的任何厚度。

161.此外,当已经形成了绝缘膜fl21时,在绝缘膜fl21上设置抗蚀剂rg11。然后,使用一般的光刻技术和干式蚀刻技术来形成焊盘开口的图案,且因此已经形成于上侧基板21的布线结构中的al焊盘35的一部分或整个部分通过该焊盘开口而暴露出来。

162.于是,如箭头q83所示,开口op11被形成于上侧基板21上,焊盘35通过开口op11而暴露出来。从这个开口op11来实施对焊盘35的引线接合是可能的。

163.随后,在上侧基板21上设置片上透镜33和彩色滤光片34,且因此形成了半导体装置11。应当注意的是,在上侧基板21和下侧基板22的接合之后所要执行的步骤取决于应用了本技术的器件;然而,当本技术被应用于固体摄像器件时,就会执行例如jp 2007

‑

234725a中所说明的步骤。

164.如上所述,即使当绝缘膜71

‑

1和绝缘膜71

‑

2被埋入到下侧基板22中时,si基板41中的与焊盘35电连接的局部区域也能够与其它区域绝缘。

165.第三实施例

166.半导体装置的构造示例

167.此外,被设置于半导体装置的上侧基板中的金属焊盘能够在上侧基板的cu布线的制造期间内被制造出来;然而,通过在形成接触部的同时制造金属焊盘,可以不设置al焊盘用的布线层。因此,能够免除使用al布线的焊盘形成步骤。

168.当如上所述在形成接触部的同时制造金属焊盘时,如图11所示构造出半导体装置。应当注意的是,与图3中的元件对应的图11中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

169.半导体装置101具有被接合在一起的上侧基板21和下侧基板22,并且在该图中的上侧基板21与下侧基板22之间的虚线表示上侧基板21和下侧基板22的接合表面。

170.上侧基板21包括si基板31和配线层32,并且片上透镜33和彩色滤光片34被设置于该图中的si基板31的上侧上。

171.此外,均由钨(w)形成的引线接合用焊盘111以及接触部112

‑

1至接触部112

‑

5被设置于布线层l31中,布线层l31位于包括多个布线层的配线层32中且被设置成与si基板31相邻。

172.应当注意的是,当没有特别的需要来区分接触部112

‑

1至接触部112

‑

5时,它们在下文中也将简称为接触部112。接触部112使设置于si基板31内的晶体管(未图示)和设置于紧邻地位于布线层l31下面的布线层中的cu布线电连接。焊盘111被设置于里面形成有接触部112的布线层l31中。

173.此外,下侧基板22包括si基板41和配线层42。

174.同样在半导体装置101中,如箭头a11所示,在配线层32和配线层42的位于引线接合焊盘111与si基板41之间的各层中设置有由cu形成的、且用来保护焊盘111的焊盘。应当注意的是,在si基板41的表面上形成有绝缘膜,且因此把用来保护焊盘111的那些焊盘设定

成不与si基板41电接触。

175.具体地,在该图中的焊盘111下面的布线层中,用于保护焊盘111的cu焊盘被设置于焊盘111的至少拐角部分中。此外,在该图中的各层cu焊盘下面的布线层中,用来进一步保护用于保护焊盘111的那些cu焊盘的cu焊盘被设置于上一层cu焊盘的至少拐角部分中。以这种方式,在焊盘111与si基板41之间的各布线层中,用来保护处于上一层中的焊盘的焊盘被设置于所述处于上一层中的焊盘的至少拐角部分中。换言之,用来保护焊盘111的各层焊盘被层叠着。

176.各层中的cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上的形状被设定成图2中的由箭头q22所示出的焊盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

177.如上所述通过简单地将cu焊盘设置于该图中的焊盘111的下侧,就能够提高抗裂性。此外,利用这样的构造,引线接合用或探测用的金属焊盘能够被设置于上侧基板21上。结果,从si基板31至金属焊盘的深度能够被设定成比较浅,能够缩短焊盘开口形成时间,并且能够抑制引线接合不良或针接触不良的发生。

178.此外,在半导体装置101中,上侧基板21和下侧基板22利用用于保护焊盘111的那些cu焊盘而被电连接。

179.应当注意的是,图11中所示的半导体装置101示出的是充当半导体装置101的固体摄像器件的横截面。

180.此外,在半导体装置101中,充当使制造于si基板31内的晶体管与cu布线电连接的接触电极的接触部112在布线层l31中是由钨(w)形成的。

181.此时,在制造接触部112的同时,宽的焊盘111也被制造以作为引线接合用焊盘。这里,在接触部112和焊盘111的制造过程中,氧化物膜被形成于布线层l31(在该布线层中,通过cvd方法用w制成了布线)的一部分中,接着通过光刻而被图案化,然后通过干式蚀刻而在所需的图案化部分中形成开口。然后,在该开口部分中通过cvd方法用w形成膜,通过cmp方法除去不必要的部分,且因此形成了接触部112和焊盘111。

182.在制造出焊盘111之后执行配线层32中的cu布线的制造过程时,在直到接合表面的各布线层中按顺序地如上所述把用来保护焊盘111的各层cu焊盘形成为布线。

183.此外,在保护焊盘111的拐角和侧边的时候,以与上侧基板21中的方式相同的方式,还在下侧基板22中在si基板41与其跟上侧基板21的接合表面之间也制造出用来保护焊盘111的cu焊盘(cu布线)。

184.接近于si基板41的布线层中的cu布线利用绝缘膜而与si基板41电气隔离,以防止与si基板41的电接触。

185.当制造出了上侧基板21和下侧基板22时,把上侧基板21和下侧基板22接合在一起,并且进一步制造出焊盘111的开口op21,与焊盘111的引线接合是通过该开口op21而被实施的。

186.如上所述,根据半导体装置101,不必经历特别的布线过程,通过在用与焊盘111相同的材料(金属)来制作接触部112的同时制作焊盘111,就能够更简单地制造出引线接合用焊盘111。结果,能够以更少的步骤制造出半导体装置101。

187.第四实施例

188.半导体装置制造工艺的说明

189.应当注意的是,尽管上面已经说明了在使上侧基板21和下侧基板22接合之前在制造上侧基板21的步骤中制造出引线接合用和探测用焊盘的示例,但是该焊盘也可以在上侧基板21和下侧基板22的接合之后才被形成。

190.下面,将参照图12和图13来说明当在上侧基板21和下侧基板22的接合之后形成焊盘时的半导体装置制造工艺。应当注意的是,与图3中的元件对应的图12和图13中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

191.图12和图13中所示的示例是在上侧基板21和下侧基板22的接合之后形成引线接合用焊盘的过程的示例和在片上透镜33和彩色滤光片34的形成之前形成引线接合用焊盘的示例。

192.首先,如图12中的箭头q91所示,在构成上侧基板21的si基板31上形成配线层32。此时,用于焊盘开口形成过程的停止层141与cu布线一起被形成于包括多个布线层的配线层32中的布线层l41中。例如,cu布线142被形成于布线层l41中。

193.此外,cu焊盘(布线)被形成于该图的配线层32中的位于布线层l41上侧上的各层(即,位于接合表面侧的各个布线层)中,以便保护将要被形成于停止层141这个部分中的金属焊盘。这里,用来保护金属焊盘的cu焊盘被设置成具有例如图2中所示的形状的焊盘,并且被形成于下侧基板22的接合表面与停止层141之间的各布线层中。

194.此外,当制造出上侧基板21时,也以相同的方式制造出下侧基板22。然后,如箭头q92所示,使上侧基板21和下侧基板22彼此相对且相互接合。具体地,把构成上侧基板21的配线层32和构成下侧基板22的配线层42布置成彼此面对,把上侧基板21和下侧基板22的彼此面对的cu部分接合在一起,并且把上侧基板21和下侧基板22的彼此面对的绝缘膜部分接合在一起。

195.在上侧基板21和下侧基板22被接合在一起之后,使si基板31减薄。

196.在由箭头q92所示出的示例中,绝缘膜43被设置于下侧基板22中的其中配线层42与si基板41发生接触的部分的一部分中。此外,在配线层32的停止层141与配线层42的绝缘膜43之间的各层中设置有由cu形成的、且用来保护引线接合用焊盘的焊盘,并且这些焊盘借助于绝缘膜43来与si基板41绝缘。换言之,在停止层141与绝缘膜43之间设置有焊盘组143,所述焊盘组143包括多层cu焊盘且用来保护被形成于停止层141中的金属焊盘。

197.设置于停止层141与绝缘膜43之间的那些cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上的形状被设定成图2中的由箭头q22所示出的焊盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

198.通过如上所述将cu焊盘设置于引线接合用焊盘的下侧,该简单构造能够提高抗裂性。

199.此外,利用这样的构造,引线接合用或探测用的金属焊盘能够被设置于上侧基板21上。结果,从si基板31至金属焊盘的深度能够被设定成比较浅,能够缩短焊盘开口形成时间,并且能够抑制引线接合不良或针接触不良的发生。

200.而且,通过如上所述地设置cu焊盘,上侧基板21和下侧基板22能够利用这些cu焊盘而被电连接。

201.在si基板31被减薄之后,如箭头q93所示,在上侧基板21中的si基板31的表面上形成抗蚀剂rg21,并且使用光刻和干式加工等技术来形成引线接合用焊盘这个部分的开口。因此,除去si基板31的局部区域、绝缘膜和停止层141,并由此形成开口op31。这个开口op31是引线接合用焊盘的连接孔(通孔)。

202.然后,如图13中的箭头q94所示,在上侧基板21的开口op31这个部分中形成绝缘膜之后,使用回蚀(etchback)等方法除去在si基板31的表面上和开口op31的底部上的该绝缘膜。结果,绝缘膜144只被设置于开口op31的侧壁部分上。

203.此外,如箭头q95所示,在开口op31中形成al膜,使用cmp等方法对该al膜进行研磨,且因此形成了引线接合用焊盘145。

204.即使在布线层l41中混合地存在着材料不同的al焊盘145和cu布线142等,也能够通过在上侧基板21和下侧基板22的接合之后才制造焊盘145来简单地制造出焊盘145。

205.在制造出焊盘145之后,如箭头q96所示,在上侧基板21上形成片上透镜33和彩色滤光片34,且因此形成了具有上侧基板21和下侧基板22的半导体装置151。然后,将球块146放置在焊盘145的底部以实施引线接合。

206.通过在上侧基板21中制作停止层141、然后在上侧基板21和下侧基板22的接合之后除去该停止层141并且制作焊盘145,能够把引线接合用焊盘的收纳用插口(receptacle)制作于上侧基板21内的诸如第一布线层等任意给定布线层中。

207.第五实施例

208.半导体装置制造工艺的说明

209.此外,可以按如下方式来形成引线接合用焊盘,该方式是:在将上侧基板21和下侧基板22接合在一起之前,形成贯穿通孔(贯穿硅通孔或tsv(through

‑

silicon via))(即,将会充当接触部的结构),并且在所述接合之后削切该贯穿通孔(接触部)。在这种情况下,不需要在基板接合之后而被执行的严峻工艺的期间内钻出一个深孔,就能够形成引线接合用焊盘。

210.下面,将参照图14至图16来说明当在上侧基板21和下侧基板22的接合之前形成将会充当贯穿通孔的结构时的半导体装置制造工艺。应当注意的是,与图3中的元件对应的图14至图16中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

211.首先,如图14中的箭头q101所示,在si基板31上形成将要充当贯穿通孔的连接孔181

‑

1和连接孔181

‑

2,并且在连接孔181

‑

1和连接孔181

‑

2的表面和si基板31的表面上形成绝缘膜182。

212.应当注意的是,当没有特别的需要来区分这些连接孔时,连接孔181

‑

1和连接孔181

‑

2还将简称为连接孔181。在由箭头q101所示出的状态中,连接孔181尚未穿透si基板31。

213.然后,如箭头q102所示,在si基板31的上方形成al膜183。因此,连接孔181被填满了al。

214.而且,如箭头q103所示,使用cmp等方法除去形成于si基板31的表面上方的al膜183,直到si基板31的表面上的绝缘膜182被除去为止。结果,获得了由填充连接孔181

‑

1的al形成的通孔184

‑

1和由填充连接孔181

‑

2的al形成的通孔184

‑

2。

215.应当注意的是,当没有特别的需要来区分这些通孔时,通孔184

‑

1和通孔184

‑

2在

下文中还将简称为通孔184。此外,尽管通孔184在这里被描述为由al(铝)形成,但是它们也能够由诸如多晶硅、钨、铜(cu)、钛、钽或钌等任意导电材料形成。

216.在如上所述地将通孔184形成于si基板31中之后,执行一般的处理。

217.也就是,如箭头q104所示,在si基板31内形成晶体管或在si基板31上层叠配线层32,以便形成上侧基板21。

218.在这一时刻,利用任何手段来避免填充连接孔181的al(即,通孔184)与配线层32发生接触。

219.在这个示例中,如箭头a21所示,用来保护引线接合用焊盘的cu焊盘被形成于配线层32的各层中,并且这些cu焊盘和通孔184利用形成于配线层32中的接触部185

‑

1和接触部185

‑

2而被电连接起来。

220.具体地,cu焊盘和通孔184

‑

1被接触部185

‑

1电连接,并且cu焊盘和通孔184

‑

2被接触部185

‑

2电连接。应当注意的是,当没有特别的需要来区分这些接触部时,接触部185

‑

1和接触部185

‑

2还将简称为接触部185。

221.此外,当制造出上侧基板21时,以相同的方式制造出下侧基板22。然后,如图15中的箭头q105所示,使上侧基板21和下侧基板22彼此面对地相互接合。

222.在由图15中的箭头q105所示出的示例中,绝缘膜43被设置于下侧基板22中的其中配线层42与si基板41发生接触的那部分的一部分中。此外,如箭头a22所示由cu形成的、且用来保护引线接合用焊盘(更具体地,被连接至该焊盘的通孔184)的焊盘被设置于配线层32内的接触部185与配线层42内的绝缘膜43之间的各层中。此外,这些cu焊盘利用绝缘膜43来与si基板41绝缘。

223.设置于接触部185与绝缘膜43之间的这些cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上的形状被设定成图2中的由箭头q22所示出的焊盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

224.通过如上所述地将cu焊盘设置于引线接合用焊盘的下侧,该简单构造能够提高抗裂性。

225.此外,利用上述构造,引线接合用或探测用的金属焊盘能够被设置于上侧基板21中。结果,能够抑制引线接合不良或针接触不良的发生。

226.此外,通过如上所述地设置cu焊盘,上侧基板21和下侧基板22能够被这些cu焊盘电连接。此外,接触部185的形状也能够是一种用来保护通孔184的形状,即,参照图2所说明的焊盘形状中的任一者。

227.在使上侧基板21和下侧基板22接合之后,如箭头q106所示,使si基板31的厚度减薄。当通过si基板31的减薄处理而刮掉si基板31的表面时,通孔184出现在si基板31的表面中。即,通孔184穿透si基板31。

228.而且,如图16中的箭头q107所示,在si基板31上形成al膜186,在该al膜186上形成抗蚀剂rg32,然后通过光刻和干式加工等技术形成焊盘。

229.因此,如箭头q108所示,引线接合用焊盘187被形成于si基板31的表面中的通孔184

‑

1和通孔184

‑

2上。此外,片上透镜33和彩色滤光片34被形成于si基板31上,且因此形成了具有上侧基板21和下侧基板22的半导体装置191。然后,将球块放置在焊盘187上以实施

引线接合。

230.通过如上所述地在构成上侧基板21的si基板31上制造出使引线接合用焊盘187与配线层32电连接的通孔184(接触部),能够简单地形成焊盘187。

231.第六实施例

232.半导体装置制造方法的说明

233.在半导体装置中,如上所述的由al等形成的金属焊盘和cu布线也能够被设置于同一层中。在这样的情况下,例如,在制作cu布线的同时制作al焊盘。jp 2012

‑

15278a中说明了该金属焊盘的制造方法。

234.然而,在jp 2012

‑

15278a中所说明的方法中,由al等形成金属焊盘与cu布线被放置处于同一层中,且因此必须使这些焊盘和cu布线设置在同一高度处。换言之,必须使由al等形成的金属焊盘和cu布线具有相同的厚度。

235.例如,如果al焊盘的高度与cu布线的高度对齐,那么al焊盘的厚度可能是不足的,并且该焊盘在引线接合的期间内可能会损坏,或者al和au的合金化可能变得不理想,这会引起连接不佳。

236.另一方面,如果用al焊盘中的足够厚度来形成cu布线,那么布线配置之间的寄生电容根据布线的高度的增加而增大,且因此由于电阻和电容而出现信号的延迟,这会导致器件操作不良。

237.此外,在这个方法中,各个过程是复杂的。

238.因此,强烈期望一种能够形成由al等制成的、具有足够厚度、且不会导致器件操作不良的金属焊盘的方法。因此,本技术使得能够利用金属掩模而更简单地制造出由al等制成的、具有足够厚度的金属焊盘,且不会导致器件操作不良。

239.下面,将参照图17来说明应用了本技术的半导体装置制造方法。应当注意的是,与图3中的元件对应的图17中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。此外,在假设引线接合用焊盘被制作为这个半导体装置中的金属焊盘的基础上继续说明。

240.首先,如箭头q111所示,制造上侧基板21和下侧基板22,并且使上侧基板21和下侧基板22彼此面对地相互接合。具体地,把构成上侧基板21的配线层32和构成下侧基板22的配线层42布置成彼此面对,把彼此面对的cu部分接合在一起,并且把彼此面对的绝缘膜部分接合在一起。

241.这里,上侧基板21包括si基板31和配线层32,配线层32包括多个布线层。此外,配线层32具有布线层l51、布线层l52和布线层l53,在布线层l51中设置有由钨(w)形成的接触部,在布线层l52中设置有cu布线,且在布线层l53中设置有al布线。

242.下侧基板22包括si基板41和配线层42。在这个示例中,绝缘膜43被设置于下侧基板22的配线层42中的其中该配线层与si基板41发生接触的那部分的一部分中。此外,如箭头a31所示,由cu形成的、且用来保护引线接合用焊盘的焊盘被设置在处于配线层32中的设置有al焊盘的那部分与配线层42中的绝缘膜43之间的各层中,并且这些焊盘利用绝缘膜43来与si基板41绝缘。

243.被设置在所述设置有al焊盘的那部分与绝缘膜43之间的cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上

的形状被设定成图2中的由箭头q22所示出的焊盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

244.通过如上所述地将cu焊盘设置于引线接合用焊盘的下侧,该简单构造能够提高抗裂性。

245.此外,利用这样的构造,引线接合用或探测用的金属焊盘能够被设置于上侧基板21上。结果,从si基板31至金属焊盘的深度能够被设定成比较浅,能够缩短焊盘开口形成时间,并且能够抑制引线接合不良或针接触不良的发生。

246.此外,通过如上所述地设置cu焊盘,上侧基板21和下侧基板22利用这些cu焊盘而被电连接。

247.在使上侧基板21和下侧基板22接合在一起之后,在si基板31的表面上形成抗蚀剂rg41,并且在抗蚀剂rg41被用作掩模的同时,形成作为连接孔的开口op41,该连接孔到达位于si基板31的下层中的诸如w、cu和al等金属。然后,如箭头q112所示,从si基板31上除去抗蚀剂rg41。

248.然后,如箭头q113所示,利用金属掩模mm11,只在上侧基板21中的与金属掩模mm11的开口对应的部分中使含有充当阻挡金属的钛(ti)或锆(zr)在内的金属形成为膜。而且,利用金属掩模mm11,只在上侧基板21中的与金属掩模mm11的开口对应的部分中形成al膜。因此,在处于开口op41内的布线层l51和布线层l52的部分中形成了引线接合用al焊盘221,且因此形成了包括上侧基板21和下侧基板22的半导体装置231。

249.然后,对如上所述而被制作的焊盘221实施引线接合。

250.这里,优选的是,使用气相沉积或pvd(物理气相沉积)方法作为阻挡金属(barrier metal)或al膜的形成方法。此外,因为当al焊盘221与si基板31发生接触时会出现绝缘不良,所以必须使金属掩模mm1的开口充分小,以致于si基板31和焊盘221不会发生彼此接触。在这个示例中,在该图中,金属掩模mm1的开口在水平方向上的宽度被设定成充分小于开口op41的宽度。

251.此外,焊盘221被形成为具有足够的厚度以跨过布线层l51和布线层l52。焊盘221的例如在该图的垂直方向上的厚度大于被设置于布线层l52中的cu布线层的厚度。

252.此外,在焊盘221与绝缘膜43之间设置有用来保护焊盘221的各个拐角和侧边的cu焊盘。特别地,这些cu焊盘的一部分被埋入到焊盘221中。

253.应当注意的是,与焊盘221发生接触的层可以是其中设置有接触部的布线层l51、其中设置有cu布线的布线层l52和其中设置有al布线的布线层l53中的任一层。此外,能够使用诸如co、ni、pd、pt或au等金属代替al来形成焊盘221,并且co、ni、pd、pt或au能够被用作阻挡金属。

254.如上所述,通过利用金属掩模mm11来形成引线接合用焊盘221,能够形成具有足够厚度的焊盘,并且能够显著提高在引线接合时的焊盘抗损坏性。

255.此外,因为不必在cu布线形成步骤的中途执行用于形成al焊盘221的步骤,所以能够以更少的步骤在设置有由其它材料(例如,cu)形成的金属布线的各层内简单地制作出引线接合用焊盘221。因此,al焊盘221的厚度能够被设定成不同于所述金属布线(例如,cu)的厚度,并且能够防止器件操作不良的发生。

256.第七实施例

257.半导体装置制造工艺的说明

258.此外,在第六实施例中,通过将金属掩模mm11的开口形成为小的开口,把由诸如al等金属形成的焊盘221设定成不与si基板31发生接触。然而,当开口op41(它是连接孔)和金属掩模mm11的开口没有准确对齐时,就会担忧al焊盘221与si基板31发生接触。

259.因此,可以采取的办法是:在开口op41中形成绝缘膜一次,并且利用回蚀除去仅位于si基板31和开口op41的底部中的该绝缘膜,只留下位于开口op41的侧面上的该绝缘膜,且因此如果随后制作焊盘221,那么能够避免与si基板31的接触。

260.下面,将参照图18和图19来说明如上所述的当制作焊盘221时的半导体装置231的制造方法。应当注意的是,与图17中的元件对应的图18和图19中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

261.首先,通过图18中的如箭头q121和箭头q122所示出的步骤在上侧基板21中形成开口op41。应当注意的是,因为如箭头q121和箭头q122所示出的步骤与图17中的如箭头q111和箭头q112所示出的步骤相同,所以省略它们的说明。

262.此外,在这个示例中,以与在图17的情况下的方式相同的方式,如箭头a31所示,在位于配线层32中的其中设置有al焊盘221的那部分与配线层42中的绝缘膜43之间的各层中设置有由cu形成的、且用来保护引线接合用焊盘的焊盘。

263.然后,如箭头q123所示,在si基板31及开口op41的表面上形成绝缘膜241。

264.然后,如图19中的箭头q124所示,通过回蚀除去形成于si基板31的表面上及开口op41的底部部分上的绝缘膜241。因此,绝缘膜241只被形成于开口op41的侧面部分中。

265.此外,如箭头q125所示,利用金属掩模mm11,只在上侧基板21的与金属掩模mm11的开口对应的部分中形成al膜。因此,引线接合用al焊盘221被形成于位于开口op41内的布线层l51和布线层l52的部分中,且因此形成了包括上侧基板21和下侧基板22的半导体装置231。然后,对如上所述而被制作的焊盘221实施引线接合。

266.通过在绝缘膜241被形成于开口op41的侧面上的状态下制作焊盘221,能够避免焊盘221与si基板31的接触。

267.应当注意的是,作为阻挡金属,至少包括ti或zr的金属能够被用到al焊盘221的顶面、底面或者这两个面上。

268.此外,能够使用代替al的诸如co、ni、pd、pt或au等金属来形成焊盘221,并且co、ni、pd、pt或au能够被用作阻挡金属。此外,尽管使用sio2作为绝缘膜241是优选的,但是也能够使用由sin或sioch等形成的膜。

269.如上所述,通过在开口op41的侧面上形成绝缘膜241且利用金属掩模mm11来形成引线接合用焊盘221,能够形成具有足够厚度的焊盘,并且能够显著提高在引线接合时的焊盘抗损坏性。此外,能够避免焊盘221与si基板31的接触。

270.此外,因为不必在cu布线形成步骤的中途执行用于形成al焊盘221的步骤,所以能够以更少的步骤在设置有由其它材料(例如,cu)形成的金属布线的各层内简单地制作出引线接合用焊盘221。因此,al焊盘221的厚度能够被设定成不同于所述金属布线(例如,cu)的厚度,并且能够防止器件操作不良的发生。

271.第八实施例

272.半导体装置的构造示例

273.通过形成其中在al布线中埋入有cu布线的引线接合用焊盘,能够进一步实现焊盘开口的宽度与深度之间的纵横比的减小和由于削减al布线层所造成的低的高度。在这样的情况下,例如如图20所示来构造出半导体装置。应当注意的是,与图3中的元件对应的图20中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

274.半导体装置271具有被接合在一起的上侧基板21和下侧基板22,并且该图中的在上侧基板21与下侧基板22之间的虚线表示上侧基板21和下侧基板22的接合表面。

275.上侧基板21包括si基板31和配线层32,且片上透镜33和彩色滤光片34被设置于该图中的si基板31的上侧上。此外,由al形成的引线接合用焊盘281被设置在上侧基板21中的开口op51的底部处,并且cu布线282被埋入到焊盘281中。

276.此外,下侧基板22包括si基板41和配线层42,并且绝缘膜43被设置于配线层42中的其中该配线层与si基板41发生接触的那部分的一部分中。

277.同样在半导体装置271中,如箭头a41所示,在位于配线层32中的引线接合用焊盘281与配线层42中的绝缘膜43之间的各层中设置有由cu形成的、且用来保护焊盘281的焊盘。

278.具体地,与cu布线282电连接且用于保护焊盘281的cu焊盘被设置于该图中的焊盘281下面的布线层中。此外,在该图中的cu焊盘下面的布线层中,用来进一步保护用于保护焊盘281的那些cu焊盘的cu焊盘被设置于上一层cu焊盘的至少拐角部分中。以这种方式,在焊盘281与绝缘膜43之间的各布线层中,用来保护位于上层中的焊盘的焊盘被设置于所述位于上层中的焊盘的至少拐角部分中。换言之,用来保护焊盘281的焊盘被层叠着。

279.各层中的cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上的形状被设定成图2中的由箭头q22所示出的焊盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

280.通过如上所述将cu焊盘设置于该图中的焊盘281的下侧,能够简单地提高抗裂性。此外,利用这样的构造,引线接合用或探测用的金属焊盘能够被设置于上侧基板21上。结果,从si基板31至金属焊盘的深度能够被设定成比较浅,能够缩短焊盘开口形成时间,并且能够抑制引线接合不良或针接触不良的发生。

281.此外,在半导体装置271中,上侧基板21和下侧基板22利用用于保护焊盘281的cu焊盘而被电连接。

282.在半导体装置271中,如该图中的下侧所示,焊盘281被设置成跨过布线层l61和布线层l62。应当注意的是,下侧的这个图是半导体装置271中的方形区域fa11的放大图。

283.在形成有焊盘281的布线层l61中设置有使上侧cu布线与下侧cu布线电连接的通孔,并且在布线层l62中设置有cu布线。

284.此外,埋入到al焊盘281中的cu布线282被设置于里面设置有其它cu布线的布线层l62中。通过以这种方式将cu布线282埋入到焊盘281中来形成引线接合用焊盘281,不必提供用来设置引线接合用焊盘的al布线层,并且半导体装置271能够被设定成具有低的高度。此外,因为焊盘281能够被设置于靠近si基板31的布线层中,所以能够使开口op51的宽度与深度之间的纵横比减小。

285.应当注意的是,尽管在这个示例中紧邻地设置于焊盘281下面的cu焊盘不是被设置于焊盘281的拐角部分处,但是紧邻于焊盘281下面的cu焊盘被设置在处于该cu焊盘的上

一层中的cu布线282的拐角部分处,且因此cu布线282被保护着。于是,通过把这个结构中的直到绝缘膜43为止的用来保护焊盘281的焊盘层叠起来,能够提高抗裂性。

286.半导体装置制造工艺的说明

287.接下来,将参照图21和图22来说明半导体装置271(特别地,焊盘281这个部分)的制造方法。应当注意的是,与图20中的元件对应的图21和图22中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。此外,图20中所示的半导体装置271的布线结构在图21和图22中被简化,以便更容易理解这两幅图。

288.首先,如图21中的箭头q131所示,在cu布线被形成于构成上侧基板21中的配线层32的给定布线层中之前,先形成al膜311,该al膜311是引线接合用焊盘281的焊盘材料,并且在该al膜311的表面上形成抗蚀剂rg51。

289.然后,如箭头q132所示,执行光刻和干式蚀刻,且因此形成了将要埋入有cu布线282的凹槽312,然后除去抗蚀剂rg51。

290.这里,尽管其中将要形成有引线接合用焊盘281的层可以是任何布线层(只要该层与cu布线的材料相同即可),但是考虑到减小焊盘281的开口op51的宽度与深度之间的纵横比的方面,较低侧的布线层(即,靠近si基板31的布线层)是优选的。

291.在形成凹槽312之后,通过光刻和干式蚀刻来处理al膜311以设定引线接合用焊盘所必需的布局,且因此形成焊盘281。

292.换言之,如箭头q133所示,在抗蚀剂rg52被涂敷到al膜311的整个表面上且执行光刻之后,留下抗蚀剂rg52的一部分。然后,在干式蚀刻中处理al膜311,且因此如箭头q134所示,形成al焊盘281。

293.进一步,如箭头q135所示,要作为cu布线层的层间绝缘膜313被形成于焊盘281之上,并且通过cmp使层间绝缘膜313平坦化,直到如箭头q136所示,获得在层叠各布线层时所必需的平坦化程度。

294.然后,如箭头q137所示,形成了凹槽314和凹槽315,凹槽314处于该图中的al焊盘281的上侧上,所述al焊盘281具有其中将要埋入有cu布线282的凹槽312,凹槽315用于将要被形成于该同一布线层中的cu布线,并且所埋入的cu布线是通过镶嵌方法而被形成的。

295.换言之,如图22中的箭头q138所示,阻挡金属和cu膜316被形成于凹槽314和凹槽315中,然后如箭头q139所示,处理该cu膜316以形成cu布线282和另一个cu布线317。

296.然后,形成用来保护焊盘281的cu焊盘的布线,并且制作直到接合表面为止的用于构成配线层32的各布线层。在如上所述而获得了上侧基板21之后,在制作用来保护焊盘281的拐角和侧边的cu布线结构的同时,也制造出下侧基板22。此时,下侧基板22中的si基板41利用绝缘膜43来与用于保护焊盘281的cu焊盘电气隔离,以避免电接触。

297.而且,在将上侧基板21和下侧基板22接合在一起之后,形成开口op51,或者形成片上透镜33和彩色滤光片34,且因此形成了半导体装置271。

298.通过如上所述地制作出其中埋入有cu布线282的焊盘281,实现了焊盘281的开口的纵横比的减小和半导体装置271的低的高度。

299.第八实施例的变形例1

300.半导体装置制造工艺的说明

301.此外,尽管在第八实施例中假定了靠近焊盘281而设置着的保护用cu焊盘不是被

设置在焊盘281的拐角或侧边处的构造,但是保护用焊盘能够被设置于焊盘281的拐角或侧边处。

302.在这样的情况下,上侧基板21是例如如图23和图24所示而被制造的。应当注意的是,与图21和图22中的元件对应的图23和图24中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

303.首先,如图23中的箭头q141至箭头q144所示,形成且处理al膜311(它是焊盘材料),并且形成焊盘281。然后,如箭头q145和箭头q146所示,形成层间绝缘膜313,且使它平坦化。应当注意的是,因为由箭头q141至箭头q146所示出的步骤与由图21中的箭头q131至箭头q136所示出的步骤相同,所以将省略它们的说明。

304.然后,如箭头q147所示,形成了凹槽341和凹槽315,凹槽341处于该图中的al焊盘281的上侧上,所述al焊盘281具有其中将要埋入有cu布线的凹槽312,凹槽315用于将要被形成于该同一布线层中的cu布线,并且所埋入的cu布线是通过镶嵌方法而被形成的。

305.换言之,如图24中的箭头q148所示,阻挡金属和cu膜316被形成于凹槽341和凹槽315中,然后如箭头q149所示,处理该cu膜316以形成cu布线343和另一个cu布线317。

306.这里,在由图23中的箭头q147至图24中的箭头q149所示出的步骤中,只有凹槽341的形状(即,cu布线343的形状)不同于由图21中的箭头q137至图22中的箭头q139所示出的步骤中的形状,并且其它方面都是相同的。

307.从参照图23和图24所说明的制造过程而获得的cu布线343的一部分被埋入到引线接合用焊盘281中,并且焊盘281的位于cu布线343侧的整个表面都与cu布线343接触。也就是说,cu布线343的没有被埋入到焊盘281中的部分起到如下cu焊盘的作用:该cu焊盘被设置于与焊盘281的下侧基板22侧相邻的布线层中且用于保护焊盘281。

308.因此,当在焊盘281上实施引线接合或探测时,焊盘281中的集中了载荷的部分(即,焊盘281的拐角或侧边)被cu布线343加固(保护),且因此能够抑制开裂。

309.第八实施例的变形例2

310.半导体装置制造工艺的说明

311.在第八实施例的变形例1中,包括焊盘281的拐角或侧边在内的整个焊盘281被假定为具有将要被cu布线343保护的形状。除此之外,通过在用来保护焊盘281的cu布线(保护用焊盘)的中央部分处适度地设置不包含cu的部分,即使当该焊盘的面积较大时,也能够抑制由于cu镶嵌(cmp)而造成的凹陷的发生。

312.在这样的情况下,上侧基板21是例如如图25和图26所示而被制造的。应当注意的是,与图23和图24中的元件对应的图25和图26中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

313.首先,如图25中的箭头q151至箭头q154所示,形成且处理al膜311(它是焊盘材料),并且在构成上侧基板21中的配线层32的给定布线层中形成焊盘281。然后,如箭头q155和箭头q156所示,形成层间绝缘膜313,且使它平坦化。应当注意的是,因为由箭头q151至箭头q156所示出的步骤与由图23中的箭头q141至箭头q146所示出的步骤相同,所以将省略它们的说明。

314.然后,如箭头q157所示,形成了凹槽371和凹槽315,凹槽371处于该图中的al焊盘281的上侧上,所述al焊盘281具有其中将要埋入有cu布线的凹槽312,凹槽315用于将要被

形成于该同一布线层中的cu布线,并且所埋入的cu布线是通过镶嵌方法而被形成的。

315.换言之,如图26中的箭头q158所示,阻挡金属和cu膜316被形成于凹槽371和凹槽315中,然后如箭头q159所示,处理该cu膜316以形成cu布线382和另一个cu布线317。

316.这里,在由图25中的箭头q157至图26中的箭头q159所示出的步骤中,只有凹槽371的形状(即,cu布线382的形状)不同于由图23中的箭头q147至图24中的箭头q149所示出的步骤中的形状,并且其它方面都是相同的。

317.从参照图25和图26所说明的制造过程而获得的cu布线382的一部分被埋入到引线接合用焊盘281中,并且焊盘281的包括其位于cu布线382侧的表面上的拐角和侧边在内的局部区域与cu布线382处于接触状态。也就是说,cu布线382中的没有被埋入到焊盘281中的部分起到如下的cu焊盘的作用:该cu焊盘被设置于与焊盘281的下侧基板22侧相邻的布线层中且用于保护焊盘281。

318.因此,当在焊盘281上实施引线接合或探测时,焊盘281中的集中了载荷的部分(即,焊盘281的拐角或侧边)被cu布线382加固(保护),且因此能够抑制开裂。

319.而且,不包含cu(该cu是cu布线382的材料)的部分(即,其中埋入有层间绝缘膜313的部分)被设置于cu布线382的与焊盘281侧相反的一侧的表面上。因此,在cu布线382的表面上的cu部分的面积能够被设定成比较小,并且能够抑制凹陷的发生。特别地,如果在上侧基板21或下侧基板22中在上侧基板21和下侧基板22的接合表面部分中设置有像cu布线382一样、在表面的中央部分的一部分中具有不包含cu的部分的cu布线(焊盘),那么上侧基板21和下侧基板22能够更稳固地被接合在一起。

320.第九实施例

321.半导体装置的构造示例

322.下面将会说明应用了本技术的半导体装置的又一个实施例。

323.图27是示出了本技术适用的半导体装置的实施例的构造示例的图。应当注意的是,与图3中的元件对应的图27中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

324.图27中所示的半导体装置411具有被接合在一起的上侧基板21和下侧基板22,并且该图中的上侧基板21与下侧基板22之间的虚线表示上侧基板21和下侧基板22的接合表面。

325.上侧基板21包括si基板31和配线层32,并且片上透镜33和彩色滤光片34被设置于该图中的si基板31的上侧上。

326.此外,由al形成的焊盘421和由al形成的另一个焊盘422被设置于包括多个布线层的配线层32中的预定布线层中。这里,焊盘421被设定成引线接合用或探测用焊盘。

327.此外,下侧基板22包括si基板41和配线层42,并且绝缘膜43被设置于配线层42中的其中该配线层与si基板41发生接触的那部分的一部分中。

328.同样在半导体装置411中,如箭头a51所示,由cu形成的用来保护焊盘421的焊盘被设置于配线层32中的用于引线接合等用途的焊盘421与配线层42中的绝缘膜43之间的各层中。

329.各层中的cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上的形状被设定成图2中的由箭头q22所示出的焊

盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

330.通过如上所述而简单地将cu焊盘设置于该图中的焊盘421的下侧,能够提高抗裂性。此外,利用这样的构造,引线接合用或探测用的金属焊盘能够被设置于上侧基板21上。结果,从si基板31至金属焊盘421的深度能够被设定成比较浅,能够缩短焊盘开口形成时间,并且能够抑制引线接合不良或针接触不良的发生。

331.此外,在半导体装置411中,上侧基板21和下侧基板22利用用来保护焊盘421的cu焊盘而被电连接。

332.此外,在半导体装置411中,cu焊盘423和cu焊盘424以彼此面对的方式分别被设置于上侧基板21的接合表面和下侧基板22的接合表面上,且因此上侧基板21中的焊盘423和下侧基板22中的焊盘424以cu

‑

cu接合的方式被接合在一起。

333.在这个示例中,因为焊盘423通过cu通孔而直接地被电连接至焊盘422,所以焊盘422通过焊盘423和焊盘424而被电连接至下侧基板22中的cu布线。

334.半导体装置制造工艺的说明

335.这里,将参照图28至图32来说明半导体装置411的制造过程。应当注意的是,与图27中的元件对应的图28至图32中的元件将会被赋予相同的附图标记,并且将适当地省略它们的说明。

336.首先,由图28中的箭头q161所示出的下侧基板22是具有逻辑电路的基板,其具有针对于多个mos晶体管(未图示)的元件隔离区或源/漏区域。此外,下侧基板22具有诸如多层布线451和层间绝缘膜452等用于信号处理的逻辑电路。

337.在这个示例中,在设置于下侧基板22的si基板41上的配线层中形成有四个cu布线层以作为多层布线451,并且假定最上层相当于半全局层(semi

‑

global layer)和相当于全局层。

338.然后,如箭头q162所示,在该图中的层间绝缘膜452的上侧上,用来形成接合用cu焊盘的阻挡绝缘膜453由例如厚度为0.01μm至0.5μm的p

‑

sin或p

‑

sicn形成。进一步,在阻挡绝缘膜453的表面上,另一个层间绝缘膜454由厚度大约为0.3μm至5μm的sio2形成。

339.应当注意的是,尽管p

‑

sin或p

‑

sicn被举例为阻挡绝缘膜453,但是也可以使用具有钝化性能的其它膜材料。此外,尽管这里氧化物膜被举例为层间绝缘膜454,但是例如氢倍半硅氧烷(hsq:hydrogen silsesquioxane)或它的层叠体可以被用于层间绝缘膜454作为氮化物膜、氮氧化物膜(sion)或无机涂布型绝缘膜。

340.然后,如图29中的箭头q163所示,用于与上侧基板21接合的cu焊盘的凹槽455

‑

1至凹槽455

‑

5被形成为开口。应当注意的是,当没有特别的需要来区分这些凹槽时,凹槽455

‑

1至凹槽455

‑

5还将简称为凹槽455。

341.此外,在形成凹槽455的开口的同时,也形成连接孔456

‑

1至连接孔456

‑

6的开口,所述连接孔456

‑

1至连接孔456

‑

6用于与诸如位于凹槽455的下层中的多层布线451等cu多层布线接合。应当注意的是,当没有特别的需要来区分这些连接孔时,连接孔456

‑

1至连接孔456

‑

6还将简称为连接孔456。

342.此外,尽管这里没有图示中间过程,但是可以按如下方式来执行处理。即,例如,首先使用双镶嵌加工方法来使凹槽455形成图案,并且使用干式蚀刻来执行开口形成处理直到到达阻挡绝缘膜453的中间。然后,在使凹槽455形成图案之后,同时执行凹槽455及连接

孔456的开口形成处理直到到达作为下层的cu层。

343.应当注意的是,凹槽455被形成为具有0.15μm至3μm的深度和大约0.3μm至10μm的宽度。此外,凹槽455的间距(即,在该图的水平方向上的相邻凹槽455之间的距离)被设定成0.6μm以上。

344.此外,连接孔456被形成为具有大约0.2μm至5μm的深度和大约0.1μm至3μm的宽度。

345.此外,在一个示例中,连接孔456的干式蚀刻处理的干燥条件被设定如下:温度是室温;压强是50mtorr至100mtorr;源功率是1000w至2000w;八氟环丁烷(c4f8)、氩气(ar)和氧气(o2)的气体流量比是c4f8:ar:o2=9:1:1;并且基板偏置是50w至300w。

346.这里,尽管假定了蚀刻被执行至阻挡绝缘膜453的中间,但是该蚀刻可以在层间绝缘膜454的中间处停止。此外,优选的是在如下条件的示例中加工凹槽455:室温;压强是50mtorr至150mtorr;源功率是500w至3000w;处理气体八氟环戊烯(c5f8)、氩气(ar)和氧气(o2)的气体流量比是c5f8:ar:o2=6:1:1;并且基板偏置是500w至2000w。

347.然后,如箭头q164所示,镀cu膜被形成以作为已形成开口的凹槽455和连接孔456中的厚度大约为0.5μm至3μm的金属膜457。

348.此外,尽管没有图示,但是阻挡金属膜或cu片膜被布置于层间绝缘膜454与金属膜457之间。然后,使用例如cmp方法从上层除去不必要的镀cu膜以及阻挡金属膜和层间绝缘膜454的一部分,且因此该层被平坦化。层间绝缘膜454被除去直至具有大约0.05μm至0.5μm的厚度。

349.因此,形成了例如接合用的cu焊盘424。

350.应当注意的是,在上侧基板21和下侧基板22被接合之后,充当引线接合用焊盘(例如,图27中所示的焊盘421)的下层的区域具有如上所述在引线接合时用来稳固地保护接合表面的结构。

351.通过以上这些步骤,下侧基板22被制造出来。

352.接下来,将说明上侧基板21的制造。如图30中的箭头q165所示,两个cu布线层和一个al层被形成于si基板31上。

353.构成上侧基板21的si基板31具有均未图示的光电二极管、像素晶体管或传输晶体管的源极和漏极,并且具有处于周边的由cu布线形成的多层布线481及层间绝缘膜482。

354.此外,金属焊盘483、421和422被设置于多层布线481上,金属焊盘483、421和422用于引线接合且是能够与cu焊盘连接的。焊盘483由例如al、ti、tin、ta或tan等构成,并且被设置成具有大约0.3μm至2μm的高度、大约2μm至800μm的宽度和0.6μm以上的布线间距。

355.然后,如箭头q166所示,在金属焊盘483和421上形成厚度为大约0.3μm至5μm的由sio2等形成的层间绝缘膜484。应当注意的是,尽管这里层间绝缘膜484被举例为由例如sio2膜形成,但是该膜可以由能够使金属焊盘绝缘且容易平坦化的任何材料(例如,p

‑

sin)形成。

356.然后,如箭头q167所示,使用cmp方法使形成在金属焊盘上的层间绝缘膜484的涂敷台阶485变得平坦化,以便将层间绝缘膜484的表面处理成平面的。

357.而且,如图31中的箭头q168所示,与下侧基板22接合的cu焊盘中的凹槽486

‑

1至凹槽486

‑

8在层间绝缘膜484中被形成开口。应当注意的是,当没有特别的需要来区分这些凹槽时,凹槽486

‑

1至凹槽486

‑

8还将简称为凹槽486。

358.此外,在形成凹槽486的开口的同时,也形成与位于凹槽486的下层中的多层布线接合的连接孔487

‑

1至连接孔487

‑

6的开口。应当注意的是,当没有特别的需要来区分这些连接孔时,连接孔487

‑

1至连接孔487

‑

6还将简称为连接孔487。

359.此外,尽管这里没有图示中间过程,但是可以按如下方式来执行处理。即,例如,首先使用双镶嵌加工方法使连接孔487形成图案,并且使用干式蚀刻来执行开口形成处理直到到达焊盘483上方的层间绝缘膜484。然后,在使凹槽486形成图案之后,同时执行凹槽486及连接孔487的开口形成处理直到到达金属焊盘。

360.应当注意的是,凹槽486被形成为具有0.15μm至3μm的深度和大约0.3μm至10μm的宽度。此外,凹槽486的间距(即,在该图的水平方向上的相邻凹槽486之间的距离)被设置成0.6μm以上。

361.此外,连接孔487被形成为具有大约0.2μm至5μm的深度和大约0.1μm至3μm的宽度。

362.此外,在一个示例中,连接孔487的干式蚀刻处理的干燥条件被设定如下:温度是室温;压强是50mtorr至100mtorr;源功率是1000w至2000w;八氟环丁烷(c4f8)、氩气(ar)和氧气(o2)的气体流量比是c4f8:ar:o2=9:1:1;并且基板偏置是50w至300w。

363.这里,尽管假定蚀刻被执行到金属焊盘483的顶部,但是该蚀刻可以在层间绝缘膜484的中间处停止。此外,优选的是在如下条件的示例中加工凹槽486:室温;压强是50mtorr至150mtorr;源功率是500w至3000w;处理气体八氟环戊烯(c5f8)、氩气(ar)和氧气(o2)的气体流量比是c5f8:ar:o2=6:1:1;并且基板偏置是500w至2000w。

364.然后,如箭头q169所示,镀cu膜被形成为在已形成开口的凹槽486和连接孔487中厚度为大约0.5μm至3μm的金属膜488。

365.此外,尽管没有图示,但是阻挡金属膜或cu片膜被布置于层间绝缘膜484与金属膜488之间。然后,使用例如cmp方法从上层除去不必要的镀cu膜以及阻挡金属膜和层间绝缘膜484的一部分,且因此该层被平坦化。层间绝缘膜484被除去直至具有大约0.05μm至0.5μm的厚度。

366.因此,形成了例如接合用的cu焊盘423。

367.通过以上这些步骤,上侧基板21被制造出来。

368.然后,如图32所示,使构成上侧基板21的si基板31的si减薄,并且执行上侧基板21和下侧基板22的cu

‑

cu接合。

369.因此,由al等形成的金属焊盘和接合用cu焊盘被电连接。在这个示例中,焊盘422和cu焊盘424被电连接。应当注意的是,在上侧基板21和下侧基板22被接合之后,充当引线接合用焊盘421的下层的区域具有如上所述在引线接合时用来稳固地保护接合表面的结构。换言之,作为用来保护焊盘421的cu焊盘,例如,具有参照图2所说明的形状的焊盘被设置于焊盘421的所述下层中。

370.然后,形成开口op61,或设置片上透镜33和彩色滤光片34,且因此形成了半导体装置411。

371.如上所述,在过去,上侧基板、下侧基板是使用例如tsv而被电连接的,因此引线必须从tsv绕到焊盘,这导致了tsv必须被放在芯片的拐角处的这一限制。

372.另一方面,根据半导体装置411,通过在例如al焊盘422与诸如紧邻地位于该al焊盘下面的接合用cu焊盘423等焊盘之间形成连接孔,上侧基板21和下侧基板22这两个基板

能够相互电接合。因此,缠绕用的引线是不必要的,并且不会强加对芯片布局的限制。因此,预期能够实现芯片(半导体装置411)的小型化、低功耗等。

373.第十实施例

374.半导体装置的构造示例

375.在设置有引线接合用或探测用al焊盘421的半导体装置411中,与引线接合用al焊盘421同时地在上侧基板21和下侧基板22的接合表面上的cu焊盘423的上层上形成al焊盘422。因此,cu焊盘423利用cu通孔而直接被电连接至al焊盘422的结构是可能的。

376.然而,因为cu焊盘的微细加工是先进的,所以al焊盘在设计方面是不如cu焊盘的,这意味着al的微细加工比cu难,因此,由于cu焊盘的间距被al焊盘的间距束缚的这个事实,所以很可能难以让cu焊盘具有窄间距。

377.因此,上侧基板21和下侧基板22可以利用如下的cu通孔而被电连接:这些cu通孔不是从接合表面上的cu焊盘被接地至al焊盘而是被接地至作为更高层的布线层、且具有两层以上的长度。

378.在这样的情况下,半导体装置是例如如图33所示而被构造的。应当注意的是,与图27中的元件对应的图33中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

379.图33中所示的半导体装置511具有接合在一起的上侧基板21和下侧基板22,并且该图中的上侧基板21与下侧基板22之间的虚线表示上侧基板21和下侧基板22的接合表面。

380.上侧基板21包括si基板31和配线层32,并且片上透镜33和彩色滤光片34被设置于该图中的si基板31的上侧上。

381.此外,由al形成的焊盘421被设置于包括多个布线层的配线层32中的预定布线层中。这里,焊盘421被设定成引线接合用或探测用焊盘。

382.此外,下侧基板22包括si基板41和配线层42,并且绝缘膜43被设置于配线层42中的其中该配线层与si基板41发生接触的那部分的一部分中。

383.同样在半导体装置511中,如箭头a52所示,由cu形成的用来保护焊盘421的焊盘被设置于配线层32中的用于引线接合等用途的焊盘421与配线层42中的绝缘膜43之间的各层中。

384.各层中的cu焊盘的形状被设定成例如参照图2所说明的焊盘形状。特别地,cu焊盘在上侧基板21和下侧基板22的接合表面上的形状被设定成图2中的由箭头q22所示出的焊盘cpd31、由箭头q23所示出的焊盘cpd32、由箭头q24所示出的焊盘cpd33等等的形状。

385.通过如上所述简单地将cu焊盘设置于该图中的焊盘421的下侧,能够提高抗裂性。此外,利用这样的构造,引线接合用或探测用的金属焊盘能够被设置于上侧基板21上。结果,从si基板31至金属焊盘的深度能够被设定成比较浅,能够缩短焊盘开口形成时间,并且能够抑制引线接合不良或针接触不良的发生。

386.此外,在半导体装置511中,上侧基板21和下侧基板22利用用来保护焊盘421的cu焊盘而被电连接。

387.而且,在半导体装置511中,布线用的cu焊盘521和接合用的cu焊盘522被设置于上侧基板21中,并且焊盘521和焊盘522利用穿透多个布线层的cu通孔523而被电连接。这里,焊盘521被设置在处于比引线接合用焊盘421更靠近si基板31的位置处的布线层中。

388.以相同的方式,布线用的cu焊盘524和接合用的cu焊盘525被设置于下侧基板22中,并且焊盘524和焊盘525利用穿透多个布线层的cu通孔526而被电连接。

389.此外,cu焊盘522和cu焊盘525以彼此面对的方式分别被设置于上侧基板21的接合表面和下侧基板22的接合表面上,并且焊盘522和焊盘525以cu

‑

cu接合的方式被接合在一起。

390.因此,上侧基板21中的焊盘521和下侧基板22中的焊盘524被电连接。此外,在这个示例中,因为不仅焊盘521和焊盘524而且放置在这些焊盘之间的焊盘和通孔都是由cu形成的,所以能够实现比当al等被用作材料时更先进的微细加工。

391.半导体装置制造工艺的说明

392.接下来,这里,将参照图34至图38来说明半导体装置511的制造过程。应当注意的是,与图33中的元件对应的图34至图38中的元件将会被赋予相同的附图标记,且将适当地省略它们的说明。

393.首先,由图34中的箭头q171所示出的下侧基板22是具有逻辑电路的基板,该基板具有用于多个mos晶体管(未图示)的元件隔离区或源/漏区域。此外,下侧基板22具有诸如多层布线541和层间绝缘膜542等用于信号处理的逻辑电路。

394.在这个示例中,四个cu布线层被形成为在被设置于下侧基板22中的si基板41上的配线层中的多层布线541,并且假定最上层相当于半全局层和全局层。

395.然后,如箭头q172所示,在该图中的层间绝缘膜542的上侧上,用来形成接合用的cu焊盘的阻挡绝缘膜543由例如厚度为0.01μm至0.5μm的p

‑

sin或p

‑

sicn形成。而且,在阻挡绝缘膜543的表面上,另一个层间绝缘膜544由厚度大约为0.3μm至5μm的sio2形成。

396.应当注意的是,尽管p

‑

sin或p

‑

sicn被举例为阻挡绝缘膜543,但是也可以使用具有钝化性能的其他膜材料。此外,尽管这里氧化物膜被举例为层间绝缘膜544,但是例如氢倍半硅氧烷(hsq)或它的层叠体可以被用于层间绝缘膜544作为氮化物膜、氮氧化物膜或无机涂布型绝缘膜。

397.然后,如图35中的箭头q173所示,与上侧基板21接合的cu焊盘中的凹槽581

‑

1至凹槽581

‑

8被形成开口。应当注意的是,当没有特别的需要来区分这些凹槽时,凹槽581

‑

1至凹槽581

‑

8还将简称为凹槽581。

398.此外,在形成凹槽581的开口的同时,也形成与诸如位于凹槽581的下层中的多层布线541等cu多层布线接合的连接孔582

‑

1至连接孔582

‑

5的开口。应当注意的是,当没有特别的需要来区分这些连接孔时,连接孔582

‑

1至连接孔582

‑

5还将简称为连接孔582。应当注意的是,连接孔583的深度根据其中安置有与连接孔连接的布线层的布线而不同。

399.此外,尽管这里没有图示中间过程,但是可以如下地执行处理。即,例如,首先使用双镶嵌加工方法使连接孔582和连接孔583形成图案,并且使用干式蚀刻执行开口形成处理直到到达阻挡绝缘膜543的中间。然后,在使凹槽581形成图案之后,以干式蚀刻的方式同时执行凹槽581及连接孔582和连接孔583的开口形成处理直到到达cu层。此外,可以首先使凹槽581形成开口,然后可以在具有不同深度的连接孔中的各连接孔上单独地执行图案化处理和开口形成处理。应当注意的是,尽管没有图示,但是连接孔可以被形成为直到其中设置有cu布线584的布线层。

400.这里,凹槽581被形成为具有大约0.15μm至3μm的深度和大约0.3μm至10μm的宽度。

此外,凹槽581的间距(即,在该图的水平方向上的相邻凹槽581之间的距离)被设置成0.6μm以上。

401.此外,连接孔582被形成为具有大约0.2μm至5μm的深度和0.1μm至3μm的宽度。连接孔583被形成为具有大约0.6μm至10μm的深度和0.1μm至3μm的宽度。此外,尽管在该图中示出了一个连接孔583,但是多个连接孔583是可能的。

402.此外,在一个示例中,凹槽581的干式蚀刻处理的干燥条件被设置成:温度是室温;压强是50mtorr至150mtorr;源功率是500w至3000w;八氟环戊烯(c5f8)、氩气(ar)和氧气(o2)的气体流量比是c5f8:ar:o2=6:1:1;并且基板偏置是500w至2000w。

403.此外,在一个示例中,连接孔582和连接孔583的处理条件被设置成:温度是室温;压强是50mtorr至100mtorr;源功率是1000w至2000w;八氟环丁烷(c4f8)、氩气(ar)和氧气(o2)的气体流量比是c4f8:ar:o2=9:1:1;并且基板偏置是50w至300w。

404.这里,假定蚀刻在阻挡绝缘膜543的中间被执行直到具有全部深度的连接孔被形成开口,并且在最后一个连接孔的处理之后,用于全部连接孔的阻挡绝缘膜543被破坏。用于破坏阻挡绝缘膜543的优选条件被设置成:例如,压强为50mtorr至200mtorr;源功率为300w至2000w;被用作处理气体的八氟环丁烷(c4f8)、氩气(ar)和氧气(o2)的气体流量比是c4f8:ar:o2=1:2:20;并且基板偏置是100w至2000w。

405.然后,如箭头q174所示,镀cu膜被形成为在已经形成开口的凹槽581、连接孔582和连接孔583中的厚度为大约0.5μm至3μm的金属膜585。

406.此外,尽管没有图示,但是阻挡金属膜或cu片膜被布置于层间绝缘膜544与金属膜585之间。然后,使用例如cmp方法从上层除去不必要的镀cu膜以及阻挡金属膜和层间绝缘膜544的一部分,且因此该层变得平坦化。层间绝缘膜544被除去直至具有大约0.05μm至0.5μm的厚度。

407.因此,例如,形成了接合用的cu焊盘525和通孔526。

408.应当注意的是,在上侧基板21和下侧基板22被接合之后,充当引线接合用焊盘(例如,图33中所示的焊盘421)的下层的区域具有如上所述在引线接合时用来稳固地保护接合表面的结构。

409.通过以上这些步骤,下侧基板22被制造出来。

410.接下来,将说明上侧基板21的制造。如图36中的箭头q175所示,两个cu布线层和一个al层被形成于si基板31上。

411.上侧基板21具有均未图示的光电二极管、像素晶体管或传输晶体管的源极和漏极,并且具有处于周边的由cu布线等形成的多层布线611和层间绝缘膜612。

412.然后,引线接合用金属焊盘421被设置于多层布线611上,即,在al层中。焊盘421由例如al、ti、tin、ta或tan等形成,且具有大约0.3μm至2μm的高度、大约2μm至800μm的宽度和0.6μm以上的布线间距。此外,焊盘421通过通孔613而被连接至cu布线。

413.然后,如箭头q176所示,在金属焊盘421上形成具有大约0.3μm至5μm的厚度的由sio2等形成的层间绝缘膜614。应当注意的是,尽管这里层间绝缘膜614被举例为由例如sio2膜形成,但是该膜可以由能够隔离金属焊盘且容易变平坦化的任何材料(例如,p

‑

sin)形成。

414.然后,如箭头q177所示,使用cmp方法使形成于金属焊盘上的层间绝缘膜614的涂

敷台阶617变得平坦,以便将层间绝缘膜614的表面处理成平面的。

415.而且,如图37中的箭头q178所示,与下侧基板22接合的cu焊盘中的凹槽641

‑

1至凹槽641

‑

8在层间绝缘膜614中被形成开口。应当注意的是,当没有特别的需要来区分这些凹槽时,凹槽641

‑

1至凹槽641

‑

8还将简称为凹槽641。

416.此外,在形成凹槽641的开口的同时,也形成与位于凹槽641的下层中的多层布线接合的连接孔642

‑

1至连接孔642

‑

4、连接孔643

‑

1、连接孔643

‑

2和连接孔644的开口。

417.应当注意的是,当没有特别的需要来区分这些连接孔时,连接孔642

‑

1至连接孔642

‑

4还将简称为连接孔642。此外,当没有特别的需要来区分这些连接孔时,连接孔643

‑

1和连接孔643

‑

2还将简称为连接孔643。

418.此外,尽管这里没有图示中间过程,但是可以如下地执行处理。即,例如,首先使用双镶嵌加工方法使连接孔642至连接孔644形成图案,并且使用干式蚀刻执行开口形成处理直到到达在焊盘421上面的层间绝缘膜614或没有图示的紧邻地位于布线645或焊盘521(布线)上面的阻挡绝缘膜的中间处。然后,在使凹槽641形成图案之后,使用干式蚀刻同时执行凹槽641和连接孔642至连接孔644的开口形成处理。

419.应当注意的是,凹槽641可以首先被形成开口,然后可以对具有不同深度的各连接孔单独地执行图案化和开口形成处理。

420.这里,凹槽641被形成为具有大约0.15μm至3μm的深度和大约0.3μm至10μm的宽度。此外,凹槽641的间距(即,在该图的水平方向上的相邻凹槽641之间的距离)被设置成0.6μm以上。

421.此外,连接孔642和643被形成为具有大约0.2μm至5μm的深度和0.1μm至3μm的宽度。连接孔644被形成为具有大约0.6μm至10μm的深度和0.1μm至3μm的宽度。此外,尽管在该图中示出了一个连接孔644,但是多个连接孔644是可能的。

422.此外,在一个示例中,凹槽641的干式蚀刻处理的干燥条件被设置成:温度是室温;压强是50mtorr至150mtorr;源功率是500w至3000w;八氟环戊烯(c5f8)、氩气(ar)和氧气(o2)的气体流量比是c5f8:ar:o2=6:1:1;并且基板偏置是500w至2000w。

423.此外,在一个示例中,连接孔642至连接孔644的处理条件被设置成:温度是室温;压强是50mtorr至100mtorr;源功率是1000w至2000w;八氟环丁烷(c4f8)、氩气(ar)和氧气(o2)的气体流量比是c4f8:ar:o2=9:1:1;并且基板偏置是50w至300w。

424.这里,假定蚀刻在位于焊盘421的上层中的没有图示的阻挡绝缘膜的中间或在布线645或焊盘521的没有图示的阻挡绝缘膜中被执行直到具有全部深度的连接孔被形成开口,并且在最后一个连接孔的处理之后,用于全部连接孔的阻挡绝缘膜被破坏。

425.用于破坏阻挡绝缘膜的优选条件被设置成:例如,压强为50mtorr至200mtorr;源功率为300w至2000w;八氟环丁烷(c4f8)、氩气(ar)和氧气(o2)的气体流量比是c4f8:ar:o2=1:2:20;并且基板偏置是100w至2000w。

426.然后,如箭头q179所示,镀cu膜被形成为已经形成开口的凹槽641和连接孔642至连接孔644中的具有大约0.5μm至3μm的厚度的金属膜646。

427.此外,尽管没有图示,但是阻挡金属膜或cu片膜被布置于层间绝缘膜614与金属膜646之间。然后,使用例如cmp方法从上层除去不必要的镀cu膜以及阻挡金属膜和层间绝缘膜614的一部分,且因此该层变得平坦化。层间绝缘膜614被除去直至具有大约0.05μm至0.5

μm的厚度。

428.因此,例如,形成了接合用cu焊盘522和通孔523。

429.通过以上步骤,上侧基板21被制造出来。

430.然后,如图38所示,使构成上侧基板21的si基板31的si减薄,并且执行上侧基板21和下侧基板22的cu

‑

cu接合。

431.因此,由al等形成的金属焊盘和接合用cu焊盘被电连接。此外,上侧基板21中的焊盘521和下侧基板22中的焊盘524通过通孔523、焊盘522、焊盘525和通孔526而被电连接。

432.应当注意的是,在上侧基板21和下侧基板22被接合之后,充当引线接合用焊盘421的下层的区域具有如上所述在引线接合时用来稳固地保护接合表面的结构。换言之,作为用来保护焊盘421的cu焊盘,例如,具有参照图2所说明的形状的焊盘被设置于焊盘421的所述下层中。

433.然后,形成开口op61,或设置片上透镜33和彩色滤光片34,且因此形成了半导体装置511。

434.如上所述,在过去,上侧、下侧基板是使用例如tsv而被电连接的,因此引线必须从tsv绕到焊盘,这导致了tsv必须被放在芯片的拐角处的这一限制。

435.另一方面,根据半导体装置511,通过形成在例如cu焊盘521与诸如紧邻地位于al焊盘下面的接合用cu焊盘522等焊盘之间的通孔523等,上侧基板21和下侧基板22这两个基板能够被电接合。因此,缠绕用的引线是不必要的,并且不会强加对芯片布局的约束。

436.此外,在不将除了引线接合用焊盘421以外的al焊盘设置为接合用cu焊盘的连接目标的情况下,通过使该cu焊盘与位于si基板31侧的布线层中的cu布线(焊盘)连接,能够实现在设计方面比al焊盘更先进的cu焊盘的窄间距。因此,预期可以实现比第九实施例更先进的小型化、更低功耗等的芯片(半导体装置511)。

437.固体摄像器件的构造示例

438.本技术能够进一步被应用于各种各样的半导体装置,例如,其中逻辑电路被设置于上侧基板21中且存储器被设置于下侧基板22中的芯片、或者其中片上透镜33和光电二极管被设置于上侧基板21中且布线被设置于下侧基板22中的固体摄像器件。

439.图39是示出了应用了本技术的固体摄像器件的构造示例的图。

440.固体摄像器件901是由例如cmos图像传感器构成的背照射型图像传感器,接收来自被摄对象的光而用于光电转换,生成图像信号,且因此拍摄图像。

441.应当注意的是,背照射型图像传感器是通过设置如下光电二极管而被构造出来的图像传感器:该光电二极管在光接收表面(即,使光集中的片上透镜)与设置有布线(例如,驱动像素的晶体管)的布线层之间接收来自被摄对象的光,来自该被摄对象的光入射到该光接收表面上。

442.固体摄像器件901包括像素阵列部911、垂直驱动部912、列处理部913、水平驱动部914、系统控制部915、像素驱动线916、垂直信号线917、信号处理部918和数据存储部919。

443.在固体摄像器件901中,像素阵列部911被形成于没有图示的半导体基板(芯片)上,并且垂直驱动部912至系统控制部915进一步被整合在该半导体基板上。例如,假定形成有像素阵列部911的半导体基板是具有上侧基板21和下侧基板22等的半导体装置。

444.像素阵列部911是由像素构成的,各像素具有作为光电转换单元的光电二极管,该

光电二极管生成且积累取决于从被摄对象入射的光的量的电荷,并且构成像素阵列部911的像素在该图中的水平方向(行方向)和垂直方向(列方向)上呈二维状被排列着。

445.在像素阵列部911中,像素驱动线916针对由在行方向上排列的像素构成的像素行中的各行像素而在行方向上被连线,并且垂直信号线917针对由在列方向上排列的像素构成的像素列中的各列像素而在列方向上被连线。

446.垂直驱动部912是由移位寄存器、地址解码器等构成的,并且通过经由多个像素驱动线916而将信号提供给各像素,垂直驱动部912以行为单位同时驱动像素阵列部911中的全部像素,等等。

447.列处理部913经由垂直信号线917而针对像素阵列部911中的各像素列读取来自各像素的信号,执行噪声消除处理、相关双采样处理、模数(a

‑

d:analog

‑

to

‑

digital)转换处理等,并由此生成像素信号。

448.水平驱动部914是由移位寄存器、地址解码器等构成的,并且顺序地选择列处理部913中的与像素列对应的单元电路。通过利用这个水平驱动部914的选择扫描,被列处理部913中的各单元电路顺序处理的像素信号被输出至信号处理部918。

449.系统控制部915是由生成各种时序信号等的时序发生器构成的,并且基于由该时序发生器生成的时序信号而执行垂直驱动部912、列处理部913和水平驱动部914的驱动控制。

450.信号处理部918在必要时将数据暂时存储于数据存储部919中的同时,对从列处理部913提供过来的像素信号执行信号处理(例如,算术处理),并且输出由像素信号组成的图像信号。

451.本技术的实施例不局限于上述实施例,并且在不脱离本技术的范围的情况下,可以作出各种变化和修改。

452.此外,在本说明书中说明的效果不是限制性的,而仅仅是示例,并且可以展现额外的效果。

453.此外,本技术还可以如下地被构造。

454.(1)一种半导体装置,它包括:

455.第一基板,所述第一基板具有多个布线层;以及

456.第二基板,所述第二基板具有多个布线层,并且所述第二基板被接合至所述第一基板,

457.其中,在所述第一基板和所述第二基板中的一个基板中设置有焊盘,在所述焊盘与以最靠近另一个基板的方式位于所述另一个基板侧上的布线层之间在各布线层中设置有由金属形成的金属布线,并且在与所述焊盘或所述金属布线相邻的位于所述另一个基板侧上的布线层中,在处于上一层中的所述焊盘或所述金属布线的至少拐角部分处设置有其它的金属布线。

458.(2)根据(1)所述的半导体装置,其中,所述焊盘是引线接合用或探测用焊盘。

459.(3)根据(1)或(2)所述的半导体装置,其中,所述焊盘被设置于所述第一基板和所述第二基板中的用于实施引线接合或探测的那一侧的基板中。

460.(4)根据(1)至(3)中任一项所述的半导体装置,其中,所述第一基板和所述第二基板通过把设置于所述第一基板的表面上的cu布线和设置于所述第二基板的表面上的cu布

线接合起来而被接合在一起。

461.(5)根据(1)至(4)中任一项所述的半导体装置,其中,在所述金属布线的位于所述第一基板和所述第二基板的接合表面上的接合表面侧表面的中央部分处设置有不包含用于形成所述金属布线的材料的区域。

462.(6)根据(1)至(5)中任一项所述的半导体装置,其中,在所述焊盘或所述金属布线的至少侧边部分处设置有所述其它的金属布线。

463.(7)根据(1)至(6)中任一项所述的半导体装置,其中,在构成所述另一个基板且上面层叠有多个布线层的那个基板与所述金属布线之间设置有绝缘膜。

464.(8)根据(1)至(6)中任一项所述的半导体装置,其中,构成所述另一个基板且上面层叠有多个布线层的那个基板中的与所述金属布线发生接触的那部分的区域利用被埋入所述另一个基板中的绝缘体来与所述另一个基板的其它区域电气隔离。

465.(9)根据(1)至(6)中任一项所述的半导体装置,其中,在形成有接触部的布线层中,所述焊盘由与所述接触部相同的金属形成,所述接触部用于使构成所述一个基板且上面层叠有多个布线层的那个基板与设置于所述一个基板中的布线层中的布线连接。

466.(10)根据(1)至(6)中任一项所述的半导体装置,其中,在所述第一基板和所述第二基板的接合之后,所述焊盘被形成在停止层这个部分中,所述停止层被设置于所述一个基板内的布线层中、且是通过形成开口而被除去的。

467.(11)根据(1)至(6)中任一项所述的半导体装置,它还包括:

468.被设置在构成所述一个基板且上面层叠有多个布线层的那个基板中的通孔,所述通孔穿透所述一个基板并且被连接至所述金属布线,

469.其中,所述焊盘被设置于所述一个基板的表面的所述通孔上方。

470.(12)根据(1)至(6)中任一项所述的半导体装置,其中,所述焊盘被设置于所述一个基板中的开口的一部分中,并且是通过利用具有比所述一个基板中的所述开口更窄的开口的金属掩模而被形成的。

471.(13)根据(12)所述的半导体装置,其中,在所述一个基板中的所述开口的侧面上形成有绝缘膜。

472.(14)根据(1)至(6)中任一项所述的半导体装置,其中,在所述焊盘中埋入有由不同于所述焊盘的金属形成的布线,并且在位于该布线的所述另一个基板侧上的布线层中设置有所述金属布线。

473.(15)根据(14)所述的半导体装置,其中,在与所述焊盘相邻的位于所述另一个基板侧上的布线层中在所述焊盘的至少拐角部分处,所述布线被设置为所述金属布线。

474.(16)根据(15)所述的半导体装置,其中,在所述布线的表面的中央部分处设置有不包含用于形成所述布线的材料的区域。

475.(17)一种半导体装置,它包括:

476.第一基板,所述第一基板具有多个布线层;以及

477.第二基板,所述第二基板具有多个布线层,且所述第二基板被接合至所述第一基板,

478.其中,在所述第一基板中设置有:设置于跟所述第二基板接合的接合表面上的接合用cu焊盘;及穿透多个布线层且使所述接合用cu焊盘与cu布线连接的cu通孔,并且

479.其中,在所述第二基板中设置有:设置于跟所述第一基板接合的接合表面上且与所述接合用cu焊盘接合的另一个接合用cu焊盘。

480.(18)一种固体摄像器件,它包括:

481.第一基板,所述第一基板具有多个布线层;以及

482.第二基板,所述第二基板具有多个布线层,且所述第二基板被接合至所述第一基板,

483.其中,在所述第一基板和所述第二基板中的一个基板中设置有焊盘,在所述焊盘与以最靠近另一个基板的方式位于所述另一个基板侧上的布线层之间在各布线层中设置有由金属形成的金属布线,并且在与所述焊盘或所述金属布线相邻的位于所述另一个基板侧上的布线层中,在处于上一层中的所述焊盘或所述金属布线的至少拐角部分处设置有其它的金属布线。

484.附图标记列表

485.11 半导体装置

486.21 上侧基板

487.22 下侧基板

488.31 si基板

489.32 配线层

490.35 焊盘

491.41 si基板

492.42 配线层

493.43 绝缘膜

494.111 焊盘

495.184

‑

1、184

‑

2、184 通孔

496.187 焊盘

497.281 焊盘

498.282 cu布线

499.521 焊盘

500.522 焊盘

501.523 通孔

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1