半导体存储装置及其制造方法与流程

半导体存储装置及其制造方法

1.[相关申请]

[0002]

本技术享有以日本专利申请2020

‑

51576号(申请日:2020年3月23日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

[0003]

实施方式涉及一种半导体存储装置及其制造方法。

背景技术:

[0004]

作为半导体存储装置,已知有nand(not and,与非)型闪速存储器。为了使该nand型闪速存储器大容量化,采用将多个存储单元积层而成的构成的三维nand型闪速存储器已付诸实用。关于这种积层型的三维nand型闪速存储器,提高电特性成为课题。

技术实现要素:

[0005]

实施方式提供一种能够提高三维nand型闪速存储器的电特性的半导体存储装置及其制造方法。

[0006]

实施方式的半导体存储装置具备:半导体衬底;结构体,由多个绝缘膜及多个导电膜交替地积层在半导体衬底上而成;及柱状体,贯通结构体;多个导电膜包含多个第1导电膜、及配置在相比多个第1导电膜更靠半导体衬底侧的第2导电膜,柱状体与第2导电膜一起作为源极侧选择栅极晶体管的一部分发挥功能,在与半导体衬底相接的部分具有掺杂有硼与碳的第1外延生长层,且多个第1导电膜作为多个非易失性存储单元的一部分发挥功能。

附图说明

[0007]

图1是对本发明的实施方式的半导体存储装置进行说明的剖视图。

[0008]

图2是对本发明的实施方式的半导体存储装置的制造方法进行说明的剖视图。

[0009]

图3是对本发明的实施方式的半导体存储装置的制造方法进行说明的剖视图。

[0010]

图4是对本发明的实施方式的半导体存储装置的制造方法进行说明的剖视图。

[0011]

图5是表示本发明及比较例的实施方式的半导体存储装置的源极侧选择栅极晶体管的阈值电压的分布的图。

[0012]

图6是对本发明的变化例的半导体存储装置进行说明的剖视图。

具体实施方式

[0013]

以下,参照附图对本实施方式的非易失性半导体存储装置具体地进行说明。此外,在以下的说明中,对具有大致相同的功能及构成的构成要素标注相同符号,只在必要时进行重复说明。另外,以下所示的各实施方式例示用来使本实施方式的技术思想具体化的装置或方法,实施方式的技术思想并不将构成零件的材质、形状、结构、配置等特定为下述内容。实施方式的技术思想能够在权利要求书的范围内施加各种变更。

[0014]

附图有时与实际形态相比,对各部的宽度、厚度、形状等示意性地表示,以使说明更明确,但只不过是一例,并不限定本发明的解释。在本说明书与各附图中,有时对具备与关于已出现的附图所说明的要素相同的功能的要素标注相同符号,并省略重复说明。

[0015]

通过相同工艺形成的多个膜具有相同的层结构,且包含相同材料。在本说明书中,即使在多个膜发挥互不相同的功能或作用的情况下,像这样通过相同工艺形成的多个膜也分别作为存在于同一层的膜进行处理。

[0016]

[半导体存储装置的构成]

[0017]

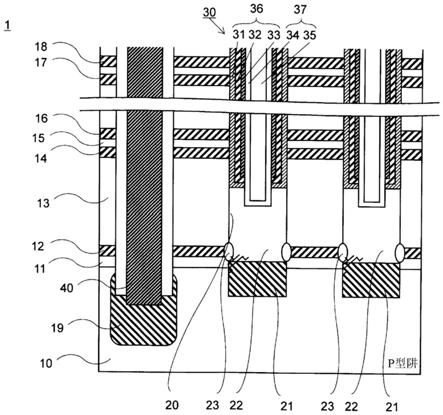

利用图1对本发明的实施方式的半导体存储装置的构成进行说明。图1是对本发明的实施方式的半导体存储装置1进行说明的剖视图。

[0018]

半导体存储装置1是nand型闪速存储器装置,包含三维配置在半导体衬底10上的存储单元。具体来说,在与半导体衬底10垂直的方向上源极侧选择栅极晶体管、多个例如64个存储单元晶体管、及漏极侧选择栅极晶体管串联连接而构成存储器串。此外,在串联连接的多个存储单元晶体管的两端或多个存储单元晶体管间当中的一部分之间也可以包含虚设单元晶体管。

[0019]

如图1所示,在半导体衬底10上配置结构体,所述结构体与半导体衬底10平行地配置且由多个导电膜及多个绝缘膜交替地积层而成。这多个导电膜对应于与存储器串的各晶体管连接的源极侧选择栅极线12、字线14、16、17、18

…

。在图1中,只表示1层源极侧选择栅极线12、4层字线14、16、17、18,但各导电膜的数量并无特别限定。在图1中,只示出存储单元区域的积层结构体的下层侧,但该积层结构体例如也延伸到引出区域。另外,虽然在图1中没有示出,但在积层结构体的上层侧配置漏极侧选择栅极线,还在积层结构体之上配置位线。半导体衬底10是配置着形成在n型区域(半导体衬底10可以是n型,也可以是设置在半导体衬底10的一部分的n型区域)中的p型阱pwell的单晶硅衬底。多个导电膜例如使用钨等导电体。多个绝缘膜例如使用二氧化硅等绝缘体。

[0020]

在贯通积层结构体的存储器孔20配置存储器柱(柱状体)30。存储器柱30的底部到达半导体衬底10的p型阱pwell,且与它电连接。存储器柱30包含第1外延生长层21、第2外延生长层22、以及栅极绝缘膜36及半导体柱37。如下所述,第1外延生长层21及第2外延生长层22是使单晶硅在使用单晶硅的半导体衬底10上外延生长而形成。第1外延生长层21是与半导体衬底10相接地配置在存储器柱30的底部。第1外延生长层21也可以局部或者全部填埋在半导体衬底10中。第2外延生长层22配置在第1外延生长层21上。栅极绝缘膜36及半导体柱37配置在第2外延生长层22上。也就是说,第2外延生长层22配置在第1外延生长层21与栅极绝缘膜36及半导体柱37之间。

[0021]

第2外延生长层22介隔绝缘体23被源极侧选择栅极线12包围,成为源极侧选择栅极晶体管的一部分。也就是说,第1外延生长层21配置在相比源极侧选择栅极线12更靠半导体衬底10侧。第1外延生长层21与第2外延生长层22的边界配置在源极侧选择栅极线12与半导体衬底10之间。

[0022]

在第1外延生长层21中掺杂有硼与碳。第1外延生长层21的硼密度优选在1

×

10

18

cm

‑3以上1

×

10

19

cm

‑3以下。通过第1外延生长层21的硼密度在所述范围内,可以确保源极侧选择栅极晶体管特性的余裕。如果第1外延生长层21的硼密度在1

×

10

18

cm

‑3以下,那么导电率降低。如果第1外延生长层21的硼密度在1

×

10

19

cm

‑3以上,那么源极侧选择栅极晶体管

的阈值电压上升。

[0023]

第1外延生长层21的碳密度优选在1

×

10

17

cm

‑3以上1

×

10

19

cm

‑3以下。通过第1外延生长层21的碳密度在所述范围内,可以抑制第1外延生长层21中的硼在(例如,之后的热步骤中)耗尽区中扩散,可以抑制源极侧选择栅极晶体管的阈值电压的分布范围扩大(阈值电压的偏差)。如果第1外延生长层21的碳密度在1

×

10

17

cm

‑3以下,那么抑制硼扩散的效果降低。如果第1外延生长层21的碳密度在1

×

10

19

cm

‑3以上,那么妨碍硼向孔的供给。

[0024]

在图5中表示本实施方式及比较例的源极侧选择栅极晶体管的阈值电压的分布。在图5中表示本实施方式的具有掺杂有硼与碳的第1外延生长层21的各源极侧选择栅极晶体管的阈值电压的分布(42)、及比较例的具有掺杂有硼(未掺杂碳)的第1外延生长层的各源极侧选择栅极晶体管的阈值电压的分布(41)。将41与42进行比较可知,本实施方式的半导体存储装置1通过具有掺杂有硼与碳的第1外延生长层21,而各源极侧选择栅极晶体管的阈值电压的偏差得到抑制,可以抑制阈值电压的分布(42)范围扩大。本实施方式的半导体存储装置1通过具有这种构成,可以抑制源极侧选择栅极晶体管的阈值电压的分布范围扩大(阈值电压的偏差),可以抑制源极侧选择栅极晶体管的漏电流。

[0025]

第1外延生长层21的硼与碳一边外延生长一边掺杂。第1外延生长层21的碳密度优选低于第1外延生长层21的硼密度。

[0026]

第2外延生长层22是几乎没有掺杂硼与碳(硼密度与碳密度在1

×

10

12

cm

‑3以下)的所谓非掺杂层(i型)。因此,第2外延生长层22的碳密度低于第1外延生长层21的碳密度。第2外延生长层22的硼密度低于第1外延生长层21的硼密度。

[0027]

在存储器孔20内部的第2外延生长层22之上配置与存储器孔20的内侧相接的栅极绝缘膜36及与栅极绝缘膜36的内侧相接的半导体柱37。半导体柱37从外周侧朝向中心侧积层有非晶或多晶硅膜34、二氧化硅膜35。栅极绝缘膜36从外周侧朝向中心侧积层有二氧化硅膜31、氮化硅膜32、二氧化硅膜33。半导体柱37介隔栅极绝缘膜36被字线14、16、17、18

…

包围,作为将载流子捕获到氮化硅膜32的非易失性存储单元的一部分发挥功能。

[0028]

在半导体衬底10的p型阱pwell中配置高浓度的n型区域19。在n型区域19之上配置并电连接有沿与半导体衬底10垂直的方向延伸的源极线40。源极线40与多个导电膜12、14、16、17、18

…

绝缘。

[0029]

[半导体存储装置的制造步骤]

[0030]

图2~4是对本发明的实施方式的半导体存储装置的制造方法进行说明的剖视图。

[0031]

如图2所示,在包含单晶硅的半导体衬底10上形成由多个sio2膜(绝缘膜)11、13、15

…

及多个si3n4膜(虚设膜)12'、14'、16'、17'、18'

…

交替地积层而成的积层结构体。这些sio2膜(绝缘膜)及si3n4膜(虚设膜)使用cvd(chemical vapor deposition,化学气相沉积)装置而沉积。

[0032]

接着,使用掩模选择性地对积层结构体进行干蚀刻,由此形成存储器孔20。存储器孔20使半导体衬底10露出。此时,存储器孔20的底面也可以形成得比半导体衬底10的上表面低。也就是说,也可以通过积层结构体的蚀刻,对半导体衬底10局部进行蚀刻。

[0033]

如图3所示,将存储器孔20底部的半导体衬底10作为晶种进行单晶硅的外延生长。单晶硅的外延生长也使用cvd装置进行,形成第1外延生长层21。与第1外延生长层21的外延生长同时地掺杂硼及碳。作为用于外延生长的si原料气体,可以使用甲硅烷(sih4)、二氯硅

烷(sih2cl2)、三氯硅烷(sihcl3)等。作为用于硼的掺杂的b原料气体,可以使用二硼烷(b2h6)等。作为用于碳的掺杂的c原料气体,可以使用四氯化碳(ccl4)等。第1外延生长层21的硼密度形成为1

×

10

18

cm

‑3以上1

×

10

19

cm

‑3以下。第1外延生长层21的碳密度形成为1

×

10

17

cm

‑3以上1

×

10

19

cm

‑3以下。在本实施方式中,第1外延生长层21从存储器孔20底部形成到多个si3n4膜(虚设膜)的最下层12'之下为止。

[0034]

如图4所示,将存储器孔20内的第1外延生长层21作为晶种进行单晶硅的外延生长。单晶硅的外延生长也使用cvd装置进行,形成与第1外延生长层21电连接的第2外延生长层22。第2外延生长层22的外延生长以非掺杂的方式,即,以第2外延生长层22的硼密度成为1

×

10

12

cm

‑3以下及第2外延生长层22的碳密度成为1

×

10

12

cm

‑3以下的方式进行。在本实施方式中,第2外延生长层22从第1外延生长层21的上表面形成到多个si3n4膜(虚设膜)的从下往上数为第2个的层之下为止。也就是说,第2外延生长层22的上表面形成为位于多个si3n4膜(虚设膜)的最下层12'与从下往上数为第2个的层14'之间。

[0035]

虽然图中没有示出,但形成第2外延生长层22之后,在存储器孔20的内部分别形成栅极绝缘膜36及与第2外延生长层22电连接的半导体柱37。栅极绝缘膜36及半导体柱37从外侧(存储器孔20的内侧面)按照二氧化硅膜31、氮化硅膜32、二氧化硅膜33、非晶或多晶硅膜34、二氧化硅膜35的顺序使薄膜沉积。

[0036]

进而,深挖未图示的狭缝,从该狭缝将积层结构体中包含的si3n4膜(虚设膜)12'、14'、16'、17'、18'

…

一起去除。结果,在si3n4膜(虚设膜)原先存在的部分产生空洞。

[0037]

si3n4膜(虚设膜)的最下层12'原先存在的部分的空洞使第2外延生长层22的侧面露出。从该空洞将第2外延生长层22的侧面热氧化而形成绝缘体23。此时,si3n4膜(虚设膜)的其它层14'、16'、17'、18'

…

原先存在的部分的空洞使栅极绝缘膜36的二氧化硅膜31露出。然后,通过将钨等金属填埋在这些空洞中,形成利用图1说明的导电膜12,14、16、17、18

…

。

[0038]

通过以上的一连串步骤,可以制造图1所示的构成的半导体存储装置1。

[0039]

[半导体存储装置的变化例]

[0040]

利用图6对本发明的变化例的半导体存储装置的构成进行说明。图6是对本发明的变化例的半导体存储装置进行说明的剖视图。

[0041]

本变化例的半导体存储装置1a具有2层源极侧选择栅极线12a、12b,除此以外,与所述半导体存储装置1相同,因此,对共通的部分省略说明。

[0042]

本变化例的半导体存储装置1a具有2层源极侧选择栅极线12a、12b。第2外延生长层22介隔绝缘体23被源极侧选择栅极线12a包围,作为源极侧选择栅极晶体管的一部分发挥功能。也就是说,第1外延生长层21配置在相比源极侧选择栅极线12a更靠半导体衬底10侧。第1外延生长层21与第2外延生长层22的边界配置在源极侧选择栅极线12a与源极侧选择栅极线12b之间。然而,并不限定于此,第1外延生长层21与第2外延生长层22的边界也可以配置在源极侧选择栅极线12b与半导体衬底10之间。

[0043]

对本发明的若干实施方式进行了说明,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些新颖的实施方式能以其它多种方式实施,可以在不脱离发明主旨的范围内进行各种省略、置换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其均等的范围内。

[0044]

[符号的说明]

[0045]

1、1a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体存储装置

[0046]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体衬底

[0047]

12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极侧选择栅极线

[0048]

21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第1外延生长层

[0049]

22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第2外延生长层

[0050]

23

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

绝缘体

[0051]

30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储器柱

[0052]

36

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极绝缘膜

[0053]

37

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体柱。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1