半导体封装装置及其制造方法与流程

1.本公开涉及半导体封装技术领域,具体涉及半导体封装装置及其制造方法。

背景技术:

2.为了提高衬底的i/o(input-output,输入-输出)数,现有技术中经常出现将两个小尺寸衬底(substrate)组合在一起的方案。然后,在取放(pick&place)衬底的过程中,可能会因为其中一个衬底有较大角度旋转,因此重布线层(rdl,redistribution layer)的导线与其对应焊垫(bonding pads)之间相对位置关系发生改变,即产生偏移(shift),从而导致重布线层的焊垫之间电性路径变长,继而重布线层的焊垫之间电性连接效果不佳。另外,最上层重布线层的导线之间交错(overlap)产生寄生电容而影响其电性表现。如图1所示,由于抓取第二衬底12过程中产生了角度旋转,继而连接第一衬底11和第二衬底12的导线13位于第二衬底12的另一端无法连接第二衬底12上的相应焊垫,二者之间存在偏移16,从而影响电性能。而连接第一衬底11和第二衬底12的导线14虽然连接了第二衬底12上的相应焊垫,但也会使得电性路径相对于第二衬底12为产生角度旋转而边长。另外,因为第二衬底12产生角度偏移而导致导线13和导线14产生了交错,进而可能产生寄生电容,影响电性能,如图1中15所示。

技术实现要素:

3.本公开提出了半导体封装装置及其制造方法。

4.第一方面,本公开提供了一种半导体封装装置,包括:

5.第一衬底,所述第一衬底包括第一线路;

6.第二衬底,所述第二衬底包括第二线路,所述第一衬底和所述第二衬底水平并排放置,所述第一衬底的第一侧壁和所述第二衬底的第二侧壁固定接合;

7.桥接重布线层,设置于所述第一衬底上表面和所述第二衬底上表面,所述桥接重布线层包括第一导电垫和电连接所述第一导电垫的第二导电垫,所述第一线路和所述第二线路分别电连接所述第一导电垫和第二导电垫。

8.在一些可选的实施方式中,所述桥接重布线层还包括连接线路,所述第一导电垫和所述第二导电垫通过所述连接线路电连接。

9.在一些可选的实施方式中,所述连接线路包括并列设置的至少两条桥接线路,所述桥接线路包括第三导电垫和以导电迹线电连接第三导电垫的第四导电垫,所述第三导电垫电连接所述第一导电垫,所述第四导电垫电连接所述第二导电垫。

10.在一些可选的实施方式中,所述至少两条桥接线路的线宽/线距为10/10微米到25/25微米。

11.在一些可选的实施方式中,所述桥接重布线层设置于所述第一衬底上表面靠近所述第一侧壁的第一区域和所述第二衬底上表面靠近所述第二侧壁的第二区域。

12.在一些可选的实施方式中,所述桥接重布线层还包括第一导电柱和电连接所述第

一导电柱的第二导电柱,所述第一导电柱电连接各所述第一导电垫,所述第二导电柱电连接各所述第二导电垫。

13.在一些可选的实施方式中,所述桥接重布线层包括至少两对并排设置的第一导电垫和通过连接条电连接第一导电垫的第二导电垫。

14.在一些可选的实施方式中,各所述电连接第一导电垫和第二导电垫的连接条的线宽/线距为20/20微米到30/30微米。

15.在一些可选的实施方式中,所述第一区域的面积小于等于所述第一衬底上表面面积的2/3,和/或,所述第二区域的面积小于等于所述第二衬底上表面面积的2/3。

16.在一些可选的实施方式中,所述桥接重布线层位于所述第一衬底上的部分包括r1列第一导电垫,且每列第一导电垫平行于所述第一侧壁,所述r1为小于等于3的正整数。

17.在一些可选的实施方式中,所述桥接重布线层位于所述第二衬底上的部分包括r2列第二导电垫,且每列第二导电垫平行于所述第二侧壁,所述r2为小于等于3的正整数。

18.在一些可选的实施方式中,所述第一衬底和所述第二衬底为堆积衬底、具有芯基板的衬底、不具有芯基板的衬底或者具有扇出重布线层的衬底。

19.在一些可选的实施方式中,所述桥接重布线层的最小线宽l’是通过所述第一侧壁与所述第二侧壁之间的距离d,所述第一衬底的高度h和重布线制程对应的最小线路线宽l按照如下公式计算得到的:

20.l’=l

×

(d+2h)/(2h)。

21.第二方面,本公开提供了一种制造半导体封装装置的方法,包括:

22.提供第一衬底和第二衬底,其中,所述第一衬底包括第一线路,所述第二衬底包括第二线路,所述第一衬底和所述第二衬底水平并排放置,所述第一衬底的第一侧壁和所述第二衬底的第二侧壁固定接合;

23.在所述第一衬底上表面和所述第二衬底上表面形成桥接重布线层,所述桥接重布线层包括第一导电垫和电连接所述第一导电垫的第二导电垫,所述第一线路和所述第二线路分别电连接所述第一导电垫和第二导电垫。

24.为了解决现有为提高i/o数而组合衬底过程中,可能因抓取衬底过程中角度旋转而产生的各种问题,本公开提供的半导体封装装置及其制造方法,通过将小尺寸的衬底信号走线采纵向方式传递至衬底表面的桥接重布线层,再利用桥接重布线层的细间距(fine pitch)特性,将两个小尺寸衬底进行电连接,可以实现包括但不限于以下技术效果:(1)通过利用桥接重布线层连接两个小尺寸衬底,实现了大尺寸衬底,即提高了i/o数且维持高良率;(2)由于整体大尺寸衬底容易发生翘曲,而将两个小尺寸的衬底进行连接可以改善大尺寸衬底的翘曲程度;(3)通过将两个小尺寸衬底两侧壁固定接合,并在表面设计桥接重布线层进行电连接,即将桥接重布线层设置在两小尺寸衬底表面中邻近所固定接合的侧壁的区域,进而将电性连接路径变短,即使在取放小尺寸衬底过程中产生偏移或者角度旋转,也可降低对电性连接的路径影响,以及可减缓电性连接效果的影响;(4)降低产生寄生电容的机率;(5)小尺寸衬底中相同信号的走线可以集中于单一焊垫,进而降低最上层桥接重布线层的布线复杂度。

附图说明

25.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本公开的其它特征、目的和优点将会变得更明显:

26.图1是现有技术中的半导体封装装置的一个实施例的俯视示意图;

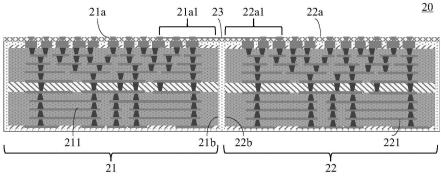

27.图2根据本公开的半导体封装装置的一个实施例的纵向截面结构示意图;

28.图3是根据本公开的半导体封装装置的一个实施例的俯视示意图;

29.图4是根据本公开的半导体封装装置的又一个实施例的俯视示意图;

30.图5是根据本公开的半导体封装装置的再一个实施例的俯视示意图;

31.图6、图7、图8是根据本公开的半导体封装装置的不同实施例的纵向截面结构示意图;

32.图9是根据本公开的半导体封装装置的一个实施例的水平截面结构放大示意图;

33.图10a-10b是根据本公开的制造半导体封装装置的方法一个实施例在各个阶段制造的半导体封装装置的纵向截面结构示意图。

34.符号说明:

35.11-第一衬底;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14-导线;

36.12-第二衬底;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

15-导线交错;

37.13-导线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

16-偏移;

38.23-桥接重布线层;

ꢀꢀꢀꢀꢀꢀꢀꢀ

233-连接线路;

39.231-第一导电垫;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

2331-桥接线路;

40.232-第二导电垫;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23311-第三导电垫;

41.234-第一导电柱;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23312-第四导电垫;

42.235-第二导电柱;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23313-导电迹线;

43.236-连接条;

44.21-第一衬底;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22-第二衬底;

45.211-第一线路;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

221-第二线路;

46.21a-第一衬底上表面;

ꢀꢀꢀꢀꢀꢀ

22a-第二衬底上表面;

47.21a1-第一区域;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22a1-第二区域;

48.21b-第一侧壁;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22b-第二侧壁。

具体实施方式

49.下面结合附图和实施例对说明本发明的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本发明所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外,为了便于描述,附图中仅示出了与有关发明相关的部分。

50.需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述

的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本发明可实施的范畴。

51.还需要说明的是,本公开的实施例对应的纵向截面可以为对应前视图方向截面。

52.另外,在不冲突的情况下,本公开中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本公开。

53.参考图2,图2示出了根据本公开的半导体封装装置的一个实施例20的纵向截面结构示意图。

54.如图2所示,半导体封装装置20包括:第一衬底21、第二衬底22和桥接重布线层23。其中:

55.第一衬底21包括第一线路211,第二衬底22包括第二线路221,第一衬底21和第二衬底22水平并排放置,第一衬底21的第一侧壁21b和第二衬底22的第二侧壁22b固定接合。例如,第一衬底21的第一侧壁21b可以通过封装材与第二衬底22的第二侧壁22b固定接合。封装材可以由各种模封材料(molding compound)形成。例如,模封材料可包括环氧树脂(epoxy resin)、填充物(filler)、催化剂(catalyst)、颜料(pigment)、脱模剂(release agent)、阻燃剂(flame retardant)、耦合剂(coupling agent)、硬化剂(hardener)、低应力吸收剂(low stress absorber)、粘合促进剂(adhesion promoter)、离子捕获剂(ion trapping agent)等。

56.桥接重布线层23,设置于第一衬底21的上表面21a和第二衬底22的上表面22a,桥接重布线层23包括第一导电垫(如图3俯视图中所示231)和电连接第一导电垫231的第二导电垫(如图3俯视图中所示232)。第一衬底21的第一线路211和第二衬底22的第二线路221分别电连接桥接重布线层23的第一导电垫231和第二导电垫232。继而,第一衬底21和第二衬底22通过桥接重布线层23实现电连接。第一导电垫231和第二导电垫232可以是各种具有导电功能的连接结构。

57.这里,第一衬底21和第二衬底22可以是各种类型的衬底,本公开对此不做具体限定。第一衬底21和第二衬底22可包括有机物和/或无机物,其中有机物例如可以是:聚酰胺纤维(polyamide,pa)、聚酰亚胺(polyimide,pi)、环氧树脂(epoxy)、聚对苯撑苯并二噁唑(poly-p-phenylene benzobisoxazole,pbo)纤维、fr-4环氧玻璃布层压板、pp(prepreg,预浸材料或称为半固化树脂、半固化片)、abf(ajinomoto build-up film)等,而无机物例如可以是硅(si),玻璃(glass),陶瓷(ceramic),氧化硅,氮化硅,氧化钽等。

58.第一衬底21和第二衬底22还可以是例如印刷电路板,比如纸基铜箔层合物、复合铜箔层合物或聚合物浸渍的玻璃纤维基铜箔层合物等。

59.第一衬底21和第二衬底22还可包括互连结构(interconnection),比如导电迹线(conductive trace)、导电导孔(conductive via)等。这里,导电导孔可以是通孔、埋孔或盲孔,且通孔、埋孔或盲孔中可以填充例如金属或金属合金的导电材料,这里,金属例如可以是金(au)、银(ag)、铝(al)、镍(ni)、钯(pd)、铜(cu)或其合金。

60.桥接重布线层23可以是由导电迹线和介电材料(dielectric)组成的重布线层。

61.本公开提供的上述实施例提供的半导体封装置20可以实现的技术效果包括但不限于:(1)通过利用桥接重布线层23连接两个小尺寸衬底:第一衬底21和第二衬底22,实现了大尺寸衬底20,相对于单独大尺寸衬底提高了i/o数且维持高良率;(2)相对于整体大尺

寸衬底可以改善大尺寸衬底的翘曲程度;(3)通过将两个小尺寸的第一衬底21和第二衬底22两侧壁固定接合,并在表面设计桥接重布线层23进行电连接,即将桥接重布线层23设置在两小尺寸衬底表面中邻近所固定接合的侧壁的区域,进而将电性连接路径变短,即使在取放小尺寸衬底过程中产生偏移或者角度旋转,也可降低对电性连接的路径影响,以及可减缓电性连接效果的影响;(4)降低产生寄生电容的机率;(5)小尺寸衬底中相同信号的走线可以集中于单一导电垫,进而降低最上层桥接重布线层23的布线复杂度。

62.在一些可选的实施方式中,桥接重布线层23设置于第一衬底21上表面21a靠近第一侧壁21b的第一区域21a1和第二衬底22上表面22a靠近第二侧壁22b的第二区域22b。如此,可以缩短第一线路211和第二线路221之间的电性路径,进而提高第一线路211和第二线路221之间的电性连接效果,即使在取放第一衬底21或者第二衬底22的过程中发生偏移或者角度旋转,也可以降低或减少对第一线路211和第二线路221之间电性路径或者电性连接性能的影响。

63.在一些可选的实施方式中,第一区域21a1的面积小于等于第一衬底21上表面21a面积的2/3,和/或,第二区域22a1的面积小于等于第二衬底22上表面22a面积的2/3。从而,可以进一步缩短第一线路211和第二线路221之间的电性路径。

64.在一些可选的实施方式中,桥接重布线层23位于第一衬底21上的部分包括r1列第一导电垫231,且每列第一导电垫231平行于第一侧壁21b,r1为小于等于3的正整数。如此,也可以缩短第一线路211和第二线路221之间的电性路径。具体而言,在如图3所示的半导体封装装置的俯视示意图中,只包括1列第一导电垫231,即r1为1,具体为图3中虚线框c11所示的1列第一导电垫231,且该列第一导电垫231平行于第一侧壁21b。在如图4所示的半导体封装装置的俯视示意图中,也包括1列第一导电垫231,即r1为1,具体为图4中虚线框c12所示的1列第一导电垫231,且该列第一导电垫231平行于第一侧壁21b。在如图5所示的半导体封装装置的俯视示意图中,包括2列第一导电垫231,即r1为2,具体为图5中虚线框c13所示的第1列第一导电垫231和虚线框c14所示的第2列第一导电垫231,而且该两列第一导电垫231均平行于第一侧壁21b。

65.在一些可选的实施方式中,桥接重布线层23位于第二衬底22上的部分包括r2列第二导电垫232,且每列第二导电垫232平行于第二侧壁22b,r2为小于等于3的正整数。如此,也可以缩短第一线路211和第二线路221之间的电性路径。具体而言,在如图3所示的半导体封装装置的俯视示意图中,只包括1列第二导电垫232,即r2为1,具体为图3中虚线框c21所示的1列第二导电垫232,且该列第二导电垫232平行于第二侧壁22b。在如图4所示的半导体封装装置的俯视示意图中,也包括1列第二导电垫232,即r2为1,具体为图4中虚线框c22所示的1列第二导电垫232,且该列第二导电垫232平行于第二侧壁22b。在如图5所示的半导体封装装置的俯视示意图中,包括2列第二导电垫232,即r2为2,具体为图5中虚线框c23所示的第1列第二导电垫232和虚线框c24所示的第2列第二导电垫232,而且该两列第二导电垫232均平行于第二侧壁22b。

66.在一些可选的实施方式中,第一衬底21和第二衬底22可以为如图6所示的堆积衬底(build up substrate)、如图2所示的具有芯基板的衬底(core substrate)、如图8所示的不具有芯基板的衬底(coreless substrate)或者如图7所示的具有扇出重布线层的衬底(fan-out substrate)。

67.在一些可选的实施方式中,如图9所示,桥接重布线层23的最小线宽l’是通过第一侧壁21b与第二侧壁22b之间的距离d,第一衬底21的高度h和重布线制程对应的最小线路线宽l按照如下公式计算得到的:

68.l’=l

×

(d+2h)/(2h)。

69.即,为了弥补线路路径损失,原本若用重布线制程中的线路直接连接第一线路211和第二线路221,则直接连接的线路总长度为2h,直接连接的线路线宽可以对应重布线制程对应的最小线路线宽l。现在将直接连接的线路切割得到第一线路211和第二线路221再通过桥接重布线层23进行连接,其对应的线路总长度即为(d+2h),即线路长度增加了d,因此需要将桥接重布线层23的线宽相应增加以弥补电性损失,而增加部分的比例应为(d/2h),增加后的桥接重布线层23的线宽l’应为:l’=l

×

(d+2h)/2h。

70.按照该线宽l’可以在尽量减小线宽/线距以提高i/o数,减小占用面积的同时,不影响电性能。

71.下面参考图3,图3是根据本公开的半导体封装装置的一个实施例30的水平截面结构示意图。图3所示的半导体封装装置30类似于图2中所示的半导体封装装置20,不同之处在于:半导体封装装置30中桥接重布线层23还包括如图3中虚线框233所示的连接线路,第一导电垫231和第二导电垫232通过连接线路233电连接。

72.在一些可选的实施方式中,连接线路233可以包括并列设置的至少两条桥接线路2331,桥接线路2331包括第三导电垫23311和以导电迹线电连接第三导电垫23311的第四导电垫23312,第三导电垫23311电连接第一导电垫231,第四导电垫23312电连接第二导电垫232。

73.在一些可选的实施方式中,桥接线路2332的线宽/线距(l/s,line/space)为10/10微米到25/25微米之间。

74.下面参考图4,图4是根据本公开的半导体封装装置的一个实施例30的水平截面结构示意图。图4所示的半导体封装装置40类似于图2中所示的半导体封装装置20,不同之处在于:桥接重布线层23还包括第一导电柱234和电连接第一导电柱234的第二导电柱235,第一导电柱234电连接各第一导电垫231,第二导电柱235电连接各第二导电垫232。从图4中可以看出,相对于图3所示的半导体封装装置30,在半导体封装装置30中某个桥接线路2332损坏时,该桥接是2332对应的第一导电垫231将无法电连接相应的第二导电232,而在半导体封装装置40中,即使某个连接第一导电柱234和第二导电柱235的导电迹线断开,还有其他导电迹线可以连接第一导电柱234和第二导电柱235,继而所有第一导电垫231还可以连接所有第二导电垫232,即提高了封装装置的可靠性。

75.下面参考图5,图5是根据本公开的半导体封装装置的一个实施例50的水平截面结构示意图。图5所示的半导体封装装置50类似于图2中所示的半导体封装装置20,不同之处在于:桥接重布线层23包括至少两对并排设置的第一导电垫231和通过连接条(connect bar)236电连接第一导电垫231的第二导电垫232。

76.在一些可选的实施方式中,各电连接第一导电垫231和第二导电垫232的连接条236的线宽/线距为20/20微米到30/30微米之间。

77.图10a和图10b是根据本公开的一些实施例的在各个阶段制造的半导体封装装置10a和10b的纵向截面结构示意图。为了更好地理解本公开的各方面,已简化各图。

78.参考图10a,提供第一衬底21和第二衬底22。

79.这里,第一衬底21包括第一线路211,第二衬底22包括第二线路221,且第一衬底21和第二衬底22水平并排放置,第一衬底21的第一侧壁21b和第二衬底22的第二侧壁22b固定接合。例如,第一衬底21的第一侧壁21b可以通过封装材与第二衬底22的第二侧壁22b固定接合。又例如,第一衬底21的第一侧壁21b也可以通过粘合剂与第二衬底22的第二侧壁22b固定接合。

80.参考图10b,在第一衬底21上表面21a和第二衬底22上表面22a形成桥接重布线层23。

81.桥接重布线层23包括第一导电垫231和电连接第一导电垫231的第二导电垫232。第一衬底21的第一线路221和第二衬底22的第二线路221分别电连接桥接重布线层23的第一导电垫231和第二导电垫232。继而,第一衬底21通过桥接重布线层23实现电连接。第一导电垫231和第二导电垫232可以是各种具有导电功能的连接结构。

82.需要说明的是,制程上可以采用当前已知或未来开发的重布线层形成技术,本技术对此不做具体限定,例如可采用包括但不限于光刻、电镀(plating),化学镀(electroless plating)等形成桥接重布线层23。桥接重布线层23可以包括介电材料和各种导电材料,例如钛(ti),钨(w),镍(ni)、金(au)、银(ag)、铝(al)、镍(ni)、钯(pd)、铜(cu)或其合金等。

83.尽管已参考本公开的特定实施例描述并说明本公开,但这些描述和说明并不限制本公开。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效元件而不脱离如由所附权利要求书限定的本公开的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本公开中的技术再现与实际实施之间可能存在区别。可存在未特定说明的本公开的其它实施例。应将说明书和图示视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本公开的目标、精神以及范围。所有此些修改都落入在此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本文中所公开的方法,但应理解,可在不脱离本公开的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本文中特别指示,否则操作的次序和分组并不限制本公开。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1