一种双沟槽SiC功率MOS器件

一种双沟槽sic功率mos器件

技术领域

1.本发明属于微电子技术领域,涉及半导体器件的设计,特别涉及一种能够提高栅介质可靠性的sic umosfet器件,该结构能够将器件在工作时栅槽下峰值电场向源槽转移,缓解了栅电极下的的电场集中现象,从而能够有效避免栅氧化层提前击穿,使得器件获得较高的击穿电压。

背景技术:

2.第三代半导体sic具有宽禁带宽度、高临界击穿电场、高饱和漂移速率等特点,非常适合于高温、大电压、高频率、抗辐射等极端恶劣的应用环境。sic基半导体的发展将有利于为现代军事电子系统实现高效能、高机动、小型化、全天候应用;同时也可以广泛的应用于民用电力电子设备,在轨道交通、太阳能发电、航空航天等领域发挥重要作用。sic umosfet由于具有低栅电流、低导通电阻、稳定的电阻正温度系数、散热效率高等特点,成为各类sic器件中的首要选择。但是传统的sic umosfet结构存在一个严重的缺点,即当器件处于阻断工作状态时,栅槽底部氧化层的电场集中效应非常显著,这将导致栅氧化层的提前击穿,降低器件的击穿电压。本设计提出了一种具有双沟槽结构的sic umosfet,在传统umosfet的基础上在源极下也进行挖槽。这种在源极处也挖槽的双沟槽umosfet能够将原本在栅电极下的峰值电场向源极槽下转移,有效缓解了栅电极的电场集中现象。同时,还在栅下加入了p屏蔽层和一个超结(superjunction)结构。p

‑

shielding结构的引入,屏蔽了栅氧化层受到来自漂移区的高电场影响,提高了器件可靠性。超结增强了其阻塞能力,将局部超结放置在p屏蔽层域下方,克服了p屏蔽层域和ndrift区域之间耗尽区域展宽所引起的电流通路变窄的问题,提高了导通模式特性在保持击穿电压的前提下同时具有较低的导通电阻。

技术实现要素:

3.本发明的目的在于针对上述现有技术的不足,提出一种双沟槽sic功率mos器件,以提高器件击穿电压的前提下具有较低的导通电阻。

4.为实现上述目的,本发明采取的技术方案是:一种双沟槽sic功率mos器件,其特征在于,包括源极、漏极、栅极、n+衬底层和n

‑

漂移区,在n+衬底层的底面和上面分别设有漏极和n

‑

漂移区;在该n

‑

漂移区的上面两侧分别设有对称设置的l形的p井区,在该p井区的横向段的外端上面设有p+区;在两侧的该p井区的中间设有p屏蔽层,在该p屏蔽层的下方设有超结;在p屏蔽层的上面设有栅极凹槽,在该栅极凹槽内设有栅极;在该栅极凹槽与两侧的p井区之间均设有p

‑

body区,在该p

‑

body区的上面设有n+区;在该p井区、p+区和n+区的上面设有源极;在两侧的源极以及栅极之间设有互连电极。

5.本发明与现有技术相比具有如下优点:本发明通过对传统的槽栅垂直功率sic mos结构进行改进,提高了器件的击穿电压,降低了导通电阻,并且有效的阻止了栅氧化层的提前击穿。

附图说明

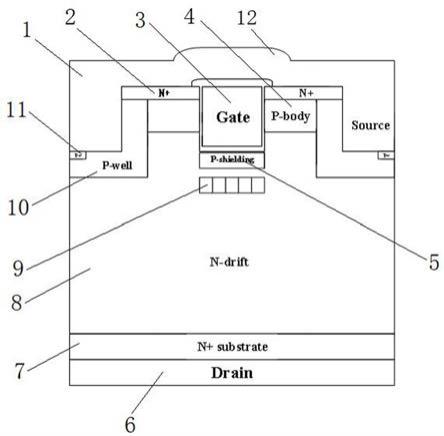

6.图1是本发明器件的结构示意图。

7.图2是本发明器件的制备工艺流程和结构图。

8.附图标记说明:1、源极,2、n+区,3、栅极,4、p

‑

body区,5、p屏蔽层,6、漏极,7、n+衬底层,8、n

‑

漂移区,9、超结,10、p井区,11、p+区,12、互连电极。

具体实施方式

9.参见图1,本发明一种双沟槽sic功率mos器件,其特征在于,包括源极1、漏极6、栅极3、n+衬底层7和n

‑

漂移区8,在n+衬底层7的底面和上面分别设有漏极6和n

‑

漂移区8;在该n

‑

漂移区8的上面两侧分别设有对称设置的l形的p井区10,在该p井区10的横向段的外端上面设有p+区11;在两侧的该p阱区10的中间设有p屏蔽层5,在该p屏蔽层5的下方设有超结9;在p屏蔽层5的上面设有栅极凹槽,在该栅极凹槽内设有栅极3;在该栅极凹槽与两侧的p阱区10之间均设有p

‑

body区4,在该p

‑

body区4的上面设有n+区2;在该p阱区10、p+区11和n+区2的上面设有源极1;在两侧的源极1以及栅极3之间设有互连电极12。其中n

‑

漂移区8由n

‑

漂移区8上部和n

‑

漂移区8下部组成(图1中视为一个区域),分别位于超结9的上、下。在制作时,n

‑

漂移区8下部和n

‑

漂移区8上部分两次外延形成。

10.参见图2,本发明上述器件的制备方法的工艺流程如下(以下工艺的各个步骤的具体操作都属于常规技术):

11.步骤1、形成n

‑

漂移区(8)的下部:在n+衬底层(7)一侧外延形成n

‑

漂移区(8)的下部,并对表面进行标准湿法工艺清洗;参见图2中的a图。

12.步骤2、超结(9)的形成(参见图2中的b图):

13.(1)被清洗过的外延片的n

‑

漂移区(8)的表面涂光刻胶,刻出超结(9)中n型区的高温离子注入区域,然后进行高温氮离子注入,形成超结(9)的n区,该n区的厚度为0.2μm,浓度为3e+17cm

‑3。

14.(2)在已经形成超结(9)n区的外延片表面涂光刻胶,刻出超结9中的p型高温离子注入区,然后进行高温al离子注入,形成厚度为0.2μm,浓度为3e+17cm

‑3的超结9的p型区。

15.步骤3、n

‑

漂移区(8)上部的形成:在超结(9)的上面进行外延生长,得到11μm厚度n型漂移区(8)上部,浓度为7.5e+15cm

‑3;参见图2中的c图。

16.步骤4、源极沟槽(13)和栅极沟槽(14)的形成:在该n型漂移区(8)上部的上面两端刻蚀形成源极沟槽(13);在该n型漂移区(8)上部的上面中间刻蚀形成栅极沟槽(14);参见图2中的d图。

17.步骤5、p井区(10)的形成:在该源极沟槽和涂光刻胶,刻出p井区区(10)注入区域,形成p井区,浓度为5e+17cm

‑3,深度为0.3μm。p屏蔽层(5)的形成:在栅极沟槽涂光刻胶,刻出p屏蔽层(5)注入区域,并进行p型离子注入形成p屏蔽层(5),浓度为5e+18cm

‑3。参见图2中的e图。

18.步骤6、p

‑

body区(4)的形成:在上一步骤完成的芯片上面涂光刻胶,在栅极沟槽的两侧刻出p

‑

body(4)的离子注入区域,并进行p型离子注入形成p

‑

body(4)区,其浓度为1e+17cm

‑3,深度为0.5μm;参见图2中的f图。

19.步骤7、n+区(2)的形成:在p

‑

body区(4)和p井区区(10)上表面涂光刻胶,刻出n+区

(2)的注入区域,并进行n型离子注入形成n+(2)区域,其浓度为1e+20cm

‑3,深度为0.2μm;参见图2中的g图。

20.步骤8、n

‑

漂移区(8)表面碳保护膜的形成:在进行了步骤5的p型离子注入之后,在n

‑

漂移区(8)表面形成碳保护膜;

21.步骤9、高温离子注入激活:对步骤9完成的芯片进行1600℃高温离子注入退火:

22.步骤10、碳保护膜的去除:去除芯片表面的碳保护膜:

23.步骤11、栅极氧化层(15)的制备:将去除了碳保护膜的芯片表面用hf酸清洗,然后进行sio2栅介质层的生长,形成栅极氧化层(15),厚度为50nm;参见图2中的h图。

24.步骤12、漏极(6)的形成:在进行了栅极氧化层(15)的形成后,进行漏区金属淀积,20nm/240nm的ni/au两种金属,然后剥离形成漏区欧姆接触的漏极(6)。

25.步骤13、源极(1)的形成:涂光刻胶,刻蚀出源区欧姆接触图形,进行源区金属淀积,依次淀积20nm/240nm的ni/au两种金属,然后进行欧姆接触退火,剥离形成源极(1)。参见图2中的i图。

26.步骤14、栅极3的形成:对进行了欧姆接触电极退火的sic样品进行栅电极的形成:20nm/240nm的ni/au;参见图2中的j图。

27.步骤15、互连电极(12)的形成:对已形成栅极(6)的芯片表面涂剥离胶、光刻胶、刻出栅极(6)、源极(1)和n+区(2)的接触孔,然后淀积金属层,并剥离形成栅栅极(6)、源极(1)和n+区(2)之间的互连电极(12)图形,互连电极(12)为ti/au两层金属,厚度分别为50nm/200nm。参见图2中的k图。

28.本发明的器件能够提高器件的击穿电压,降低导通电阻,并且有效的阻止栅氧化层的提前击穿,其原理说明如下:

29.现有的单沟槽umosfet由于器件电场主要集中在栅氧化层下方,因此氧化物的可靠性受到了严峻考验,容易提前击穿,而引入在源极挖槽的双沟槽设计后,源极处的沟槽能够缓解栅氧化层底部的电场集中效应,从而避免其提前击穿,从而提高了器件击穿电压。引入的p屏蔽层掺杂浓度相比pbase的掺杂浓度要大,当器件工作在反向状态时,漏极加高电压,器件电场将被分散到p屏蔽层和n

‑

drift区域,从而缓解了栅氧化层底部电场集中效应,避免了栅氧化层的提前击穿。电压增大,耗尽区增大,电场降低。所以,源漏电压越高,漂移层的电阻越大,其导通电阻也变得越大;而引入的超结结构在漂移层中n层和p层的排列呈纵向槽结构,施加电压之后,耗尽层呈横向延伸连接,最终相当于拓展了栅下的耗尽层,实质是超结结构突破了器件掺杂浓度与vb的依赖关系,因此在保持高击穿电压的基础上,可以保持较高的掺杂浓度,因此可以降低其导通电阻。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1