一种双极选通忆阻器的制备方法及双极选通忆阻器

1.本发明属于微电子器件领域,更具体地,涉及一种双极选通忆阻器的制备方法及双极选通忆阻器。

背景技术:

2.在物联网时代背景下,前所未有的数据量增长推动高效、廉价、微型存储技术的发展。由于摩尔定律面临瓶颈,互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)继续微缩会带来成本的大幅提高。近年来,廉价、结构简单、可微缩、低功耗、可靠、非易失性的忆阻器成为最有物流网应用前景的存储技术之一。由于简单的三明治器件结构,忆阻器适合采用无源交叉阵列结构来进行大规模二维或三维集成。交叉阵列结构特点就是存储单元位于互相垂直的字线和位线交叉点上,理论上交叉阵列结构允许的最小尺寸为4f2/n,其中,f为最小的特征尺寸,n是堆叠层数,集成密度非常高。在高集成密度的交叉阵列中,选取的单元周围存在很多未选取单元上的低欧姆导通路径,从而会带来漏电流问题。这些低欧姆路径上的电流叠加起来足以影响选取单元的信息读取结果,读取裕度范围,以及大大限制阵列的规模。为了防止出现这样的问题,与交叉阵列结构兼容的方案中,忆阻器与二极管的堆叠结构受限于二极管没有足够的正向电流密度和单极性忆阻器不成熟;此外两个忆阻器反向串联的结构也存在固有的破坏性读取过程,对操作速度、复杂性、功耗造成巨大影响。相较而言,选通器件与忆阻器的堆栈结构是有效的抑制漏电流通路并与交叉阵列结构兼容的解决方案之一。因为选通器件具有高非线度、高耐久性、高导通/关断电流。

3.目前高性能的双极选通器件的工艺制备难度较为复杂,需要人为控制制备参数来调控其材料的固定化学计量比,否则不会表现选通特性;制备的选通层薄膜材料后续需要高达几百度的高温退火来转变为晶态从而表现出选通特性,此外当该层与阻变层堆叠后的超高温退火对忆阻器层的稳定特性会造成很大的破坏;制备的选通层薄膜材料后续需要大电压初始化过程来转变为晶态从而表现出选通特性,该大电压对外围电路设计复杂度带来巨大压力;跟忆阻器堆叠后界面的扩散问题对选通层及阻变层的稳定电学特性会产生不可逆的影响。这些问题导致这类器件的性能指标很难达到存储器的商业化应用。

4.综上,目前高性能的双极选通器件的工艺制备难度较为复杂,例如需要精确调控其材料的化学计量比、制备的薄膜材料后续需要高达几百度的高温退火、需要跟忆阻器独立分开堆叠保证各自的可靠性和差异性、需要大电压进行初始化。这导致这类器件是很难实现结合存储器的商业化应用。

技术实现要素:

5.针对现有技术的缺陷,本发明的目的在于提供一种双极选通忆阻器的制备方法及双极选通忆阻器,旨在解决现有高性能的双极选通器件的工艺制备难度较为复杂,例如需要精确调控其材料的化学计量比、制备的薄膜材料后续需要高达几百度的高温退火、需要

跟忆阻器独立分开堆叠保证各自的可靠性和差异性、需要大电压进行初始化的问题。

6.为实现上述目的,第一方面,本发明提供了一种双极选通忆阻器的制备方法,包括如下步骤:

7.制备下电极;

8.在下电极上沉积阻变材料层;所述阻变材料层为一元或多元金属氧化物材料;

9.在阻变材料层上沉积上电极;所述沉积上电极的方式为:采用磁控溅射方式在阻变材料层上沉积上电极,通过控制溅射功率以控制上电极金属粒子具备合适的动能,并控制上电极和阻变材料层所处区域的真空度,以使得在上电极沉积的过程中上电极与阻变材料层自发发生氧化还原反应,形成内建双极选通层,并继续在内建双极选通层上沉积上电极;或沉积上电极的方式为:选用相比阻变材料层金属元素活性高的材料作为上电极的金属材料,并在阻变材料层上沉积上电极,使得在上电极沉积的过程中上电极与阻变材料层自发发生氧化还原反应,形成内建双极选通层,并继续在内建双极选通层上沉积出上电极;

10.其中,上电极金属材料的氧化物具有双极选通的特性,所述内建双极选通层的材料为上电极金属材料的氧化物;所述下电极、阻变材料层、内建双极选通层以及上电极组成双极选通忆阻器;所述双极选通忆阻器在正反向电压小于或等于阈值电压时,处于关断状态,在正反向电压大于阈值电压时,可以对阻变材料层进行擦写操作。

11.在一个可选的示例中,所述上电极金属材料为:nb、v、ni、cr、ti、co、zr、ru中的任一种。

12.在一个可选的示例中,通过控制所述氧化还原反应过程以控制所述内建双极选通层的厚度为1nm~10nm。

13.在一个可选的示例中,所述控制上电极和阻变材料层所处区域的真空度,具体为:

14.通过抽取待控制区域的空气以及向待控制区域通入惰性气体并控制通入惰性气体的速度控制待控制区域的真空度,所述待控制区域的真空度控制在5*10

‑3pa~5*10

‑4pa。

15.在一个可选的示例中,所述下电极材料为:pt、au、ta、al、pd、hf、w、tin、tiw中的任一种。

16.在一个可选的示例中,所述上电极的厚度为50nm~1um,所述阻变材料层的厚度为5nm~50nm,所述下电极的厚度为50nm~1um。

17.第二方面,本发明提供一种利用上述第一方面提供的制备方法制备得到的双极选通忆阻器,当所述双极选通忆阻器外部施加的正向电压或者反向电压大小达到所述内建双极选通层的阈值电压时,所述内建双极选通层内会形成晶化区域,所述内建双极选通层的阻值状态由关态电阻状态转变为开态电阻状态,使得所述双极选通忆阻器具有双向开关的特性;

18.所述内建双极选通层形成的过程中,所述阻变材料层中形成一些氧空位晶粒区域,所述氧空位晶粒区域使得所述双极选通忆阻器器件的初始阻值下降,且所述氧空位晶粒区域可作为阻变材料层发生阻变形成晶化导电丝过程中的种子。

19.总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:

20.本发明提供一种双极选通忆阻器的制备方法及双极选通忆阻器,通过上电极与阻变材料在物理沉积制备过程中发生的氧化还原反应,从而在上电极与阻变材料界面处自发

氧化过程形成一层上电极元素的内建双极选通层,上电极从含氧的阻变材料层夺取氧发生还原反应,从而在阻变材料层中形成大量的氧空位晶粒区域,这些区域呈现出低阻状态,从而将整体器件的初始阻值大大降低,实现免大电压初始化的过程;由于本发明中选通层是在制备上电极的过程中与阻变层自发发生氧化还原反应形成的,无需额外的高温退火处理,同时该自发氧化层的存在也刚好解决了界面扩散问题;此外,阻变材料层中氧空位晶粒区域也可以作为后面阻变材料层发生阻变形成晶化导电丝的种子,将导电丝形成区域局域化,从而大大减小整体器件的循环间与器件间的差异性,提高器件的脉冲擦写次数以及保持能力。

21.本发明提供一种双极选通忆阻器的制备方法及双极选通忆阻器,本发明制得的整体器件呈现出稳定的内建双极选通的忆阻特性,该器件可以有多重操作模式,在小电压操作范围下表现出双极选通特性,该层具有优异的双向开关特性,脉冲开关速度小于20ns,高低阻开关比大于100,高开态电流大于1ma,耐擦写次数大于10

12

,循环间及器件间的差异性很小,小于6%。大电压操作范围下表现出具有内建双极选通的忆阻特性曲线,由于该内建双极选通层的存在,电压小于该特性中的阈值开启电压时都会被强制关断,只有当电压大于其阈值电压时,才可以对阻变层进行擦写操作,所以该内建层能够有效限制大规模交叉阵列结构中的漏电流路径问题,大大提高了集成规模且不而外增加工艺复杂度,具有很大的应用价值。此外,内建选通层将整体忆阻器件的开态电流(开态电流由于选通层的关断使得从ma降到ua)减小了至少100倍,意味着忆阻器件的开启功耗也至少降低了100倍。

附图说明

22.图1为根据本发明的一实施例绘示一种具有内建双极选通特性的忆阻器的简化结构剖面图;

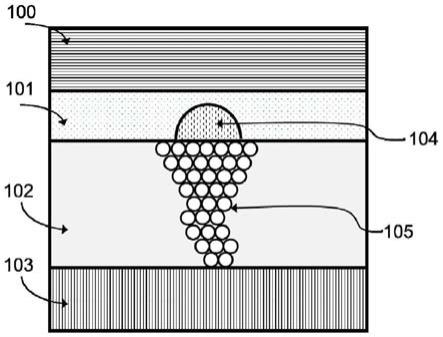

23.图2为本发明实施例提供的一种采用溅射法来制备电极材料制备系统简化图;

24.图3为本发明实施例提供的又一种采用化学沉积法来制备电极材料制备系统简化图;

25.图4为本发明实施例提供的另一种采用溅射法来制备阻变材料制备系统简化图;

26.图5为本发明实施例提供的具有内建双极选通特性忆阻器在小电压操作模式下的电流

‑

电压特性曲线图;

27.图6为本发明实施例提供的具有内建双极选通特性忆阻器大电压操作范围下表现出具有内建双极选通的忆阻特性曲线图;

28.图7为本发明实施例提供的内建双极选通的忆阻特性曲线在不同电压范围下对应的器件机理模型图;

29.图8为本发明实施例提供的具有内建双极选通特性的忆阻器结构的tem图;

30.图9为本发明实施例提供的具有内建双极选通特性的忆阻器循环特性示意图;

31.图10为本发明实施例提供的具有内建双极选通特性的忆阻器保持特性示意图;

32.在所有附图中,相同的附图标记用来表示相同的元件或结构,其中具体包括:100:上电极;主要是金属铌nb、钒v、镍ni、铬cr、钛ti、钴co、锆zr、钌ru中的任一种;101:自发氧化形成的内建双极选通层;102:阻变材料层;主要为一元或多元金属的氧化物材料;103:下电极;主要是金属pt、au、ta、al、pd、hf、w、tin、tiw中的任一种;104:内建双极选通层达到阈

值电压后形成晶化区域;105:阻变材料达到开启电压后形成晶化导电丝区域。

具体实施方式

33.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

34.为此,本发明提出了一种新型内建双极选通的忆阻器件结构及其制备方法,基于该可靠结构的器件显示出优异的整体性能改善,例如免大电压初始化过程、常温下制备、结构简单、多种操作模式下性能优异、无需高温退火步骤。基于本发明的内建双极选通忆阻器交叉阵列堆叠结构将为下一代的非易失性存储、全忆阻神经网络架构、可重构逻辑电路提供了硬件基础。

35.本发明针对上述存在的工艺制备问题,提供一种选通的忆阻器及其制备方法,通过上电极与阻变材料在制备过程中的自发氧化过程形成优异的内建双极选通特性,为交叉阵列堆叠结构将为下一代的非易失性存储、全忆阻神经网络架构、可重构逻辑电路提供了硬件基础。

36.本发明经过大量实验研究,开发了一种通过上电极与阻变材料在制备过程中的自发氧化过程形成优异的内建双极选通特性的忆阻器件,所述器件从上至下包括上电极、阻变材料层、下电极,其中上电极采用金属铌nb、钒v、镍ni、铬cr、钛ti、钴co、锆zr、钌ru中的任一种,阻变材料为一元或多元金属的氧化物材料,下电极采用金属pt、au、ta、al、pd、hf、w、tin、tiw中的任一种。

37.进一步地,上述技术方案中所述的上电极在使用磁控溅射工艺沉积过程中,通过控制溅射功率及背景真空度,使得上电极以及阻变材料间会发生氧化还原反应,从而在上电极与阻变材料界面处自发形成一层上电极材料元素的氧化物层。该层氧化物厚度约为1nm~10nm。

38.进一步地,上述技术方案中所述的上电极元素氧化物具有双极选通的特性。

39.进一步地,上述技术方案中所述的上电极在使用磁控溅射工艺沉积过程中,由于功率及背景真空度的影响,在上电极以及阻变材料间会发生氧化还原反应,所以在阻变层薄膜中会出现大量的晶粒区域,这些区域呈现出低阻特性。

40.进一步地,上述技术方案中所述的上电极薄厚厚度为50nm~1um,阻变材料厚度约为5nm~50nm,下电极材料厚度为50nm~1um。

41.进一步地,上述技术方案中所述的内建双极选通特性的忆阻器件特征尺寸为2nm~1000nm。

42.本发明的实施例将配合图1至图10详述如下:

43.图1为根据本发明的一实施例绘示一种具有内建双极选通特性的忆阻器的简化结构剖面图,其中,这个内建双极选通层101由上电极100制备过程中与阻变材料102自发形成的;本发明通过上电极100与阻变材料102在物理沉积制备过程中发生的氧化还原反应,从而在上电极与阻变材料界面处自发氧化过程形成一层上电极元素的内建双极选通层101,该层具有优异的双向开关特性,当整体器件外部施加电压大小达到内建双极选通层的阈值电压时,会形成晶化区域104,该层的阻值状态由关态电阻大小变为开态电阻大小,该层具

有优异的双向开关特性,脉冲开关速度<20ns,高低阻开关比>100,高开态电流>1ma,耐擦写次数>10

12

,循环间及器件间的差异性很小<6%。

44.上电极材料会与阻变材料层发生氧化还原过程,使得阻变材料层失去很多氧,从而在阻变材料层中形成大量的氧空位晶粒区域,这些区域呈现出低阻状态,从而将整体器件的初始阻值大大降低,实现免大电压初始化的过程;此外,这些区域也可以作为后面阻变材料层发生阻变形成晶化导电丝105的种子,从而大大减小整体器件的循环间与器件间的差异性,提高器件的脉冲擦写次数以及保持能力。

45.本发明制得的整体器件呈现出稳定的内建双极选通的忆阻特性,该器件可以有多重操作模式,在小电压操作范围下表现出双极选通特性,大电压操作范围下表现出具有内建双极选通的忆阻特性曲线,由于该内建双极选通层的存在,电压小于该特性中的阈值开启电压时都会被强制关断,只有当电压大于其阈值电压时,才可以对阻变层进行擦写操作,所以该内建层能够有效限制大规模交叉阵列结构中的漏电流路径问题,大大提高了集成密度且不而外增加工艺复杂度,具有很大的应用价值。

46.图2为本发明实施例提供的一种采用溅射法来制备阻变材料制备系统简化图;如图2所示,上电极100与下电极103采用物理气相沉积来制备,气体氛围为惰性气体,如氩气。上电极100溅射时的背景真空度由真空泵的抽取以及惰性气体通入速度来平衡控制,合适的真空度范围为5*10

‑3pa~5*10

‑4pa。在这个范围内,由电源施加的上电极靶材上轰击下来的金属粒子由于具有较大的动能,从而与已经制备好下电极与阻变材料层的样品发生氧化还原反应,从而自发形成内建双极选通层102。下电极103溅射时的背景真空度由真空泵的抽取以及惰性气体通入速度来平衡控制,合适的真空度范围为<9*10

‑4pa。在这个范围内,下电极才能保证在制备过程中不被氧化。在沉积上下电极过程中,需要给晶圆样品一个旋转装置,另其保持固定的匀速旋转,速度选择范围为10rpm~15rpm,从而保证沉积到样品各个位置的薄膜材料均匀一致。

47.在另一个用来形成内建选通层的电极沉积系统简化图实施例中,如图3所示,为绘示一种采用化学气相沉积来形成高低空位浓度阻变材料的系统简化图。此系统包含真空槽,其中有电极材料分的反应源与晶圆基片。反应源是进行化学反应的原料,并连接至外部的电源,用来控制其反应过程的进行。该真空槽配置机械泵或真空泵将沉积前的腔内真空度抽到至少10

‑3pa以下。真空槽配置有反应气体源,提供不同电极所需的原料。槽内还有每次沉积循环结束后的吹扫系统,用来带走腔内残留的反应原料,确保每个反应循环都能精确控制反应原料的比例。槽内还应包括控温系统用来控制真空腔内的反应温度,范围从50℃~500℃。使用相应的反应源并调控反应参数后,晶圆基片上便可以沉积得到不同电极材料。采用化学气相沉积方法来形成内建选通的忆阻器件时,上电极金属元素的活性需要比阻变层材料的金属元素高,那么上电极金属沉积到阻变层表面时,两者会发生氧化还原反应,在两者界面处形成上电极元素的氧化物层,即内建选通层。值得注意的是,图3仅为用来描述本实施例的简化图。溅射反应槽为半导体制造工厂的标准配备,可以在不同商业来源中取得。

48.图4为本发明实施例提供的一种采用溅射法来制备阻变材料制备系统简化图;阻变材料102采用物理气相沉积来制备,气体氛围为惰性气体与氧气。阻变材料102溅射时的背景真空度由真空泵的抽取、惰性气体与氧气通入速度来平衡控制,合适的真空度范围为>

5*10

‑3pa。在沉积阻变材料过程中,需要给晶圆样品一个旋转装置,另其保持固定的匀速旋转,速度选择范围为10rpm~15rpm,从而保证沉积到样品各个位置的薄膜材料均匀一致。

49.本发明的一实施例中之中,上电极可以为钒(v),阻变层可以为hwo(铪钨共价氧化物),下电极可以为铂(pt),上电极与阻变层界面处自发氧化形成的内建双极选通层可以为vox,0<x<2.5。

50.图5为本发明实施例提供的具有内建双极选通特性忆阻器在小电压操作模式下的电流

‑

电压特性曲线图;对上述器件进行电学特性量测,具体为通过测试仪器在上电极施加操作电压,下电极接地。初始状态下,阻变材料层为低阻,内建选通层则为关态阻值,所以整体器件阻值表现为内建选通层的关断阻值大小。对器件正向操作过程中,操作电压由0增大到1.5v再回到0v,在0到1.5v的施加过程中,器件达到阈值电压(内建选通层的阈值电压约等于1v)便会发生电流值由小变大的突变,内建选通层则由高阻转变为低阻;在1.5到0v的施加过程中,器件达到保持电压(内建选通层的保持电压约等于0.5v)便会电流值自发由小变大的突变,内建选通层则由低阻转变为高阻。对器件负向操作过程中,操作电压由0增大到

‑

1.5v再回到0v,在0到

‑

1.3v的施加过程中,器件达到负向阈值电压(内建选通层的阈值电压约等于

‑

1v)便会发生电流值由小变大的突变,内建选通层则由高阻转变为低阻;在

‑

1.3到0v的施加过程中,器件达到保负向持电压(内建选通层的负向保持电压约等于

‑

0.5v)便会电流值自发由小变大的突变,内建选通层则由低阻转变为高阻,由于该内建双极选通层的存在,正反向电压小于该特性中的阈值开启电压时都会被强制关断,只有当正反向电压大于其正反向阈值电压时,才可以对阻变层进行擦写操作,所以该内建层能够有效限制大规模交叉阵列结构中的漏电流路径问题,大大提高了集成密度且不而外增加工艺复杂度,具有很大的应用价值。该层具有优异的双向开关特性,脉冲开关速度<20ns,高低阻开关比>100,高开态电流>1ma,耐擦写次数>10

12

,循环间及器件间的差异性很小<6%。

51.具体地,如图5所示;大电压下本发明提供的忆阻器特性跟普通忆阻器特性相比,小电压时多了个内建选通的钳制,所以低阻变为选通层的关断阻值,整体阻值升高。如果要用器件的选通特性就在小电压下操作就行,一般用于选通开关、神经元电路等等;如果要用器件的忆阻器特性则在大电压范围下操作完成擦写阻态,0.1v下的读取的高低阻就可以用作非易失存储信息。

52.图6为本发明实施例提供的具有内建双极选通特性忆阻器大电压操作范围下表现出具有内建双极选通的忆阻特性曲线图;对上述器件进行电学特性量测,具体为通过测试仪器在上电极施加操作电压,下电极接地。初始状态下,阻变材料层为高阻,内建选通层则为关态阻值,所以整体器件阻值表现为阻变材料层的高阻值大小。对器件正向操作过程中,操作电压由0增大到2.5v再回到0v,在0到2.5v的施加过程中,器件达到阻变层开启电压(阻变层开启电压约等于1.5v,内建选通层的阈值电压约等于1v)便会发生电流值由小变大的突变,阻变层、内建选通层都由高阻转变为低阻;在2.5到0v的施加过程中,外部施加电压大小减小到内建选通层的保持电压(内建选通层的保持电压约等于0.5v)便会电流值自发由小变大的突变,内建选通层则由低阻转变为高阻,此时整体忆阻器件的阻态内建选通层的关断阻值大小,所以忆阻整体器件的开态电流减小了至少100倍,意味着器件的开启功耗也至少降低了100倍。

53.对器件负向操作过程中,操作电压由0增大到

‑

3v再回到0v,在0到

‑

3v的施加过程

中,器件达到负向阈值电压(内建选通层的阈值电压约等于

‑

1v)便会发生电流值由小变大的突变,内建选通层则由高阻转变为低阻,内建选通层处于开态后继续增大外部施加电压时,压降都落在阻变材料层上,阻变材料层发生电流由大变小的渐变过程,阻变层被关断且阻态大于内建选通层的关态阻值;在

‑

3到0v的施加过程中,器件整体的阻态由阻变层决定,所以整体器件阻值表现出高阻值。由于该内建双极选通层的存在,正反向电压小于该特性中的阈值开启电压时都会被强制关断,只有当正反向电压大于其正反向阈值电压时,才可以对阻变层进行擦写操作,所以该内建层能够有效限制大规模交叉阵列结构中的漏电流路径问题,大大提高了集成密度且不而外增加工艺复杂度,具有很大的应用价值。大操作电压范围下,整体器件具有优异内建双极选通的忆阻特性,整体的开态及关态阻值分别为100k与10m,所以器件功耗整体降低了至少100倍,开关比>100,耐擦写次数>10

10

,阻态保持时间在85摄氏度下>10000s。

54.图7为本发明实施例提供的内建双极选通的忆阻特性曲线在不同电压范围下对应的器件机理模型图。a图对应图6特性曲线中的操作电压达到阻变层开启电压且未减小到内建选通层保持电压的这个施加过程,器件达到阻变层开启电压(阻变层开启电压约等于1.5v,内建选通层的阈值电压约等于1v)便会发生电流值由小变大的突变,阻变层形成贯通的晶态导电细丝,内建选通层形成半球形的晶化区域阻变层、内建选通层都由高阻转变为低阻;b图对应图6特性曲线中的阻变层开启下,外部正向施加电压小于正向阈值电压,外部反向电压小于负向阈值电压的这个施加过程,阻变层已经形成贯通的晶态导电细丝,内建选通层由于压降不足以使其打开,阻变层为低阻,内建阻变层为关断状态;c图对应图6特性曲线中的外部负向施加电压大于内建选通层的负向阈值电压的这个施加过程,此时内建选通层被打开,内建阻变层为打开状态,主要压降落在阻变层上,阻变层熔断贯通的晶态导电细丝,阻变层由低阻变为高阻;d图对应图6特性曲线中的阻变层被关断后

‑

3v到0v的外部施加情况,此时阻变层阻值比选通层关断电阻值高,压降都落在阻变层上。

55.图8为具有内建双极选通特性的忆阻器结构的透射电子显微镜(tem)图;该图从左至右分别为本发明实施例之一的pt下电极,hwo阻变材料层,制备过程中自发氧化形成的内建选通层vox以及v上电极。上电极到阻变材料层中都存在一些自发产生的晶化区域。

56.图9为本发明实施例提供的具有内建双极选通特性的忆阻器循环特性图;对器件进行脉冲循环特性量测,采用图6中的操作方法将器件置到低阻态,通过测试仪对器件的上电极施加单个负脉冲(幅值为

‑

3v,脉宽为20ns),下电极接地,器件则由低阻态转变为高阻态(用小电压读取器件阻态),接着通过测试仪对器件的上电极施加单个正脉冲(幅值为2v,脉宽为20ns),下电极接地,器件则由低阻态转变为高阻态(用小电压读取器件阻态)。重复施加上述的正负脉冲对,统计循环次数,可以明显看到本发明改进的器件可以在10

10

的循环次数后保持器件不坏,大大提升了器件的擦写能力,确保器件在实际的存取数据中能进行高速、多次的操作,此外内建选通层将整体器件的开态电流减小了至少100倍,意味着器件的开启功耗也至少降低了100倍。

57.图10为本发明实施例提供的具有内建双极选通特性的忆阻器保持特性图;对器件进行保持特性量测,将环境温度升至85℃,通过测试仪对器件的上电极施加不同电压进行阻值读取(最高阻态读电压为0.1v,选通层关断下的低阻读电压为0.1v,选通层打开下的低阻读取读电压为1.1v),下电极接地,可以发现本发明的改进器件的多个阻态都具有优异的

保持特性。

58.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1