集成式半导体装置的制备方法和集成式半导体装置与流程

monolithic integration of si

‑

based ic and iii

‑

v epilayers

‑

a mass manufacturable approach for active matrix micro

‑

led displays[j]。

[0009]

另外,专利文献cn110462850a和tw201724442a也公开了整面金属键合和图形化金属对准键合方案。

[0010]

然而,图形化金属对准键合以及整面金属键合方案都存在着以下缺点。

[0011]

图形化金属对准键合方案的缺点主要基于其对于对准精度的要求极高,进而造成设备和制造成本高昂,在键合过程中因为金属流动或者对准偏差等问题,每个对准模块的最小尺寸限制较大,一般只能进行单个器件几十微米以上量级的作业,对集成器件的密度有很高要求。

[0012]

整面金属键合方案的缺点主要在于键合后的键合金属的图形化工作中,由于键合金属涉及多种材料,进而在键合过程中会形成复杂的多种不同晶相,这对图形化带来了极大的挑战,一般的干法刻蚀设备无法满足刻蚀需求,进而其采用了电子束刻蚀方案,但是金属刻蚀过程中很容易出现金属粒子四散、去除不净带来的器件漏电问题,并且因为电子束刻蚀无法形成良好的阻挡层也无法做到选择性刻蚀,极易导致过刻蚀,进而过刻蚀导致了驱动相关器件损伤。

[0013]

另外,因为图形化金属键合和整面金属键合都面临着键合金属的刻蚀问题,所以为保证能够进行金属刻蚀,需要预留相对较宽的刻蚀沟道空间,这给高度集成器件的密度带来了不利影响。以专利tw201724442a为例,该类型器件因键合金属存在的厚度影响,金属刻蚀时需满足接近1:1的高宽比,导致每个像素中需要预留50%宽度来满足金属刻蚀,最终使得真正有源区仅剩50%的空间。

[0014]

另外,图形化金属键合和整面金属键合的金属键合过程都需要在高温环境下进行,加上不同材料体系的热膨胀系数差异的客观因素,导致了键合后的晶圆出现翘曲的问题,容易导致有效结构开裂、断层以及翘曲过大带来的制造困难等问题。

[0015]

因此,如何避免图形化金属键合和整面金属键合的上述各种缺点,便成为亟待解决的问题。

技术实现要素:

[0016]

有鉴于此,本发明提供一种集成式半导体装置的制备方法和集成式半导体装置,采用非金属键合手段,以解决图形化金属对准键合方案成本高和集成密度受限,整面金属键合方案的漏电和器件损伤,以及金属键合带来的晶圆翘曲、结构开裂和断层等问题。

[0017]

本发明的技术方案是这样实现的:

[0018]

一种集成式半导体装置的制备方法,包括:

[0019]

提供第一衬底,并在所述第一衬底表面形成第一非金属键合材料层;

[0020]

提供第二衬底,并在所述第二衬底表面形成器件材料层;

[0021]

在所述器件材料层表面形成第二非金属键合材料层;

[0022]

将所述第二非金属键合材料层和所述第一非金属键合材料层进行键合形成非金属键合层;

[0023]

去除所述第二衬底;

[0024]

对所述器件材料层进行图形化刻蚀以获得含有至少一个半导体器件的器件层。

[0025]

进一步,所述半导体器件为微米发光二极管micro

‑

led,所述器件材料层为micro

‑

led材料;

[0026]

所述第一衬底中含有驱动集成电路,所述第一衬底表面形成于所述第一衬底的包含所述驱动集成电路的金属触点的表面。

[0027]

进一步,所述方法还包括:

[0028]

将所述器件层与所述第一衬底进行桥接。

[0029]

进一步,所述的将所述器件层与所述第一衬底进行桥接,包括:

[0030]

将所述器件层中所有所述micro

‑

led的第一极与所述第一衬底中的金属触点进行桥接。

[0031]

进一步,在将所述器件层与所述第一衬底进行桥接之后,所述方法还包括:

[0032]

在所述器件层上制备公共电极层,所述公共电极层同时连接于所述器件层中所有所述micro

‑

led的第二极。

[0033]

进一步,所述方法还包括:

[0034]

在包含所述器件层的基体表面制备光学结构层。

[0035]

进一步,所述光学结构层包括微型透镜和/或微型反射杯。

[0036]

进一步,所述方法还包括:

[0037]

在所述微型反射杯中填充颜色转换材料并密封。

[0038]

进一步,所述方法还包括:

[0039]

对包含所述第一衬底和所述器件层的基体进行切割,以获得含有设定数量的所述半导体器件的集成式半导体装置。

[0040]

一种集成式半导体装置,包括:

[0041]

第一衬底;

[0042]

非金属键合层,所述非金属键合层位于所述第一衬底的表面;

[0043]

器件层,所述器件层位于所述非金属键合层上,所述器件层含有至少一个半导体器件;

[0044]

其中:

[0045]

所述非金属键合层由形成于所述第一衬底表面的第一非金属键合材料层和形成于一器件材料层的一第二非金属键合材料层键合而成,所述器件层由所述器件材料层经过图形化刻蚀而成。

[0046]

从上述方案可以看出,本发明的集成式半导体装置的制备方法和集成式半导体装置中,通过非金属键合方式,避免了金属键合后图形化刻蚀金属四溢以及清洗金属粒子残留导致的漏电问题,通过非金属键合方式,形成了有效的刻蚀高选择比,增加工艺窗口并提高可行性。

[0047]

另外,本发明中,通过通孔方式减小了器件间距,通孔尺寸小,同时还因不需将非金属键合层完全隔断,可实现同尺寸下更大有源区面积或者更高集成度。

[0048]

本发明中,通过非金属键合方式,可以使多个目标晶圆集成式光电表现(如透光性)不再受键合金属影响,可以制备垂直集成分布的多个器件,可以在相同面积内实现更大的单个器件尺寸或同样尺寸时的更多的器件集成密度及成品数量产出。

[0049]

本发明中,可自由定义触点接触方式,可自由采用共极或非共极桥接,并且器件之

间的串并联方案更加便利。

[0050]

另外,相比金属键合需要高温,本发明中的非金属键合可实现低温键合优化热失配,避免热失配带来的良率及可靠性损伤。

附图说明

[0051]

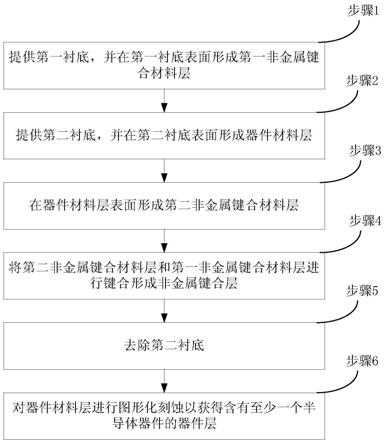

图1为本发明实施例的集成式半导体装置的制备方法步骤流程图;

[0052]

图2a~图2n为采用本发明实施的集成式半导体装置的制备方法的器件结构演化过程结构示意图;

[0053]

图3a~图3d为本发明实施例中的几种桥接方式结构示意图。

[0054]

附图中,各标号所代表的部件名称如下:

[0055]

101、驱动背板

[0056]

102、第一非金属键合材料层

[0057]

103、金属触点

[0058]

201、晶圆衬底

[0059]

202、micro

‑

led材料层

[0060]

2021、缓冲层

[0061]

2022、n型氮化镓层

[0062]

2023、量子阱层

[0063]

2024、p型氮化镓层

[0064]

2025、欧姆接触层

[0065]

203、第二非金属键合材料层

[0066]

204、micro

‑

led结构

[0067]

301、非金属键合层

[0068]

401、桥接层

[0069]

402、公共电极层

[0070]

501、钝化层

[0071]

601、大发光角结构

[0072]

602、小发光角结构

[0073]

603、蝶形发光角结构

[0074]

604、微型反射杯

[0075]

701、颜色转换材料

具体实施方式

[0076]

为了使本发明的目的、技术方案及优点更加清楚明白,以下参照附图并举实施例,对本发明作进一步详细说明。

[0077]

如图1所示,本发明实施例提供了一种集成式半导体装置的制备方法,主要包括以下步骤:

[0078]

步骤1、提供第一衬底,并在第一衬底表面形成第一非金属键合材料层;

[0079]

步骤2、提供第二衬底,并在第二衬底表面形成器件材料层;

[0080]

步骤3、在器件材料层表面形成第二非金属键合材料层;

[0081]

步骤4、将第二非金属键合材料层和第一非金属键合材料层进行键合形成非金属键合层;

[0082]

步骤5、去除第二衬底;

[0083]

步骤6、对器件材料层进行图形化刻蚀以获得含有至少一个半导体器件的器件层。

[0084]

在可选实施例中,第一衬底的材料可以为第一代半导体材料(如硅、锗等)、第二代半导体材料(如砷化镓、磷化铟等)、第三代半导体材料(如氮化镓、碳化硅、氧化锌、金刚石等)或半成品及成品器件等。

[0085]

在可选实施例中,第一非金属键合材料层的材料可以为氧化硅、氮化硅、氧化态钛、氧化镁、氧化铝、氮化镓、砷化镓等材料中的至少一种所组成的单层或叠层半导体材料。

[0086]

在可选实施例中,在第一衬底表面形成第一非金属键合材料层可以采用化学气相沉积(cvd)、原子层沉积(ald)、溅射(sputter)、蒸镀等方法实现。

[0087]

在可选实施例中,第一非金属键合材料层除了具有键合功能外,也可以具备反射、散热等功能。

[0088]

在可选实施例中,第一非金属键合材料层为在第一衬底表面的整面形成。

[0089]

在可选实施例中,第一非金属键合材料层为图形化的。

[0090]

在可选实施例中,第二衬底的材料可以为第一代半导体材料、第二代半导体材料、第三代半导体材料或半成品及成品器件等。

[0091]

在可选实施例中,器件材料层的材料包括从深紫外到远红外波长的材料体系。

[0092]

在可选实施例中,第二非金属键合材料层的材料可以为氧化硅、氧化铝、氮化硅等薄膜材料。

[0093]

在可选实施例中,第二非金属键合材料层为在器件材料层表面的整面形成。

[0094]

在可选实施例中,第二非金属键合材料层为图形化的。

[0095]

在可选实施例中,所述的将第二非金属键合材料层和第一非金属键合材料层进行键合形成非金属键合层包括:

[0096]

将整面形成的第一非金属键合材料层和整面形成的第二非金属键合材料层直接键合。

[0097]

在可选实施例中,所述的将第二非金属键合材料层和第一非金属键合材料层进行键合形成非金属键合层包括:

[0098]

将图形化的第一非金属键合材料层和图形化的第二非金属键合材料层进行对准键合。

[0099]

在可选实施例中,去除第二衬底可采用采用激光剥离去除、化学药液去除或者机械研磨去除。

[0100]

在可选实施例中,对器件材料层进行图形化刻蚀以获得含有至少一个半导体器件的器件层,可采用光刻加刻蚀方法实现。其中,刻蚀可采用干法或者湿法刻蚀方法。

[0101]

在可选实施例中,器件层中的半导体器件的形状可以为圆柱、梯形、三角等结构形状,器件层中的半导体器件分布可以为整齐排列,也可以为交叉排列。

[0102]

在可选实施例中,半导体器件为微米发光二极管micro

‑

led,器件材料层为micro

‑

led材料;第一衬底中含有驱动集成电路,第一衬底表面形成于第一衬底的包含驱动集成电

路的金属触点的表面。

[0103]

在可选实施例中,图形化的第一非金属键合材料层可以覆盖于驱动集成电路的金属触点的,也可以不覆盖于驱动集成电路的金属触点而将驱动集成电路的金属触点裸露。

[0104]

在可选实施例中,器件材料层(micro

‑

led材料)包括依次堆叠于第二衬底的缓冲层、n型层、量子阱层、p型层、欧姆接触层。

[0105]

在可选实施例中,n型层材料为n型氮化镓、p型层为p型氮化镓。

[0106]

在可选实施例中,缓冲层材料可以为氮化镓、铝镓氮、铟镓氮等材料及其合金。

[0107]

在可选实施例中,欧姆接触层的材料可以为金属或者金属氧化物。具体地,欧姆接触层的材料包括银、镍、金、铝等金属材料,也可以包括铟锡氧化物,氧化锌等金属氧化物材料,欧姆接触层可以为单层或者多层结构。

[0108]

在可选实施例中,在欧姆接触层和第二非金属键合材料层之间还可以设有反射性材料或结构,如布拉格反射层等。

[0109]

在可选实施例中,欧姆接触层可以是整面的,也可以是图形化的。

[0110]

关于器件材料层的制备,可采用现有技术实现,此处不再赘述。

[0111]

在可选实施例中,驱动集成电路包括tft薄膜晶体管和/或ltps低温多晶硅和/或cmos集成电路。

[0112]

在可选实施例中,本发明实施例的集成式半导体装置的制备方法还可进一步包括:步骤7、将器件层与第一衬底进行桥接。

[0113]

具体地,在可选实施例中,步骤7包括:

[0114]

步骤71、将器件层中所有micro

‑

led的第一极与第一衬底中的金属触点进行桥接。

[0115]

在可选实施例中,micro

‑

led的第一极为p极。在可选实施例中,p极为micro

‑

led中的p型氮化镓层。

[0116]

除此以外,在其他可选实施例中,步骤7还可以包括:

[0117]

步骤71’、将器件层中所有micro

‑

led的第二极与第一衬底中的金属触点进行桥接。

[0118]

其中,micro

‑

led的第二极为n极。在可选实施例中,n极为micro

‑

led中的n型氮化镓层。

[0119]

在可选实施例中,步骤71和步骤71’可以选择性地执行其中之一,也可以全部执行。以下实施例是在执行步骤71而并不执行步骤71’的基础上执行。

[0120]

在可选实施例中,在完成步骤7的将器件层与第一衬底进行桥接之后,本发明实施例的集成式半导体装置的制备方法还包括:

[0121]

步骤8、在器件层上制备公共电极层,公共电极层同时连接于器件层中所有micro

‑

led的第二极。

[0122]

其中,micro

‑

led的第二极为n极。在可选实施例中,n极为micro

‑

led中的n型氮化镓层。

[0123]

完成步骤8后,便形成了一种共n极的micro

‑

led发光矩阵。

[0124]

在可选实施例中,在完成步骤8之后,本发明实施例的集成式半导体装置的制备方法还包括:

[0125]

步骤9、在包含器件层的基体表面制备光学结构层。

[0126]

在可选实施例中,光学结构层包括微型透镜和/或微型反射杯。

[0127]

在可选实施例中,微型透镜和微型反射杯的材料可以为透明绝缘的无机材料或者有机材料,例如氧化硅、氧化铝、su8(一种光敏有机硅类型材料)、聚酰亚胺等。其中,无机材料可采用cvd或者sputter等方法镀膜后使用图形化刻蚀工艺制备而成,无机材料可通过曝光和高温烘烤制备。

[0128]

在可选实施例中,若步骤9中进行的是微型反射杯的制备,则在完成步骤9之后,本发明实施例的集成式半导体装置的制备方法还包括:

[0129]

步骤10、在微型反射杯中填充颜色转换材料并密封。

[0130]

在可选实施例中,颜色转换材料为荧光粉、量子点等材料。

[0131]

在可选实施例中,在完成步骤10之后,本发明实施例的集成式半导体装置的制备方法还包括:

[0132]

步骤11、对包含第一衬底和器件层的基体进行切割,以获得含有设定数量的半导体器件的集成式半导体装置。

[0133]

以下结合micro

‑

led制备过程的具体实例,对本发明实施例的集成式半导体装置的制备方法进行进一步说明。

[0134]

步骤a1、如图2a所示,提供驱动背板(第一衬底)101,并在驱动背板101表面形成第一非金属键合材料层102。

[0135]

其中,驱动背板101中包含有tft薄膜晶体管驱动电路、ltps低温多晶硅驱动电路或者cmos集成电路驱动电路。第一非金属键合材料层102形成在驱动背板101的金属触点103的一面。

[0136]

其中,第一非金属键合材料层102的材料可以是氧化硅、氮化硅、氧化钛、氧化镁、氧化铝、氮化镓、砷化镓等单层或叠层半导体材料。第一非金属键合材料层102的制备方式可以是化学气相沉积(cvd)、原子层沉积(ald)、溅射(sputter)、蒸镀等方法,除键合功能外,第一非金属键合材料层102也可以具备反射、散热等能力。

[0137]

其中,第一非金属键合材料层102可以是如图2a所示整面的,也可以是图形化的,若第一非金属键合材料层102为图形化的,则图形化的第一非金属键合材料层102可以覆盖金属触点103,也可以裸露金属触点103。

[0138]

步骤a2、如图2b所示,提供晶圆衬底(第二衬底)201,并在晶圆衬底201表面形成micro

‑

led材料层202。

[0139]

其中,晶圆衬底201的材料例如蓝宝石或者碳化硅。

[0140]

其中,micro

‑

led材料层202包括依次堆叠于晶圆衬底201的缓冲层2021、n型氮化镓层2022、量子阱层2023、p型氮化镓层2024和欧姆接触层2025。

[0141]

步骤a3、如图2c所示,在micro

‑

led材料层202表面形成第二非金属键合材料层203。

[0142]

其中,第二非金属键合材料层203可以是氧化硅、氧化铝、氮化硅等薄膜材料。第二非金属键合材料层203的材料与第一非金属键合材料层102的材料相对应。

[0143]

其中,在欧姆接触层2025和第二非金属键合材料层203之间可以有反射性材料或结构,如布拉格反射层等。

[0144]

其中,第二非金属键合材料层203可以是如图2c所示整面的,也可以是图形化的。

[0145]

步骤a4、将第二非金属键合材料层203和第一非金属键合材料层102进行键合形成非金属键合层301,如图2d所示。

[0146]

其中,对于第一非金属键合材料层102和/或第二非金属键合材料层203是整面形成的,直接将第二非金属键合材料层203和第一非金属键合材料层102进行键合;对于第一非金属键合材料层102和第二非金属键合材料层203都是图形化的,需要进行对准键合,以保证金属触点103落在符合需求的范围内。

[0147]

步骤a5、去除晶圆衬底201,如图2e所示。

[0148]

该步骤视晶圆衬底201材料而采用相应工艺。如蓝宝石材料可以采用激光剥离去除,若为硅衬底、碳化硅、氮化镓、砷化镓衬底则可采用化学药液去除或研磨去除。

[0149]

采用本发明实施例的方式还可以实现多层micro

‑

led材料层202的叠对键合。例如,在去除晶圆衬底201后,在micro

‑

led材料层202制备第一非金属键合材料层,并在另一晶圆衬底201表面制备另一micro

‑

led材料层和第二非金属键合材料层,将第二非金属键合材料层与第一非金属键合材料层键合,从而实现了两层micro

‑

led材料层的堆叠,反复采用这种方式能够实现多层micro

‑

led材料层的叠对键合。

[0150]

步骤a6、进行器件结构制备,如图2f所示。

[0151]

该步骤中,对micro

‑

led材料层202进行图形化刻蚀以获得含有至少一个micro

‑

led结构204的器件层。

[0152]

该步骤中,通过干法或湿法刻蚀去除缓冲层2021等其他牺牲层结构,暴露出欧姆接触层2025以及n型氮化镓层2022,micro

‑

led结构204的形状可以是圆柱、梯形、三角等常见结构,其分布可以是整齐排列,可以是交叉排列。

[0153]

步骤a7、将器件层中所有micro

‑

led结构204的p型氮化镓层2024与第一衬底101中的金属触点103进行桥接,如图2g所示。

[0154]

本步骤中,桥接的方式是根据需求而确定micro

‑

led结构204与金属触点103之间的桥接方式,图2g中示意出的是一种桥接方式。图3a、图3b、图3c分别示意出了另外几种桥接方式,其中,图3a为将n型氮化镓层2022与金属触点103进行桥接的方式,图3b为将g型氮化镓层2024的一侧与金属触点103进行桥接的方式,图3c为将g型氮化镓层2024和n型氮化镓层2022分别与不同的金属触点103进行桥接的方式。另外,如图3d所示,金属触点103还可以处于半导体器件(如micro

‑

led结构204)的一侧。

[0155]

在桥接前可以进行绝缘防护,该绝缘防护可将micro

‑

led结构204空间填平或仅包裹micro

‑

led结构204表面。可选择地,桥接过程中,将非金属键合层301以micro

‑

led结构204本身形状进行刻蚀,也可以选择对非金属键合层301挖孔至下方金属触点103的方式,该所挖通孔的位置、大小、数量、形状视micro

‑

led结构204的空间而定,桥接方案可以是单电极(如图2g、图3a、图3b所示),也可以是多电极(如图3c所示),桥接位置可以选择任意可通孔区域,桥接的桥接层401的材料可以是金属,如铝、钛、钛氮、铬、铂、金等一种或叠层,也可以是金属氧化物,如铟锡氧化物,氧化锌等导电材料。

[0156]

步骤a8、制备公共电极层402,如图2h、图2i、图2j所示。

[0157]

对于p极、n极均搭桥的结构(图3c所示)可以跳过本步骤。本步骤中,可以采用钝化层501覆盖平坦化(图2h)或者钝化层501覆盖(图2i、图2j)方式,钝化层501可以是氧化硅、氮化硅、氧化铝等无机材料,也可以是是聚酰亚胺、su8等有机材料。完成钝化层501的绝缘

后进行公共电极层402的制备,公共电极层402可采用金属或金属氧化物,如镍、金、锌、铬、铝、钛等单种或多种可形成欧姆接触的金属单层结构或者堆叠结构,或者采用铟锡氧化物、氧化锌等透明导电薄膜,也可以采用金属及金属氧化物的混用。

[0158]

步骤a9、制备光学结构层,如图2k、图2l、图2m所示。

[0159]

其中,光学结构层包括微型透镜,微型透镜包括大发光角结构601、小发光角结构602、蝶形发光角结构603,光学结构层还包括微型反射杯604。

[0160]

其中,微型透镜和微型反射杯的材料可以使用无机材料,如氧化硅、氧化铝等透明绝缘材料,通过cvd或sputter等方式镀膜后,使用图形化刻蚀进行制备,也可以使用有机材料,如su8,聚酰亚胺等透明绝缘材料,通过曝光和高温烘烤制备。

[0161]

步骤a10、彩色化及器件分离制备。

[0162]

其中,如图2n所示,彩色化过程是在微型反射杯604中填充颜色转换材料701。在可选实施例中,相邻三个micro

‑

led结构204的位置分别填充红、绿、蓝三色的颜色转换材料701后,该相邻三个micro

‑

led结构204可以共同组成一个像素点。颜色转换材料701例如荧光粉、量子点等材料。颜色转换材料701填充完毕后进行薄膜沉积密封或者微型透镜密封。针对不同应用,可以进行切割选择制备具备单个或多个像素的分立器件或者具备一定分辨率的显示屏幕。

[0163]

上述彩色化方案也可通过将不同颜色的micro

‑

led材料晶圆进行多次键合构成,在步骤a5完成后重复步骤a1到步骤a5中的相关过程,将构成micro

‑

led的多层材料晶圆(例如红绿蓝三色的红光砷化镓体系micro

‑

led晶圆、绿光氮化镓体系micro

‑

led晶圆、蓝光氮化镓体系micro

‑

led晶圆)全部完成集成,且每一次键合选取的键合薄膜可以根据需要键合的晶圆材料体系选取最佳组合,如蓝宝石衬底的材料可使用氧化铝

‑

氧化铝,或者氧化硅

‑

氧化硅键合,砷化镓衬底的材料可以使用砷化镓

‑

砷化镓键合,并且键合材料和晶圆间可包括欧姆接触层以及需要的光学反射或过滤层,键合顺序根据实际需求作业,如光电类型器件,从上到下的半导体材料禁带宽度依次减小,可以实现最佳取光。集成后从步骤a6开始作业,逐一图形化,完成后按照步骤a7的方案进行桥接,可以自由选择是否共极以及共极极性,完成最终集成方案,该集成桥接可以发生在驱动与晶圆器件之间以及晶圆器件与器件之间,可以选择合适的串并联以及通孔方案。

[0164]

本发明实施例的集成式半导体装置的制备方法中的各项实施例也可以用于其他类型的半导体器件的集成。

[0165]

本发明实施例还同时提供了一种集成式半导体装置,包括第一衬底、非金属键合层和器件层。其中,非金属键合层位于第一衬底的表面。器件层位于非金属键合层上,器件层含有至少一个半导体器件。其中,非金属键合层由形成于第一衬底表面的第一非金属键合材料层和形成于一器件材料层的一第二非金属键合材料层键合而成,器件层由器件材料层经过图形化刻蚀而成。

[0166]

本发明实施例的集成式半导体装置的制备方法和集成式半导体装置中,通过非金属键合方式,避免了金属键合后图形化刻蚀金属四溢以及清洗金属粒子残留导致的漏电问题,通过非金属键合方式,形成了有效的刻蚀高选择比,增加工艺窗口并提高可行性。另外,本发明实施例中,通过通孔方式减小了器件间距,通孔尺寸小,同时还因不需将非金属键合层完全隔断,可实现同尺寸下更大有源区面积或者更高集成度。

[0167]

本发明实施例中,通过非金属键合方式,可以使多个目标晶圆集成式光电表现(如透光性)不再受键合金属影响,可以制备垂直集成分布的多个器件,可以在相同面积内实现更大的单个器件尺寸或同样尺寸时的更多的器件集成密度及成品数量产出。

[0168]

本发明实施例中,可自由定义触点接触方式,可自由采用共极或非共极桥接,并且器件之间的串并联方案更加便利。

[0169]

另外,相比金属键合需要高温,本发明实施例中的非金属键合可实现低温键合优化热失配,避免热失配带来的良率及可靠性损伤。

[0170]

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明保护的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1