半导体封装结构制造方法与流程

1.本技术有关于一种半导体封装结构制造方法,尤指一种透过切割半导体封装体再进行迭合组装的半导体封装结构制造方法。

背景技术:

2.近年来由于半导体科技快速发展,芯片的功能越来越多变化,并且其尺寸越来越小。对于单一芯片来说,越多变化的功能需要更多的信号传输引脚,另一方面,越小尺寸则代表芯片以及信号传输引脚的密集化。然而,在如此大量化以及高密度的设计下,因为构造密集导致制程的复杂度大幅提高,并影响产品的可靠度,因此,制程的简化成为半导体科技持续发展的重要研究课题。

技术实现要素:

3.有鉴于此,在本技术一实施例中,提供一种半导体封装结构制造方法,透过切割半导体封装体再进行迭合组装,能够改善封装产品的可靠度,并简化组装程序,以提高产品的稳定性。

4.本技术一实施例揭露一种半导体封装结构制造方法,包括下列步骤:提供一基板,具有一底面;设置一第一电路组件与一第二电路组件于上述基板;设置一第一导电组件以及一第二导电组件于上述基板,其中上述第一导电组件以及上述第二导电组件设置于上述第一电路组件两侧,上述第二导电组件设置于上述第一电路组件与上述第二电路组件之间;形成封胶层以覆盖上述第一电路组件与上述第二电路组件、上述第一导电组件以及上述第二导电组件与上述基板以形成一封装体,并露出上述第一导电组件以及上述第二导电组件;切割上述封装体以形成分离之一第一子封装体以及一第二子封装体;翻转上述第一子封装体;以及将上述第一子封装体的上述底面与上述第二子封装体的上述底面接触。

5.本技术一实施例揭露一种半导体封装结构制造方法,包括下列步骤:提供一基板,上述基板具有一第一表面以及相对于上述第一表面之一第二表面;设置一第一电路组件与一第二电路组件于上述第一表面;设置一第一导电组件以及一第二导电组件于上述第一表面,其中上述第一导电组件以及上述第二导电组件设置于上述第一电路组件两侧,上述第二导电组件设置于上述第一电路组件与上述第二电路组件之间;形成封胶层以覆盖上述第一电路组件与上述第二电路组件、上述第一导电组件以及上述第二导电组件与上述基板以形成一封装体,并露出上述第一导电组件以及上述第二导电组件;切割上述封装体以形成分离之一第一子封装体以及一第二子封装体;将上述第一子封装体与上述第二子封装体的上述第二表面互相接触。

6.根据本技术一实施例所述的半导体封装结构制造方法,更包括设置复数接合垫于上述底面,其中位于上述第一子封装体的上述接合垫与位于上述第二子封装体的上述接合垫接触。

7.根据本技术一实施例,上述第一子封装体旋转180

°

后与上述第二子封装体接合。

8.根据本技术一实施例,上述封装体的切割处位于上述第二导电组件与上述第二电路组件之间。

9.根据本技术一实施例,上述第一导电组件以及上述第二导电组件为锡球。

10.根据本技术实施例所提供的半导体封装结构制造方法,透过切割半导体封装体再进行迭合组装,实现了半导体双面封装结构,在制程中,半导体封装结构上层与下层的组件可在同一置件程序中安装在基板上,有效地简化了组装程序,再者,透过切割的方式,相较于直接折迭基板的作法而言,避免了基板变形或碎裂而影响产品的质量,大幅改善半导体封装产品的可靠度以及生产效率。

附图说明

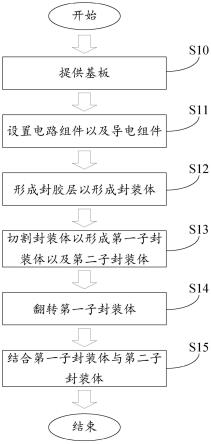

11.图1显示根据本技术一实施例所述的半导体封装结构的制造方法的操作流程图。

12.图2a-图2f显示根据本技术一实施例所述的半导体封装结构的制造方法的剖面示意图。

13.主要元件符号说明

14.10、10a、10b:基板

15.101:第一表面

16.102:第二表面、102a、102b

17.12、12a、12b:接合垫

18.14a:第一电路组件

19.14b:第二电路组件

20.16a:第一导电组件

21.16b:第二导电组件

22.18:封胶层

23.19:切割处

24.20:封装体

25.22a:第一子封装体

26.22b:第二子封装体

27.s10-s15:流程步骤

28.如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

29.为了便于本领域普通技术人员理解和实施本技术,下面结合附图与实施例对本技术进一步的详细描述,应当理解,本技术提供许多可供应用的发明概念,其可以多种特定型式实施。熟悉此技艺之人士可利用这些实施例或其他实施例所描述之细节及其他可以利用的结构,逻辑和电性变化,在没有离开本技术之精神与范围之下以实施发明。

30.本技术说明书提供不同的实施例来说明本技术不同实施方式的技术特征。其中,实施例中的各组件之配置系为说明之用,并非用以限制本技术。且实施例中图式标号之部分重复,系为了简化说明,并非意指不同实施例之间的关联性。其中,图标和说明书中使用之相同的组件编号系表示相同或类似之组件。本说明书之图示为简化之形式且并未以精确

比例绘制。为清楚和方便说明起见,方向性用语(例如顶、底、上、下以及对角)系针对伴随之图示说明。而以下说明所使用之方向性用语在没有明确使用在以下所附之申请专利范围时,并非用来限制本技术之范围。

31.再者,在说明本技术一些实施例中,说明书以特定步骤顺序说明本技术之方法以及(或)程序。然而,由于方法以及程序并未必然根据所述之特定步骤顺序实施,因此并未受限于所述之特定步骤顺序。熟习此项技艺者可知其他顺序也为可能之实施方式。因此,于说明书所述之特定步骤顺序并未用来限定申请专利范围。再者,本技术针对方法以及(或)程序之申请专利范围并未受限于其撰写之执行步骤顺序,且熟习此项技艺者可了解调整执行步骤顺序并未跳脱本技术之精神以及范围。

32.图1显示根据本技术一实施例所述的半导体封装结构的制造方法的操作流程图。图2a-图2f显示根据本技术一实施例所述的半导体封装结构的制造方法的剖面示意图。参阅图1,首先提供基板10(流程步骤s10)。如图2a所示,基板10可以是完成前处理的双层或多层电路层的基板,也就是通过提供芯层板,并在该芯层板表面形成第一导电金属层,并图案化该第一导电金属层而形成第一电路层,接着,进行增层工序,以在第一电路层形成绝缘层,再于绝缘层形成第二导电金属层,之后,图案化该第二导电金属层以形成第二电路层,如此根据需求循环此方式,持续进行增层工序,以形成多层电路层的基板。其中,基板10中的绝缘层可以是环氧树脂(expoxyresin)、聚酰亚胺(polyimide)、氰酸脂(cyanate ester)、玻璃纤维、双马来酰亚胺三嗪(bt,bismaleimide triazine)或混合环氧树脂与玻璃纤维等绝缘有机材料或陶瓷材料构成;基板10中的导电金属层的材料可以是金、银、铜、铝、钨、锡、合金或其他合适的导电材料,一般是以导电性较高的铜为主,作为该基板传递信号的导线材料,并且基板10中的绝缘层中形成多个导电通孔 (via),以便电性连接相邻的电路层。此外,基板10可通过压合法(laminated)及增层法(build-up)等方式形成,此为本领域技术人员所熟知,在此不予赘述以精简说明。基板10具有第一表面101(在图2a中为顶面)以及与第一表面101相对的第二表面102(在图2a中为底面),在第二表面102形成了复数接合垫12,接合垫12 为导体,并与基板10中的导电金属层电性连接。

33.接下来,设置第一电路组件14a、第二电路组件14b、第一导电组件16a以及第二导电组件16b于基板10(流程步骤s11)。如图2b所示,在图2b的左半部设置第一电路组件14a以及在图2b的右半部设置第二电路组件14b。根据本技术一实施例,第一电路组件14a以及第二电路组件14b可包括各种包含主动组件(有源器件)或是包括电阻器、电容器、电感器、滤波器、振荡器等的被动组件(无源器件)、数字电路或模拟电路(digital or analog circuits)等集成电路的电子组件 (electronic components),例如是有关于光电装置(optoelectronic devices)、微机电系统(micro-electromechanical systems,mems)、功率放大芯片、电源管理芯片、生物辨识装置、微流体系统(microfluidic systems)、或利用热、光线及压力等物理量变化来测量的物理传感器(physical sensor)。特别是可选择使用晶圆级封装(waferscale package,wsp)制程对影像感测装置、发光二极管(light-emitting diodes,leds)、太阳能电池(solar cells)、加速计(accelerators)、陀螺仪(gyroscopes)、指纹辨识器、微制动器(micro actuators)、表面声波组件(surface acoustic wave devices)、压力传感器(process sensors)或喷墨头(ink printer heads)等半导体芯片。

34.根据本技术一实施例,第一电路组件14a以及第二电路组件14b可以倒装方式设置于基板10的第一表面101并与基板10中的导电金属层电性连接,此外,第一电路组件14a以及第二电路组件14b也可通过胶黏剂设置在基板10的第一表面101,并通过打线方式(wire bonding)电性连接至基板10中的导电金属层,也就是本技术可实施于倒装式封装,也可实施于打线式封装,此为本领域技术人员所能推知的等效实施。另外,在图2b的左半部还设置了第一导电组件16a以及第二导电组件16b。根据本技术一实施例,第一导电组件16a以及第二导电组件16b 可为锡球。如图2b所示,第一导电组件16a以及第二导电组件16b设置于第一电路组件14a的两侧,而第二导电组件16b设置于第一电路组件14a以及第二电路组件14b之间。必须说明的是,图2b显示单一第一电路组件14a仅为示例,当第一电路组件14a为多个时,则所有第一电路组件14a设置于第一导电组件16a 以及第二导电组件16b之间。

35.接下来,于基板10上顺应性形成封胶层18(流程步骤s12)。封胶层18可提供机械稳定性及抵抗氧化、湿度及其它环境条件的保护。根据本技术一实施例,封胶层18可由一封装材料(molding material)形成。该封装材料可包括酸醛基树脂 (novolac-based resin)、环氧基树脂(epoxy-based resin)、硅基树脂(silicone-based resin) 或其它适当的包覆剂。该封装材料亦可包括适当的填充剂(filler),例如是粉状的二氧化硅。该封装材料可以是预浸渍材料(pre-impregnated material),例如是预浸渍介电材料。如图2c所示,于基板10上顺应性形成封胶层18,并覆盖第一电路组件 14a以及第二电路组件14b且覆盖部分第一导电组件16a以及第二导电组件16b,在图2c中,第一导电组件16a以及第二导电组件16b有部分未被封胶层18覆盖而露出在封胶层18的外部。形成封胶层18后,即完成根据本技术一实施例的封装体20。接下来,于第二导电组件16b与第二电路组件14b之间的切割处19切割封装体20(流程步骤s13),切割后如图2d所示。

36.参阅图2d,切割后的封装体20形成分离之第一子封装体22a以及第二子封装体22b。为了方便说明,在图2d中,将位于第一子封装体22a的基板10重新标号为10a,第二表面102重新标号为102a,接合垫12重新标号为12a,同样的,位于第二子封装体22b的基板10重新标号为10b,第二表面102重新标号为102b,而位于第二子封装体22b的接合垫12重新标号为12b。

37.接下来,将第一子封装体22a旋转180

°

(流程步骤s14),旋转后的状态如图 2e所示。必须说明的是,在本实施例中,是以翻转第一子封装体22a为例,在实 际实施时,也可翻转第二子封装体22b,所翻转的子封装体可视实际的组件特性或 制程限制而选择。接下来,将翻转后的第一子封装体22a的第二表面102a与第 二子封装体22b的第二表面102b互相接触(流程步骤s15),如图2f所示,第一子 封装体22a以及第二子封装体22b结合后,位于第二表面102b的接合垫12b以 及位于第二表面102a的接合垫12a互相接触且电性连接,以传递第一子封装体 22a以及第二子封装体22b之间的电性信号。根据本技术一实施例,所有位于第 二表面102b的接合垫12b皆与位于第二表面102a的接合垫12a一对一接触。另 外,第一子封装体22a的第二表面102a与第二子封装体22b的第二表面102b接 触的位置中,非接合垫的绝缘部分,可透过黏着剂贴合。根据本技术一实施例, 黏着层可包括聚酰亚胺(polyimide,pi)、聚乙烯对苯二甲酸酯(polyethylene terephthalate,pet)、铁氟龙(teflon)、液晶高分子(liquid crystal polymer,lcp)、 聚乙烯(polyethylene,pe)、聚丙烯(polypropylene,pp)、聚苯乙烯(polystyrene,ps)、 聚氯乙烯(polyvinyl chloride,

pvc)、尼龙(nylon or polyamides)、聚甲基丙烯酸甲 酯(polymethylmethacrylate,pmma)、abs塑料(acrylonitrile-butadiene-styrene)、 酚树脂(phenolic resins)、环氧树脂(epoxy)、聚酯(polyester)、硅胶(silicone)、聚氨 基甲酸乙酯(polyurethane,pu)、聚酰胺-酰亚胺(polyamide-imide,pai)或其组合, 但不限于此,只要具有黏着特性的材料皆可应用于本技术。

38.根据本技术实施例所提供的半导体封装结构制造方法,透过切割半导体封装体再进行迭合组装,实现了半导体双面封装结构,在制程中,半导体封装结构上层与下层的组件可在同一置件程序中安装在基板上,有效地简化了组装程序,再者,透过切割的方式,相较于直接折迭基板的作法而言,避免了基板变形或碎裂而影响产品的质量,大幅改善半导体封装产品的可靠度以及生产效率。

39.对本领域的普通技术人员来说,可以根据本技术的发明方案和发明构思结合生成的实际需要做出其他相应的改变或调整,而这些改变和调整都应属于本发明权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1