沟槽栅逆导型IGBT器件的制作方法

沟槽栅逆导型igbt器件

技术领域

1.本发明涉及一种半导体集成电路,特别是涉及一种逆导型(reverse conducting,rc)绝缘栅双极型晶体管(insulated gate bipolar transistor,igbt)器件。

背景技术:

2.在电力电子系统应用中,功率半导体器件常常需要反并联二极管来获得反向续流能力。对于igbt器件来说,由于背面p型集电区的存在,其本身很难实现反向导通,而采用反并联二极管的方式又会给系统带来额外的寄生电容及电感,增加系统的损耗。近年来逆导型igbt的出现很好地解决了这个问题,逆导型igbt在背面引入了和p型集电区掺杂类型相反的n型集电区,从而能在发射区、基区、漂移区到n型集电区之间形成反向恢复二极管,从而能为反向电流提供了导电通路,弥补了传统igbt无法反向导电的不足。然而逆导型igbt仍然存在很多问题,如开关速度较慢、工作在续流模式时器件的反向恢复特性较差等。

3.如图1所示,是现有沟槽栅逆导型igbt器件的结构示意图;以n型器件为例,现有沟槽栅逆导型igbt器件的器件单元结构包括:

4.n型掺杂的漂移区105。

5.在所述漂移区105的表面形成有p型掺杂的基区(base)107。

6.在所述漂移区105的背面形成有p型重掺杂的集电区102以及n型重掺杂的背面n型区103。

7.在所述漂移区105和所述集电区102之间还形成有n型掺杂的缓冲层104,所述缓冲层104的掺杂浓度大于所述漂移区105的掺杂浓度。缓冲层104通常作为电场终止层(field stop,fs),电场会在缓冲层104中快速下降。

8.在所述基区107和所述漂移区105之间还形成有n型掺杂的载流子存储层(carrier stored,cs)106,所述载流子存储层106的掺杂浓度大于所述漂移区105的掺杂浓度。载流子存储层106能阻挡空穴进入到基区107中,从而能增加所述漂移区105中的空穴浓度,所以,载流子存储层106也称为空穴阻挡层。空穴阻挡层的设置主要是抑制发射极对于空穴的抽取作用,增强电导调制效应,降低器件的饱和压降。

9.沟槽栅包括栅极沟槽,所述栅极沟槽穿过所述基区107。

10.沟槽上包括依次叠加的栅介质层110和栅极导电材料层111。栅介质层110通常采用二氧化硅,栅极导电材料层111通常采用多晶硅栅。

11.被所述栅极导电材料层111侧面覆盖的所述基区107的表面用于形成导电沟道。

12.在所述基区107表面形成有n型重掺杂的发射区109,所述发射区109的第一侧面和所述栅极沟槽的侧面对准。

13.在所述基区107表面还形成有p型重掺杂的基区引出区108,所述基区引出区108位于所述发射区109的第二侧面外的所述基区107表面上。

14.所述集电区102和所述背面n型区103同时和由背面金属层101组成的集电极接触。

15.所述栅极导电材料层111的顶部通过对应的接触孔连接到由正面金属层113组成

的栅电极(图1的剖面图中未显示)。

16.所述基区引出区108和所述发射区109的顶部都通过对应的接触孔连接到由所述正面金属层113组成的发射极。所述基区引出区108和顶部的接触孔之间形成欧姆接触,所述发射区109也会和顶部的接触孔之间形成欧姆接触。

17.由所述发射区109、通过所述栅极导电材料层111控制的所述基区107、所述漂移区105和所述集电区102组成igbt单元。

18.由所述基区引出区108、所述基区107、所述漂移区105和所述背面n型区103形成的寄生体二极管作为反向恢复二极管单元。

19.沟槽栅逆导型igbt器件通常由多个器件单元结构并联而成。

20.沟槽栅逆导型igbt器件在反向续流阶段igbt单元会截止,反向恢复二极管单元会导通并进行反向电流输运。

技术实现要素:

21.本发明所要解决的技术问题是提供一种沟槽栅逆导型igbt器件,能提高反向恢复的开关速度和功耗,改善反向恢复特性。

22.为解决上述技术问题,本发明提供的沟槽栅逆导型igbt器件的器件单元结构包括:

23.第一导电类型掺杂的漂移区。

24.在所述漂移区的表面形成有第二导电类型掺杂的基区。

25.在所述漂移区的背面形成有第二导电类型重掺杂的集电区以及第一导电类型重掺杂的背面源区。

26.沟槽栅包括栅极沟槽,所述栅极沟槽穿过所述基区。

27.在所述栅极沟槽中形成有第一栅极结构和第二栅极结构。

28.所述第一栅极结构包括依次叠加的第一栅介质层和第一栅极导电材料层。

29.所述第二栅极结构包括依次叠加的第二栅介质层和第二栅极导电材料层。

30.所述第一栅介质层形成在所述栅极沟槽的第一侧面。

31.所述第二栅介质层形成在所述栅极沟槽的第二侧面。

32.所述第一栅极导电材料层和所述第二栅极导电材料层之间间隔有栅间介质层。

33.被所述第一栅极导电材料层侧面覆盖的所述基区的表面用于形成第一沟道,被所述第二栅极导电材料层侧面覆盖的所述基区的表面用于形成第二沟道,形成所述第二沟道的第二阈值电压小于形成所述第一沟道的第一阈值电压。

34.在所述基区表面形成有第一导电类型重掺杂的发射区,所述发射区的第一侧面和所述栅极沟槽的侧面对准。

35.所述集电区和所述背面源区同时和由背面金属层组成的集电极接触。

36.所述第一栅极导电材料层的顶部通过对应的接触孔连接到由正面金属层组成的栅电极。

37.所述发射区和所述第二栅极导电材料层的顶部都通过对应的接触孔连接到由所述正面金属层组成的发射极。

38.由所述发射区、通过所述第一栅极导电材料层控制的所述基区、所述漂移区和所

述集电区组成igbt单元。

39.由所述发射区、通过所述第二栅极导电材料层控制的所述基区、所述漂移区和所述背面源区组成反向恢复晶体管单元。

40.进一步的改进是,在所述漂移区和所述集电区之间还形成有第一导电类型掺杂的缓冲层,所述缓冲层的掺杂浓度大于所述漂移区的掺杂浓度。

41.进一步的改进是,在所述基区和所述漂移区之间还形成有第一导电类型掺杂的载流子存储层,所述载流子存储层的掺杂浓度大于所述漂移区的掺杂浓度。

42.进一步的改进是,所述第二栅介质层的材料和所述第一栅介质层的材料都采用氧化硅,所述第一栅介质层的厚度为50nm~150nm。所述第二栅介质层的厚度为10nm~50nm。通过设置所述第二栅介质层的厚度小于所述第一栅介质层的厚度来使所述第二阈值电压小于所述第一阈值电压。

43.进一步的改进是,所述第一栅极导电材料层的材料为多晶硅或者为金属。所述第二栅极导电材料层的材料和所述第一栅极导电材料层的材料相同。

44.进一步的改进是,所述第一栅极导电材料层的底部表面和所述栅极沟槽的底部表面之间以及所述第二栅极导电材料层的底部表面和所述栅极沟槽的底部表面之间间隔有底部介质层。

45.进一步的改进是,所述第一栅极导电材料层的底部表面和所述栅极沟槽的底部表面之间的所述底部介质层由所述第一栅介质层延伸而成,所述第二栅极导电材料层的底部表面和所述栅极沟槽的底部表面之间的所述底部介质层由所述第二栅介质层延伸而成。

46.进一步的改进是,所述栅间介质层的采用包括氧化硅。

47.进一步的改进是,所述第一栅极导电材料层和所述第二栅极导电材料层之间的横向间距大小为0.2μm~1μm。

48.进一步的改进是,所述第二栅极导电材料层顶部的接触孔的长度为0.2μm~1μm。

49.进一步的改进是,在所述基区表面还形成有第二导电类型重掺杂的基区引出区,所述基区引出区位于所述发射区的第二侧面外的所述基区表面上。

50.所述基区引出区的顶部也通过对应的接触孔连接到所述发射极且所述基区引出区和顶部的接触孔之间形成欧姆接触。

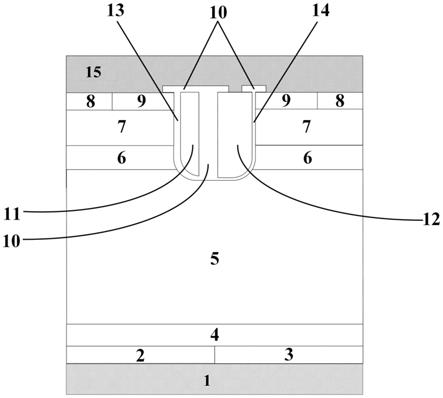

51.进一步的改进是,第一导电类型为n型,第二导电类型为p型;或者,第一导电类型为p型,第二导电类型为n型。

52.进一步的改进是,所述载流子存储层的掺杂浓度为1e16cm

‑3~1e16cm

‑3,厚度为1μm~2μm。

53.本发明在现有沟槽栅逆导型igbt器件的集成上,对器件单元结构中的沟槽栅做了特别设置,将沟槽栅设置为包括同时形成于栅极沟槽中的第一栅极结构和第二栅极结构,其中,第一栅极结构控制的第一沟道用于igbt单元的导通和截止的控制;第二栅极结构控制的第二沟道用于反向恢复晶体管的导通和截止的控制,第二栅极结构的第二栅极导电材料层会连接到发射极,在igbt单元截止并开始反向续流时,第二沟道会导通从而使得反向恢复晶体管能快速导通,和现有技术中反向恢复电流时通过寄生体二极管输运不同,本发明的反向恢复电流是通过沟道控制的反向恢复晶体管控制,通过降低反向恢复晶体管的阈值电压即开启电压,如通过降低第二栅介质层的厚度降低反向恢复晶体管的阈值电压,能

使得器件一直处于单极导电模式,从而避免进入寄生体二极管导通的双极导电模式,因此能大幅度降低功率损耗,改善器件的反向恢复特性。

54.此外,由于igbt单元的第一栅极导电材料层与漂移区的耦合面积减小,由此减弱了器件电极间的耦合作用,使得沟槽栅逆导型igbt器件的电容特性、栅电荷特性也得到了极大改善。

附图说明

55.下面结合附图和具体实施方式对本发明作进一步详细的说明:

56.图1是现有沟槽栅逆导型igbt器件的结构示意图;

57.图2是本发明实施例沟槽栅逆导型igbt器件的结构示意图。

具体实施方式

58.如图2所示,是本发明实施例沟槽栅逆导型igbt器件的结构示意图;本发明实施例沟槽栅逆导型igbt器件的器件单元结构包括:

59.第一导电类型掺杂的漂移区5。

60.在所述漂移区5的表面形成有第二导电类型掺杂的基区7。

61.在所述漂移区5的背面形成有第二导电类型重掺杂的集电区2以及第一导电类型重掺杂的背面源区3。

62.沟槽栅包括栅极沟槽,所述栅极沟槽穿过所述基区7。

63.在所述栅极沟槽中形成有第一栅极结构和第二栅极结构。

64.所述第一栅极结构包括依次叠加的第一栅介质层13和第一栅极导电材料层11。

65.所述第二栅极结构包括依次叠加的第二栅介质层14和第二栅极导电材料层12。

66.所述第一栅介质层13形成在所述栅极沟槽的第一侧面。

67.所述第二栅介质层14形成在所述栅极沟槽的第二侧面。

68.所述第一栅极导电材料层11和所述第二栅极导电材料层12之间间隔有栅间介质层10。

69.被所述第一栅极导电材料层11侧面覆盖的所述基区7的表面用于形成第一沟道,被所述第二栅极导电材料层12侧面覆盖的所述基区7的表面用于形成第二沟道,形成所述第二沟道的第二阈值电压小于形成所述第一沟道的第一阈值电压。

70.在所述基区7表面形成有第一导电类型重掺杂的发射区9,所述发射区9的第一侧面和所述栅极沟槽的侧面对准。

71.在所述基区7表面还形成有第二导电类型重掺杂的基区引出区8,所述基区引出区8位于所述发射区9的第二侧面外的所述基区7表面上。

72.所述集电区2和所述背面源区3同时和由背面金属层1组成的集电极接触。

73.所述第一栅极导电材料层11的顶部通过对应的接触孔连接到由正面金属层15组成的栅电极(图2的剖面图中未显示)。

74.所述基区引出区8、所述发射区9和所述第二栅极导电材料层12的顶部都通过对应的接触孔连接到由所述正面金属层15组成的发射极。所述基区引出区8和顶部的接触孔之间形成欧姆接触,所述发射区9也会和顶部的接触孔之间形成欧姆接触。

75.由所述发射区9、通过所述第一栅极导电材料层11控制的所述基区7、所述漂移区5和所述集电区2组成igbt单元。

76.由所述发射区9、通过所述第二栅极导电材料层12控制的所述基区7、所述漂移区5和所述背面源区3组成反向恢复晶体管单元。反向恢复晶体管单元导通时,所述发射区9作为所述反向恢复晶体管单元的漏区,所述基区7表面形成的第二沟道实现所述反向恢复晶体管单元的漏区和所述背面源区3之间的导通,实现反向电流的输运。

77.本发明实施例中,在所述漂移区5和所述集电区2之间还形成有第一导电类型掺杂的缓冲层4,所述缓冲层4的掺杂浓度大于所述漂移区5的掺杂浓度。

78.在所述基区7和所述漂移区5之间还形成有第一导电类型掺杂的载流子存储层6,所述载流子存储层6的掺杂浓度大于所述漂移区5的掺杂浓度。

79.本发明实施例中,所述第一栅介质层13的材料为氧化硅如二氧化硅。在其他实施例中,也能为:所述第一栅介质层13的材料为低介电常数材料或高介电常数材料。

80.本发明实施例中,所述第二栅介质层14的材料和所述第一栅介质层13的材料相同,通过设置所述第二栅介质层14的厚度小于所述第一栅介质层13的厚度来使所述第二阈值电压小于所述第一阈值电压。所述第二栅介质层14的材料和所述第一栅介质层13的材料都采用氧化硅,所述第一栅介质层13的厚度为50nm~150nm。所述第二栅介质层14的厚度为10nm~50nm。在其他实施例中,也能为:所述第二栅介质层14的材料和所述第一栅介质层13的材料不相同,通过选择所述第二栅介质层14的材料的介电常数或调节所述第二栅介质层14的厚度来使所述第二阈值电压小于所述第一阈值电压,所述第二栅介质层14的材料的介电常数越低所述第二阈值电压越小以及所述第二栅介质层14的材料的厚度越低所述第二阈值电压越小。

81.本发明实施例中,所述第一栅极导电材料层11的材料为多晶硅即采用多晶硅栅。在其他实施例中也能为:所述第一栅极导电材料层11的材料为金属即采用金属栅。

82.所述第二栅极导电材料层12的材料和所述第一栅极导电材料层11的材料相同。

83.所述第一栅极导电材料层11的底部表面和所述栅极沟槽的底部表面之间以及所述第二栅极导电材料层12的底部表面和所述栅极沟槽的底部表面之间间隔有底部介质层。本发明实施例中,所述第一栅极导电材料层11的底部表面和所述栅极沟槽的底部表面之间的所述底部介质层由所述第一栅介质层13延伸而成,所述第二栅极导电材料层12的底部表面和所述栅极沟槽的底部表面之间的所述底部介质层由所述第二栅介质层14延伸而成。在其他实施例中也能为:所述底部介质层独立于所述第一栅介质层13和所述第二栅介质层14形成。

84.所述栅间介质层10的采用包括氧化硅。本发明实施例中,所述栅间介质层10采用层间膜形成,接触孔会穿过所述层间膜。所述层间膜会覆盖在所述第一栅极导电材料层11、所述第二栅极导电材料层12以及所述发射区8和基区引出区8的表面。

85.本发明实施例中,第一导电类型为n型,第二导电类型为p型,这时沟道导电类型为n型,igbt单元导通时,所述集电区2会向所述漂移区5中注入空穴。所述载流子存储层6的掺杂类型为n型,掺杂杂质能采用磷或砷,掺杂浓度为1e16cm

‑3~1e16cm

‑3,厚度为1μm~2μm。所述第一栅极导电材料层11和所述第二栅极导电材料层12的多晶硅采用n型掺杂,掺杂杂质包括磷或砷,掺杂浓度为1e19cm

‑3~1e20cm

‑3。

86.沟槽栅逆导型igbt器件通常由多个器件单元结构并联而成。

87.本发明实施例中,通过降低所述第二阈值电压,能使沟槽栅逆导型igbt器件作为反向续流二极管使用时,使反向恢复晶体管提前导通,此时,背面源区3发射电子,通过所述缓冲层4、所述漂移区5、载流子存储层6、所述第二栅极导电材料层12控制下在侧面覆盖的所述基区7表面形成的第二沟道进入到所述发射区9,进而进入到发射极,形成由发射极指向集电极极的反向电流。反向恢复晶体管为单极导电模式的器件,而非寄生体二极管导通的双极导电模式,故采用反向恢复晶体管进行反向电流输运后,能大幅度降低功率损耗,改善器件的反向恢复特性。

88.所述第一栅极导电材料层11和所述第二栅极导电材料层12之间的横向间距大小为0.2μm~1μm。所述第二栅极导电材料层12顶部的接触孔的长度为0.2μm~1μm。和图1所示的现有结构相比,igbt单元对应的所述第一栅极导电材料层11和所述漂移区5的耦合面积减少,由此减弱了器件电极间的耦合作用,使得沟槽栅逆导igbt器件的电容特性、栅电荷特性得到了极大改善。

89.在其他实施例中,将第一导电类型改变为p型以及将第二导电类型改变为n型,则器件变为p型器件,沟道导电类型为p型。

90.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1