微凸块及其形成方法、芯片互连结构及方法与流程

1.本技术涉及半导体技术领域,涉及但不限于一种微凸块及其形成方法、芯片互连结构及方法。

背景技术:

2.在半导体封装工艺中,通常利用倒装芯片接合工艺将芯片与基板或者芯片与芯片进行接合。相关技术中,通常采用铜柱凸块(copper pillar bump)来实现芯片与基板之间或者芯片与芯片之间的结合。铜柱凸块技术是在芯片的表面制作焊接凸块,使芯片具备较佳的导电、导热和抗电子迁移能力的一种技术。采用铜柱凸块进行封装,不仅可以缩短连接电路的长度,减小芯片封装面积和体积,实现微型化,而且还可以提高芯片封装模组的性能。

3.然而,随着芯片集成度的不断增加,相邻凸块之间的间距也越来越小,相关技术中的铜柱凸块技术,由于自身工艺的局限性,不能实现小间距和小尺寸的要求。

技术实现要素:

4.有鉴于此,本技术实施例提供一种微凸块及其形成方法、芯片互连结构及方法。

5.第一方面,本技术实施例提供一种微凸块的形成方法,包括:

6.提供芯片,所述芯片至少包括硅衬底和贯穿所述硅衬底的硅通孔;

7.在所述硅通孔中形成导电层,其中,所述导电层在第一方向上具有第一预设尺寸,所述第一方向为所述硅衬底的厚度方向;

8.在所述硅通孔中的所述导电层的表面形成连接层;其中,所述连接层在所述第一方向上具有第二预设尺寸;所述第一预设尺寸与所述第二预设尺寸之和等于所述硅通孔在所述第一方向上的初始尺寸;

9.处理所述硅衬底,暴露出所述连接层,形成与所述硅通孔对应的微凸块。

10.在一些实施例中,在形成所述导电层之前,所述方法还包括:

11.在所述硅通孔的内壁沉积绝缘材料,形成绝缘层;

12.在所述绝缘层的表面沉积阻挡材料,形成阻挡层;

13.在所述阻挡层的表面沉积种子材料,形成种子层。

14.在一些实施例中,所述在所述硅通孔中形成导电层,包括:

15.采用电化学沉积工艺,在所述硅通孔中的所述种子层的表面电镀导电材料,形成所述导电层;

16.其中,所述导电材料与所述种子材料相同。

17.在一些实施例中,所述在所述硅通孔中的所述导电层的表面形成连接层,包括:

18.在所述硅通孔中的所述导电层和所述种子层的表面沉积焊接材料,形成所述连接层;

19.其中,所述焊接材料包括镍金导电材料或者焊锡膏。

20.在一些实施例中,所述硅衬底的第一面形成有所述绝缘层、所述阻挡层和所述种子层;所述方法还包括:

21.在形成所述连接层之后,对所述硅衬底的第一面进行化学机械抛光处理,以去除所述硅衬底第一面的所述绝缘层、所述阻挡层和所述种子层。

22.在一些实施例中,所述处理所述硅衬底,暴露出所述连接层,形成与所述硅通孔对应的微凸块,包括:

23.以所述硅衬底的第一面为刻蚀起点,去除具有所述第二预设尺寸的硅衬底,保留位于所述连接层侧壁的所述绝缘层、所述阻挡层和所述种子层,暴露出具有所述第二预设尺寸的连接层,形成与所述硅通孔对应的微凸块。

24.在一些实施例中,所述处理所述硅衬底,暴露出所述连接层,形成与所述硅通孔对应的微凸块,包括:

25.以所述硅衬底的第一面为刻蚀起点,去除具有所述第二预设尺寸的硅衬底和位于所述连接层侧壁的所述绝缘层、所述阻挡层和所述种子层,暴露出具有所述第二预设尺寸的连接层,形成与所述硅通孔对应的微凸块。

26.在一些实施例中,所述提供芯片,包括:

27.提供所述硅衬底;

28.以所述硅衬底的第一面为刻蚀起点,刻蚀所述硅衬底,形成贯穿所述硅衬底的所述硅通孔;

29.其中,所述硅通孔在第二方向上的尺寸小于15微米,且相邻两个硅通孔之间的间距小于20微米;所述第二方向垂直于所述第一方向。

30.在一些实施例中,所述形成贯穿所述硅衬底的硅通孔,包括:

31.在所述硅衬底的第一面形成第一光阻层;

32.图形化所述第一光阻层,形成窗口,所述窗口暴露出所述硅衬底的第一面;

33.通过所述窗口,刻蚀所述硅衬底,形成贯穿所述硅衬底的硅通孔。

34.在一些实施例中,所述芯片还包括:

35.位于所述硅衬底的第二面的介质层;所述介质层中形成有与所述硅通孔连接的金属互连线;其中,所述硅衬底的第一面和所述硅衬底的第二面为所述硅衬底沿所述第一方向上相对的两个面;

36.所述硅通孔和所述金属互连线共同用于将所述硅衬底的第一面的信号传输至所述硅衬底的第二面。

37.在一些实施例中,位于所述介质层中的所述金属互连线通过以下方式形成:

38.在所述硅衬底的第二面沉积介质材料,形成所述介质层;

39.在所述介质层的表面形成图形化的第二光阻层;

40.通过所述第二光阻层,刻蚀所述介质层,形成位于所述介质层中的互连孔;

41.在所述互连孔中填充导电材料,形成位于所述介质层中的所述金属互连线。

42.在一些实施例中,所述芯片还包括位于所述硅衬底第二面的焊垫;

43.所述焊垫的第一端连接所述芯片的内部电路,所述焊垫的第二端连接所述介质层中的金属互连线;所述金属互连线还用于引出所述硅衬底的第二面的信号。

44.第二方面,本技术实施例提供一种微凸块,所述微凸块通过上述微凸块的形成方

法形成;

45.所述微凸块位于芯片的硅通孔结构中,且所述微凸块至少用于实现两个芯片之间的互连。

46.在一些实施例中,所述芯片包括贯穿所述芯片硅衬底的硅通孔;

47.所述硅通孔与所述微凸块对应,且所述微凸块在垂直于第一方向上的尺寸小于所述硅通孔在垂直于所述的第一方向上的尺寸;

48.其中,所述第一方向为所述硅衬底的厚度方向。

49.在一些实施例中,所述微凸块在第二方向上的尺寸小于15微米,且相邻两个微凸块之间的间距小于20微米,其中,所述第二方向垂直于所述第一方向。

50.第三方面,本技术实施例提供一种芯片互连方法,包括:

51.提供至少两个芯片;所述芯片包括沿所述芯片第一面进行开口的硅通孔和位于所述芯片第二面的介质层;所述介质层中形成有与所述硅通孔连接的金属互连线;所述第一面和所述第二面为所述芯片沿所述芯片厚度方向上的相对的两个面;

52.在所述芯片的所述硅通孔的对应位置,通过上述微凸块的形成方法形成位于所述芯片第一面的微凸块;

53.在所述芯片中的所述金属互连线的暴露面进行植球,形成位于所述芯片第二面的键合凸块;

54.将所述至少两个芯片中第一芯片第一面的所述微凸块与所述至少两个芯片中第二芯片第二面的所述焊接凸块进行对准和键合,以实现通过所述微凸块实现所述至少两个芯片之间的互连。

55.第四方面,本技术实施例提供一种芯片互连结构,包括:

56.至少两个芯片;所述芯片包括沿所述芯片第一面进行开口的硅通孔和位于所述芯片第二面的介质层;所述介质层中形成有与所述硅通孔连接的金属互连线;所述第一面和所述第二面为所述芯片沿所述芯片厚度方向上的相对的两个面;

57.位于所述芯片第一面的微凸块,其中,所述微凸块与所述硅通孔连接;所述微凸块通过上述微凸块的形成方法形成;

58.位于所述芯片第二面的键合凸块;其中,所述键合凸块与所述金属互连线连接;

59.所述至少两个芯片中第一芯片第一面的所述微凸块与所述至少两个芯片中的第二芯片第二面的所述焊接凸块电连接。

60.本技术实施例提供的微凸块及其形成方法、芯片互连结构及方法,其中,微凸块的形成方法包括:提供芯片,芯片至少包括硅衬底和贯穿硅衬底的硅通孔;在硅通孔中形成导电层,在硅通孔中的导电层的表面形成连接层;处理硅衬底,暴露出连接层,形成与硅通孔对应的微凸块。本技术实施例中由于形成微凸块的连接层形成于硅通孔中,通过去除硅衬底,暴露出连接层,即可形成与硅通孔对应的微凸块,如此,可以实现制备具有小尺寸和小间距的微凸块。

附图说明

61.在附图(其不一定是按比例绘制的)中,相似的附图标记可在不同的视图中描述相似的部件。具有不同字母后缀的相似附图标记可表示相似部件的不同示例。附图以示例而

非限制的方式大体示出了本文中所讨论的各个实施例。

62.图1为相关技术中采用tsv技术进行封装的芯片的剖面结构示意图;

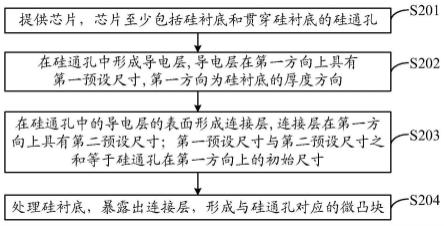

63.图2为本技术实施例提供的微凸块形成方法的一种可选的流程示意图;

64.图3a~3k为本技术实施例提供的形成微凸块的流程图;

65.图4为本技术实施例提供的芯片和微凸块的一种可选的结构示意图;

66.图5为本技术实施例提供的芯片互连方法的一种可选的流程示意图;

67.图6为本技术实施例提供的芯片互连结构的一种可选的结构示意图;

68.附图标记说明如下:

69.101/301/401/6013—介质层;102/3011/4011—金属互连线;103—铜柱凸块;1031—铜柱;1032—锡块;104/305/4001/6011/6012—硅通孔;300/400—硅衬底;301—介质层;302—焊垫;303—内部电路;304—第一光阻层;3041—窗口;306—绝缘层;307—阻挡层;308—种子层;309—导电层;310—连接层;50/71—微凸块;601/602—芯片;72—键合凸块。

具体实施方式

70.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对发明的具体技术方案做进一步详细描述。以下实施例用于说明本技术,但不用来限制本技术的范围。

71.在后续的描述中,使用用于表示元件的诸如“模块”或“单元”的后缀仅为了有利于本技术的说明,其本身没有特定的意义。因此,“模块”或“单元”可以混合地使用。

72.在说明本技术实施例的微凸块(micro bump)之前,首先,对相关技术中的铜柱凸块进行介绍。

73.相关技术中,通常采用铜柱凸块来实现芯片与基板之间或者芯片与芯片之间的结合。图1为相关技术中采用tsv技术进行封装的芯片的剖面结构示意图,如图1所示,芯片的第一面(如图1中示出的a面)形成有位于介质层101中的金属互连线102,金属互连线102用于引出芯片第一面的信号;芯片的第二面(如图1中示出的b面)形成有铜柱凸块103,铜柱凸块103由铜柱1031和用于焊接的锡块1032两部分形成,且铜柱凸块103的位置与芯片中的硅通孔104的位置对应。从图1中可以看出,相关技术中的铜柱凸块的尺寸d1大于硅通孔的尺寸d2。

74.随着芯片集成度不断增加,相邻凸块之间的间距也越来越小,而相关技术中形成的铜柱凸块的尺寸较大,无法实现凸块间距小于20微米,因此,不能满足当前芯片堆叠技术中对于小间距和小尺寸的微凸块的要求。

75.基于相关技术中存在的上述问题,本技术实施例提供一种微凸块的形成方法。通常芯片通过硅通孔(through silicon via,tsv)技术将信号从芯片的正面传输到芯片的背面,而芯片与芯片之间的直接堆叠需要通过微凸块互连。图2为本技术实施例提供的微凸块形成方法的一种可选的流程示意图,如图2所示,所述方法包括以下步骤:

76.步骤s201、提供芯片,所述芯片至少包括硅衬底和贯穿所述硅衬底的硅通孔。

77.芯片的内部形成有各种有源器件和电路,用于实现各种功能各样的功能。本技术实施例中,芯片至少包括硅衬底。

78.硅通孔是形成在芯片内部,且贯穿芯片硅衬底的通孔,硅通孔内部填充导电材料,用于实现将芯片正面的信号传输至芯片的背面。

79.所述硅衬底可以包括处于正面的顶表面以及处于与正面相对的背面的底表面;在忽略硅衬底顶表面和底表面的平整度的情况下,定义垂直硅衬底顶表面和底表面的方向,即硅衬底的厚度方向为第一方向。在硅衬底顶表面和底表面内(即硅衬底所在的平面),定义任意一个方向为第二方向。这里,所述第一方向垂直于所述第二方向。本技术实施例中,定义所述第一方向为x轴方向,定义所述第二方向为y轴方向。

80.步骤s202、在所述硅通孔中形成导电层。

81.其中,所述导电层在第一方向上具有第一预设尺寸,所述第一方向为所述硅衬底的厚度方向。

82.在一些实施例中,导电层的导电材料可以是金属铜或者金属钨。

83.在其它实施例中,在所述硅通孔中形成所述导电层之前,可以先在所述硅通孔中形成绝缘层、阻挡层和种子层。其中,绝缘层的材料可以是sio2;阻挡层的材料可以是金属钽或者氮化钽;所述种子层材料可以是金属钨、钴、铜、铝或其任何组合。

84.步骤s203、在所述硅通孔中的所述导电层的表面形成连接层。

85.其中,所述连接层在所述第一方向上具有第二预设尺寸;所述第一预设尺寸与所述第二预设尺寸之和等于所述硅通孔在所述第一方向上的初始尺寸。

86.本技术实施例中,所述连接层用于形成后续的微凸块。

87.步骤s204、处理所述硅衬底,暴露出所述连接层,形成与所述硅通孔对应的微凸块。

88.本技术实施例中,处理硅衬底是指刻蚀硅衬底或者对硅衬底进行减薄处理,以暴露出连接层。这里,刻蚀硅衬底可以是采用干法刻蚀工艺刻蚀硅衬底,所述干法刻蚀工艺可以是等离子体刻蚀工艺,反应离子刻蚀工艺或者离子铣工艺。

89.需要说明的是,本技术实施例中,处理硅衬底,暴露出所述连接层包含两种含义:一是处理硅衬底,完全暴露出所述连接层;二是处理硅衬底,暴露出部分所述连接层。

90.本技术实施例中,形成与硅通孔对应的微凸块,一方面是指形成的微凸块的位置与硅通孔对应,即每个硅通孔的位置都会对应形成一个微凸块;另一方面由于本技术实施例中的微凸块形成于硅通孔内部,因此,形成的微凸块的尺寸小于或者等于硅通孔的尺寸。

91.本技术实施例提供的微凸块的形成方法,由于形成微凸块的连接层形成于硅通孔中,通过去除硅衬底,暴露出连接层,即可形成与硅通孔对应的微凸块,如此,可以实现制备具有小尺寸和小间距的微凸块。

92.图3a~3k为本技术实施例提供的形成微凸块的流程示意图,接下来请参考图3a~3k对本技术实施例提供的微凸块的形成方法进一步地详细说明。

93.首先,可以参考图3a~3d,执行步骤s201、提供芯片,所述芯片至少包括硅衬底和贯穿所述硅衬底的硅通孔。

94.本技术实施例中,所述芯片包括硅衬底和沿所述硅衬底的第一面进行开口的硅通孔,所述芯片还包括位于所述硅衬底第二面的介质层,所述介质层中形成有与所述硅通孔连接的金属互连线。所述硅通孔和所述金属互连线共同用于将所述硅衬底的第一面(即芯片的第一面)的信号传输至所述硅衬底的第二面(即芯片的第二面),或者,将所述硅衬底第

二面(即芯片的第二面)的信号传输至硅衬底的第一面(即芯片的第一面)。所述硅衬底的第一面和所述硅衬底的第二面为所述硅衬底沿第一方向上相对的两个面。所述第一方向为硅衬底的厚度方向。

95.在一些实施例中,所述芯片还包括位于所述硅衬底第二面的焊垫;所述焊垫的第一端连接所述芯片的内部电路,所述焊垫的第二端连接所述介质层中的金属互连线;所述金属互连线还用于引出所述硅衬底的第二面(即芯片的第二面)的信号。

96.在一些实施例中,位于所述介质层中的所述金属互连线通过以下方式形成:

97.在所述硅衬底的第二面沉积介质材料,形成所述介质层。

98.这里,所述介质材料可以是sio2或者其它绝缘材料。在硅衬底的第二面沉积介质材料的工艺可以包括化学气相沉积(chemical vapor deposition,cvd)、物理气相沉积(physical vapor deposition,pvd)或者原子层沉积(atomic layer deposition,ald)。

99.在所述介质层的表面形成图形化的第二光阻层。

100.通过所述第二光阻层,刻蚀所述介质层,形成位于所述介质层中的互连孔。

101.在所述互连孔中填充导电材料,形成位于所述介质层中的所述金属互连线。

102.在一些实施例中,所述导电材料包括钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。

103.在一些实施例中,在芯片的形成过程,首先形成介质层和金属互连线,然后形成硅通孔。图3a为本技术实施例提供的形成介质层和金属互连线的剖面结构示意图,如图3a所示,在硅衬底300的第二面(如图3a中示出的c面)形成有介质层301,介质层301中形成有金属互连线3011。芯片还包括位于所述硅衬底第二面的焊垫302,焊垫302的第一端与芯片中的内部电路303连接,焊垫302的第二端与介质层301中的金属互连线3011连接。

104.在一些实施例中,所述提供芯片,可以通过以下步骤实现:

105.步骤s2011、提供所述硅衬底。

106.步骤s2012、以所述硅衬底的第一面为刻蚀起点,刻蚀所述硅衬底,形成贯穿所述硅衬底的所述硅通孔。

107.在一些实施例中,所述形成贯穿所述硅衬底的硅通孔,可以通过以下步骤形成:

108.在所述硅衬底的表面形成第一光阻层。

109.这里,可以通过任意一种合适的沉积工艺在硅衬底的第一面形成第一光阻层。

110.图形化所述第一光阻层,形成窗口,所述窗口暴露出所述硅衬底的第一面。

111.在一些实施例中,可以通过曝光、显影等步骤来图形化第一光阻层,形成所述窗口。

112.如图3b所示,在硅衬底300的第一面(如图3b中的d面)形成第一光阻层304,图形化第一光阻层304形成窗口3041,所述窗口3041暴露出硅衬底的第一面。值得注意的是,图3b中仅仅示例性地示出了在第一光阻层中形成一个窗口,在实际工艺中,第一光阻层中可以形成至少两个窗口。

113.本技术实施例中,形成的硅通孔在y轴方向上的尺寸小于15微米,且相邻两个硅通孔之间的间距小于20微米。

114.通过所述窗口,刻蚀所述硅衬底,形成贯穿所述硅衬底的硅通孔。

115.如图3c所示,通过所述窗口3041刻蚀硅衬底300,形成了贯穿硅衬底300的硅通孔

305。需要说明的是,图3c中仅仅示例性地示出了一个硅通孔,在实际工艺中,所述芯片中形成有至少两个硅通孔。

116.在一些实施例中,在通过所述第一光阻层中的窗口形成所述硅通孔后,所述微凸块的形成方法还包括:去除所述第一光阻层。

117.本技术实施例中,可以通过湿法刻蚀工艺或者干法刻蚀工艺去除所述第一光阻层。如图3d所示,去除了第一光阻层,暴露出了所述硅衬底300的d面。

118.接下来,可以参考图3e~3g,执行步骤s202、在所述硅通孔中形成导电层。

119.在一些实施例中,在所述硅通孔中形成导电层之前,所述微凸块的形成方法还包括以下步骤:

120.在所述硅通孔的内壁沉积绝缘材料,形成绝缘层。

121.本技术实施例中,所述绝缘材料可以是氧化硅或者氮氧化硅,所述绝缘层用于保护硅衬底不被破坏。这里,可以通过任意一种合适的沉积工艺形成所述绝缘层。

122.在一些实施例中,也可以在高温、高压条件下,通过原位氧化的方式,氧化所述硅衬底,形成位于所述硅通孔内壁的绝缘层。

123.如图3e所示,在硅通孔305的内壁和硅衬底300的第一面(d面)均形成了所述绝缘层306。

124.在所述绝缘层的表面沉积阻挡材料,形成阻挡层。

125.本技术实施例中,所述阻挡材料可以是金属钽或者氮化钽,所述阻挡层用于防止后续填充在硅通孔中的导电材料的扩散。这里,可以通过任意一种合适的沉积工艺形成所述阻挡层。

126.在所述阻挡层的表面沉积种子材料,形成种子层。

127.本技术实施例中,所述种子层材料可以是任意一种导电材料,例如,钨、钴、铜、铝或其任何组合。所述种子层用于为后续在硅通孔中形成导电层,提供衔接作用。

128.如图3f所示,在绝缘层306的表面形成了阻挡层307,并且在阻挡层307的表面形成了种子层308。

129.在一些实施例中,所述在所述硅通孔中形成导电层,可以包括以下步骤:

130.步骤s2021、采用电化学沉积工艺,在所述硅通孔中的所述种子层的表面电镀导电材料,形成所述导电层。

131.在一些实施例中,所述导电材料包括:钨、钴、铜、铝、多晶硅、掺杂硅、硅化物或其任何组合,所述导电材料与所述种子材料可以相同,也可以不同。本技术实施例中,形成所述导电层的导电材料和种子材料均为金属铜。

132.如图3g所示,采用电化学沉积工艺,在硅通孔中电镀导电材料,形成导电层309。所述导电层309在x轴方向上具有第一预设尺寸d3,第一预设尺寸d3小于硅通孔在x轴方向上的初始尺寸d4,即本技术实施例中,导电层309未填充满硅通孔。

133.接下来,可以参考图3h和3i,执行步骤s203、在所述硅通孔中的所述导电层的表面形成连接层。

134.在一些实施例中,所述在所述硅通孔中的所述导电层的表面形成连接层,包括以下步骤:

135.步骤s2031、在所述硅通孔中的所述导电层和所述种子层的表面沉积焊接材料,形

成所述连接层。

136.本技术实施例中,所述焊接材料包括镍金(ni/au)导电材料或者焊锡膏(solder)。这里,可以通过任意一种合适的沉积工艺形成所述连接层。

137.如图3h所示,在硅通孔中的导电层309和种子层308的表面沉积焊接材料,形成连接层310。所述连接层310在x轴方向上具有第二预设尺寸d5,第二预设尺寸d5与第一预设尺寸d3之和等于硅通孔在x轴方向上的初始尺寸d4。

138.在一些实施例中,在硅通孔中形成绝缘层,阻挡层和种子层时,在所述硅衬底的第一面同时也形成有所述绝缘层、所述阻挡层和所述种子层,所述微凸块的形成方法还包括:

139.在形成所述连接层之后,对所述硅衬底的第一面进行化学机械抛光处理,以去除所述硅衬底第一面的所述绝缘层、所述阻挡层和所述种子层。

140.如图3i所示,对硅衬底300第一面(d面)进行化学机械抛光处理,去处理硅衬底300第一面的绝缘层、阻挡层和种子层,暴露出硅衬底300的第一面。

141.接下来,可以参考图3j和3k,执行步骤s204、处理所述硅衬底,暴露出所述连接层,形成与所述硅通孔对应的微凸块。

142.在一些实施例中,所述处理所述硅衬底,暴露出所述连接层,形成与所述硅通孔对应的微凸块,可以包括以下步骤:

143.步骤s2041、以所述硅衬底的第一面为刻蚀起点,去除具有所述第二预设尺寸的硅衬底,保留位于所述连接层侧壁的所述绝缘层、所述阻挡层和所述种子层,暴露出具有所述第二预设尺寸的连接层,形成与所述硅通孔对应的微凸块。

144.如图3j所示,以硅衬底300的d面为刻蚀起点,采用干法刻蚀工艺刻蚀去除具有第二预设尺寸d5的硅衬底,并保留位于连接层310侧壁的绝缘层306、阻挡层307和种子层,暴露出具有第二预设尺寸d5的连接层310,形成与所述硅通孔对应的微凸块。

145.本技术实施例中,所形成的微凸块不仅包括连接层,还包括位于连接层侧壁的阻挡层和绝缘层。所形成的微凸块在y轴方向上尺寸与硅通孔在y轴方向的尺寸相等。绝缘层和阻挡层可以在一定程度上防止连接层的焊接材料外溢,避免连接层之间的桥接。

146.在一些实施例中,所述处理所述硅衬底,暴露出所述连接层,形成与所述硅通孔对应的微凸块,可以包括以下步骤:

147.步骤s2042、以所述硅衬底的第一面为刻蚀起点,去除具有所述第二预设尺寸的硅衬底和位于所述连接层侧壁的所述绝缘层、所述阻挡层和所述种子层,暴露出具有所述第二预设尺寸的连接层,形成与所述硅通孔对应的微凸块。

148.如图3k所示,以硅衬底300的d面为刻蚀起点,采用干法刻蚀工艺刻蚀去除具有第二预设尺寸d5的硅衬底,并刻蚀去除位于连接层310侧壁的绝缘层、阻挡层和种子层,暴露出具有第二预设尺寸d5的连接层310,形成与所述硅通孔对应的微凸块。

149.本技术实施例中,所形成的微凸块仅包括连接层,而不包括位于连接层侧壁的阻挡层和绝缘层。所形成的微凸块在y轴方向上尺寸与导电层在y轴方向的尺寸相等,且微凸块在y轴方向上的尺寸小于硅通孔在y轴方向上的尺寸。本技术实施例中,通过去除连接层侧壁的绝缘层和阻挡层,可以制备得到具有小尺寸和小间距的微凸块。

150.在一些实施例中,可以同时刻蚀去除具有第二预设尺寸的硅衬底和位于连接层侧壁的绝缘层、阻挡层和种子层,也可以依次去除具有第二预设尺寸的硅衬底和位于连接层

侧壁的绝缘层、阻挡层和种子层。

151.本技术实施例提供了一种制备微凸块的新方法,可以实现制备得到具有小尺寸和小间距的micro bump,应对未来合适间距凸块的三维(three dimension,3d)互连的需求。通过本技术实施例所形成的微凸块,凸块尺寸可以控制在15微米以下,例如,凸块尺寸可以是7微米;凸块间距可以控制在20微米以下,例如,凸块间距可以是10微米。

152.本技术实施例,在硅通孔的后端封装工艺(tsv via last)实现过程中先填充部分通过,余下部分填充ni/au micro bump或solder,刻蚀多余硅,裸露micro bump。通过本技术实施例提供的微凸块的形成方法,所形成的微凸块间距(bump pitch)与凸块尺寸(bump size)均可以做到不同程度的缩小。

153.本技术实施例提供一种微凸块,所述微凸块通过上述实施例提供的微凸块的形成方法形成,所述微凸块位于芯片的硅通孔结构中,且所述微凸块至少用于实现两个芯片之间的互连。

154.在其它实施例中,所述微凸块还用于实现芯片与基板之间的互连。

155.图4为本技术实施例提供的芯片和微凸块的一种可选的结构示意图,如图4所示,所述芯片包括硅衬底400和位于硅衬底400表面的介质层401,所述硅衬底中形成有硅通孔4001,所述硅通孔4011与微凸块50对应,所述微凸块50在y轴方向的尺寸d6小于硅通孔4001在y轴方向的尺寸d7。

156.值得注意的是,图4中仅仅示出了一个硅通孔和一个微凸块,在实际制作过程中,芯片至少包括两个硅通孔,且对应于每一硅通孔都会形成一个微凸块。

157.本技术实施例中,所述微凸块在y轴方向的尺寸小于15微米,且相邻两个微凸块之间的间距小于20微米。

158.在一些实施例中,所述介质层401中还形成有与硅通孔4001相连的金属互连线4011,所述硅通孔4001和所述金属互连线4011共同用于将所述硅衬底400的第一面(即芯片的第一面)的信号传输至所述硅衬底400的第二面(即芯片的第二面),或者,将硅衬底是第二面(即芯片的第二面)的信号传输至硅衬底的第一面(即芯片的第一面)。所述硅衬底的第一面和所述硅衬底的第二面为所述硅衬底沿x轴方向上相对的两个面。

159.本技术实施例提供的微凸块,具有小间距和小尺寸,可以应对未来fine pitch bump的3d互连需求。

160.本技术实施例提供的微凸块与上述实施例中的微凸块的形成方法类似,对于本技术实施例未详尽披露的技术特征,请参考上述实施例进行理解,这里,不再赘述。

161.本技术实施例提供一种芯片互连方法,图5为本技术实施例提供的芯片互连方法的一种可选的流程示意图,如图5所示,所述方法包括以下步骤:

162.步骤s501、提供至少两个芯片;所述芯片包括沿所述芯片第一面进行开口的硅通孔和位于所述芯片第二面的介质层;所述介质层中形成有与所述硅通孔连接的金属互连线;所述第一面和所述第二面为所述芯片沿所述芯片厚度方向上的相对的两个面。

163.本技术实施例中,所述芯片为待封装的芯片。芯片包括硅衬底和介质层,所述硅通孔形成于所述硅衬底中,并贯穿所述硅衬底。所述介质层中形成有金属互连线,所述金属互连线与所述硅通孔连接,所述硅通孔和所述金属互连线共同用于将所述芯片第一面的信号传输至所述芯片的第二面。

164.步骤s502、在所述芯片的所述硅通孔的对应位置,形成位于所述芯片第一面的微凸块。

165.所述微凸块通过上述实施例提供的微凸块的形成方法形成,对于本技术实施例未详尽披露的技术特征,请参照上述实施例进行理解。

166.本技术实施例中,所述芯片包括至少两个硅通孔,每一硅通孔的对应位置均会形成一个微凸块。

167.步骤s503、在所述芯片中的所述金属互连线的暴露面进行植球,形成位于所述芯片第二面的键合凸块。

168.在一些实施例中,所述金属互连线还用于引出芯片第二面的信号。所述键合凸块也用于实现芯片与芯片或者芯片与基板之间的堆叠。这里,所述键合凸块的尺寸大于微凸块的尺寸。

169.步骤s504、将所述至少两个芯片中第一芯片第一面的所述微凸块与所述至少两个芯片中第二芯片第二面的所述焊接凸块进行对准和键合,以实现通过所述微凸块实现所述至少两个芯片之间的互连。

170.本技术实施例中,芯片与芯片之间的互连是背对面焊接的方式,即至少两个芯片中的第一芯片的第一面与至少两个芯片中第二芯片的第二面相接触。通过微凸块和焊接凸块之间的对准和键合,实现芯片与芯片之间的互连。

171.本技术实施例提供的芯片互连方法,由于在芯片第一面形成的微凸块可以实现小尺寸和小间距,如此,能够满足未来3d互连的需求。

172.本技术实施例还提供一种芯片互连结构,所述芯片互连结构包括至少两个芯片、位于每一芯片第一面的微凸块和位于每一芯片第二面的键合凸块。图6为本技术实施提供的芯片互连结构一种可选的结构示意图,如图6所示,本技术实施例中,所述芯片互连结构60包括两个堆叠的601、602、位于每一芯片第一面的微凸块71和位于每一芯片第二面的键合凸块72。

173.本技术实施例中,所述芯片互连结构中的每一个芯片的结构都是相同的,下面,以芯片601为例对芯片的内部结构进行介绍。

174.请继续参见图6,芯片601包括沿芯片第一面(如图6中示出的e面)进行开口的硅通孔6011、6012和位于芯片第二面(如图6中示出的f面)的介质层6013;所述介质层6013中形成有与每一硅通孔6011、6012连接的金属互连线6014。其中,第一面(e面)和第二面(f面)为芯片601沿x轴方向上的相对的两个面。

175.本技术实施例中,每一芯片的所述微凸块与硅通孔连接,所述微凸块通过上述实施例提供的微凸块的形成方法形成。且每一芯片的键合凸块与所述金属互连线连接。所述至少两个芯片中第一芯片第一面的所述微凸块与所述至少两个芯片中的第二芯片第二面的所述焊接凸块电连接。

176.需要说明的是,本技术实施例图6中只是示例性示出了两个硅通孔和两个微凸块,在实际工艺中,芯片中存在多个硅通孔,每一硅通孔的位置都会形成一个微凸块。

177.本技术实施例提供的芯片互连结构与上述实施例中的芯片互连方法类似,对于本技术实施例未详尽披露的技术特征,请参照上述实施例进行理解,这里不再赘述。

178.本技术实施例提供的芯片互连结构,由于在芯片第一面形成的微凸块可以实现小

尺寸和小间距,如此,能够满足未来3d互连的需求。

179.在本技术所提供的几个实施例中,应该理解到,所揭露的设备和方法,可以通过非目标的方式实现。以上所描述的设备实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,如:多个单元或组件可以结合,或可以集成到另一个系统,或一些特征可以忽略,或不执行。另外,所显示或讨论的各组成部分相互之间的耦合、或直接耦合。

180.上述作为分离部件说明的单元可以是、或也可以不是物理上分开的,作为单元显示的部件可以是、或也可以不是物理单元,即可以位于一个地方,也可以分布到多个网络单元上;可以根据实际的需要选择其中的部分或全部单元来实现本实施例方案的目的。

181.本技术所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

182.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1