一种感光晶体管、阵列基板及显示面板的制作方法

1.本发明涉及显示技术,尤其涉及一种感光晶体管、阵列基板及显示面板。

背景技术:

2.由于指纹对于每一个人而言是与生俱来的,是独一无二的。随着科技的发展,市场上出现了多种带有指纹识别功能的显示装置,如手机、平板电脑以及智能可穿戴设备等。这样,用户在操作带有指纹识别功能的显示装置前,只需要用手指触摸显示装置,通过指纹传感器识别指纹信息,就可以进行权限验证,简化了权限验证过程。

3.指纹识别电路为显示面板中用于实现指纹识别的电路,指纹识别电路中的感光晶体管的阈值电压在不同光照强度下容易发生波动,从而影响指纹识别电路的稳定性。

技术实现要素:

4.本发明实施例提供一种感光晶体管、阵列基板及显示面板,以提升感光晶体管的感光效应,以及减小感光晶体管的阈值电压偏移,提高指纹识别电路的稳定性。

5.第一方面,本发明实施例提供一种感光晶体管,包括第一有源层、第一极、第二极、第一子栅极和第二子栅极,所述第一极与所述第一有源层的第一端电连接,所述第二极与所述第一有源层的第二端电连接;

6.垂直于所述第一有源层所在平面的方向,所述第一子栅极与所述第一有源层交叠,位于所述第一有源层远离所述第一极以及所述第二极一侧,所述第二子栅极与所述第一有源层交叠,与所述第一子栅极不交叠,位于所述第一有源层与所述第一极以及所述第二极之间。

7.可选地,还包括辅助极,所述辅助极与所述第一子栅极电连接;

8.所述第二极与所述第二子栅极电连接。

9.第二方面,本发明实施例提供一种阵列基板,包括:

10.衬底;

11.子像素,位于所述衬底的一侧;

12.指纹识别电路,位于所述衬底的一侧,包括第一方面所述的感光晶体管。

13.可选地,还包括像素驱动电路,所述像素驱动电路包括薄膜晶体管;

14.所述薄膜晶体管包括第二有源层、第二栅极、第三极和第四极,所述第三极与所述第二有源层的第一端电连接,所述第四极与所述第二有源层的第二端电连接,所述第二有源层位于所述第三极以及所述第四极与所述衬底之间;垂直于所述衬底所在平面的方向,所述第二栅极与所述第二有源层交叠;

15.所述第二栅极与第一子栅极或者第二子栅极同层。

16.可选地,所述第二栅极与所述第一子栅极同层;

17.所述第二栅极位于所述第二有源层与所述衬底之间,或者,所述第二栅极位于所述第三极以及所述第四极与所述第二有源层之间。

18.可选地,所述第三极、所述第四极与所述第二子栅极同层。

19.可选地,所述第二栅极位于所述第二有源层与所述衬底之间,所述第一有源层与所述第二有源层同层。

20.可选地,所述第二栅极与所述第二子栅极同层;

21.所述第二栅极位于所述第三极以及所述第四极与所述第二有源层之间。

22.可选地,所述第一极、所述第二极、所述第三极与所述第四极同层。

23.可选地,所述第一有源层与所述第二有源层同层。

24.可选地,所述第一有源层与所述第二有源层采用同种材料。

25.第三方面,本发明实施例还提供一种显示面板,包括第二方面所述的阵列基板。

26.本发明实施例提供一种感光晶体管,包括第一子栅极和第二子栅极,第一子栅极与第二子栅极分别位于第一有源层的相对两侧,且第一子栅极与第二子栅极分别与第一有源层的不同区域交叠,相当于形成了底栅结构与顶栅结构结合的晶体管。光线投射至感光晶体管时,由于第一子栅极位于第一有源层的背面,不会对光线造成遮挡,光线投射至第一子栅极上方对应的第一有源层上,增加了感光晶体管的漏电流,提升了感光晶体管的感光效应。光线投射至感光晶体管时,由于第二子栅极位于第一有源层的正面,第二子栅极防止光线投射至其下方对应的第一有源层上,第二子栅极所形成的顶栅结构的临界电压的偏移,能够减小感光晶体管的阈值电压偏移,抑制感光晶体管的阈值电压在不同光照强度的波动,提高指纹识别电路的稳定性。

附图说明

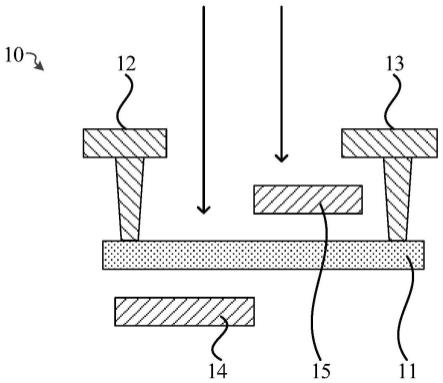

27.图1为本发明实施例提供的一种感光晶体管的结构示意图;

28.图2为本发明实施例提供的另一种感光晶体管的结构示意图;

29.图3为本发明实施例提供的一种阵列基板的俯视结构示意图;

30.图4为沿图3中aa’的剖视结构示意图;

31.图5为本发明实施例提供的另一种阵列基板的俯视结构示意图;

32.图6为本发明实施例提供的另一种阵列基板的俯视结构示意图;

33.图7为本发明实施例提供的另一种阵列基板的俯视结构示意图;

34.图8为本发明实施例提供的另一种阵列基板的俯视结构示意图;

35.图9为本发明实施例提供的另一种阵列基板的俯视结构示意图;

36.图10为本发明实施例提供的一种指纹识别电路的电路结构示意图;

37.图11为本发明实施例提供的一种显示面板的剖视结构示意图。

具体实施方式

38.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

39.图1为本发明实施例提供的一种感光晶体管的结构示意图,参考图1,感光晶体管10包括第一有源层11、第一极12、第二极13、第一子栅极14和第二子栅极15,第一极12与第一有源层11的第一端电连接,第二极13与第一有源层11的第二端电连接。其中,第一有源层

11可以包括单晶硅、多晶硅或者金属氧化物中的至少一种。金属氧化物例如可以为铟镓锌氧化物(即igzo)。垂直于第一有源层11所在平面的方向,第一子栅极14与第一有源层11交叠,第一子栅极14位于第一有源层11远离第一极12以及第二极13一侧,第二子栅极15与第一有源层11交叠,第二子栅极15与第一子栅极14不交叠,第二子栅极15位于第一有源层11与第一极12以及第二极13之间。第一子栅极14与第二子栅极15分别位于第一有源层11的相对两侧。

40.本发明实施例提供一种感光晶体管10,包括第一子栅极14和第二子栅极15,第一子栅极14与第二子栅极15分别位于第一有源层11的相对两侧,且第一子栅极14与第二子栅极15分别与第一有源层11的不同区域交叠,相当于形成了底栅结构与顶栅结构结合的晶体管。光线(如图1中箭头所示)投射至感光晶体管10时,由于第一子栅极14位于第一有源层11的背面,不会对光线造成遮挡,光线投射至第一子栅极14上方对应的第一有源层11上,增加了感光晶体管10的漏电流,提升了感光晶体管10的感光效应。光线投射至感光晶体管10时,由于第二子栅极15位于第一有源层11的正面,第二子栅极15防止光线投射至其下方对应的第一有源层11上,第二子栅极15所形成的顶栅结构的临界电压的偏移,能够减小感光晶体管10的阈值电压偏移,抑制感光晶体管10的阈值电压在不同光照强度的波动,提高指纹识别电路的稳定性。

41.示例性地,第一极12和第二极13位于同一膜层中,第一极12和第二极13采用同种材料并在同一构图工艺中形成。第一极12可以为源极,第二极13可以为漏极;或者,第一极12可以为漏极,第二极13可以为源极。

42.可以理解的是,第一子栅极14与第二子栅极15共同控制第一有源层11的沟道导电性,即,第一子栅极14与第二子栅极15共同控制第一极12和第二极13的通断状态,因此可以为第一子栅极14与第二子栅极15提供相同的电信号。进一步地,在一些指纹识别电路中,需要为感光晶体管10的第二极13、第一子栅极14与第二子栅极15提供相同的电信号。需要说明的是,在另一些指纹识别电路中,也可以为感光晶体管10的第二极13与第一子栅极14提供不同的电信号。

43.图2为本发明实施例提供的另一种感光晶体管的结构示意图,感光晶体管10还包括辅助极16,辅助极16与第一子栅极14电连接,第二极13与第二子栅极15电连接。本发明实施例中,通过设置辅助极16与第一子栅极14电连接,第二极13与第二子栅极15电连接,从而便于为感光晶体管10的第二极13、第一子栅极14与第二子栅极15提供相同的电信号。进一步地,本发明实施例中,设置辅助极16的作用在于,将第一子栅极14引出至与第二极13所在膜层,便于为第二极13和辅助极16施加相同的电信号,或者,便于将第二极13和辅助极16电连接。

44.图3为本发明实施例提供的一种阵列基板的俯视结构示意图,图4为沿图3中aa’的剖视结构示意图,参考图3和图4,阵列基板包括衬底51、子像素21和指纹识别电路22。子像素21位于衬底51的一侧。子像素21为形成显示面板后的发光显示单元。指纹识别电路22位于衬底51的一侧,指纹识别电路22包括上述实施例中的的感光晶体管10。本发明实施例中,由于阵列基板包括上述实施例中的的感光晶体管10,因此具有上述感光晶体管10的有益效果,即,提升感光晶体管10的感光效应,以及减小感光晶体管10的阈值电压偏移,提高指纹识别电路的稳定性。需要说明的是,图4中包括如图2所示感光晶体管10,但并不以此为限,

图4中还可以包括如图1所示感光晶体管10。

45.可选地,参考图3和图4,阵列基板还包括像素驱动电路,像素驱动电路位于衬底51的一侧,用于驱动子像素21发光显示。像素驱动电路包括薄膜晶体管30。薄膜晶体管30包括第二有源层34、第二栅极31、第三极32和第四极33,第三极32与第二有源层34的第一端电连接,第四极33与第二有源层34的第二端电连接,第二有源层34位于第三极32以及第四极33与衬底51之间。垂直于衬底51所在平面的方向,第二栅极31与第二有源层34交叠。第二栅极31与第一子栅极14同层。本发明实施例中,第二栅极31与第一子栅极14同层,从而无需为第一子栅极14增设新的膜层,减小了阵列基板的厚度。第二栅极31与第一子栅极14同层,第二栅极31与第一子栅极14可以采用相同的材料在同一构图工艺中形成,节省了工艺制程。需要说明的是,在一实施方式中,像素驱动电路与指纹识别电路22可以共同组成完整的像素电路,一个子像素21所在的区域内或者多个子像素21所在的区域内可以设置一个像素电路,用于实现显示以及指纹识别功能。

46.可选地,参考图4,第二栅极31与第一子栅极14同层,第二栅极31位于第三极32以及第四极33与第二有源层34之间。本发明实施例中,薄膜晶体管30为顶栅结构的薄膜晶体管,第二栅极31与第一子栅极14同层。

47.示例性地,参考图4,像素驱动电路还包括存储电容40,存储电容40包括第一极板41和第二极板42,垂直于衬底51的方向上,第一极板41和第二极板42交叠。第一极板41与第二有源层34同层,并可以采用与第二有源层34相同的材料制作。第二极板42与第二栅极31同层,并可以采用与第二栅极31相同的材料制作。

48.示例性地,参考图4,第三极32可以为薄膜晶体管30的源极,第四极33可以为薄膜晶体管30的漏极。或者,第三极32可以为薄膜晶体管30的漏极,第四极33可以为薄膜晶体管30的源极。

49.可选地,参考图4,第二栅极31与第一子栅极14同层,第三极32、第四极33与第二子栅极15同层。本发明实施例中,第三极32、第四极33与第二子栅极15同层,从而无需为第二子栅极15增设新的膜层,减小了阵列基板的厚度。第三极32、第四极33与第二子栅极15同层,第三极32、第四极33与第二子栅极15可以采用相同的材料在同一构图工艺中形成,节省了工艺制程。

50.示例性地,阵列基板还可以包括多个绝缘膜层。继续参考图4,阵列基板包括依次叠层设置的缓冲层52、第一子栅极绝缘层53、第二子栅极绝缘层54、第一子间隔层55、第二子间隔层56、第一钝化层57、第二钝化层58和平坦化层59。缓冲层52位于衬底51与薄膜晶体管30之间。第一子栅极绝缘层53和第二子栅极绝缘层54均位于第二有源层34与第二栅极31之间。第一子间隔层55和第二子间隔层56均位于第二栅极31与第三极32之间,第三极32与第四极33同层。第一钝化层57位于第三极32与第一极12之间,第一极12与第二极13同层。第二钝化层58位于第一极12与平坦化层59之间。平坦化层59位于子像素21与薄膜晶体管30之间,具体地,平坦化层59位于子像素21与第一极12之间。

51.图5为本发明实施例提供的另一种阵列基板的俯视结构示意图,参考图5,第二栅极31与第一子栅极14同层,第一极12、第二极13、第三极32与第四极33同层。本发明实施例中,第一极12、第二极13、第三极32与第四极33同层,从而无需为第一极12和第二极13增设新的膜层,减小了阵列基板的厚度。第一极12、第二极13、第三极32与第四极33同层,第一极

12、第二极13、第三极32与第四极33可以采用相同的材料在同一构图工艺中形成,节省了工艺制程。进一步地,在各实施例中,辅助极16、第一极12和第二极13均位于同一个膜层中,即,均同层设置。

52.示例性地,参考图5,第一子间隔层55位于第一子栅极14与第一有源层11之间。第二子间隔层56位于第一有源层11与第二子栅极15之间。阵列基板还可以包括第一绝缘层510,第一绝缘层510位于第二子间隔层56和第一钝化层57之间,第一绝缘层510位于第二子栅极15与第一极12之间。

53.图6为本发明实施例提供的另一种阵列基板的俯视结构示意图,参考图6,第二栅极31与第一子栅极14同层,第二栅极31位于第二有源层34与衬底51之间。本发明实施例中,薄膜晶体管30为底栅结构的薄膜晶体管,第二栅极31与第一子栅极14同层。

54.示例性地,参考图6,第三极32、第四极33与第二子栅极15同层。本发明实施例中,第三极32、第四极33与第二子栅极15同层,从而无需为第二子栅极15增设新的膜层,减小了阵列基板的厚度。第三极32、第四极33与第二子栅极15同层,第三极32、第四极33与第二子栅极15可以采用相同的材料在同一构图工艺中形成,节省了工艺制程。

55.图7为本发明实施例提供的另一种阵列基板的俯视结构示意图,参考图7,第二栅极31与第一子栅极14同层,第二栅极31位于第二有源层34与衬底51之间。第一极12、第二极13、第三极32与第四极33同层。本发明实施例中,第一极12、第二极13、第三极32与第四极33同层,从而无需为第一极12和第二极13增设新的膜层,减小了阵列基板的厚度。第一极12、第二极13、第三极32与第四极33同层,第一极12、第二极13、第三极32与第四极33可以采用相同的材料在同一构图工艺中形成,节省了工艺制程。

56.示例性地,参考图7,第一子间隔层55位于第一有源层11与第二子栅极15之间。第二子间隔层56位于第二子栅极15与第一极12之间。第一极12、第二极13、第三极32与第四极33同层,从而仅需为第一极12、第二极13、第三极32与第四极33设置一个钝化层,即仅设置第一钝化层57,无需设置第二钝化层58,从而减小了阵列基板的厚度。

57.可选地,参考图6或者图7中的任意一幅,第二栅极31位于第二有源层34与衬底51之间,第一有源层11与第二有源层34同层。本发明实施例中,第一有源层11与第二有源层34同层,从而无需为第一有源层11增设新的膜层,减小了阵列基板的厚度。

58.进一步地,第一有源层11与第二有源层34采用同种材料,从而第一有源层11与第二有源层34可以采用相同的材料在同一构图工艺中形成,节省了工艺制程。示例性地,第一有源层11与第二有源层34均包括多晶硅、单晶硅或者金属氧化物,金属氧化物例如可以包括铟镓锌氧化物(igzo),金属氧化物具有较高的载流子迁移率,从而可以减小感光晶体管10的尺寸,降低成本,以及减小在显示区内所占据的空间,从而提高显示面板的分辨率。在其他实施方式中,第一有源层11与第二有源层34还可以采用不同的材料,本发明实施例对此不作限制。

59.图8为本发明实施例提供的另一种阵列基板的俯视结构示意图,参考图8,第二栅极31与第二子栅极15同层,从而无需为第二子栅极15增设新的膜层,减小了阵列基板的厚度。第二栅极31与第二子栅极15同层,第二栅极31与第二子栅极15可以采用相同的材料在同一构图工艺中形成,节省了工艺制程。

60.示例性地,参考图8,第二栅极31与第二子栅极15同层。第一极12、第二极13、第三

极32与第四极33同层,从而仅需为第一极12、第二极13、第三极32与第四极33设置一个钝化层,即仅设置第一钝化层57,无需设置第二钝化层58,从而减小了阵列基板的厚度。

61.示例性地,参考图8,第一子栅极14与第二有源层34同层,从而无需为第一子栅极14增设新的膜层,减小了阵列基板的厚度。第一子栅极绝缘层53位于第一子栅极14与第一有源层11之间。第二子栅极绝缘层54位于第一有源层11与第二子栅极15之间。

62.可选地,参考图8,第二栅极31与第二子栅极15同层,第二栅极31位于第三极32以及第四极33与第二有源层34之间。薄膜晶体管30为顶栅结构的薄膜晶体管,第二栅极31与第二子栅极15同层。

63.图9为本发明实施例提供的另一种阵列基板的俯视结构示意图,参考图9,第二栅极31与第二子栅极15同层,第一有源层11与第二有源层34同层。本发明实施例中,第一有源层11与第二有源层34同层,从而无需为第一有源层11增设新的膜层,减小了阵列基板的厚度。

64.进一步地,第一有源层11与第二有源层34还可以采用同种材料。

65.示例性地,参考图9,阵列基板还可以包括第二绝缘层511,第二绝缘层511位于缓冲层52和第一子栅极绝缘层53之间,第二绝缘层511位于第一子栅极14与第一有源层11之间。

66.示例性地,继续参考图3,阵列基板包括显示区aa,多个子像素21在显示区aa中,沿第一方向和第二方向阵列排布。多个指纹识别电路22位于显示区aa中,且呈阵列排布。在其他实施方式中,阵列基板还可以包括位于显示区aa外围的非显示区,指纹识别电路22还可以设置于非显示区中。

67.图10为本发明实施例提供的一种指纹识别电路的电路结构示意图,参考图10,感光晶体管10的栅极(包括第一子栅极14和第二子栅极15)与源极(即第二极13)电连接,即,辅助极16与第一子栅极14电连接,第二极13与第二子栅极15电连接。感光晶体管10的第二极13与第一电压端vss电连接。第一电压端vss为感光晶体管10的第二极13、第一子栅极14与第二子栅极15提供相同的电信号。感光晶体管10的第一极12连接到感测节点n1。指纹识别电路还包括第一晶体管m1、第二晶体管m2、第三晶体管m3和存储电容c。第一晶体管m1的栅极耦接到复位端口reset以接收复位控制信号。第一晶体管m1的第一极耦接到第二电压端vdd,第一晶体管m1的第二极耦接到感测节点n1。第二晶体管m2的栅极耦接到感测节点n1,第二晶体管m2的第一极耦接到第二电压端vdd。第三晶体管m3的栅极耦接到输出控制端select,第三晶体管m3的第一极耦接到第二晶体管m2的第二极。存储电容c的第一极板耦接到感测节点n1,存储电容c的第二极板耦接到第一电压端vss。在重置阶段中,第一晶体管m1导通,即复位控制信号将第一晶体管m1控制为导体,使得从第二电压端vdd向感测节点n1施加正电源电压。这使得感测节点n1响应于正电源电压而复位。在感测阶段中,复位端口reset控制第一晶体管m1截止,输出控制端select控制第三晶体管m3截止,感光晶体管10接收到光线,并根据光线强度产生光电流,从而改变感测节点n1的电压值,将感测节点n1的电压值存储在存储电容c中。在输出阶段,复位端口reset控制第一晶体管m1截止,输出控制端select控制第三晶体管m3导通,从而第二晶体管m2会根据其栅源电压产生相应的驱动电流,由于第二电压端vdd为恒定电压,因此,第二晶体管m2产生对应于感测节点n1电压的驱动电流,驱动电流会通过第三晶体管m3输出至读取线l。

68.图11为本发明实施例提供的一种显示面板的剖视结构示意图,参考图11,显示面板包括上述实施例中的阵列基板。本发明实施例中,由于显示面板包括上述实施例中的阵列基板,因此包括上述实施例中的感光晶体管10,因此具有上述感光晶体管10的有益效果,即,提升感光晶体管10的感光效应,以及减小感光晶体管10的阈值电压偏移,提高指纹识别电路的稳定性。

69.示例性地,参考图11,显示面板还可以包括像素限定层512和薄膜封装层60。子像素21可以包括阳极211、有机发光层212和阴极213。有机发光层212位于阳极211和阴极213之间。阳极211与薄膜晶体管30的第四极33电连接。像素限定层512位于薄膜封装层60与平坦化层59之间。有机发光层212设置于像素限定层512的开口中。薄膜封装层60位于子像素21远离衬底51一侧,起到防止水汽以及氧气侵蚀的作用。本发明实施例中,显示面板为有机发光显示面板,在其他实施方式中,显示面板还可以为其他类型的显示面板,例如micro-led显示面板等,本发明对此不作限制。

70.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整、相互结合和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1