具有倾斜隔离层的半导体元件及其制备方法与流程

1.本公开主张2020年9月24日申请的美国正式申请案第17/031,119号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开涉及一种半导体元件及其制备方法。特别涉及一种具有多个倾斜隔离层的半导体元件及其制备方法。

背景技术:

3.半导体元件是使用在不同的电子应用,例如个人电脑、手机、数码相机,或其他电子设备。半导体元件的尺寸逐渐地变小,以符合计算能力所逐渐增加的需求。然而,在尺寸变小的工艺期间,增加不同的问题,且如此的问题在数量与复杂度上持续增加。因此,仍然持续着在达到改善品质、良率、效能与可靠度以及降低复杂度方面的挑战。

4.上文的“现有技术”说明仅是提供背景技术,并未承认上文的“现有技术”说明揭示本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本公开的任一部分。

技术实现要素:

5.本公开的一实施例提供一种半导体元件,包括一基底;二导电栓柱,位在该基底上,并沿一垂直轴延伸;一第一组倾斜隔离层,相互平行,并位在该二导电栓柱之间;以及一第二组倾斜隔离层,相互平行,并位在该二导电栓柱之间;其中,该第一组倾斜隔离层沿一第一方向延伸,该第一方向相对于该垂直轴倾斜;该第二组倾斜隔离层沿一第二方向延伸,该第二方向相对于该垂直轴倾斜;以及该第一方向与该第二方向交叉。

6.在一些实施例中,该半导体元件还包括一第一隔离层,位在该基底上,其中该二导电栓柱沿该第一隔离层设置,该第一组倾斜隔离层与该第二组倾斜隔离层位在该第一隔离层中,以及该第一组倾斜隔离层与该第二组倾斜隔离层包含一材料,该材料不同于该第一隔离层的材料。

7.在一些实施例中,该第一组倾斜隔离层与该第二组倾斜隔离层包含一材料,该材料具有一介电常数,低于该第一隔离层的材料的介电常数。

8.在一些实施例中,该第一组倾斜隔离层与该第二组倾斜隔离层为多孔的。

9.在一些实施例中,该第一组倾斜隔离层与该第二组倾斜隔离层的各孔隙率,介于大约10%到大约80%之间。

10.在一些实施例中,该第一组倾斜隔离层与该第二组倾斜隔离层包含一材料,该材料具有一热膨胀系数以及一杨氏模数(young’s modulus),该热膨胀系数小于大约20ppm/℃,该杨氏模数小于大约15gpa。

11.在一些实施例中,该半导体元件还包括一垫层,位在该二导电栓柱、该第一组倾斜隔离层以及该第二组倾斜隔离层上。

12.在一些实施例中,该第一方向与该垂直轴之间的一角度,介于大约10度到大约80

度之间。

13.在一些实施例中,该第二方向与该垂直轴之间的一角度,介于大约-10度到大约-80度之间。

14.在一些实施例中,该第一方向与该垂直轴之间的一角度,不同于该第二方向与该垂直轴之间的一角度。

15.在一些实施例中,该第一方向与该垂直轴之间的一角度与该第二方向与该垂直轴之间的一角度相反。

16.在一些实施例中,该第一组倾斜隔离层的各下表面与该第二组倾斜隔离层的各下表面,大致与该第一隔离层的一下表面为共面。

17.在一些实施例中,该第一组倾斜隔离层的各最低点与该第二组倾斜隔离层的各最低点位在一位面处,该位面在该第一隔离层的一下表面上。

18.本公开的另一实施例提供一种半导体元件的制备方法,包括提供一基底;形成一第一隔离层在该基底上;沿着该第一隔离层形成二导电栓柱;沿着该第一隔离层形成一第一组倾斜沟槽在该二导电栓柱之间;沿着该第一隔离层形成一第二组倾斜沟槽在该二导电栓柱之间;沿一第一方向形成一第一组倾斜隔离层在该第一组倾斜沟槽中;以及沿一第二方向形成一第二组倾斜隔离层在该第二组倾斜沟槽中;其中,该第一组倾斜隔离层与该第二组倾斜隔离层同时形成,以及该第一方向与该第二方向交叉。

19.在一些实施例中,该第一组倾斜隔离层与该第二组倾斜隔离层包含一材料,该材料不同于该第一隔离层的材料。

20.在一些实施例中,该第一组倾斜隔离层与该第二组倾斜隔离层包含一材料,该材料具有一介电常数,低于该第一隔离层的材料的介电常数。

21.在一些实施例中,形成该第一组倾斜沟槽的该步骤包括:形成一第一硬遮罩层在该第一隔离层上;沿着该第一硬遮罩层形成多个第一硬遮罩开孔;以及使用该第一硬遮罩层与所述多个第一硬遮罩开孔当作多个图案引导件,以执行一第一倾斜蚀刻工艺在该第一隔离层上,以形成该第一组倾斜沟槽。

22.在一些实施例中,该第一硬遮罩层包含下列材料:氧化硅、氮化硅、氮氧化硅、氧化氮化硅(silicon nitride oxide)、氮化硼、硅硼氮化物(silicon boron nitride)、磷硼氮化物(phosphorus boron nitride)、硼碳硅氮化物(boron carbon silicon nitride)或是一碳膜。

23.在一些实施例中,形成该第二组倾斜隔离层的该步骤,包括:使用该第一硬遮罩层与所述多个第一硬遮罩开孔当作多个图案引导件,以执行一第二倾斜蚀刻工艺在该第一隔离层上,以形成该第二组倾斜沟槽,以及该第一倾斜蚀刻工艺的一入射角与该第二倾斜蚀刻工艺的一入射角相反。

24.在一些实施例中,形成该第一组倾斜隔离层的该步骤以及形成该第二组倾斜隔离层的该步骤,包括:形成一层能量可移除复合物在该第一组倾斜沟槽与该第二组倾斜沟槽中,且该层能量可移除复合物包括一基础材料以及一可分解成孔剂材料;以及执行一能量处理以转换该层能量可移除复合物成为该第一组倾斜隔离层与该第二组倾斜隔离层。

25.由于本公开该半导体元件的设计,第一组倾斜隔离层以及第二组倾斜隔离层可用来调整所述多个导电栓柱之间的介电常数。因此,可降低所述多个导电栓柱之间的寄生电

容。因此,可改善该半导体元件效能。此外,该第一组倾斜隔离层与该第二组隔离层可增加该第一隔离层的弹性,其在一接合工艺或一布线工艺(wiring process)期间,可改善该半导体元件的接合强度的电阻。

26.上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文公开的概念与特定实施例可作为修改或设计其它结构或工艺而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

27.参阅实施方式与权利要求合并考量附图时,可得以更全面了解本公开的公开内容,附图中相同的元件符号是指相同的元件。

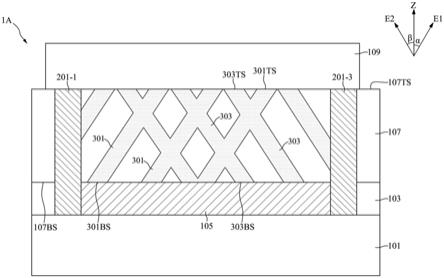

28.图1例示本公开一些实施例的半导体元件的剖视示意图。

29.图2到图9例示本公开一些实施例的各半导体元件的剖视示意图。

30.图10例示本公开一些实施例的半导体元件的制备方法的流程示意图。

31.图11到图19例示本公开一些实施例的半导体元件的制备方法的流程的剖视示意图。

32.图20到图22例示本公开另一实施例的半导体元件的制备方法的流程的剖视示意图。

33.附图标记说明:

34.1a:半导体元件

35.1b:半导体元件

36.1c:半导体元件

37.1d:半导体元件

38.1e:半导体元件

39.1f:半导体元件

40.1g:半导体元件

41.1h:半导体元件

42.1i:半导体元件

43.10:制备方法

44.101:基底

45.103:下隔离层

46.105:下导电层

47.107:第一隔离层

48.107bs:下表面

49.107ts:上表面

50.109:垫层

51.201-1:导电栓柱

52.201-3:导电栓柱

53.201-5:导电栓柱

54.201-7:导电栓柱

55.301:第一组倾斜隔离层

56.301bp:最低点

57.301bs:下表面

58.301sw:侧壁

59.301ts:上表面

60.303:第二组倾斜隔离层

61.303bp:最低点

62.303bs:下表面

63.303sw:侧壁

64.303ts:上表面

65.401:第一硬遮罩层

66.403:第一遮罩层

67.405:第一硬遮罩开孔

68.407:第一组倾斜沟槽

69.407bs:下表面

70.407sw:侧壁

71.409:第二组倾斜沟槽

72.409bs:下表面

73.409sw:侧壁

74.411:第一隔离材料

75.413:能量可移除复合物

76.501:第一倾斜蚀刻工艺

77.503:第二倾斜蚀刻工艺

78.e1:第一方向

79.e2:第二方向

80.h1:高度

81.s11:步骤

82.s13:步骤

83.s15:步骤

84.s17:步骤

85.s19:步骤

86.s21:步骤

87.w1:宽度

88.w2:宽度

89.w3:宽度

90.z:垂直轴

91.α:角度

92.β:角度

93.γ:入射角

94.γ’:锐角

95.γ”:锐角

96.δ:入射角

97.δ’:锐角

98.δ”:锐角

具体实施方式

99.以下描述了组件和配置的具体范例,以简化本公开的实施例。当然,这些实施例仅用以例示,并非意图限制本公开的范围。举例而言,在叙述中第一部件形成于第二部件之上,可能包含形成第一和第二部件直接接触的实施例,也可能包含额外的部件形成于第一和第二部件之间,使得第一和第二部件不会直接接触的实施例。另外,本公开的实施例可能在许多范例中重复参照标号及/或字母。这些重复的目的是为了简化和清楚,除非内文中特别说明,其本身并非代表各种实施例及/或所讨论的配置之间有特定的关系。

100.此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下面(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所示出的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

101.应当理解,当形成一个部件在另一个部件之上(on)、与另一个部件相连(connected to)、及/或与另一个部件耦合(coupled to),其可能包含形成这些部件直接接触的实施例,并且也可能包含形成额外的部件介于这些部件之间,使得这些部件不会直接接触的实施例。

102.应当理解,尽管这里可以使用术语第一,第二,第三等来描述各种元件、部件、区域、层或区段(sections),但是这些元件、部件、区域、层或区段不受这些术语的限制。相反,这些术语仅用于将一个元件、组件、区域、层或区段与另一个区域、层或区段所区分开。因此,在不脱离本发明进步性构思的教导的情况下,下列所讨论的第一元件、组件、区域、层或区段可以被称为第二元件、组件、区域、层或区段。

103.除非内容中另有所指,否则当代表定向(orientation)、布局(layout)、位置(location)、形状(shapes)、尺寸(sizes)、数量(amounts),或其他测量(measures)时,则如在本文中所使用的例如“同样的(same)”、“相等的(equal)”、“平坦的(planar)”,或是“共面的(coplanar)”等术语(terms)并非必要意指一精确地完全相同的定向、布局、位置、形状、尺寸、数量,或其他测量,但其意指在可接受的差异内,包含差不多完全相同的定向、布局、位置、形状、尺寸、数量,或其他测量,而举例来说,所述可接受的差异可因为制造流程(manufacturing processes)而发生。术语“大致地(substantially)”可被使用在本文中,以表现出此意思。举例来说,如大致地相同的(substantially the same)、大致地相等的(substantially equal),或是大致地平坦的(substantially planar),为精确地相同的、相等的,或是平坦的,或者是其可为在可接受的差异内的相同的、相等的,或是平坦的,而举

doped silicon oxide)、有机硅酸盐玻璃(organo silicate glass)、低介电常数介电材料或其组合。该低介电常数材料可具有一介电常数,小于3.0或甚至小于2.5。

111.请参考图1,下导电层105可设置在下隔离层103中。举例来说,下导电层105包含铜、铝、钛、钨、类似物或其组合。下导电层105可电性耦接到所述多个装置元件。

112.请参考图1,第一隔离层107可设置在下隔离层103上。在一些实施例中,第一隔离层107可包含下列材料:氮化硅、氧化硅、氮氧化硅、氧化氮化硅、流动氧化物、硅氮烷、未掺杂硅玻璃、硼二氧化硅玻璃、磷硅酸盐玻璃、硼磷硅酸盐玻璃、等离子体辅助四氧乙基硅、氟硅酸盐玻璃、掺碳的氧化硅、有机硅酸盐玻璃、低介电常数介电材料或其组合。

113.在一些实施例中,第一隔离层107可包含下列材料:氧化硅、氮化硅、氮氧化硅、氮化氧化硅(silicon oxide nitride)、聚酰亚胺(polyimide)、聚苯并恶唑(polybenzoxazole)、磷硅酸盐玻璃、未掺杂硅玻璃或氟硅酸盐玻璃。第一隔离层107可视为一钝化层。

114.请参考图1,导电栓柱201-1、201-3可沿第一隔离层107与下隔离层103垂直设置。意即,导电栓柱201-1、201-3可沿垂直轴z延伸。导电栓柱201-1、201-3的各侧壁的各下部可贴合到下导电层105。换言之,导电栓柱201-1、201-3以及下导电层105可电性连接。导电栓柱201-1、201-3的各上表面可大致与第一隔离层107的各上表面107ts为共面。举例来说,导电栓柱201-1、201-3可包含钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物(例如碳化钽、碳化钛、碳化钽镁(tantalum magnesium carbide)、金属氮化物(例如氮化钛)、过渡金属铝化物或其组合。

115.请参考图1,第一组倾斜隔离层301可设置在第一隔离层107中,以及在导电栓柱201-1、201-3之间。第一组倾斜隔离层301的各上表面301ts可大致与第一隔离层107的上表面107ts为共面。第一组倾斜隔离层301的各下表面301bs可大致与第一隔离层107的下表面107bs为共面。第一组倾斜隔离层301可相互平行。第一组倾斜隔离层301可沿一第一方向e1延伸。第一方向e1可相对于垂直轴z倾斜。第一方向e1与垂直轴z之间的一角度α,可介于大约10度与大约80度之间。

116.请参考图1,第二组倾斜隔离层303可设置在第一隔离层107中,以及在导电栓柱201-1、201-3之间。第二组倾斜隔离层303的各上表面303ts可大致与第一隔离层107的上表面107ts为共面。第二组倾斜隔离层303的各下表面303bs可与第一隔离层107的下表面107bs为共面。第二组倾斜隔离层303可相互平行。第二组倾斜隔离层303可沿一第二方向e2延伸。第二方向e2可相对于垂直轴z倾斜。第一方向e1与第二方向e2可交叉。第二方向e2与垂直轴z之间的一角度β,介于大约-10度到大约-80度之间。第一组倾斜隔离层301中的一些以及第二组倾斜隔离层303中的一些可交叉。第一组倾斜隔离层301中的另一些以及第二组倾斜隔离层303中的另一些可不交叉。

117.在一些实施例中,第一方向e1与第二方向e2之间的一角度,可介于大约20度到大约160度之间。

118.第一组倾斜隔离层301与第二组倾斜隔离层303可包含相同材料。在一些实施例中,第一组倾斜隔离层301与第二组倾斜隔离层303可包含不同于第一隔离层107的材料。在一些实施例中,第一组倾斜隔离层301与第二组倾斜隔离层303可包含下列材料:氮化硅、氧化硅、氮氧化硅、氧化氮化硅、流动氧化物、硅氮烷、未掺杂硅玻璃、硼二氧化硅玻璃、磷硅酸

盐玻璃、硼磷硅酸盐玻璃、等离子体辅助四氧乙基硅、氟硅酸盐玻璃、掺碳的氧化硅、有机硅酸盐玻璃、低介电常数介电材料或其组合。

119.在一些实施例中,第一组倾斜隔离层301与第二组倾斜隔离层303可包含一材料,具有一介电常数,该介电常数低于第一隔离层107的介电常数。包含较低介电常数的材料的第一组倾斜隔离层301与第二组倾斜隔离层303,可降低导电栓柱201-1、201-3之间的寄生电容。意即,包含较低介电常数的材料的第一组倾斜隔离层301与第二组倾斜隔离层303,减缓导电栓柱201-1、201-3所产生的电子信号之间或是施加到导电栓柱201-1、201-3之间的电子信号之间的一干扰效应(interference effect)。

120.在一些实施例中,第一组倾斜隔离层301与第二组倾斜隔离层303可包含一材料,该材料具有一热膨胀系数以及一杨氏模数(young’s modulus),该热膨胀系数小于大约20ppm/℃,杨氏模数小于大约15gpa。在一些实施例中,第一组倾斜隔离层301与第二组倾斜隔离层303可包含一材料,该材料包括聚酰亚胺或一环氧基(epoxy-based)材料。第一组倾斜隔离层301与第二组倾斜隔离层303可当成一减震垫(cushion),以降低一凸块工艺(bumping process)或一布线工艺(wiring process)的一应力;因此,可减少第一隔离层107的分层(delamination)。

121.请参考图1,垫层109可设置在第一隔离层107上。垫层109可覆盖导电栓柱201-1、201-3的各上表面、第一组倾斜隔离层301的各上表面301ts以及第二组倾斜隔离层303的各上表面301ts。举例来说,垫层109可包含下列材料:铝、铜、钛、钨、铝-铜合金、铝合金或铜合金。

122.图2到图9例示本公开一些实施例的各半导体元件1b、1c、1d、1e、1f、1g、1h、1i的剖视示意图。请参考图2,半导体元件1b可具有类似于如图1所例示的一结构。图2中与图1中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。请参考图2,导电栓柱201-1、201-3的各侧壁的各下部可远离下导电层105。第一组倾斜隔离层301与第二组倾斜隔离层303可设置在导电栓柱201-1、201-3之间。

123.请参考图3,半导体元件1c可具有类似于如图1所例示的一结构。图3中与图1中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。

124.请参考图3,导电栓柱201-1、201-3可沿第一隔离层107设置,并设置在下导电层105上。第一组倾斜隔离层301与第二组倾斜隔离层303可设置在导电栓柱201-1、201-3之间。

125.请参考图4,半导体元件1d可具有类似于如图1所例示的一结构。图4中与图1中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。请参考图4,导电栓柱201-1可沿第一隔离层107设置,并设置在下导电层105上。导电栓柱201-3可沿第一隔离层107与下导电层105设置。导电栓柱201-3的侧壁的下部可接合在下导电层105上。第一组倾斜隔离层301与第二组倾斜隔离层303可设置在导电栓柱201-1、201-3之间。

126.请参考图5,半导体元件1e可具有类似于如图4所例示的一结构。图5中与图4中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。请参考图5,导电栓柱201-3的侧壁的下部可远离下导电层105。在一些实施例中,导电栓柱201-3可电性隔离下导电层105。第一组倾斜隔离层301与第二组倾斜隔离层303可设置在导电栓柱201-1、201-3之间。导电栓柱201-3可改善半导体元件1e的机械强度(mechanical strength)。

127.请参考图6,半导体元件1f可具有类似于如图1所例示的一结构。图6中与图1中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。请参考图6,第一组倾斜隔离层301与第二组倾斜隔离层303可为多孔的(porous)。第一组倾斜隔离层301与第二组倾斜隔离层303的个孔隙率可介于大约10%到大约80%之间。第一组倾斜隔离层301与第二组倾斜隔离层303可包括一骨架以及多个空的空间,所述多个空的空间在骨架之间。多个空的空间可相互连接,并可填满空气。举例来说,骨架可包含氧化硅、低介电质材料(low-dielectric materials)或甲基硅倍半氧烷(methylsilsesquioxane)。第一组倾斜隔离层301与第二组倾斜隔离层303的多个空的空间可填满空气。因此,举例来说,第一组倾斜隔离层301与第二组倾斜隔离层303的一介电常数,可大大地低于包含氧化硅的一层。因此,第一组倾斜隔离层301与第二组倾斜隔离层303可大大地降低导电栓柱201-1、210-3之间的寄生电容。意即,第一组倾斜隔离层301与第二组倾斜隔离层303可减缓导电栓柱201-1、201-3所产生的电子信号之间或是施加到导电栓柱201-1、201-3之间的电子信号之间的一干扰效应(interference effect)。

128.请参考图7,半导体元件1g可具有类似于如图1所例示的一结构。图7中与图1中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。请参考图7,更多的导电栓柱可设置在半导体元件1g中。举例来说,导电栓柱201-1、201-3可沿第一隔离层107与下隔离层103设置。导电栓柱201-5、201-7可沿第一隔离层107设置,并可设置在下导电层105上。第一组倾斜隔离层301与第二组倾斜隔离层303可分别对应设置在相邻对的导电栓柱201-1、201-3、201-5、201-7之间。

129.请参考图8,半导体元件1h可具有类似于如图7所例示的一结构。图8中与图7中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。请参考图8,第一组倾斜隔离层301与第二组倾斜隔离层303可仅设置在相邻对的导电栓柱201-1、201-3、201-5、201-7中的一些中。举例来说,在本公开中,第一组倾斜隔离层301与第二组倾斜隔离层303可仅设置在导电栓柱201-1、201-5之间,以及在导电栓柱201-7、201-3之间。

130.请参考图9,半导体元件1i可具有类似于如图7所例示的一结构。图9中与图7中相同或类似的元件已以相似的元件编号进行标示,并已省略重复的描述。

131.请参考图9,第一组倾斜隔离层301的各最低点301bp以及第二组倾斜隔离层303的各最低点303bp可位在一垂直位面,位在第一隔离层107的下表面107bs的一垂直位面上。

132.图10例示本公开一些实施例的半导体元件1a的制备方法10的流程示意图。图11到图19例示本公开一些实施例的半导体元件1a的制备方法的流程的剖视示意图。请参考图10及图11,在步骤s11,可提供一基底101,一下导电层104可形成在基底101上,以及一第一隔离层107可形成在下导电层105上。

133.请参考图11,一下隔离层103可形成在基底101上。下隔离层103的制作技术可包含一沉积工艺,例如化学气相沉积、等离子体加强化学气相沉积、低压化学气相沉积或类似方法。下导电层105可通过一镶嵌工艺(damascene process)而形成在下隔离层103中。第一隔离层107可以类似于下隔离层103形成的一程序而形成在下导电层105与下隔离层103上。

134.请参考图10及图12,在步骤s13,导电栓柱201-1、201-3可沿第一隔离层107形成,并电性连接到下导电层105,以及一第一硬遮罩层401可形成在第一隔离层107上。请参考图12,可执行一微影工艺以界定导电栓柱201-1、201-3的一所欲图案。可继续进行一继续的蚀

刻工艺,例如一非等向性该蚀刻工艺,以沿着第一隔离层107与下隔离层103而垂直形成多个开孔。一导电材料可完全填满所述多个开孔,而该导电材料例如钨、钴、锆、钽、钛、铝、钌、铜、金属碳化物(例如碳化钽、碳化钛、碳化钽镁(tantalummagnesium carbide)、金属氮化物(例如氮化钛)、过渡金属铝化物或其组合。接下来,可执行一平坦化工艺,例如化学机械研磨,直到第一隔离层107的上表面暴露为止,以移除多余材料,提供一大致平坦表面给接下来的处理步骤,并同时形成导电栓柱201-1、210-3。

135.在一些实施例中,第一硬遮罩层401可包含氧化硅、氮化硅、氮氧化硅、氧化氮化硅、类似物或其组合。第一硬遮罩层401的制作技术包含多个沉积工艺,例如化学气相沉积、等离子体加强化学气相沉积、低压化学气相沉积或类似方法。

136.应当理解,在本公开的描述中,氮氧化硅表示一物质(substance),其包含硅、氮以及氧,且在其中的氧的一比率大于氮的一比率。氧化氮化硅表示一物质,其包含硅、氧以及氮,且在其中的氮的一比率大于氧的一比率。

137.在一些实施例中,第一硬遮罩层401可包含氮化硼、硅硼氮化物、磷硼氮化物或硼碳硅氮化物。第一硬遮罩层401的制作技术可包含一膜形成工艺以及一处理工艺。在一些实施例中,在模形成工艺中,可为硼基(boron-based)前驱物的第一前驱物可引入在第一隔离层107上,以形成一硼基层。接下来,在处理工艺中,可为氮基前驱物的第二前驱物可引入,以与硼基层产生反应,并转换硼基层成为第一硬遮罩层401。

138.在一些实施例中,所述多个第一前驱物可为二硼烷(diborane)、硼氮炔(borazine)或是硼氮炔的一烷基取代衍生物(alkyl-substituted derivative)。在一些实施例中,所述多个第一前驱物可以一流量引入,该流量介于大约5sccm(每分钟标准立方厘米(standard cubic centimeter per minute))到大约50slm(每分钟标准公升(standard liter per minute))之间;在一些实施例中,介于大约10sccm到大约1slm之间。在一些实施例中,所述多个第一前驱物可通过稀释气体(dilution gas)而被引入,该稀释气体例如氮(nitrogen)、氢(hydrogen)、氩(argon)或其组合。该稀释气体可以一流量被引入,该流量介于大约5sccm到大约50slm之间;在一些实施例中,介于大约1slm到大约10slm之间。

139.在一些实施例中,膜形成工艺无须等离子体的辅助即可执行。在此状况下,膜形成工艺的一基底温度可介于大约100℃到大约1000℃之间。举例来说,膜形成工艺的基底温度可介于大约300℃到大约500℃之间。膜形成工艺的一工艺压力可介于大约10mtorr到大约760torr之间。举例来说,膜形成工艺的工艺压力可介于大约2torr到大约10torr之间。

140.在一些实施例中,膜形成工艺可在等离子体存在下进行。在此情况下,膜形成工艺的一基底温度可介于大约100℃到大约1000℃之间。举例来说,膜形成工艺的基底温度可介于大约300℃到大约500℃之间。膜形成工艺的一工艺温度可介于大约10mtorr到大约760torr。举例来说,膜形成工艺的工艺温度可介于大约2torr到大约10torr。等离子体可通过介于2w到5000w之间的一射频功率(rf power)所提供。举例来说,等离子体通过介于30w到1000w之间的一射频功率(rf power)所提供。

141.在一些实施例中,所述多个第二前驱物可为氨水(ammonia)或联氨(hydrazine)。在一些实施例中,所述多个第二前驱物可以一流量引入,该流量介于大约5sccm到大约50slm之间;在一些实施例中,介于大约10sccm到大约1slm之间。

142.在一些实施例中,多个氧基前驱物可在处理工艺中与所述多个第二前驱物一起引

入。举例来说,所述多个氧基前驱物可为氧、一氧化氮(nitric oxide)、一氧化二氮(nitrous oxide)、二氧化碳或水。

143.在一些实施例中,多个硅基前驱物可在处理工艺中与所述多个第二前驱物一起引入。举例来说,所述多个硅基前驱物可为硅烷(silane)、三甲硅烷基胺(trisilylamine)、三甲基硅烷(trimethylsilane)以及硅氮烷(silazanes)(例如六甲基环三硅氮烷(hexamethylcyclotrisilazane))。

144.在一些实施例中,多个磷基前驱物可在处理工艺中与所述多个第二前驱物一起引入。举例来说,所述多个磷基前驱物可为磷化氢(phosphine)。

145.在一些实施例中,所述多个氧基前驱物、所述多个硅基前驱物或所述多个磷基前驱物可在处理工艺中与所述多个第二前驱物一起引入。

146.在一些实施例中,处理工艺可用一等离子体工艺、一紫外线固化(uv cure)工艺、一热退火(thermal anneal)工艺或其组合的一辅助所执行。

147.当该处理以等离子体工艺为辅助而执行时,等离子体工艺的等离子体可通过射频功率(rf power)所提供。在一些实施例中,在介于大约100khz直到大约1mhz之间的一单一低频率下,射频功率可介于大约2w到大约5000w。在一些实施例中,在大于约13.6mhz的一单一高频率下,射频功率可介于大约30w到大约1000w。在此情况下,处理工艺的一基底温度可介于大约20℃到大约1000℃之间。处理工艺的一工艺压力可介于大约10mtorr到大约760torr之间。

148.当该处理以紫外线固化工艺为辅助所执行时,在此情况下,处理工艺的一基底温度可介于大约20℃到大约1000℃之间。处理工艺的一工艺温度可介于大约10mtorr到大约760torr之间。紫外线固化可通过任何紫外线源所提供,例如汞微波弧灯(mercury microwave arc)、脉冲式氙闪光灯(pulsed xenon flash lamps)或高效率uv发光二极管阵列(high-efficiency uv light emitting diode arrays)。紫外线源可具有一波长,介于大约170nm到大约400nm之间。紫外线源可提供一光子能量(photon energy),介于大约0.5ev到大约10ev之间;在一些实施例中,介于大约1ev到大约6ev之间。紫外线固化工艺的辅助可从第一硬遮罩层201移除氢。当氢可扩散进入半导体元件1a的其他区域以及可能降低半导体元件1a的可靠度时,氢通过紫外线固化工艺的辅助的移除可改善半导体元件1a的可靠度。此外,紫外线固化工艺可增加第一硬遮罩层401的密度。

149.当该处理以热退火工艺为辅助所执行时,在此状况下,处理工艺的一基底温度可介于大约20℃到大约1000℃之间。处理工艺的一工艺压力可介于大约10mtorr到大约760torr之间。

150.在一些实施例中,第一硬遮罩层401可由一碳膜所制。在文中所使用的术语“碳膜(carbon film)”,其主要由多个碳原子所界定,或者是其物理和化学性质取决于其碳含量。术语“碳膜”是指排除作为简单混合物或包含碳的化合物的材料,举例来说,包含碳的化合物的材料为介电材料,例如掺杂碳的氮氧化硅、掺杂碳的氧化硅或掺杂碳的多晶硅。举例来说,这些术语确实包括石墨(graphite)、炭(charcoal)以及卤素碳化物(halocarbons)。

151.在一些实施例中,碳膜通过一工艺所沉积,该工艺包括引入一工艺气体混合物进入一工艺腔室,该工艺气体混合物由一或多个烃化合物(hydrocarbon compounds)。烃化合物具有一化学式c

xhy

,其中x具有介于2到4之间的一范围,y具有介于2到10之间的一范围。举

例来说,烃化合物可为丙烯(propylene,c3h6)、丙炔(propyne,c3h4)、丙烷(propane,c3h8)、丁烷(butane,c4h

10

)、丁烯(butylene,c4h8)、丁二烯(butadiene,c4h6)、乙炔(acetylene,c2h2)或其组合。在一些实施例中,可以使用烃化合物的部分或完全氟化的衍生物(fluorinated derivatives)。掺杂衍生物包括烃化合物的含硼衍生物(boron-containing derivatives)及其氟化衍生物(fluorinated derivatives)。

152.在一些实施例中,碳膜通过维持在一基底温度以从处理气体混合物所沉积,而该基底温度介于大约100℃到大约700℃之间;在一些实施例中,介于大约350℃到550℃之间。在一些实施例中,碳膜通过维持在一腔室压力以从处理气体混合物所沉积,而该腔室压力介于大约1torr到大约20torr之间。碳膜可以一流量分别通过引入烃气体(hydrocarbon gas)和任何惰性或反应性气体而从处理气体混合物进行沉积,而该流量介于大约50sccm到大约2000sccm之间。

153.在一些实施例中,处理气体混合物还可包括一非活性气体(inert gas),例如氩。然而,其可使用其他非活性气体,例如氮或其他惰性气体,惰性气体例如氦。可使用所述多个非活化气体以控制碳膜的密度以及沉积率。此外,可以将多种不同气体添加到处理气体混合物中以改变碳膜的特性。所述多个气体可为反应气体,例如氢、氨、氢与氮的混合物或其组合。可使用氢或氨的添加以控制碳膜的氢的比率,进而控制层特性,例如蚀刻选择性、化学机械研磨阻力特性以及反射率(reflectivity)。在一些实施例中,可添加所述多个反应气体与所述多个非活化气体的一混合物到处理气体混合物,以沉积碳膜。

154.碳膜可包含碳与氢原子,其可为一可调整的碳:氢比率,介于大约10%的氢到大约60%的氢之间。控制碳膜的氢比例可以调节相对应的蚀刻选择性和化学机械研磨阻力特性。当氢含量降低时,碳膜的蚀刻阻力以及选择性增加。当执行蚀刻工艺以将所欲的图案转移到下层上时,碳膜移除率的降低可以使碳膜适合作为一遮罩层。

155.请参考图13,一第一遮罩层403可形成在第一硬遮罩层401上。第一遮罩层43可为一光刻胶层。第一遮罩层403可通过一微影工艺进行图案化。请参考图14,可执行一蚀刻工艺,例如一非等向性干蚀刻工艺,以移除第一硬遮罩层401的一些部分,且同时形成多个第一硬遮罩开孔405。在一些实施例中,蚀刻工艺的第一硬遮罩层401的蚀刻率,可快于蚀刻工艺的第一隔离层107的蚀刻率。举例来说,在蚀刻工艺期间,第一硬遮罩层401对第一隔离层107的蚀刻率比率,可介于大约100:1到大约1.05:1之间、介于大约100:1到大约10:1之间、介于大约50:1到大约10:1之间、介于大约30:1到大约10:1之间、介于大约20:1到大约10:1之间,或是介于大约15:1到大约10:1之间。在一些实施例中,所述多个第一硬遮罩开孔405的宽度w1对第一硬遮罩开孔405的高度h1的一比率,可介于大约5:1到大约1:15之间、介于大约3:1到大约1:13之间、介于大约1:1到大约1:11之间,以及介于大约5:1到大约1:8之间。

156.请参考图10、图15以及图16,在步骤s17,一第一组倾斜沟槽407以及一第二组倾斜沟槽409可沿第一隔离层107以形成在导电栓柱201-1、201-3之间。请参考图15,可执行一第一倾斜蚀刻工艺501,以沿第一隔离层107形成第一组倾斜沟槽407。第一倾斜蚀刻工艺501可使用第一硬遮罩层401与所述多个第一硬遮罩开孔405当成多个图案引导件(pattern guides)。在一些实施例中,第一倾斜蚀刻工艺501的一入射角γ可由所述多个第一硬遮罩开孔405的宽度w1与所述多个第一硬遮罩开孔405的高度h1所界定。在一些实施例中,第一倾斜蚀刻工艺501的入射角γ可介于大约10度到大约80度之间。在一些实施例中,第一倾斜

蚀刻工艺501的入射角γ可介于大约20度到大约60度之间。在一些实施例中,第一倾斜蚀刻工艺501的入射角γ可介于大约20度到大约40度之间。

157.在一些实施例中,第一倾斜蚀刻工艺501可为一非等向性蚀刻工艺,例如一反应性离子蚀刻工艺(reactive ion etching process)。反应性离子蚀刻工艺可包括多个蚀刻剂气体(etchant gases)以及多个钝化气体(passivation gases),这可能会抑制等向性效应(isotropic effect),以限制材料在水平方向上的移除。所述多个蚀刻剂气体可包括氯气(chlorine gas)以及三氯化硼(boron trichloride)。所述多个钝化气体可包括氟仿(fluoroform)或其他适合的卤烃(halocarbons)。在一些实施例中,由碳膜所制的所述多个第一硬遮罩层401可以作为反应性离子蚀刻工艺的所述多个钝化气体的一卤烃源。

158.在一些实施例中,第一倾斜蚀刻工艺501的第一隔离层107的蚀刻率,可快于第一倾斜蚀刻工艺501的第一硬遮罩层401的蚀刻率。举例来说,在第一倾斜蚀刻工艺501期间,第一隔离层107对第一硬遮罩层401的蚀刻率比率,可介于大约100:1到大约1.05:1之间、介于大约100:1到大约10:1之间、介于大约50:1到大约10:1之间、介于大约30:1到大约10:1之间、介于大约20:1到大约10:1之间,或是介于大约15:1到大约10:1之间。在一些实施例中,在第一倾斜蚀刻工艺501期间,第一隔离层107对导电栓柱201-1、201-3的一蚀刻率比率,可介于大约100:1到大约1.05:1之间、介于大约100:1到大约10:1之间、介于大约50:1到大约10:1之间、介于大约30:1到大约10:1之间、介于大约20:1到大约10:1之间,或是介于大约15:1到大约10:1之间。

159.第一组倾斜沟槽407可沿第一方向e1延伸,而第一方向e1相对于垂直轴z倾斜。第一组倾斜沟槽407的各侧壁407sw与第一组倾斜沟槽407的各下表面407bs之间的一锐角γ’,可介于大约10度到大约80度之间。第一组倾斜沟槽407的宽度w2可小于所述多个第一硬遮罩开孔405的宽度w1。

160.请参考图16,可执行一第二倾斜蚀刻工艺503,以沿第一隔离层107形成第二组倾斜沟槽409。第二倾斜蚀刻工艺503可使用第一硬遮罩层401与所述多个第一硬遮罩开孔405当成多个图案引导件。在一些实施例中,第二倾斜蚀刻工艺503的入射角δ可与第一倾斜蚀刻工艺501相对于垂直轴z的入射角γ相反,并可由所述多个第一硬遮罩开孔405的宽度w1与所述多个第一硬遮罩开孔405的高度h1所界定。在一些实施例中,第二倾斜蚀刻工艺503的入射角δ可不同于第一倾斜蚀刻工艺501的入射角γ。在一些实施例中,第二倾斜蚀刻工艺503的入射角δ可介于大约-10度到大约-80度之间。

161.在一些实施例中,第二倾斜蚀刻工艺503可为一非等向性蚀刻工艺,例如一反应性离子蚀刻工艺。第二倾斜蚀刻工艺503的第一隔离层107的蚀刻率,可快于第二倾斜蚀刻工艺503的第一硬遮罩层401的蚀刻率。举例来说,在第二倾斜蚀刻工艺503期间,第一隔离层107对第一硬遮罩层401的一蚀刻率比率,可介于大约100:1到大约1.05:1之间、介于大约100:1到大约10:1之间、介于大约50:1到大约10:1之间、介于大约30:1到大约10:1之间、介于大约20:1到大约10:1之间,或是介于大约15:1到大约10:1之间。在一些实施例中,在第二倾斜蚀刻工艺503期间,第一隔离层107对导电栓柱201-1、201-3的一蚀刻率比率,可介于大约100:1到大约1.05:1之间、介于大约100:1到大约10:1之间、介于大约50:1到大约10:1之间、介于大约30:1到大约10:1之间、介于大约20:1到大约10:1之间,或是介于大约15:1到大约10:1之间。

162.第二组倾斜沟槽409可沿一第二方向e2延伸,而第二方向e2相对于垂直轴z倾斜。第二方向e2与第一方向e1可交叉。在一些实施例中,第二组倾斜沟槽409的各侧壁409sw与第二组倾斜沟槽409的各下表面409bs间的一锐角δ’,可介于大约-10度到大约-80度之间。在一些实施例中,第一组倾斜沟槽407与第二组倾斜沟槽409的一些部分可重叠。换言之,一些第一组倾斜沟槽407与第二组倾斜沟槽409可交叉。第二组倾斜沟槽409的宽度w3可小于所述多个第一硬遮罩开孔405的宽度w1。在一些实施例中,第二组倾斜沟槽409的宽度w3可相同于第一组倾斜沟槽407的宽度w2,但并不以此为限。

163.请参考图10、图17及图18,在步骤s19,一第一组倾斜隔离层301可形成在第一组倾斜沟槽407中,以及一第二组倾斜隔离层301可形成在第二组倾斜沟槽409中。请参考图17,可形成一层第一隔离材料411以完全填满第一组倾斜沟槽407、第二组倾斜沟槽409以及所述多个第一硬遮罩开孔405,并覆盖第一硬遮罩层401。在一些实施例中,第一隔离材料411可为不同于第一隔离层107的材料。在一些实施例中,第一隔离材料411可为一材料,具有一介电常数,该介电常数小于第一隔离层107的介电常数。在一些实施例中,第一隔离材料411可为氮化硅、氧化硅、氮氧化硅、氧化氮化硅、流动氧化物、硅氮烷、未掺杂硅玻璃、硼二氧化硅玻璃、磷硅酸盐玻璃、硼磷硅酸盐玻璃、等离子体辅助四氧乙基硅、氟硅酸盐玻璃、掺碳的氧化硅、有机硅酸盐玻璃或其组合。在一些实施例中,第一隔离材料411可为一材料,该材料具有一热膨胀系数以及一杨氏模数,热膨胀系数小于大约20ppm/℃,杨氏模数小于大约15gpa。

164.请参考图18,可执行一平坦化工艺,例如化学机械研磨,直到第一隔离层107的上表面107ts暴露为止,以移除多余材料,提供一大致平坦表面给接下来的处理步骤,且同时形成第一组倾斜隔离层301以及第二组倾斜隔离层303。

165.第一组倾斜隔离层301的剖面轮廓可由第一组倾斜沟槽407所界定。在一些实施例中,第一组倾斜隔离层301可沿第一方向e1延伸。第一组倾斜隔离层301的各侧壁301sw与第一组倾斜隔离层301的各下表面301bs之间的一锐角γ”,可介于大约10度到大约80度之间。

166.第二组倾斜隔离层303的剖面轮廓可由第二组倾斜沟槽409所界定。在一些实施例中,第二组倾斜隔离层303可沿第二方向e2延伸。第二组倾斜隔离层303的各侧壁303sw与第二组倾斜隔离层303的各下表面303bs之间的一锐角δ”,可介于大约-10度到大约-80度之间。在一些实施例中,第一组倾斜隔离层301与第二组倾斜隔离层303的一些部分可重叠。换言之,第一组倾斜隔离层301与第二组倾斜隔离层303的一些部分可交叉。

167.请参考图10及图19,在步骤s21,一垫层109可形成在导电栓柱201-1、201-3上。请参考图19,可形成垫层109以覆盖导电栓柱201-1、201-3的各上表面、第一组倾斜隔离层301的各上表面以及第二组倾斜隔离层303的各上表面。垫层109的制作技术包含一沉积工艺以及一继续的光蚀刻(photo-etch)工艺。沉积工艺可为物理气相沉积、化学气相沉积、喷溅或电镀。

168.图20到图22例示本公开另一实施例的半导体元件1f的制备方法的流程的剖视示意图。请参考图20,一中间半导体可以类似于图11到图16所例示的一程序进行制造。一层能量可移除复合物413可完全填满第一组倾斜沟槽407、第二组倾斜沟槽409以及所述多个第一硬遮罩开孔405,并覆盖第一硬遮罩层401。能量可移除复合物413可包括一材料,例如一热可分解材料、一光可分解材料、一电子束可分解材料或其组合。举例来说,能量可移除复

合物413可包括一基础材料以及一可分解成孔剂材料,该可分解成孔剂材料在暴露于一能量源时被牺牲地移除。基础材料可包括一甲基硅倍半氧烷基(methylsilsesquioxane based)材料、低介电质材料或氧化硅。可分解成孔剂材料可包括一成孔剂有机化合物,其提供孔隙率给能量可移除复合物413的基础材料。在一些实施例中,能量可移除复合物413可包含大约10%的可分解成孔剂材料以及大约90%的基础材料。在一些实施例中,能量可移除复合物413可包含大约80%的可分解成孔剂材料以及大约20%的基础材料。

169.请参考图21,可执行类似于图18所例示的一平坦化工艺。垫层109可通过类似于如图19所例示的一程序而形成在第一隔离层107上。

170.请参考图22,一能量处理工艺可通过对其施加一能量源而执行在如图21所例示的中间半导体上。能量源可包括热、光或其组合。当热使用当成能量源时,能量处理的一温度可介于大约800℃到大约900℃之间。当光使用当成能量源时,可施加一紫外光。能量处理可从该层能量可移除复合物413而移除该可分解成孔剂材料,以产生多个空的空间(孔洞),而基础材料保留在原处。在能量处理之后,该层能量可移除复合物413可转换成为多孔的第一组倾斜隔离层301与第二组倾斜隔离层303。

171.本公开的一实施例提供一种半导体元件,包括一基底;二导电栓柱,位在该基底上,并沿一垂直轴延伸;一第一组倾斜隔离层,相互平行,并位在该二导电栓柱之间;以及一第二组倾斜隔离层,相互平行,并位在该二导电栓柱之间;其中,该第一组倾斜隔离层沿一第一方向延伸,该第一方向相对于该垂直轴倾斜;该第二组倾斜隔离层沿一第二方向延伸,该第二方向相对于该垂直轴倾斜;以及该第一方向与该第二方向交叉。

172.本公开的另一实施例提供一种半导体元件的制备方法,包括提供一基底;形成一第一隔离层在该基底上;沿着该第一隔离层形成二导电栓柱;沿着该第一隔离层形成一第一组倾斜沟槽在该二导电栓柱之间;沿着该第一隔离层形成一第二组倾斜沟槽在该二导电栓柱之间;沿一第一方向形成一第一组倾斜隔离层在该第一组倾斜沟槽中;以及沿一第二方向形成一第二组倾斜隔离层在该第二组倾斜沟槽中;其中,该第一组倾斜隔离层与该第二组倾斜隔离层同时形成,以及该第一方向与该第二方向交叉。

173.由于本公开该半导体元件的设计,第一组倾斜隔离层301以及第二组倾斜隔离层303可用来调整导电栓柱201-1、201-3之间的介电常数。因此,可降低导电栓柱201-1、201-3之间的寄生电容。因此,可改善半导体元件1a效能。此外,第一组倾斜隔离层301与第二组隔离层303可增加第一隔离层107的弹性,其在一接合工艺或一布线工艺期间,可改善半导体元件1a的接合强度的电阻。

174.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多工艺,并且以其他工艺或其组合替代上述的许多工艺。

175.再者,本公开的范围并不受限于说明书中所述的工艺、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的公开内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的工艺、机械、制造、物质组成物、手段、方法、或步骤。据此,这些工艺、机械、制造、物质组成物、手段、方法、或步骤包含于本公开的权利要求内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1