一种氮化物发光二极管外延片及其制备方法与流程

1.本发明涉及光电子技术领域,具体涉及一种氮化物发光二极管外延片及其制备方法。

背景技术:

2.近年来,以led器件为核心的半导体照明光源,已经被证实了在光电方面有着广阔的应用前景。因其具有发光效率高、耐用、空间占比小、无环境污染等优势,广泛的应用于照明、显示屏背光源等行业。

3.目前gan基led通常都生长在蓝宝石、sic和si等异质衬底上。由于gan与衬底间存在晶格失配以及热失配,gan基led器件中穿透位错密度达108‑

10

10

/cm2,并且这些穿透位错在生长量子阱时形成v

‑

pits。作为ingan led器件中的一个典型特征,v

‑

pits可能影响空穴往量子阱注入,造成电子与空穴在v型坑中进行非辐射复合,降低了电子与空穴辐射复合的效率。

4.现有gan外延片包括依次在衬底上沉积缓冲层、非掺杂氮化物层、n型氮化物层、应力释放层、有源层、低温p型层、电子阻挡层、p型氮化物层。目前低温p型层厚度30

‑

40nm,厚度较厚,吸光严重,降低led外量子效率。通过应力释放层开v

‑

pits至低温p型层,因v

‑

pits开口较大,沿pits空穴注入效率低,影响led发光效率。结合上述叙述,本发明在此基础上提供了一种氮化物发光二极管外延片及其制备方法。

技术实现要素:

5.本发明的目的是提供一种氮化物发光二极管外延片及其制备方法,改善了现有技术中低温p层空穴注入效率低、厚度较厚,吸光严重,外量子效率低等问题,并且通过应力释放层搭配薄低温p层,减小v

‑

pits密度及大小,增强空穴注入效率,提升高光效发光效率。

6.本发明采用以下技术方案解决上述技术问题的:

7.一种氮化物发光二极管外延片,包括衬底,以及依次层叠在衬底上的缓冲层、非故意掺杂gan层、n型gan层、应力释放层、多层量子阱层、低温p型层、电子阻挡层、高温p型层和p型接触层;所述所述应力释放层为gan/in

x

ga1‑

x

n,0.1≤x≤0.6;所述低温p型层为掺mg的al

x

in

y

ga1‑

x

‑

y

n,0.01≤x≤0.1,0≤y≤0.02。

8.进一步地,所述衬底包括蓝宝石衬底、硅衬底、碳化硅衬底、氮化镓衬底、氧化锌衬底中的一种。

9.进一步地,所述应力释放层in组分浓度沿外延层方向逐渐升高。

10.进一步地,所述应力释放层厚度为30nm~60nm,厚度比10≤th

gan

/th

inxga1

‑

xn

≤30。

11.进一步地,所述应力释放层叠层数为2~6个。

12.进一步地,所述低温p型层中al组分浓度随外延层生长方向逐渐降低,in组分浓度沿外延层方向逐渐降低。

13.进一步地,所述低温p层厚度为15

‑

25nm,其中mg掺杂浓度为5e19~5e20cm

‑3。

14.进一步地,所述应力释放层生长温度800~950℃。

15.进一步地,所述低温p型层生长温度为700~850℃。

16.这种氮化物发光二极管外延片的制备方法,步骤包括:

17.(1)提供一衬底;

18.(2)在所述衬底上依次沉积缓冲层,非故意掺杂的gan层,n型gan层,应力释放层,多层量子阱层,低温p型层,电子阻挡层,高温p型层和p型接触层;所述应力释放层in组分浓度沿外延层方向逐渐升高,所述低温p型层为alingan结构,所述al组分浓度随外延层生长方向逐渐降低,in组分浓度沿外延层方向逐渐增加。

19.本发明的有益效果在于:

20.通过减薄低温p型层厚度,提高了p层出光效率。低温p型层材料为al

x

in

y

ga1‑

x

‑

y

n,其中al组分沿外延层生长方向逐渐减少,al组分的势垒较高,可以阻挡电子跃迁至p层与空穴发生非辐射复合,减少电子在p层与空穴发生非辐射复合影响led的发光效率。

21.低温p型层为重掺mg结构,主要给led发光提供空穴,当mg掺杂浓度过高易形成mg

‑

h络合物,而in组分能够促进mg的活化,激发出更多的空穴与电子复合,提高led的发光效率。其中al组分沿外延层生长方向逐渐减少,in组分浓度沿外延层生长方向逐渐增加,整体低温p形成势垒高度沿外延层生长方向逐渐降低,更好的阻挡了电子跃迁至p层,促进空穴更好的注入到量子阱中与电子复合。

22.另外,在低温p型层通入in组分,因为in组分能够促进mg的活化,激发出更多的空穴与电子复合;另外in组分浓度沿外延层生长方向逐渐增加,促进空穴更好的注入到量子阱与电子复合,提升了led的内量子效率。

23.v

‑

pits开口大小与低温p型层厚度也有较大关系,低温p型层厚度减薄,v

‑

pits减小,搭配高mg浓度调整,droop下降,在小电流密度下提升高光效发光效率,gan生长时掺入少量的in,可起到表面活性剂的作用,因此在调整应力释放层的in组分浓度,增强了gan生长时的表面迁移能力,使v

‑

pits变小;同时应力释放层的厚度、结晶质量对v

‑

pits数量、密度有很大的影响,综上,应力释放层搭配低层p型层调整,可以有效提高led在小电流密度的发光效率。本技术提供的外延片的制备方法制备得到的外延片相对于目前量产制备得到的外延片在120ma/60ma电流下测试,亮度能够提升1%~1.5%。

附图说明

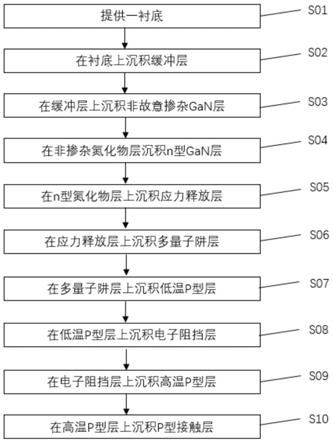

24.图1为本发明实施例中氮化物发光二极管外延片的制备流程图;

25.图2为本发明实施例中氮化物发光二极管的结构示意图。

26.附图说明:

27.1:衬底、2:缓冲层、3:非故意掺杂gan层、4:n型gan层、5:应力释放层、6:多层量子阱层、7:低温p型层、8:电子阻挡层、9:高温p型层、10:p型接触层。

具体实施方式

28.下面结合具体实施方式和附图对本发明做进一步说明,以下实施例旨在说明本发明而不是对本发明的进一步限定。

29.如图1所示,本发明一种氮化物发光二极管外延片,包括衬底1,以及依次沉积在上

述衬底1上的缓冲层2,非故意掺杂的gan层3,n型gan层4,应力释放层5,多层量子阱层6,低温p型层7,电子阻挡层8,高温p型层9和p型接触层10;

30.其中应力释放层应力释放层厚度为30nm~60nm,厚度比10≤th

gan

/th

inxga1

‑

xn

≤30,生长温度为800~950℃,应力释放层in

x

ga1‑

x

nin浓度沿外延层方向逐渐升高,即随周期数增加逐渐增加。

31.其中,低温p型层为掺mg的al

x

in

y

ga1‑

x

‑

y

n,0.01≤x≤0.1,0≤y≤0.02,低温p型层厚度为15

‑

25nm,生长温度为700~850℃,mg掺杂浓度为5e19~5e20cm

‑3,al组分沿外延层生长方向逐渐降低,in组分浓度随外延层逐渐增加。

32.在本实施例中,缓冲层2可为aln缓冲层。设置在缓冲层2上可为非故意掺杂的gan层3,生长温度为1000~1200℃,其厚度可为0.5~5μm,n型半导体层4可为n型gan层,生长温度为1000~1200℃,si掺杂浓度为1e19~2e19,其厚度可为1.5~5.5μm。

33.可选地,应力释放层所述应力释放层5为gan/in

x

ga1‑

x

n,0.1≤x≤0.6,in浓度随循环数增加逐渐增加。

34.可选地,所述应力释放层厚度为30nm~60nm,生长温度为800~950℃,厚度比10≤th

gan

/th

inxga1

‑

xn

≤30,0.1≤x≤0.6,释放层叠层数为2~6个。

35.优选地,应力释放层厚度为50nm,生长温度为850~900℃,th

gan

/th

inxga1

‑

xn

为25,循环数为3个,in

x

ga1‑

x

n,应力释放层loop数in含量为0.2,0.3,0.4。

36.可选地,多层量子阱发光层6由ingan量子阱层和algan量子垒层交替堆叠而形成,其周期厚度为8~20nm,生长温度为750~950℃,周期数为6~12,

37.可选地,低温p型层7为al

x

in

y

ga1‑

x

‑

y

n,低温p型层生长厚度为15~25nm,生长温度为700~850℃,因为低温p型厚度较厚会吸光,降低led的发光效率。

38.可选地,低温p型层mg的浓度为mg掺杂浓度为5e19~5e20cm

‑3,较高的mg掺杂浓度保证提供足够的空穴。

39.进一步地,低温p型层生长al组分由0.1渐变至0.01,in组分由0渐变至0.02,al组分和in组分的这种变化可以阻挡了电子跃迁至p层空穴发生非辐射复合,同时可以促进空穴更好的注入到量子阱中与电子复合,提高发光效率。

40.可选地,电子阻挡层为7为alingan,生长温度为900~1000℃,厚度10~50nm,高温p型层9为掺mggan,生长温度为900~1000℃,厚度5~20nm,mg掺杂浓度为1e19~5e19cm

‑3,p型接触层10为高掺mggan,厚度为1~5nm,mg掺杂浓度为1e20~5e21cm

‑3。

41.图2为本发明实施例提供的一种氮化物发光二极管外延片的制备流程图,如图1所示,制备方法包括:

42.步骤s01,提供一衬底,

43.在本实例中,衬底可选用蓝宝石衬底;

44.在其他实施例中衬底可选用硅衬底、碳化硅衬底、氮化镓衬底、氧化锌衬底中的一种。

45.步骤s02,在衬底上沉积厚度为10~30nm的aln缓冲层。

46.本实例实施中,aln层厚度为15nm。

47.步骤s03,在缓冲层上沉积非故意掺杂gan层。

48.在本实施例中,非故意掺杂的gan层生长温度为1060℃,厚度为2um。

49.步骤s04,在非故意掺杂gan层沉积n型gan层,生长温度为1100℃,厚度为2um,si掺杂浓度为1.6e19。

50.步骤s05,在n型gan层上沉积应力释放层。

51.在本实施例中,应力释放层包括3个交替生长的ingan阱层和gan垒层,其中ingan阱层厚度为2nm,其中in组分浓度沿外延层分布依次0.2,0.3,0.4,gan垒层厚度为50nm,生长温度800~950℃。

52.步骤s06,在应力释放层上沉积多量子阱层。

53.具体地,多层量子阱发光层为交替堆叠的ingan量子阱层和algan量子垒层,其中ingan量子阱层生长温度为790~810℃,厚度为2~3.5nm,algan量子垒层生长温度为850~880℃,厚度为9~12nm,al组分为0.1。

54.步骤s07,在多量子阱层上沉积低温p型层。

55.具体地,低温p型层生长温度700~800℃,压力100~600torr,mg掺杂浓度为1.9e20。

56.具体地,低温p型层厚度为18~20nm。

57.具体地,生长低温p型层时,控制al组分浓度沿外延层生长方向0.1渐变至0.01,in组分浓度沿外延层方向由0渐变至0.02。

58.步骤s08,在低温p型层上沉积电子阻挡层。

59.具体地,电子阻挡层为alingan厚度25~40nm,生长温度900

‑

1000℃。

60.步骤s09,在电子阻挡层上沉积高温p型层。

61.具体地,高温p型层为掺mg gan层,厚度为5

‑

10nm,mg浓度为1e20,生长温度900~100℃.

62.步骤s10,在高温p型层上沉积p型接触层。

63.具体地,p型接触层为掺mg gan层,厚度为1~5nm,mg浓度为5e20,生长温度700~800℃。

64.将a样品和b样品使用相同芯片工艺条件制备成10mil*24mil芯片,其中a样品为目前量产制备得到的外延片,b样品为本方案制备得到的外延片,两个样品分别抽取300颗led芯片,在120ma/60ma电流下测试,亮度提升1%~1.5%。

65.本发明实施例对应力释放层的in浓度控制,及低温p型层减薄并改为重掺杂mg的al

x

in

y

ga1‑

x

‑

y

n,可以有效控制v

‑

pits大小及密度,提高led发光效率。

66.最后应说明的是:以上实施例仅用以说明本发明而并非限制本发明所描述的技术方案;本领域的普通技术人员应当理解,仍然可以对本发明进行修改或等同替换;而一切不脱离本发明的精神和范围的技术方案及其改进,其均应涵盖在本发明的权利要求范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1