功率元件及其制造方法与流程

1.本发明涉及一种功率元件及其制造方法,特别涉及一种具有场氧化区与自动对准漂移区的功率元件及其制造方法。

背景技术:

2.图1a及图1b分别显示一种已知功率元件100的俯视示意图与剖视示意图。图1b显示图1a的aa’剖线的剖视示意图。所谓的功率元件,是指于正常操作时,施加于漏极的电压高于5v。一般而言,功率元件的漏极与栅极间,具有漂移区12a(如图1b中虚线框范围所示意),将漏极19与本体区16分隔,且漂移区12a的横向长度根据正常操作时所承受的操作电压而调整。如图1a与图1b所示,功率元件100包含:阱区12、绝缘结构13、本体区16、栅极17、源极18与漏极19。其中,阱区12的导电型为n型,形成于基板11上,绝缘结构13为区域氧化(local oxidation of silicon,locos)结构,以定义操作区13a,作为功率元件100操作时主要的作用区。操作区13a的范围由图1a中,粗黑虚线框所示意。为提高功率元件100的击穿电压,可延长漂移区12a在通道方向上的长度,但会使导通电阻提高,使得操作速度降低;此外,漂移区12a与漏极19的n型杂质浓度差异较大,且分别耦接的电压的电压差超过5v至数百伏的高压,限制了功率元件100的击穿电压,而限制了功率元件100的应用范围,降低元件的性能。

3.有鉴于此,本发明提出一种能够提高不导通操作时的击穿电压使功率元件100的耐压(withstand voltage)提高,并降低导通电阻的功率元件及其制造方法。

技术实现要素:

4.于一观点中,本发明提供一种功率元件,包含:一半导体层,形成于一基板上,该半导体层具有一上表面;一阱区,具有一第一导电型,形成于该半导体层中,且该阱区位于该上表面下并连接于该上表面;一本体区,具有一第二导电型,形成于该半导体层中,且该本体区位于该上表面下并连接于该上表面,该本体区于一通道方向上,与该阱区邻接;一栅极,形成于该上表面上,部分该本体区位于该栅极正下方并连接于该栅极,以提供该功率元件在一导通操作中的一反转电流通道,且部分该阱区位于该栅极正下方,以提供该功率元件在该导通操作中的一漂移电流通道;一源极与一漏极,具有该第一导电型,且该源极与该漏极形成于该上表面下并连接于该上表面,且该源极与该漏极分别位于该栅极的外部下方的该本体区中与远离该本体区侧的该阱区中;一场氧化区,形成于该上表面上,且该场氧化区介于该栅极与该漏极之间,且该场氧化区由一化学机械研磨(chemical mechanical polish,cmp)工艺步骤形成;以及一自动对准漂移区,具有该第一导电型,形成于该半导体层中,且该自动对准漂移区完全位于并连接于该场氧化区正下方。

5.于另一观点中,本发明提供一种功率元件制造方法包含:形成一半导体层于一基板上,该半导体层具有一上表面;形成一阱区于该半导体层中,且该阱区具有第一导电型,且该阱区位于该上表面下并连接于该上表面;形成一本体区于该半导体层中,且该本体区

具有一第二导电型,且该本体区位于该上表面下并连接于该上表面,该本体区于一通道方向上,与该阱区邻接;形成一栅极于该上表面上,部分该本体区位于该栅极正下方并连接于该栅极,以提供该功率元件在一导通操作中的一反转电流通道,且部分该阱区位于该栅极正下方,以提供该功率元件在该导通操作中的一漂移电流通道;形成一源极与一漏极于该上表面下并连接于该上表面,且该源极与该漏极具有该第一导电型,且该源极与该漏极分别位于该栅极的外部下方的该本体区中与远离该本体区侧的该阱区中;以一化学机械研磨(chemical mechanical polish,cmp)工艺步骤形成一场氧化区于该上表面上,且该场氧化区介于该栅极与该漏极之间;以及形成一自动对准漂移区于该半导体层中,该自动对准漂移区具有该第一导电型,且该自动对准漂移区完全位于并连接于该场氧化区正下方。

6.于一实施例中,该功率元件还包含一场极板,具有导电性,且该场极板形成于该场氧化区上且连接于该场氧化区,该场极板用以电连接于一预设电位,以缓和该功率元件操作时的电场分布。

7.于一实施例中,该自动对准漂移区的第一导电型杂质浓度低于该漏极的第一导电型杂质浓度,且该自动对准漂移区的第一导电型杂质浓度高于该阱区的第一导电型杂质浓度。

8.于一实施例中,该自动对准漂移区与该场氧化区由同一个微影工艺步骤所定义。

9.于一实施例中,该场极板电连接于该源极。

10.于一实施例中,该功率元件制造方法,还包含:以一微影工艺步骤形成一屏蔽于该上表面上且连接于该上表面,且该屏蔽定义该场氧化区与该自动对准漂移区;以一离子注入工艺步骤,将该第一导电型杂质,以加速离子的形式,注入该屏蔽所定义的区域中,以形成该自动对准漂移区;以一沉积工艺步骤,沉积一氧化层,且该cmp工艺步骤将该屏蔽所定义的区域之外的该氧化层移除;以及移除该屏蔽。

11.本发明的优点为本发明通过屏蔽覆盖整个低压区域并只暴露高压区域的上表面可保护低压区域,通过屏蔽可防止绝缘结构被蚀刻,仅用单一屏蔽就可同时形成自动对准漂移区及场氧化区,通过cmp工艺步骤取代加热工艺步骤可减少加热工艺对低压区域的影响,且通过自动对准漂移区可使高压区域具有渐进式的第一导电形杂质浓度。

12.以下通过具体实施例详加说明,会更容易了解本发明的目的、技术内容、特点及其所实现的效果。

附图说明

13.图1a与图1b分别显示一种已知功率元件的俯视示意图与剖视示意图。

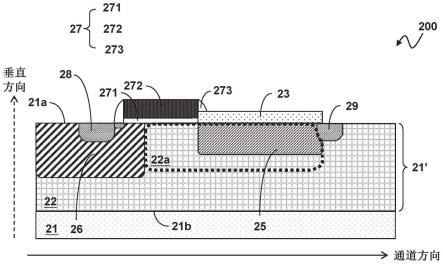

14.图2a与图2b是分别根据本发明的一实施例显示功率元件的俯视示意图与剖视示意图。

15.图3a与图3b是分别根据本发明的另一实施例显示功率元件的俯视示意图与剖视示意图。

16.图4a-图4l是根据本发明的一实施例显示功率元件制造方法的剖视示意图。

17.图中符号说明

18.11,21,31:基板

19.12,22,32:阱区

20.12a,22a,32a:漂移区

21.13:绝缘结构

22.13a:操作区

23.16,26,36:本体区

24.17,27,37:栅极

25.18,28,38:源极

26.19,29,39:漏极

27.21’,31’:半导体层

28.21a,31a:上表面

29.21b,31b:下表面

30.23,33:场氧化区

31.25,35:自动对准漂移区

32.33’:氧化层

33.34:屏蔽

34.34’:屏蔽材料

35.36’,38’:光阻层

36.37’:场极板

37.100,200,300:功率元件

38.271,371,371’:介电层

39.272,372,372’:导电层

40.273,373,373’:间隔层

具体实施方式

41.涉及本发明的前述及其他技术内容、特点与效果,在以下配合参考附图的较佳实施例的详细说明中,将可清楚地呈现。本发明中的附图均属示意,主要意在表示工艺步骤以及各层之间的上下次序关系,至于形状、厚度与宽度则并未依照比例绘制。

42.请参考图2a与图2b,其是分别根据本发明的一实施例显示功率元件200的俯视示意图与剖视示意图。图2b显示图2a的bb’剖线的剖视示意图。如图2a与图2b所示,功率元件200包含:半导体层21’、阱区22、场氧化区23、自动对准漂移区25、本体区26、栅极27、源极28以及漏极29。半导体层21’形成于基板21上;阱区22、自动对准漂移区25、源极28与漏极29具有第一导电型;本体区26具有第二导电型。功率元件200例如为如图2a与图2b所示的横向双扩散金属氧化物半导体场效晶体管(lateral double-diffused metal oxide semiconductor field effect transistor,ldmos)元件。根据本发明的功率元件例如应用于切换式电源供应电路中的功率级电路中,切换式电源供应电路为本领域技术人员所熟知,在此不予赘述。

43.半导体层21’形成于基板21上,半导体层21’于垂直方向(如图2b中的虚线箭头方向所示意,下同)上,具有相对的上表面21a与下表面21b。基板21例如但不限于为一p型或n型的半导体硅基板。半导体层21’例如以外延的步骤,形成于基板21上,或是以基板21的部分,作为半导体层21’。形成半导体层21’的方式,为本领域技术人员所熟知,在此不予赘述。

44.请继续参阅图2a与图2b,阱区22具有第一导电型,形成于半导体层21’中,且阱区22位于上表面21a下并连接于上表面21a。本体区26具有第二导电型,形成于半导体层22中,且本体区26位于上表面21a下并连接于上表面21a,本体区26于通道方向(如图2b中的实线箭头方向所示意,下同)上,与阱区22邻接。栅极27形成于上表面21a上,部分本体区26位于栅极27正下方并连接于栅极27,以提供功率元件200在导通操作中的反转电流通道,且部分阱区22位于栅极27正下方,以提供功率元件200在导通操作中的漂移电流通道(如图2b中粗虚线框所示意)。源极28与漏极29具有第一导电型,且源极28与漏极29形成于上表面21a下并连接于上表面21a,且源极28与漏极29分别位于栅极27的外部下方的本体区26中与远离本体区26侧的阱区22中。

45.场氧化区23形成于上表面21a上,且场氧化区23介于栅极27与漏极29之间。于一实施例中,场氧化区23由化学机械研磨(chemical mechanical polish,cmp)工艺步骤形成。自动对准漂移区25具有第一导电型,且形成于半导体层21’中。自动对准漂移区25完全位于并连接于场氧化区23正下方。

46.自动对准漂移区25与场氧化区23由利用同一个光罩于同一个微影工艺步骤定义。于一实施例中,自动对准漂移区25的第一导电型杂质浓度低于漏极29的第一导电型杂质浓度,且自动对准漂移区25的第一导电型杂质浓度高于阱区22的第一导电型杂质浓度。

47.栅极27包括与上表面21a连接的介电层271、具有导电性的导电层272以及具有电绝缘特性的间隔层273。栅极27用以接受控制信号控制而导通及不导通功率元件200。

48.请继续参阅图2b,于通道方向上,漂移区22a位于漏极29与本体区26之间,并分隔漏极29与本体区26,且位于靠近上表面21a的阱区22中,用以作为功率元件200在导通操作中的漂移电流通道。

49.需说明的是,所谓反转电流通道是指功率元件200在导通操作中因施加于栅极27的电压,而使栅极27的下方形成反转层(inversion layer)以使导通电流通过的区域,此为本领域技术人员所熟知,在此不予赘述。

50.需说明的是,所谓漂移电流通道是指功率元件200在导通操作中使导通电流以漂移的方式通过的区域,此为本领域技术人员所熟知,在此不予赘述。

51.需说明的是,上表面21a并非指一完全平坦的平面,而是指半导体层21’的一个表面。

52.需说明的是,前述的“第一导电型”与“第二导电型”是指于功率元件中,以不同导电型的杂质掺杂于半导体组成区域(例如但不限于前述的阱区、本体区、源极与漏极等区域)内,使得半导体组成区域成为第一或第二导电型(例如但不限于第一导电型为n型,而第二导电型为p型,或反之亦可),其中,第一导电型与第二导电型为彼此电性相反的导电型。

53.此外需说明的是,所谓的功率元件,是指于正常操作时,施加于漏极的电压高于一特定的电压,例如5v,且本体区26与漏极29的横向距离(漂移区长度)根据正常操作时所承受的操作电压而调整,因而可操作于前述较高的特定电压。此都为本领域技术人员所熟知,在此不予赘述。

54.请参考图3a与图3b,其是分别根据本发明的另一实施例显示功率元件300的俯视示意图与剖视示意图。图3b显示图3a的cc’剖线的剖视示意图。如图3a与图3b所示,功率元件300包含:半导体层31’、阱区32、场氧化区33、自动对准漂移区35、本体区36、栅极37、场极

板(field plate)37’、源极38以及漏极39。阱区32、自动对准漂移区35、源极38与漏极39具有第一导电型;本体区36具有第二导电型。

55.请继续参阅图3a与图3b,本实施例与图2b的实施例不同之处在于,本实施例的功率元件300包括场极板37’,其具有导电性,且场极板37’形成于场氧化区33上且连接于场氧化区33。场极板37’用以电连接于预设电位,以缓和功率元件300操作时的电场分布。在一种较佳的实施例中,场极板37’电连接于源极38。于一实施例中,场极板37’可利用与栅极37相同的工艺步骤形成。于此实施例中,如图3b所示,场极板37’包括与上表面31a连接的介电层371’、具有导电性的导电层372’以及具有电绝缘特性的间隔层373’。于另一实施例中,场极板37’也可以为利用其他硅化金属工艺步骤或金属工艺步骤形成的硅化金属层或金属层。

56.请参考图4a-图4l,其是根据本发明的一实施例显示功率元件制造方法的剖视示意图。如图4a所示,首先提供基板31,基板31例如但不限于为一p型或n型的半导体硅基板。接着,如图4b所示,形成半导体层31’于基板31上,半导体层31’于垂直方向(如图4b中的虚线箭头方向所示意,下同)上,具有相对的上表面31a与下表面31b。半导体层31’例如以外延的步骤,形成于基板31上,或是以基板31的部分,作为半导体层31’。形成半导体层31’的方式,为本领域技术人员所熟知,在此不予赘述。

57.请继续参阅图4b,接着,形成阱区32于半导体层31’中,且于垂直方向上,阱区32位于上表面31a下并连接于上表面31a。阱区32具有第一导电型,例如可利用例如但不限于离子注入工艺步骤,将第一导电型杂质,以加速离子的形式,如图4b中向下的虚线箭头所示意,注入半导体层31’中,以形成阱区32。

58.接着,请参阅图4c,形成本体区36于半导体层31’中,且本体区36位于上表面31a下并连接于上表面31a,本体区36于通道方向(如图4c中的实线箭头方向所示意,下同)上,与阱区32邻接。部分本体区36位于后续形成的栅极37正下方并连接于栅极37,以提供功率元件300在导通操作中的反转电流通道。本体区36具有第二导电型,形成本体区36的步骤,例如但不限于利用由微影工艺步骤形成光阻层36’为屏蔽,将第二导电型杂质掺杂至半导体层31’的阱区32中,将定义的部分从阱区32反掺杂(counter dope)而形成本体区36。其中,本实施例可利用例如但不限于离子注入工艺步骤,将第二导电型杂质,以加速离子的形式,注入部分阱区32中,以形成本体区36。

59.接着,请参阅图4d,利用例如沉积工艺步骤形成屏蔽材料34’于半导体层31’的上表面31a上,以覆盖整个上表面31a。于一实施例中,屏蔽材料34’例如但不限于氮化硅(sin)。接续,请参照图4e,利用例如微影工艺步骤形成光阻层38’于屏蔽材料34’之上。接着,请参阅图4f,利用例如蚀刻工艺步骤移除未被光阻层38’覆盖住的部分屏蔽材料34’,使得剩余的屏蔽材料得以作为屏蔽34。屏蔽34形成于上表面31a上且连接于上表面31a,且屏蔽34定义了场氧化区33与自动对准漂移区35。应注意者为,屏蔽34覆盖整个低压区域的上表面31a,只有在高压区域才会如图4f暴露出上表面31a。

60.之后,请参照图4g,形成自动对准漂移区35于半导体层31’中。自动对准漂移区35完全位于并连接于后续形成的场氧化区33正下方。自动对准漂移区35具有第一导电型,例如可利用例如但不限于离子注入工艺步骤,将第一导电型杂质,以加速离子的形式,如图4g中向下的虚线箭头所示意,注入屏蔽34所定义的区域中,以形成自动对准漂移区35。于一实施例中,自动对准漂移区35的第一导电型杂质浓度低于漏极39的第一导电型杂质浓度,且

自动对准漂移区35的第一导电型杂质浓度高于阱区32的第一导电型杂质浓度。

61.接续,请参照图4h,移除光阻层38’后,并利用例如沉积工艺步骤形成氧化层33’于屏蔽34之上。

62.接着,请参照图4i,以cmp工艺步骤将屏蔽34所定义的区域之外的氧化层33’移除,以形成场氧化区33于上表面31a上。场氧化区33介于后续形成的栅极37与漏极39之间。

63.之后,请参照图4j,移除屏蔽34。接着,请参照图4k,形成栅极37于半导体层31’的上表面31a上,且形成场极板37’于场氧化区33上。其中,部分本体区36位于栅极37正下方并连接于栅极37,以提供功率元件300在导通操作中的反转电流通道。部分阱区32位于栅极37正下方,以提供功率元件300在导通操作中的漂移电流通道。场极板37’连接于场氧化区33,且场极板37’具有导电性。场极板37’用以电连接于预设电位,以缓和功率元件300操作时的电场分布。场极板37’电连接于后续形成的源极38。

64.于本实施例中,场极板37’可利用与栅极37相同的工艺步骤同时形成。于此实施例中,如图4k所示,场极板37’包括与上表面31a连接的介电层371’、具有导电性的导电层372’以及具有电绝缘特性的间隔层373’。于另一实施例中,场极板37’也可为利用其他硅化金属工艺步骤或金属工艺步骤形成的硅化金属层或金属层。

65.如图4k所示,栅极37包括与上表面31a连接的介电层371、具有导电性的导电层372以及具有电绝缘特性的间隔层373。栅极37用以接受控制信号控制而导通及不导通功率元件300。

66.请继续参阅图4l,形成源极38与漏极39于上表面31a下并连接于上表面31a,且源极38与漏极39分别位于栅极37在通道方向的外部下方的本体区36中与远离本体区36侧的阱区32中,且于通道方向上,漂移区32a位于漏极39与本体区36之间,靠近上表面31a的阱区32中,用以作为功率元件300在导通操作中的漂移电流通道。形成源极38与漏极39的步骤,例如但不限于利用栅极37、场极板37’、场氧化区33以及由微影工艺步骤形成光阻层为屏蔽,将第一导电型杂质分别掺杂至本体区36中与阱区32中,以形成源极38与漏极39。其中,本实施例可利用例如但不限于离子注入工艺步骤,将第一导电型杂质,以加速离子的形式,注入本体区36中与阱区32中,以形成源极38与漏极39。

67.如上所述,本发明提供了一种具有场氧化区33与自动对准漂移区35的功率元件300及其制造方法,其通过屏蔽覆盖整个低压区域并只暴露高压区域的上表面可保护低压区域,通过屏蔽可防止绝缘结构被蚀刻,仅用单一屏蔽就可同时形成自动对准漂移区及场氧化区,通过cmp工艺步骤取代加热工艺步骤可减少加热工艺对低压区域的影响,且通过自动对准漂移区可使高压区域具有渐进式的第一导电形杂质浓度。

68.以上已针对较佳实施例来说明本发明,但以上所述,仅为使本领域技术人员易于了解本发明的内容,并非用来限定本发明的权利范围。在本发明的相同精神下,本领域技术人员可以想到各种等效变化。例如,在不影响元件主要的特性下,可加入其他工艺步骤或结构,如硅化金属层等;又如,微影技术并不限于光罩技术,也可包含电子束微影技术。凡此种种,都可根据本发明的教示类推而得。此外,所说明的各个实施例,并不限于单独应用,也可以组合应用,例如但不限于将两实施例并用。因此,本发明的范围应涵盖上述及其他所有等效变化。此外,本发明的任一实施型态不必须达成所有的目的或优点,因此,权利要求的任一项也不应以此为限。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1