半导体封装结构及其制造方法与流程

1.本公开涉及半导体技术领域,具体涉及半导体封装结构及其制造方法。

背景技术:

2.引线键合(wire bonding)封装技术是将芯片设于重布线结构上,再以导线将芯片和重布线结构上的焊盘(pad)相连接,但由多层重布线堆叠而形成的重布线结构因非平整表面而造成打线力道失衡,并且重布线结构中的有机材料刚性低,打线力道容易被有机材料吸收,因此造成引线键合的焊点与焊盘接合不良的情况,影响电性连接的效果。

技术实现要素:

3.本公开提供了半导体封装结构及其制造方法。

4.第一方面,本公开提供了一种半导体封装结构,该半导体封装结构包括:重布线结构,包括键合衬垫,所述键合衬垫的底表面与所述重布线结构的介电层的底表面共平面;芯片,设于所述重布线结构上,并通过导线与所述键合衬垫电连接。

5.在一些可选的实施方式中,所述重布线结构为多层重布线结构;所述键合衬垫为所述多层重布线结构中最下层的重布线层。

6.在一些可选的实施方式中,所述重布线结构具有一开孔,所述开孔暴露出所述键合衬垫。

7.在一些可选的实施方式中,所述开孔的侧壁平滑。

8.在一些可选的实施方式中,所述开孔的底部沿周向设有环形槽。

9.在一些可选的实施方式中,所述开孔的侧壁包括至少两个曲面。

10.第二方面,本公开提供了一种半导体封装结构,该半导体封装结构包括:支撑体;

11.重布线结构,包括键合衬垫,所述键合衬垫设于所述支撑体上,并与所述支撑体电连接;

12.芯片,设于所述重布线结构上,并通过导线与所述键合衬垫电连接,所述导线与所述键合衬垫之间的接合面位于所述支撑体投影至所述键合衬垫的范围内。

13.在一些可选的实施方式中,所述支撑体为至少两个;所述接合面位于至少两个所述支撑体投影至所述键合衬垫所环绕的投影范围内。

14.在一些可选的实施方式中,所述支撑体为导电柱。

15.第三方面,本公开提供了一种半导体封装结构的制造方法,该方法包括:提供载体;在所述载体上形成包括键合衬垫的重布线结构;在所述重布线结构上设置开孔,所述开孔暴露出所述键合衬垫;在重布线结构上放置芯片;通过导线连接所述芯片与所述键合衬垫。

16.在一些可选的实施方式中,以激光工艺形成所述开孔。

17.在一些可选的实施方式中,以等离子处理工艺形成所述开孔。

18.第四方面,本公开提供了一种半导体封装结构的制造方法,该方法包括:

19.提供载体;

20.在所述载体上形成支撑体;

21.在支撑体上形成包括键合衬垫的重布线结构;

22.在重布线结构上放置芯片;

23.通过导线连接所述芯片与所述键合衬垫。

24.在一些可选的实施方式中,所述通过导线连接所述芯片与所述键合衬垫,包括:

25.导线的打线位置在所述支撑体投影至所述键合衬垫的范围内。

26.在一些可选的实施方式中,所述在所述载体上形成支撑体,包括:

27.在所述载体上形成至少两个支撑体;以及

28.所述通过导线连接所述芯片与所述键合衬垫,包括:

29.导线的打线位置在至少两个所述支撑体投影至所述键合衬垫所环绕的投影范围内。

30.为了解决现有技术中重布线结构因非平整表面而造成打线力道失衡、打线力道容易被有机材料吸收所造成的引线键合的焊点与焊盘接合不良的问题,本公开提供的半导体封装结构及其制造方法,引线键合直接焊在重布线结构中最下层的重布线层,不会受到有机材料的影响,或者引线键合焊在具有支撑结构的焊盘上,支撑结构可以增加结构强度,以达到提升承受打线力道的效果。

附图说明

31.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本公开的其它特征、目的和优点将会变得更明显:

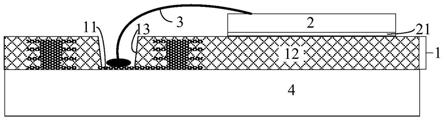

32.图1到图4是根据本公开的半导体封装结构的第一结构示意图至第四结构示意图;

33.图5到图9是根据本公开的半导体封装结构的第一制造过程中的结构示意图;

34.图10到图14是根据本公开的半导体封装结构的第二制造过程中的结构示意图。

35.符号说明:

[0036]1‑

重布线结构,11

‑

键合衬垫,12

‑

介电层,13

‑

开孔,2

‑

芯片,3

‑

导线,31

‑

打线位置,4

‑

载体,5

‑

支撑体。

具体实施方式

[0037]

下面结合附图和实施例对说明本公开的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本公开所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外,为了便于描述,附图中仅示出了与有关发明相关的部分。

[0038]

需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本公开可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本公开所能产生的功效及所能达成的目的下,均应仍落在本公开所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述的明了,而非用以限定本公开可实施的范围,其相对关系的改变或调整,在无实质变更技术

内容下,应当也视为本公开可实施的范畴。

[0039]

另外,在不冲突的情况下,本公开中的实施例及实施例中的特征可以相互组合。下面将参考图1到图4并结合实施例来详细说明本公开。

[0040]

图1到图4是是根据本公开的半导体封装结构的第一结构示意图至第四结构示意图。

[0041]

图1示出了本公开的半导体封装结构的第一结构示意图。如图1所示的半导体封装结构包括重布线结构1和芯片2。其中,重布线结构1可以包括键合衬垫11,键合衬垫11的底表面与重布线结构1的介电层12的底表面共平面。芯片2可以设于重布线结构1上。芯片2可以通过导线3与键合衬垫11电连接。

[0042]

在本实施例中,重布线结构1可以包括介电材料和导电材料,介电材料可包括有机物和/或无机物,其中有机物例如可以是:聚酰胺纤维(polyamide,pa)、聚酰亚胺(polyimide,pi)、环氧树脂(epoxy)、聚对苯撑苯并二噁唑(poly

‑

p

‑

phenylene benzobisoxazole,pbo)纤维、fr

‑

4环氧玻璃布层压板、pp(prepreg,预浸材料或称为半固化树脂、半固化片)、abf(ajinomoto build

‑

up film)等,而无机物例如可以是硅(si),玻璃(glass),陶瓷(ceramic),氧化硅,氮化硅,氧化钽等。导电材料可包括种子层和金属层。这里,种子层例如可以是钛(ti),钨(w),镍(ni)等,而金属层例如可以是金(au)、银(ag)、铝(al)、镍(ni)、钯(pd)、铜(cu)或其合金。

[0043]

在本实施例中,重布线结构1可以是多层重布线结构1。键合衬垫11可以是多层重布线结构1中最下层的重布线层。重布线结构1可以具有一开孔13。开孔13可以暴露出键合衬垫11。开孔13的侧壁平滑。

[0044]

芯片2可以是各种功能的芯片,例如可以为逻辑芯片、存储芯片、微机电系统(mems,micro

‑

electro

‑

mechanical system)芯片、射频芯片、电源管理集成电路(pmic,power management ic)芯片等。芯片2可以通过粘合层粘合至重布线结构1上,粘合层例如可以是裸片附接薄膜(die attaching film,daf)。

[0045]

图1所示的半导体封装结构,引线键合直接焊在重布线结构1中最下层的重布线层,不会受到有机材料的影响。并且可以将载体4作为键合衬垫11的支撑结构,以达到均匀支撑的功能。

[0046]

图2示出了本公开的半导体封装结构的第二结构示意图。如图2所示的半导体封装结构中的开孔13的底部沿周向设有环形槽,即开孔13的底部与键合衬垫11的交界处沿周向设有环形槽。在制程中,由于采用激光打孔技术,激光反射烧至介电层12表面,出现孔底扩孔现象。

[0047]

图3示出了本公开的半导体封装结构的第三结构示意图。如图3所示的半导体封装结构中的开孔13的侧壁可以包括至少两个曲面。在制程中,由于采用等离子处理技术,经过多次离子轰击而形成由多个曲面形成的开孔13侧壁。

[0048]

图4示出了本公开的半导体封装结构的第四结构示意图。如图4所示的半导体封装结构包括重布线结构1以及芯片2。其中,重布线结构1可以包括支撑体5和键合衬垫11。键合衬垫11可以设于支撑体5上。键合衬垫11可以与支撑体5电连接。芯片2可以设于重布线结构1上。芯片2可以通过导线3与键合衬垫11电连接。导线3与键合衬垫11之间的接合面(导线3接触键合衬垫11的区域)可以位于支撑体5投影至键合衬垫11上表面的范围内,即打线位置

31可以位于支撑体5投影至键合衬垫11上表面的范围内。

[0049]

在本实施例中,支撑体5可以为导电柱,导电柱例如可以采用金(au)、银(ag)、铝(al)、镍(ni)、钯(pd)、铜(cu)或其合金。支撑体5可以为至少两个。导线3与键合衬垫11之间的接合面可以位于至少两个支撑体5投影至键合衬垫11上表面所环绕的投影范围内。具体地,如图4中(a)图所示,支撑体5可以为两个,如图4中(b)图所示,支撑体5可以为三个,如图4中(c)图所示,支撑体5可以为四个。支撑体5可以为焊盘提供支撑力,引线键合焊在具有支撑结构的焊盘上,以达到提升承受打线力道的效果。

[0050]

图5到图9示出了根据本公开的半导体封装结构的第一制造过程中的结构示意图。为了更好地理解本公开的各方面,已简化各图。

[0051]

如图5所示,提供载体4。这里,可以将载体4作为键合衬垫11的支撑结构,以达到均匀支撑的功能。

[0052]

如图6所示,在载体4上形成包括键合衬垫11的第一重布线。在第一重布线层上依次设置多层重布线和介电层12,形成重布线结构1。

[0053]

这里,可以采用物理气相沉积(physical vapor deposition,pvd)、电镀等工艺制备出包括键合衬垫11的第一重布线和其他重布线,采用化学气相沉积(chemical vapor deposition,cvd)或旋涂等工艺等制备出介电层12。

[0054]

如图7所示,在重布线结构1上设置开孔13,以使开孔13暴露出键合衬垫11。

[0055]

这里,可以以激光工艺形成开孔13,形成如图2所示的开孔13。可以以等离子处理工艺形成开孔13,形成如图3所示的开孔13。

[0056]

如图8所示,在重布线结构1上放置芯片2,可以通过粘合层将芯片2粘合至重布线结构1上。

[0057]

如图9所示,通过导线3连接芯片2与键合衬垫11。

[0058]

这里,可以引线键合技术,用导线3将芯片2与键合衬垫11相连接。

[0059]

图10到图14示出了根据本公开的半导体封装结构的第二制造过程中的结构示意图。为了更好地理解本公开的各方面,已简化各图。

[0060]

如图10所示,提供载体4。

[0061]

如图11所示,在载体4上设置支撑体5和介电层12。

[0062]

这里,支撑体5可以为一个或者至少两个。可以采用先形成金属层,然后图案化金属层得到支撑体5,然后形成介电层12,或者先形成介电层12,然后图案化介电层12,在图案化介电层12中形成支撑体5。若支撑体5的上表面不平整,可以通过研磨等工艺使支撑体5的上表面平整,使键合衬垫11形成于平整的表面,支撑体5可以提供均匀支撑,增加键合衬垫11的强度。

[0063]

如图12所示,可以采用物理气相沉积工艺在支撑体5上设置键合衬垫11,形成重布线结构1。

[0064]

如图13所示,在重布线结构1上放置芯片2,可以通过粘合层将芯片2粘合至重布线结构1上。

[0065]

如图14所示,通过导线3连接芯片2与键合衬垫11。

[0066]

这里,可以引线键合技术,用导线3将芯片2与键合衬垫11相连接。

[0067]

这里,导线3的打线位置可以在支撑体5投影至键合衬垫11的范围内。当支撑体5为

至少两个时,导线3的打线位置可以在至少两个支撑体5投影至键合衬垫11所环绕的投影范围内。

[0068]

本公开的提供的制造半导体封装结构的方法能够实现与前述半导体封装结构类似的技术效果,这里不再赘述。

[0069]

尽管已参考本公开的特定实施例描述并说明本公开,但这些描述和说明并不限制本公开。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效组件而不脱离如由所附权利要求书限定的本公开的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本公开中的技术再现与实际实施之间可能存在区别。可存在未特定说明的本公开的其它实施例。应将说明书和图示视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本公开的目标、精神以及范围。所有此些修改都落入此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本文中所公开的方法,但应理解,可在不脱离本公开的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本文中特别指示,否则操作的次序和分组并不限制本公开。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1