芯片裸片、封装体及其制造方法、无线电器件和设备与流程

1.本技术涉及半导体技术领域,尤其涉及一种芯片裸片、封装体及其制造方法、无线电器件和设备。

背景技术:

2.芯片互连线是将芯片上各个电路模块相互连接的结构。芯片工艺中通常包括多层金属互连线,越低层次的互连线支持的最小尺寸越小但损耗越大,越高层次的互连线支持的最小尺寸越大但损耗越小。因此,相距越近或互连线损耗要求越低的模块之间通常采用越低层次的线进行互连,而相距越远或对于互连损耗要求越高的模块之间通常采用高层次的线进行互连。

3.随着芯片上包含的功能模块越来越多,例如soc芯片(system-on-a-chip),其芯片尺寸随之增加,互连的模块之间的间距相应增加,但是对于互连损耗的要求却不会相应降低。因此对于互连线提出了更高的要求。

技术实现要素:

4.本技术提供一种芯片裸片、封装体及其制造方法、无线电器件和设备,在实现器件远距离互连的同时,降低互连损耗。

5.第一方面,本技术提供一种芯片裸片(die),包括:

6.互连介质层,以及形成于所述互连介质层中的至少两个需要互连的电路模块;

7.其中,所述至少两个需要互连的电路模块用于通过所述芯片裸片的封装介质层中的封装走线互连。

8.在本技术实施例中,通过将芯片裸片中需要互连的电路模块之间的连接线设置在芯片裸片之外,以在实现传统芯片裸片内互连效果的同时,还能突破芯片裸片内互连线例如尺寸、厚度、面积等方面的限制,甚至还能进一步提升互连的性能。另外,由于芯片裸片内无需设置传统的互连线,故而可预留出更多的芯片空间和面积,用于集成更多器件及电路模块等,进而提升芯片整体的性能。

9.可选的,还包括:

10.衬底,所述互连介质层形成于所述衬底之上。

11.可选的,所述需要互连的电路模块在所述芯片裸片中相邻设置。

12.可选的,所述电路模块位于所述互连介质层中的底部,所述互连介质层中还形成有多个互连结构;

13.其中,各所述电路模块通过所述互连结构贯穿所述互连介质层的顶部表面,以与对应的所述封装走线连接。

14.可选的,所述互连介质层为复合膜层结构,所述互连结构包括多个子互连结构;

15.其中,各所述子互连结构包括依次贯穿位于所述电路模块上各膜层的通孔和互连线。

16.第二方面,本技术提供一种封装体,包括:

17.包括:第一方面及第一方面任一种可能的设计中的芯片裸片;封装介质层,形成于所述互连介质层之上;

18.其中,所述封装介质层中形成有封装走线,所述需要互连的电路模块通过部分所述封装走线相互连接。

19.可选的,还包括:

20.封装焊球,所述芯片裸片通过所述封装焊球与封装体外的器件连接。

21.可选的,在封装介质层中还形成有天线结构;

22.其中,用于将电路模块互连的封装走线与所述天线结构位于同一膜层中,如aip(antenna-in-package,封装天线)芯片结构。

23.可选的,所述封装体为毫米波雷达芯片(chip)。

24.第三方面,本技术提供一芯片裸片的制造方法,包括:

25.提供芯片衬底;

26.于所述芯片衬底上形成互连介质层,所述互连介质层中制备有至少两个需要互连的电路模块;

27.其中,所述需要互连的电路模块通过用于封装所述芯片裸片的封装介质层中的封装走线互连。

28.第四方面,本技术提供一种封装体的制造方法,包括:

29.提供芯片裸片,所述芯片裸片中设置有至少两个需要互连的电路模块;

30.于所述芯片裸片之上形成封装介质层;

31.其中,所述封装介质层中形成有封装走线,所述需要互连的电路模块通过所述封装走线相互连接。

32.第五方面,本技术提供一种无线电器件,包括:

33.承载体;

34.第二方面及第二方面任一项可能的设计中的封装体,设置在所述承载体上;

35.天线,设置在所述承载体上,或者集成于所述封装体中;

36.其中,所述芯片裸片与所述天线连接,用于发收无线电信号。

37.第六方面,本技术提供一种设备,包括:

38.设备本体;以及

39.设置于所述设备本体上的如第五方面所述的无线电器件;

40.其中,所述无线电器件用于目标检测和/或通信。

41.本技术提供的一种芯片裸片,包括:互连介质层以及形成于互连介质层中的至少两个需要互连的电路模块,该至少两个需要互连的电路模块用于通过芯片裸片的封装介质层中的封装走线互连。这样,利用封装介质层中的封装走线实现芯片裸片中电路模块的互连,代替传统的利用互连介质层中的互连线实现电路模块的互连,降低芯片裸片内互连结构所占用芯片的面积。而且由于封装走线是在封装工艺中完成的,封装工艺是在芯片工艺完成后额外再添加的处理步骤,利用封装工艺实现电路模块之间的互连,可以采用大尺寸的封装走线降低阻抗,且封装工艺的成本较低,从而实现高性能的同时降低成本。

附图说明

42.为了更清楚地说明本技术或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

43.图1为一种芯片结构的结构示意图;

44.图2为本技术一实施例提供的一种芯片裸片的结构示意图;

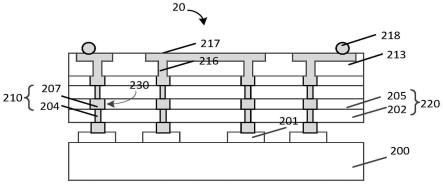

45.图3为本技术一实施例提供的一种封装体的结构示意图;

46.图4为本技术一实施例提供的一种芯片裸片的制造方法的流程图;

47.图5为本技术一实施例提供的一种封装体的制造方法的流程图。

具体实施方式

48.为使本技术的目的、技术方案和优点更加清楚,下面将结合本技术中的附图,对本技术中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

49.随着芯片上包含的功能模块越来越多,芯片尺寸也随之增加,需要互连的器件之间距离也相应增加,而对互连损耗的要求却不会相应降低。尤其对于包含射频模块的芯片,由于实现射频模块互连的金属线不仅要求有低的直流损耗,同时要求交流损耗也要尽可能低。因此,对互连线提出了更高的要求。

50.传统的互连结构,参考图1所示,在衬底100上形成互连介质层104,互连介质层104中形成有多个电路模块102。当需要互连的电路模块102相距较远时,先通过互连介质层104中的互连结构连接,互连结构包括互连线106和通孔110,而后通过连接层114将互连结构连接,以实现远距离电路模块102之间的互连。随后,在封装介质层120中形成互连的封装走线通孔116和封装走线118,封装走线通孔116与连接层114连接,封装走线118与焊球122连接。当使用芯片时将焊球122焊接至pcb板上,实现芯片与外部电路之间的连接。传统的互连结构是使用高层金属作为互连线,高层金属相比低层金属通常厚度和宽度更大,虽然其损耗相对减小,但是占用更大的芯片面积,导致成本增加。

51.针对上述问题,本技术提出了一种芯片裸片,包括:互连介质层以及形成于互连介质层中的至少两个需要互连的电路模块,该至少两个需要互连的电路模块用于通过芯片裸片的封装介质层中的封装走线互连。这样,利用封装介质层中的封装走线实现芯片裸片中电路模块的互连,代替传统的利用互连介质层中的互连线实现电路模块的互连,降低芯片裸片内互连结构所占用芯片的面积。而且由于封装走线是在封装工艺中完成的,封装工艺是在芯片工艺完成后额外再添加的处理步骤,利用封装工艺实现电路模块之间的互连,可以采用大尺寸的封装走线降低阻抗,且封装工艺的成本较低,从而实现高性能的同时降低成本。

52.下面以具体地实施例对本技术的技术方案进行详细说明。下面这几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例不再赘述。

53.本技术一实施例提供一种芯片裸片10,参考图2和图3所示,包括:互连介质层220,

以及形成于互连介质层220中的至少两个需要互连的电路模块201;

54.其中,至少两个需要互连的电路模块201用于通过芯片裸片10的封装介质层213中的封装走线217互连。

55.互连介质层220中形成有至少两个需要互连的电路模块201,互连介质层220能够对电路模块201起到保护作用。互连介质层220可以为单层结构,可以为复合膜层结构,可以包括层间介质层、金属间介质层等。互连介质层220的材料可以为氮化硅、氧化硅、dnc(nitrogen doped silicon carbide,掺氮碳化硅)等介质材料的一种或多种。

56.电路模块201可以包括一个或多个器件,例如可以包括mos器件、存储器件、传感器件、或电容以外其他无源器件等。mos器件可以包括pmos器件或nmos器件。存储器件可以包括非易失性存储器或随机存储器。非易失性存储器可以包括nor型闪存、nand型闪存等浮栅效应晶体管、铁电存储器或相变存储器。传感器件可以为感光器件,其他无源器件可以包括电阻或电感。器件还可以为平面型器件或立体器件,立体器件可以包括fin-fet(鳍式场效应晶体管)或三维存储器。

57.作为一种实现方式,需要互连的电路模块201可以在芯片裸片10中相邻设置,可以理解的是,在芯片裸片10内部,该相邻设置的电路模块201之间不存在其他电路模块,或其他需要互连的电路模块,以降低设置互连结构的难度,简化工艺。

58.电路模块201可以位于互连介质层220的底部,互连介质层220中形成有多个互连结构230,每一个互连结构230可以与一个电路模块201连接,当互连介质层220中多个相距较远的电路模块201需要互连时,可以通过互连结构230的互连实现电路模块201的互连。互连介质层220可以为复合膜层结构,互连结构230包括多个子互连结构210,各子互连结构210包括依次贯穿位于电路模块201上各膜层的通孔204和互连线207。例如互连介质层220包括第一介质层202和第二介质层205,子互连结构210中的通孔204贯穿第一介质层202,子互连结构210中的互连线207贯穿第二介质层202。互连线207的材料为金属,通孔204是指填充有金属材料的连接孔,金属例如可以为钨、铝、铜等。

59.芯片裸片10还包括衬底200,衬底200用于支撑电路模块201以及互连介质层220,衬底200为半导体衬底,例如可以为si衬底、ge衬底、sige衬底、soi(silicon on insulator,绝缘体上硅)衬底或goi(germanium on insulato,绝缘体上硅)等。在其他实施例中,半导体衬底还可以为包括其他元素半导体或化合物半导体的衬底,例如gaas、inp或sic等。还可以为叠层结构,例如si/sige等。还可以为其他外延结构,例如sgoi(silicon germanium on insulator,绝缘体上硅锗)等。

60.互连介质层220中的至少两个需要互连的电路模块201通过芯片裸片10的封装介质层213中的封装走线217连接。当电路模块201位于互连介质层220的底部时,可以利用互连介质层220中的互连结构230将电路模块201与封装走线217连接,从而实现电路模块201之间的互连。具体的,互连结构230贯穿互连介质层220的顶部表面,使得互连结构230能够与封装走线217连接,从而使得电路模块201通过互连结构230与对应的封装走线217连接。

61.利用封装走线217实现电路模块201的互连,降低互连损耗。封装走线217是在封装工艺中完成的,封装工艺是在芯片工艺完成后额外添加的处理步骤,其目的是将芯片裸片10上的电路接口引出,方便后续焊接至印刷电路板pcb上。在芯片裸片10的制造过程中,只需要将制造芯片裸片10上需要互连的电路模块201的接口,接口例如可以为互连结构230,

而后利用封装工艺将接口相互连接,以实现芯片裸片10中电路模块201之间的互连。由于在封装介质层213中布线不会有在芯片裸片10中布线需要跳线或被阻挡无法布线等限制,因而可以采用大尺寸的封装走线217以降低阻抗,而且封装工艺的成本低于芯片工艺的成本,从而能够在提高性能的同时降低成本。

62.以上对本技术提供的芯片裸片10进行了详细的描述,本技术实施例提供的芯片裸片包括互连介质层以及形成于互连介质层中的至少两个需要互连的电路模块,该至少两个需要互连的电路模块通过芯片裸片的封装介质层中的封装走线互连。利用从封装介质层中的封装走线实现芯片裸片中电路模块的互连,代替传统的利用互连介质层中的互连线实现电路模块的互连,降低芯片裸片内互连结构所占的面积,提高芯片裸片的性能降低工艺成本。

63.本技术实施例还提供一种封装体20,参考图3所示,包括:

64.上述的芯片裸片10;

65.封装介质层213,形成于互连介质层220之上;

66.其中,封装介质层213中形成有封装走线217,需要互连的电路模块201通过部分封装走线217相互连接。

67.芯片裸片10包括:互连介质层220,互连介质层220中形成有多个需要互连的电路模块201。互连介质层220中可以形成有多个互连结构230,每一互连结构230可以与一个电路模块201连接。

68.在互连介质层220至少形成有封装介质层213,封装介质层213可以为单层结构,可以为复合膜层结构,可以包括层间介质层、金属间介质层等。封装介质层213的材料可以为氮化硅、氧化硅、dnc(nitrogen doped silicon carbide,掺氮碳化硅)等介质材料的一种或多种。

69.封装介质层213中还可以形成有封装走线通孔216,封装走线通孔216与互连结构230以及封装走线217连接,即封装走线通孔216将封装走线217和互连结构230连接在一起。在平行于衬底200的方向上,封装走线通孔216的尺寸可以小于互连结构230中最顶层互连线或通孔的尺寸,从而在形成封装走线通孔216时无需过多考虑尺寸的精度,简化工艺。

70.在封装走线217上可以形成有封装焊球218,封装焊球218后续被焊接至pcb板上,从而利用封装焊球218实现芯片裸片10与封装体20外的器件连接。封装焊球的材料218为金属,例如可以为钨、铝、铜等。

71.在封装介质层213中还可以形成有天线结构(图未示出),天线结构可以与用于将电路模块201互连的封装走线217位于同一膜层中。

72.在具体的应用中,封装体20可以为毫米波雷达芯片,毫米波雷达是工作在毫米波波段(millimeter wave)探测的雷达,在通信、雷达、制导、遥感技术、射电天文学和波谱学方面都有重大的意义。

73.本技术提供的封装体,包括:芯片裸片以及封装介质层,封装介质层中形成有封装走线,封装走线将芯片裸片中的互连介质层中的电路模块连接,由于封装走线是利用封装工艺在封装层面形成的,不占用芯片裸片的面积,因而可以增大封装走线的尺寸以降低阻抗,且封装工艺的成本低于芯片工艺的成本,从而在提高封装体的性能的同时,降低工艺成本。

74.本技术实施例还提供一种芯片裸片10的制造方法,参考图4所示,包括:

75.s101、提供芯片衬底200;

76.衬底200为半导体衬底,例如可以为si衬底、ge衬底、sige衬底、soi(silicon on insulator,绝缘体上硅)衬底或goi(germanium on insulato,绝缘体上硅)等。

77.s102、于芯片衬底200上形成互连介质层220,互连介质层220中制备有至少两个需要互连的电路模块201。

78.在芯片衬底200上形成互连介质层220,互连介质层220可以为单层结构或复合膜层结构,互连介质层220中形成有至少两个需要互连的电路模块201。需要互连的电路模块201通过用于封装芯片裸片10的封装介质层213中的封装走线217互连。

79.本技术实施例还提供一种封装体20的制造方法,参考图5所示,包括:

80.s201、提供芯片裸片10,芯片裸片10中设置有至少两个需要互连的电路模块201。

81.芯片裸片10包括互连介质层220,互连介质层220中形成有至少两个需要互连的电路模块201。

82.s202、于芯片裸片10之上形成封装介质层213。

83.在芯片裸片10上形成封装介质层213,封装介质层213中形成有封装走线217,需要互连的电路模块201通过封装走线217相互连接。

84.在一个实施例中,本技术还提供一种无线电器件,可包括承载体、天线以及如上述任一实施例所述的封装体20,所述封装体20可固定设置在承载体上;天线也可设置在承载体上,或者该天线也可集成于封装体20中(即此时封装体20可为aip或aoc(antenna-on-package)结构);封装体20中的芯片裸片10与天线连接,以用于收发无线电信号。其中,上述的承载体可以为印刷电路板pcb。

85.在一个实施例中,本技术还提供一种设备,可包括设备本体以及设置于设备本体上的如上述实施例的无线电器件;其中,无线电器件可用于目标检测和/或通信。

86.具体地,在上述实施例的基础上,在本技术的一个实施例中,无线电器件可以设置在设备本体的外部,在本技术的另一个实施例中,无线电器件还可以设置在设备本体的内部,在本技术的其他实施例中,无线电器件还可以一部分设置在设备本体的内部,一部分设置在设备本体的外部。本技术对此不作限定,具体视情况而定。

87.需要说明的是,无线电器件可通过发射及接收信号实现诸如目标检测及无线通信等功能。

88.在一个可选的实施例中,上述设备本体可为应用于诸如智能住宅、交通、智能家居、消费电子、监控、工业自动化、舱内检测及卫生保健等领域的部件及产品。例如,该设备本体可为智能交通运输设备(如汽车、自行车、摩托车、船舶、地铁、火车等)、安防设备(如摄像头)、液位/流速检测设备、智能穿戴设备(如手环、眼镜等)、智能家居设备(如电视、空调、智能灯等)、各种通信设备(如手机、平板电脑等)等,以及诸如道闸、智能交通指示灯、智能指示牌、交通摄像头及各种工业化机械臂(或机器人)等,也可为用于检测生命特征参数的各种仪器以及搭载该仪器的各种设备,例如汽车舱内检测、室内人员监控、智能医疗设备(或机器人)等。当上述的设备本体应用于先进驾驶辅助系统(即adas)时,作为车载传感器的无线电器件(如毫米波雷达)则可为adas系统提供诸如自动刹车辅助(即aeb)、盲点检测预警(即bsd)、辅助变道预警(即lca)、倒车辅助预警(即rcta)、自动泊车等各种功能安全提

供保障。无线电器件则可为本技术任一实施例中所阐述的无线电器件,无线电器件的结构和工作原理在上述实施例中已经进行了详细说明,此处不在一一赘述。

89.最后应说明的是:以上各实施例仅用以说明本技术的技术方案,而非对其限制。尽管参照前述各实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换。而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1