光检测器的制作方法

光检测器

1.本技术是申请日为2019年3月28日、申请号为201980021367.2、发明名称为“光检测器”的发明专利申请的分案。

技术领域

2.本公开涉及光检测器。

背景技术:

3.近几年,在医疗、通信、生物、化学、监视、车载、放射线检测等的多方面的领域中利用高灵敏度的光检测器。作为用于高灵敏度化的方法之一,利用雪崩光电二极管(avalanche photo diode:以下,也称为apd)。apd是,将对入射到光电转换层的光进行光电转换而发生的信号电荷,利用雪崩击穿来倍增,从而提高光的检测灵敏度的光电二极管。利用apd,从而也能够检测稍微的光子的数量。

4.例如,提出了利用apd的光子计数型的光检测器(例如,参照专利文献1)以及高灵敏度图像传感器(例如,参照专利文献2)。

5.并且,例如,作为apd的结构的一个例子,公开拉通型的apd(例如,参照专利文献2以及专利文献3)。

6.并且,提出了即使光电转换层变厚,也不使雪崩击穿电压增大的结构(例如,参照专利文献4)。

7.根据该结构,在光电转换层形成内建电势梯度,据此,电荷漂移,因此,不使雪崩击穿电压增大,也能够使光电转换膜变厚。

8.并且,为了提高读出apd检测出的电荷的电路的自由度,而提出了将像素与像素电路接近配置的结构(例如,参照专利文献5以及专利文献6)。

9.并且,提出了将形成有apd阵列的晶片、与具备接口电路的其他的晶片接合,从而提高电路自由度的结构(例如,参照专利文献7)。

10.(现有技术文献)

11.(专利文献)

12.专利文献1:国际公开第2008/004547号

13.专利文献2:国际公开第2014/097519号

14.专利文献3:日本特开2015

‑

5752号公报

15.专利文献4:美国专利申请公开第2016/0163906号说明书

16.专利文献5:日本特开2004

‑

363437号公报

17.专利文献6:日本特开2004

‑

319576号公报

18.专利文献7:美国专利第8093624号说明书

19.专利文献8:美国专利第9178100号说明书

技术实现要素:

20.本公开提供灵敏度高的光检测器。

21.为了解决所述问题,本公开的一个形态涉及的光检测器,具备:半导体基板,具有第一主面以及与所述第一主面相反的一侧的第二主面;外延层,形成于所述半导体基板;倍增区域,在所述外延层中,与所述第一主面大致平行,并且对在所述半导体基板通过光电转换产生的电荷进行雪崩倍增;以及分离区域,至少分离两个所述倍增区域。

22.根据这样的结构,在光电转换层发生的电荷之中的、第一导电型的载流子即第一电荷,在光电转换层内漂移,进入倍增区域,产生雪崩倍增。由光电转换发生的电荷,由雪崩倍增放大,因此,即使在入射光的强度小的情况下,也能够进行光检测。也就是说,根据这样的结构,能够提高光检测器的灵敏度(即,受光灵敏度)。

23.例如,专利文献7公开的结构,不能由cmos(complementary metal oxide semiconductor)过程制造。

24.另一方面,根据本公开的一个形态涉及的光检测器,在相同的半导体基板内,能够形成apd以及分离晶体管等的像素电路,因此,能够由一般的cmos过程制造。据此,能够以更低成本制造,本公开的一个形态涉及的光检测器。

25.并且,例如,所述光检测器还具有被形成在所述第二主面的第二接触件,在所述第一半导体层以及所述第二半导体层之间由光电转换发生的电荷之中的第二电荷,经由所述第二接触件,向所述半导体基板的外部流动,所述第二电荷的极性与所述第一电荷不同。

26.根据这样的结构,由光电转换以及雪崩倍增发生的第二导电型的载流子即第二电荷,经由位于半导体基板的背面侧即第二主面的第二接触件,排出到光检测器的外部。

27.根据本公开的一个形态涉及的光检测器,能够将光检测时作为信号不利用的第二电荷,经由半导体基板背面在短时间内排出,因此,能够减少半导体基板背面(例如,第一半导体层以及第二半导体层)的电压的基于时间变化、以及位置的不均匀。据此,能够抑制光检测效率的空间上以及时间上的差异。

28.例如,根据专利文献8公开的结构,阳极和阴极被配置在相同的面上,因此,雪崩倍增时的电荷的漂移方向、与电荷排出时的电荷运动的方向为反方向,因此,电荷排出为止的时间变长,检测效率降低。

29.并且,例如,所述分离区域,通过电势使所述第一半导体层以及所述电路区域分离。

30.根据这样的结构,能够使分离区域变窄,能够实现开口率的提高以及像素细微化。并且,与形成沟槽等来形成分离区域的情况相比,能够简单地进行形成。

31.并且,例如,所述电势,比因由所述雪崩倍增发生的电荷而引起的所述第一半导体层的电压变化大。

32.根据这样的结构,即使在第一半导体层发生电压变化的情况下,也能够由分离区域使第一半导体层与电路区域电分离。

33.并且,例如,所述分离区域被耗尽。

34.根据本公开的一个形态涉及的光检测器,第一半导体层与电路区域,由分离区域分离。使分离区域成为耗尽,从而能够由短的分离宽度分离第一半导体层与电路区域,并且,缓和分离区域的电场。据此,本公开的一个形态涉及的光检测器,能够确保受光灵敏度,

并且,实现细微化。因此,根据本公开的一个形态涉及的光检测器,开口率提高,因此,光灵敏度提高。

35.并且,例如,在形成有所述第一半导体层以及所述分离区域的区域,没有形成sti(shallow trench isolation)即浅槽隔离或接触件。

36.根据这样的结构,与专利文献4公开的结构不同,在分离区域上,没有形成sti以及第一接触件。因此,能够抑制暗电流。

37.并且,例如,所述第二半导体层,在平面视中,形状与所述第一半导体层相同,或者,比所述第一半导体层宽。

38.根据这样的结构,雪崩倍增区域扩大,因此,光检测器的光灵敏度更提高。

39.并且,例如,所述第二半导体层,被形成在所述第一主面的全面。

40.根据这样的结构,雪崩倍增区域更扩大,因此,光检测器的光灵敏度更提高。

41.如专利文献4以及专利文献8,在分离区域设置接触件的情况下,不能为了防止雪崩倍增区域端部的电场集中,而扩大雪崩倍增区域。

42.在专利文献4中,需要将enriched region形成为比anode region窄,不能扩大倍增区域。

43.并且,在专利文献8中,为了防止雪崩倍增区域端部的电场集中,而在雪崩倍增区域与接触件之间设置保护环,因此,不能扩大雪崩倍增区域。

44.并且,例如,所述第二半导体层的杂质浓度,随着朝向深度方向增加。

45.需要使在雪崩倍增区域层叠设置的光电转换层变厚,但是,在专利文献1、专利文献2、以及专利文献3公开的结构中,在使光电转换层变厚的情况下,雪崩击穿电压变高。并且,在专利文献5公开的结构中,需要向布线施加雪崩击穿电压以上的高电压。

46.另一方面,根据本公开的一个形态涉及的光检测器,能够不增大雪崩击穿电压,而使光电转换膜变厚,因此,能够同时实现低雪崩击穿电压以及高受光灵敏度。

47.并且,例如,所述第二半导体层的杂质浓度分布,在与所述第一主面平行的方向上大致恒定。

48.根据这样的结构,分离区域的电势,相对于半导体基板表面的水平方向的变动变小,雪崩倍增区域的电场成为均匀。据此,能够更扩大雪崩倍增区域,因此,光灵敏度更提高。

49.并且,例如,本公开的一个形态涉及的光检测器还具备,被形成在所述电路区域的至少一个第一阱,所述第一阱是所述第一导电型,在所述第一阱与所述第二半导体层的边界,杂质浓度比所述第一半导体层低。

50.根据这样的结构,能够减少第一阱中发生的电场以及电流。因此,能够减少电力消耗。

51.并且,例如,所述第一阱被形成为,与所述第一半导体层相比,更接近于所述第二主面的一侧。

52.根据这样的结构,能够更减少第一阱中发生的电场。因此,能够更减少电力消耗。

53.并且,例如,关于所述第二半导体层的杂质浓度分布,从所述第一主面朝向所述第二主面,浓度梯度陡峭。

54.根据这样的结构,能够使在深的区域发生的第一电荷,以更高速度漂移。因此,能

够更缩短本公开的一个形态涉及的光检测器受光后由读出电路读出电荷为止的响应时间,并且,响应时间的差异减少。

55.并且,例如,所述第一半导体层与所述第二半导体层的分界面,被形成在比所述第二半导体层的上表面的一部分,更靠近所述第二主面的一侧。

56.根据这样的结构,雪崩击穿电压的差异减少。

57.并且,例如,在包括所述第一半导体层以及所述第二半导体层的分界面的区域,所述第一半导体层的杂质浓度,比所述第二半导体层的杂质浓度大。

58.根据这样的结构,雪崩击穿电压的差异更减少。

59.并且,例如,所述第二半导体层的杂质浓度为10

16

cm

‑3以上。

60.根据这样的结构,能够将雪崩击穿电压设为50v以下。

61.并且,例如,所述第一半导体层具有,杂质浓度随着朝向深度方向增加的区域。

62.根据这样的结构,第一半导体层的si

‑

sio2分界面(第一主面)中发生的电荷,向远离雪崩倍增区域的方向漂移。因此,dcr(dark count rate)减少。

63.并且,例如,所述第一半导体层包括,与所述半导体基板的第一主面接触的第二导电型层。

64.根据这样的结构,dcr更减少。

65.并且,例如,本公开的一个形态涉及的光检测器,具备多个所述第一接触件以及多个所述分离晶体管,多个所述分离晶体管分别与多个所述第一接触件的任意一个连接,多个所述分离晶体管被形成在一个所述电路区域内。

66.根据这样的结构,本公开的一个形态涉及的光检测器,能够缩小电路区域,因此,开口率更提高,能够实现细微化。

67.并且,例如,多个所述分离晶体管之中的至少两个分离晶体管共享所述读出电路。

68.根据这样的结构,本公开的一个形态涉及的光检测器,能够更缩小电路区域,因此,开口率更提高,能够实现细微化。

69.并且,例如,至少两个所述分离晶体管共享与所述读出电路连接的漏极。

70.根据这样的结构,能够更缩小电路区域,因此,开口率更提高,能够实现细微化。

71.并且,例如,在平面视中,在具有m次旋转对称性的n边形内,以保持m次旋转对称性的方式,形成有n个所述第一半导体层,所述电路区域,被形成在具有所述m次旋转对称性的n边形的旋转对称中心,在所述电路区域内,形成n个所述分离晶体管,m为2以上的自然数,n为3以上的自然数。

72.根据这样的结构,反复周期内包括的像素间的灵敏度的差异减少。因此,本公开的一个形态涉及的光检测器,能够提高拍摄的图像的画质。

73.并且,例如,所述读出电路,在所述电路区域内,具备:复位晶体管,与所述分离晶体管的漏极连接,经由所述分离晶体管复位所述第一半导体层;源极跟随晶体管,读出来自所述分离晶体管的输出信号;以及选择晶体管,与所述源极跟随晶体管连接。

74.根据这样的结构,能够放大每个像素的信号。因此,s/n比提高。

75.并且,本公开的一个形态涉及的光检测器,具备:半导体基板,具有第一主面以及与所述第一主面相反的一侧的第二主面;具有第一导电型的第一半导体层,被形成在所述半导体基板的所述第一主面侧;具有第二导电型的第二半导体层,被形成在所述半导体基

板的所述第一半导体层以及所述第二主面之间,所述第二导电型是与所述第一导电型不同的导电型;倍增区域,在所述第一半导体层以及所述第二半导体层,对在所述半导体基板由光电转换发生的电荷进行雪崩倍增;以及分离区域,至少分离两个所述倍增区域。

76.根据这样的结构,在光电转换层发生的电荷,在光电转换层内漂移,进入倍增区域产生雪崩倍增。由光电转换发生的电荷,由雪崩倍增放大,因此,即使在入射光的强度小的情况下,也能够进行光检测。也就是说,根据这样的结构,能够提高光检测器的灵敏度(即,受光灵敏度)。

77.并且,根据这样的结构,不需要在分离区域形成接触件或sti,能够使分离区域变窄,因此,光检测器,能够扩大倍增区域的面积,提高光灵敏度。

78.并且,例如,所述光检测器还具备被形成在所述第二主面的第二接触件,在所述第一半导体层以及所述第二半导体层之间由光电转换发生的第一电荷以及极性与所述第一电荷不同的第二电荷之中的一方,经由所述第二接触件,向所述半导体基板的外部流动。

79.根据这样的结构,例如,由光电转换以及雪崩倍增发生的第二导电型的载流子即第二电荷,经由位于半导体基板的背面侧即第二主面的接触件,排出到光检测器的外部。因此,能够减少半导体基板背面的电压的基于时间变化、以及位置的不均匀。据此,能够抑制光检测器的光检测效率的空间上以及时间上的差异。

80.并且,例如,所述分离区域,通过电势至少使两个所述倍增区域分离。

81.根据这样的结构,与像专利文献4以及专利文献8那样在分离区域形成接触件或sti的情况相比,能够使分离区域变窄,提高开口率,从而提高光灵敏度。

82.并且,例如,所述电势,比因由所述雪崩倍增发生的电荷而引起的所述第一半导体层的电压变化大。

83.根据这样的结构,即使在第一半导体层中发生电压变化的情况下,也能够由分离区域使两个倍增区域电分离,因此,不发生因溢出而引起的电气混合色。

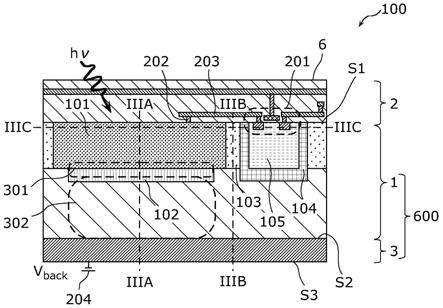

84.并且,例如,所述分离区域被耗尽。

85.根据这样的结构,使分离区域成为耗尽,从而能够由更短的分离宽度分离两个倍增区域,并且,缓和分离区域的电场。据此,本公开的一个形态涉及的光检测器,能够提高开口率,能够提高光灵敏度。另外,能够确保受光灵敏度,并且,实现细微化。因此,根据本公开的一个形态涉及的光检测器,能够提高开口率。

86.并且,例如,在形成有所述第一半导体层以及所述分离区域的区域,没有形成sti以及所述接触件。

87.根据这样的结构,能够减少半导体基板表面的缺陷能级密度,能够抑制暗电流的发生。

88.并且,例如,所述第二半导体层,在平面视中,形状与所述第一半导体层相同,或者,比所述第一半导体层宽。

89.根据这样的结构,雪崩倍增区域扩大,光检测器的光灵敏度更提高。

90.并且,例如,所述光检测器还具备多个所述第一半导体层,所述第二半导体层,以在平面视中与多个所述第一半导体层重叠的方式连续地形成在所述半导体基板。

91.根据这样的结构,雪崩倍增区域更扩大,因此,光检测器的光灵敏度更提高。

92.如专利文献4以及专利文献8,在分离区域设置接触件的情况下,不能为了防止雪

崩倍增区域端部的电场集中,而扩大雪崩倍增区域。

93.并且,在专利文献4中,需要将enriched region形成为比anode region窄,不能扩大倍增区域。

94.并且,在专利文献8中,为了防止雪崩倍增区域端部的电场集中,而在雪崩倍增区域与接触件之间设置保护环,因此,不能扩大雪崩倍增区域。

95.并且,例如,所述第二半导体层的杂质浓度,随着朝向深度方向增加。

96.需要使在雪崩倍增区域层叠设置的光电转换层变厚,但是,在专利文献1、专利文献2、以及专利文献3公开的结构中,在使光电转换层变厚的情况下,雪崩击穿电压变高。并且,在专利文献5公开的结构中,需要向布线施加雪崩击穿电压以上的高电压。

97.另一方面,根据本公开的一个形态涉及的光检测器,能够不增大雪崩击穿电压,而使光电转换膜变厚,因此,能够同时实现低雪崩击穿电压以及高受光灵敏度。

98.并且,例如,所述第二半导体层的杂质浓度分布,在与所述第一主面平行的方向上大致恒定。

99.根据这样的结构,分离区域的电势,相对于半导体基板表面的水平方向的变动变小,雪崩倍增区域的电场成为均匀。据此,能够更扩大雪崩倍增区域,因此,能够更提高光灵敏度。

100.根据本公开,能够提供灵敏度高的光检测器。

附图说明

101.图1是示出本公开的实施方式1涉及的光检测器的平面图。

102.图2是示出图1的ii

‑

ii线的、本公开的实施方式1涉及的光检测器的截面图。

103.图3是示出图2的iiia

‑

iiia线上以及iiib

‑

iiib线上的、本公开的实施方式1涉及的光检测器的电势的图。

104.图4是示出图2的iiic

‑

iiic线上的、本公开的实施方式1涉及的光检测器的电势的图。

105.图5是示出本公开的实施方式1涉及的光检测器的电路结构例的图。

106.图6是示出本公开的实施方式1涉及的光检测器的变形例的截面图。

107.图7是示出图6的viia

‑

viia线上、viib

‑

viib线上、以及viic

‑

viic线上的、本公开的实施方式1涉及的光检测器的变形例的电势的图。

108.图8是示出本公开的实施方式2涉及的光检测器的平面图。

109.图9是示出图8的ix

‑

ix线的、本公开的实施方式2涉及的光检测器的截面图。

110.图10是示出图9的xa

‑

xa线以及xb

‑

xb线上的、本公开的实施方式2涉及的光检测器的电势的图。

111.图11是示出图9的xa

‑

xa线上的、本公开的实施方式2涉及的光检测器的杂质浓度曲线的图。

112.图12是示出图9的xa

‑

xa线上的、本公开的实施方式2涉及的光检测器的杂质浓度曲线的变形例的图。

113.图13是示出本公开的实施方式2涉及的光检测器的电流电压特性的一个例子的图。

114.图14是用于说明本公开的实施方式2涉及的光检测器的雪崩击穿电压的差异减少效果的一个例子的图。

115.图15是示出本公开的实施方式2涉及的光检测器的变形例1的平面图。

116.图16是示出图15的xvi

‑

xvi线的、本公开的实施方式2涉及的光检测器的变形例1的截面图。

117.图17是示出图16的xviia

‑

xviia线上的、本公开的实施方式2涉及的光检测器的变形例1的杂质浓度曲线的图。

118.图18是示出本公开的实施方式2涉及的光检测器的变形例2的平面图。

119.图19是示出图18的xix

‑

xix线的、本公开的实施方式2涉及的光检测器的变形例2的截面图。

120.图20是示出图19的xxa

‑

xxa线上的、本公开实施方式2涉及的光检测器的变形例2的杂质浓度曲线的图。

121.图21是示出本公开的实施方式2涉及的光检测器的变形例3的平面图。

122.图22是示出图21的xxii

‑

xxii线的、本公开的实施方式3涉及的光检测器的变形例3的截面图。

123.图23是示出本公开涉及的光检测器的像素的配置布局的第1例的平面图。

124.图24是示出本公开涉及的光检测器的像素的配置布局的第2例的平面图。

125.图25是示出本公开涉及的光检测器的像素的配置布局的第3例的平面图。

126.图26是示出本公开涉及的光检测器的像素的配置布局的第4例的平面图。

127.图27是示出本公开涉及的光检测器的像素的配置布局的第5例的平面图。

128.图28是示出本公开涉及的光检测器的像素的配置布局的第6例的平面图。

129.图29是示出本公开涉及的光检测器的像素的配置布局的第7例的平面图。

130.图30是示出本公开涉及的光检测器的像素的配置布局的第8例的平面图。

131.图31是示出本公开涉及的光检测器的像素的配置布局的第9例的平面图。

132.图32是示出本公开涉及的光检测器的像素的配置布局的第10例的平面图。

133.图33是示出本公开涉及的光检测器的像素的配置布局的第11例的平面图。

134.图34是示出本公开涉及的光检测器的像素的配置布局的第12例的平面图。

135.图35是示出图34的xxxv

‑

xxxv线的、本公开涉及的光检测器的像素的配置布局的第12例的截面图。

136.图36是示出本公开涉及的光检测器的电路结构的变形例1的图。

137.图37是示出本公开涉及的光检测器的电路结构的变形例1的像素阵列的一个例子的平面图。

138.图38是示出本公开涉及的光检测器的电路结构的变形例1的驱动序列的一个例子的图。

139.图39是示出本公开涉及的光检测器的电路结构的变形例2的图。

140.图40是示出本公开涉及的光检测器的电路结构的变形例2的像素阵列的一个例子的平面图。

141.图41是示出本公开涉及的光检测器的电路结构的变形例2的像素阵列的另一个例子的平面图。

142.图42是示出本公开涉及的光检测器的电路结构的变形例2的驱动序列的一个例子的图。

143.图43是示出本公开涉及的光检测器的封装体的第1例的截面图。

144.图44是示出本公开涉及的光检测器的封装体的第2例的截面图。

145.图45是示出本公开涉及的光检测器的封装体的第3例的截面图。

146.图46是用于说明本公开涉及的光检测器的制造工序的截面图。

147.图47是用于说明本公开涉及的光检测器的制造工序的截面图。

148.图48是用于说明本公开涉及的光检测器的制造工序的截面图。

149.图49是用于说明本公开涉及的光检测器的制造工序的截面图。

150.图50是用于说明本公开涉及的光检测器的制造工序的截面图。

151.图51是用于说明本公开涉及的光检测器的制造工序的截面图。

152.图52是用于说明本公开涉及的光检测器的制造工序的截面图。

153.图53是示出本公开的实施方式3涉及的光检测器的平面图。

154.图54是示出图53的liv

‑

liv线的、本公开的实施方式3涉及的光检测器的截面图。

155.图55是示出图54的lva

‑

lva线上以及lvb

‑

lvb线上的、本公开的实施方式3涉及的光检测器的电势的图。

156.图56是示出图54的lvc

‑

lvc线上的、本公开的实施方式3涉及的光检测器的电势的图。

157.图57是示出本公开的实施方式3涉及的光检测器的变形例1的截面图。

158.图58是示出本公开的实施方式3涉及的光检测器的变形例2的截面图。

159.图59是示出图58的lixa

‑

lixa线上、lixb

‑

lixb线上、以及lixc

‑

lixc线上的、本公开的实施方式3涉及的光检测器的变形例2的电势的图。

具体实施方式

160.以下,对于本公开的实施方式,利用附图进行说明。而且,以下说明的实施方式,都示出本公开的优选的一个具体例子。因此,以下的实施方式示出的数值、构成要素、构成要素的配置位置以及连接形态、工序(步骤)以及工序的顺序等是一个例子,不是限定本公开的宗旨。因此,对于以下实施方式的构成要素中的示出本公开的最上位概念的实施方案中没有记载的构成要素,作为任意的构成要素而被说明。

161.并且,各个图是示意图,并不一定是严密示出的图。因此,各个图中的缩尺等并不一定一致。在各个图中,对于实质上相同的内容附上相同的符号,会有省略或简化重复的说明的情况。

162.并且,本公开涉及的光检测器,也可以组合多个实施方式。

163.并且,在以下的实施方式中,采用大致水平方向等的利用了“大致”的表现。例如,大致一致不仅意味着完全一致,也意味着实质上一致,即,包括例如数%左右的差异。

164.并且,记载为本说明书中的电压的值是以接地为基准的。

165.并且,在本说明书中,“上方”以及“下方”的术语,不示出绝对的空间识别的上方向(铅垂上方)以及下方向(铅垂下方),而作为由以层叠结构的层叠顺序为基准的相对的位置关系规定的术语利用。在本说明书中,以半导体基板为基准,将设置第一主面的一侧设为

“

上方”,将设置第二主面的一侧设为“下方”。并且,“上方”以及“下方”的术语,不仅两个构成要素被配置为相互隔开且在两个构成要素之间存在其他的构成要素的情况,也能够适用两个构成要素被配置为相互密接且两个构成要素接触的情况。

166.并且,在本说明书中,“深度方向”的术语,不示出绝对的空间识别的方向,而作为由层叠结构的层叠方向规定的术语利用。在本说明书中,“深度方向”是,与半导体基板的第一主面的法线平行的方向,并且,从该第一主面向半导体基板的第二主面的方向。

167.而且,在本说明书中,“平面视”示出,从光电转换层的受光面的法线方向看。并且,以后,本说明书中的“上(上方)”、“浅”等的表现示出,截面图的外延层的第一主面侧,“下(下方)”、“深”等的表现示出,截面图的外延层的第二主面侧。

168.(实施方式1)

169.首先,参照图1以及图2,说明实施方式1涉及的光检测器的结构。

170.图1是示出本公开的实施方式1涉及的光检测器100的平面图。图2是示出图1的ii

‑

ii线的、本公开的实施方式1涉及的光检测器100的截面图。

171.而且,在图1以及图2中示出,光检测器100具备的构成要素之中的、第一半导体层101、分离区域103、第一阱104(电路区域)、第二阱105(电路区域)、分离晶体管201、第一布线203、以及读出电路407(参照图5)的一部分的列信号线等的光检测器100具备的像素6,省略示出光检测器100的结构的一部分。例如,在图1中,省略示出与分离晶体管201的栅极连接的布线等的一部分的构成要素。而且,在以后说明的其他的图中,也会有省略示出本公开涉及的光检测器的结构的一部分的情况。

172.实施方式1涉及的光检测器100是,利用apd(avalanche photo diode)的光检测传感器,具备具有外延层1及半导体基板层3的半导体基板600、以及布线层2。具体而言,光检测器100具备,第二导电型的外延层1、形成在半导体基板600(具体而言,外延层1)的第一主面s1上的布线层2、以及形成在半导体基板600的背面侧的半导体基板层3。而且,在本说明书中,将外延层、以及作为用于使该外延层生长的生长基板的半导体基板层一起称为半导体基板。

173.并且,光检测器100具备,配置分离晶体管201的电路区域、以及与分离晶体管201的漏极连接,读出在第一半导体层101以及第二半导体层102之间由光电转换发生的电荷之中的第一电荷的读出电路407(参照图5)。

174.外延层1是,包括至少一个第一导电型的第一半导体层101、第二导电型的第二半导体层102、第一导电型的第一阱104、第二导电型的第二阱105、形成在第一半导体层101与第一阱104之间的具有第二导电型的分离区域103、以及形成在第二阱105内的第一导电型的分离晶体管201的层。

175.电路区域是,例如,具备具有第一导电型的第一阱104、以及具有第二导电型的第二阱105的区域。分离晶体管201是,例如第一导电型。

176.据此,光检测器100的受光灵敏度提高。并且,根据这样的结构,光检测器100的电路的设计自由度提高。

177.第一半导体层101具有,形成在半导体基板600的第一主面s1侧的第一导电型。在第一半导体层101上,形成有用于与分离晶体管201等电连接的电极即第一接触件202。

178.第二半导体层102,被形成在第一半导体层101以及半导体基板层3之间。并且,第

二半导体层102具有,与第一导电型相反的导电型的第二导电型。第二半导体层102,将与第一半导体层101间光电转换后的电荷雪崩倍增。

179.第一阱104,在与半导体基板600的第一主面s1平行的方向上,与第一半导体层101排列形成。第一阱104是,形成一个以上的分离晶体管201等的电路的电路区域。

180.布线层2是,包括形成在第一半导体层101的第一主面s1的电极即第一接触件202、以及将第一接触件202与分离晶体管201的源极电连接的金属布线即第一布线203的层。

181.半导体基板层3是,用于形成外延层1的生长基板。半导体基板层3具有,用于形成外延层1的生长面s2以及生长面s2的相反侧的第二主面s3。在半导体基板层3的背面、且半导体基板600的背面的第二主面s3,形成有背面电极即第二接触件204。若在半导体基板层3施加背面偏压v

back

,则经由半导体基板层3,外延层1的生长面s2侧的电压,固定为v

back

。

182.而且,第二阱105,与接地电连接。并且,实施方式1涉及的晶体管是,mosfet(metal oxide semiconductor field effect transistor)、或双极晶体管等,不限定种类。

183.在第一半导体层101与第二半导体层102之间,形成与外延层1的第一主面s1大致平行的倍增区域301。

184.倍增区域301是,由雪崩倍增使接受的光(图2所示的hν)被光电转换而生成的电荷倍增的区域。

185.倍增区域301的电场的大小是,例如,3至5

×

105v/cm,第一半导体层101以及第二半导体层102的杂质浓度是,例如,10

16

cm

‑3至10

20

cm

‑3,外延层1的杂质浓度是,例如,10

14

cm

‑3至10

16

cm

‑3。

186.并且,在此情况下,倍增区域301的深度方向的电势变化量为,例如20v。

187.而且,在本说明书的各个图中,将接受的光(即,入射光)记载为hν。

188.在层叠在倍增区域301下的光电转换层302由光电转换发生的第二导电型的电荷的载流子即第二电荷,若由漂移到达倍增区域301,则由雪崩倍增,载流子数倍增为1倍至10万倍。此时,由光电转换以及雪崩倍增发生的第一导电型的载流子即第一电荷,蓄积到第一半导体层101。并且,由光电转换以及雪崩倍增发生的第二电荷,漂移到第二接触件204,排出到光检测器100的外侧。也就是说,在第一半导体层101以及第二半导体层102之间由光电转换发生的电荷之中的、极性与第一电荷不同的第二电荷,经由第二接触件204,向半导体基板层3的外部流动。

189.在此,优选的是,第二接触件204,被形成在第二主面s3全面。第二接触件204是,形成在第二导电型的半导体层(第二半导体层102)、或背面(即,第二主面s3)的导电性的材料。特别是,也可以将用于使外延层1生长的生长基板即半导体基板层3作为第二接触件204利用。并且,第二接触件204也可以,对第二导电型的半导体层进行利用杂质扩散、或离子注入等的方法的载流子密度的调整来形成。

190.并且,在基板的第一主面侧形成第二接触件,通过半导体基板向该第二接触件施加电压的情况也包含在本发明内。

191.据此,作为信号不利用的第二电荷,在短时间内排出到光检测器100的外侧。因此,能够抑制光检测器100内部的电压的时间变化以及空间上的不均匀的发生,因此,光检测效率提高。

192.并且,蓄积在第一半导体层101的第一电荷,将用于读出在半导体基板600(具体而

言,第一半导体层101以及第二半导体层102)由光电转换发生的电荷的分离晶体管201接通,从而传输到读出电路407(参照图5),被处理为信号。据此,光检测器100,检测入射光。

193.而且,也可以是第一导电型为正的导电型(即,p型),第二导电型为负的导电型(即,n型)的结构,但是,将第一导电型设为负的导电型,将第二导电型设为正的导电型即可。换而言之,第一电荷是电子,第二电荷是空穴即可。

194.电子的电离率,比空穴的电离率大,因此,容易产生雪崩倍增。因此,根据这样的结构,光检测器100的受光灵敏度提高。

195.在此,在分离区域103、第一阱104、第二阱105的内部、以及第二阱105的下部由光电转换发生的电荷,不贡献于受光灵敏度。因此,将分离区域103、第一阱104、以及第二阱105形成为小,并且,将倍增区域301形成为宽即可。

196.特别是,在实施方式1涉及的光检测器100,在分离区域103上,不形成接触件(具体而言,第一接触件202)以及sti(shallow trench isoration),并且,分离区域103被耗尽且不定电位。具体而言,在形成第一半导体层101以及分离区域103的区域,没有形成sti。

197.据此,能够缩小分离区域103的宽度,因此,能够提高光检测器100的开口率。

198.尤其优选的是,与分离区域103的横方向(与第一主面s1平行的方向)的耗尽层宽度(即,分离区域103的宽度的一半左右)相比,倍增区域301的纵方向(与第一主面s1垂直的方向)的耗尽层的宽度宽。根据这样的结构,容易缓和倍增区域301的端部的电场集中,容易使电场强度均匀。因此,能够扩大雪崩倍增的区域,容易提高光灵敏度。

199.并且,分离区域103的宽度是,例如,0.1μm至1μm,杂质浓度是,10

15

cm

‑3至10

18

cm

‑3。分离区域103的电位,由第一半导体层101的电位、第一阱104的电位、以及背面偏压v

back

决定。

200.在此,若第一半导体层101与分离区域103的电位差v小,则饱和电子数变小,容易发生向相邻像素的电荷漏出。另一方面,若第一半导体层101与分离区域103的电位差v大,则在设备表面(例如,第一主面s1)发生的电场变大,存在暗电流以及暗计数增大的问题。因此,优选的是,第一半导体层101与分离区域103的电位差为,0.1v至10v左右的范围。

201.并且,实施方式1的光入射面是,外延层1的第一主面s1面。

202.据此,不需要使用背面加工等的特殊过程,能够减少成本。特别是,近红外光等的长波长的光,吸收系数低,不衰减直到半导体基板层3附近为止,因此,即使光电转换层302被形成在离外延层1的第一主面s1远的区域,与被形成在第一主面s1附近时比较的受光灵敏度也几乎不变化。例如,针对波长在近红外区的太阳光的谱强度为极小的940nm的光的si(硅)的吸收系数为1%/μm,因此,即使光电转换层302被形成在从第一主面s1深1μm,受光灵敏度的降低也是1%。

203.而且,也可以在布线层2中的、倍增区域301上设置光波导,进一步,在布线层2上设置微透镜。据此,能够提高聚光效率。

204.并且,第一半导体层101与分离晶体管201的源极,由通过分离区域103上的第一布线203连接。分离晶体管201的漏极,与读出电路407(参照图5)连接,将连接的多个像素电路(例如,分离晶体管201)形成在同一阱(例如,第二阱105)内,从而能够缩小电路区域的面积,提高开口率。而且,图1以及图2示出,分离晶体管201的漏极与列信号线连接的例子。

205.接着,参照图3以及图4,说明第一电荷的电势。

206.图3是示出图2的iiia

‑

iiia线上以及iiib

‑

iiib线上的、本公开的实施方式1涉及的光检测器100的电势的图。图4是示出图2的iiic

‑

iiic线上的、本公开的实施方式1涉及的光检测器100的电势的图。

207.而且,图3示出的实线是,图2中的iiia

‑

iiia线上的电势,第一半导体层101、倍增区域301以及光电转换层302的电势。

208.第一半导体层101,使分离晶体管201接通,据此,与读出电路407(参照图5)连接,固定为读出电路407(参照图5)的电源电压v

dd

。另一方面,外延层1的生长面s2侧,经由半导体基板层3,固定为v

back

。

209.光电转换层302被耗尽,形成有使电荷向倍增区域301漂移的电势梯度即可。

210.在使光电转换层302被耗尽的情况下,关于光电转换层302的电势变化量,例如,在光电转换层302的厚度为5μm的情况下,为20v,在光电转换层302的厚度为15μm的情况下,为40v左右。

211.而且,以后,在本说明书中,将使倍增区域301产生雪崩倍增的阈值电压被施加时的、第一接触件202与第二接触件204的电压差,称为雪崩击穿电压。在此情况下,例如,在光电转换层302的厚度为5μm时,雪崩击穿电压为40v。

212.如图3示出,iiia

‑

iiia线上、iiib

‑

iiib线上的电势,越朝向深度方向,就越接近v

back

。另一方面,越朝向第一主面s1侧,iiia

‑

iiia线上、iiib

‑

iiib线上的电势就越增大。iiia

‑

iiia线上的电势,接近v

dd

。优选的是,iiib

‑

iiib线上的电势,在第一主面s1被耗尽、电位不定。

213.如图4示出,第一半导体层101,被偏压为v

dd

,第一阱104,也被偏压为v

dd

,但是,分离区域103被耗尽、且不定电位,因此,第一半导体层101与第一阱104电分离。而且,第一半导体层101与分离区域103之间的电位差为,v

dd

至10v即可。

214.光检测器100,根据上述的结构,能够使分离区域103成为细微化,扩大倍增区域301,受光灵敏度提高。

215.例如,在像专利文献4那样,不使分离区域103成为耗尽,而设置接触件的情况下,为了确保电分离、且缓和与外延层1大致平行的方向(即,与第一主面s1平行的方向)的电场,典型而言,在与第一主面s1平行的方向上需要1μm以上的分离宽度。

216.对此,在实施方式1涉及的光检测器100中,分离区域103被耗尽。根据使分离区域103成为耗尽的效果,第一半导体层101与分离区域103之间的电场减少。因此,能够将分离宽度狭窄到0.1μm至1μm。也就是说,能够实现光检测器100的小型化。

217.接着,参照图5,说明实施方式1涉及的光检测器100的电路结构。

218.图5是示出本公开的实施方式1涉及的光检测器100的电路结构例的图。而且,在图5中示出,读出电路407,与垂直信号线404、水平扫描电路408、以及缓冲放大器409连接的例子。并且,在图5中,关于apd401以及转送晶体管402,仅示出一个,但是,也可以形成为矩阵状,来成为阵列化。

219.如图5示出,光检测器100具备,apd401、传输晶体管402、水平信号线403、垂直信号线404、垂直扫描电路406、读出电路407、水平扫描电路408、以及缓冲放大器409。

220.apd401是包括,图2所示的、第一半导体层101、倍增区域301、以及光电转换层302的apd。

221.由apd401光电转换后蓄积的信号电荷即第一电荷,使由垂直扫描电路406选择的行的传输晶体管402接通,经由图1示出的列信号线205以及垂直信号线404,传输到读出电路407。传输晶体管402,例如,由图2示出的分离晶体管201构成。传输到读出电路407的第一电荷,经由缓冲放大器409,输出到后级的信号处理电路(图中未示出)。在信号处理电路执行白平衡等的信号处理后传输到显示器(图中未示出)、存储器(图中未示出)等,例如,成为图像化。

222.优选的是,具备能够将背面偏压v

back

切换为雪崩击穿电压以上的电压va(例如,

‑

20v)、或雪崩击穿电压以下的电压vn(例如,

‑

10v),向apd401有选择地施加电压的电路。

223.据此,例如,在拍摄的对象的照度高的情况下,施加vn,在拍摄的对象的照度低的情况下,施加va来进行拍摄,据此,能够对应从向一个apd401入射一个光子至数光子的非常暗的照度,到入射10000个光子以上的、由一般的相机能够拍摄的照度的拍摄。

224.并且,按每个帧将施加电压切换va以及vn来拍摄,合成图像,从而也能够拍摄动态范围宽的运动图像。

225.如上所述,实施方式1涉及的光检测器100,具备:半导体基板600,具有第一主面s1以及与第一主面s1相反的一侧的第二主面s3;具有第一导电型的第一半导体层101,被形成在半导体基板600的第一主面s1侧;具有第二导电型的第二半导体层102,被形成在半导体基板600的第一半导体层101以及第二主面s3面之间,第二导电型是与第一导电型不同的导电型;以及倍增区域301,在第一半导体层101以及第二半导体层102,对在半导体基板600由光电转换发生的电荷进行雪崩倍增。并且,光检测器100具备:电路区域(具体而言,第一阱104以及第二阱105),在与第一主面s1平行的方向上,与第一半导体层101排列形成;被形成在该电路区域的一个以上的分离晶体管201;被形成在第一半导体层101以及该电路区域之间的分离区域103;被形成在第一半导体层101上的一个以上的第一接触件202;连接第一接触件202以及分离晶体管201的源极的第一布线203;以及读出电路407,与分离晶体管201的漏极连接,读出在第一半导体层101以及第二半导体层102之间由光电转换发生的电荷之中的第一电荷。

226.根据这样的结构,第一半导体层101与第一阱104,由分离区域103电分离。据此,光检测器100能够,确保受光灵敏度,并且,成为细微化。因此,根据光检测器100,能够提高开口率。

227.<变形例>

228.图6是示出本公开的实施方式1涉及的光检测器的变形例1的截面图。

229.变形例涉及的光检测器100c,在像素63具备与光检测器100不同的外延层1i。具体而言,外延层1i与外延层1,第二半导体层102c的平面视中的尺寸不同。更具体而言,变形例涉及的光检测器100c与光检测器100,第二半导体层102c的截面视中的宽度不同。换而言之,变形例涉及的光检测器100c,在与第一主面s1平行的方向上,与光检测器100相比,第二半导体层102c的宽度不同。

230.如此,例如,第二半导体层102c,在平面视中,与第一半导体层101相同的形状,或者,比第一半导体层101宽。并且,第二半导体层102c,也可以由多个像素63共享。

231.根据这样的结构,相对于与半导体基板602的第一主面s1大致平行的方向,电场更均匀,倍增区域301被形成为更宽。具体而言,第二半导体层102c,比第一半导体层101宽。据

此,光检测器100c,开口率更提高,因此,能够更提高光灵敏度。

232.图7是示出图6的viia

‑

viia线上、viib

‑

viib线上、以及viic

‑

viic线上的、光检测器100c的电势的图。

233.如图7示出,可见,在第一半导体层101中,即使位置在与第一主面s1平行的方向上变化,电势的变化的方法也几乎不变化。因此,相对于与半导体基板602的第一主面s1大致平行的方向,电场更均匀,倍增区域301被形成为更宽。具体而言,第二半导体层102c,比第一半导体层101宽。据此,光检测器100c,开口率更提高,因此,能够更提高光灵敏度。

234.(实施方式2)

235.接着,参照图8以及图9,说明实施方式2涉及的光检测器的结构。

236.而且,在实施方式2涉及的光检测器的说明中,对于与实施方式1涉及的光检测器实质上相同的构成要素,附上相同的符号,会有省略或简化说明的一部分的情况。

237.并且,对于实施方式2涉及的光检测器的周边电路结构,例如,也可以与图5示出的实施方式1涉及的光检测器100的电路结构同样,省略说明。

238.图8是示出本公开的实施方式2涉及的光检测器100a的平面图。图9是示出图8的ix

‑

ix线的、本公开的实施方式2涉及的光检测器100a的截面图。

239.实施方式2涉及的光检测器100a具备的像素6a具有的第二半导体层102a,从第一半导体层101a的下面形成到生长面s2,在外延层1a的深度方向上具有杂质浓度的浓度梯度。

240.外延层1a被形成为,以在生长面s2侧比第一主面s1浓度高的方式,杂质浓度逐渐增大。在此,逐渐增大是指,杂质浓度在深度方向上一定或单调增加,包括杂质浓度成为一定的区域的情况,或者,包括杂质浓度以阶梯状增加的情况。

241.在光电转换层302由光电转换发生的第一电荷,由内建电势,向倍增区域301漂移,在倍增区域301被雪崩倍增。

242.并且,如图9示出,第二半导体层102a被形成为,覆盖半导体基板层3的第一主面s1的全面。具体而言,第二半导体层102a被形成为,在半导体基板(即外延层1a以及半导体基板层3)的、与第一主面s1平行的方向上,在全面扩大。换而言之,第二半导体层102a被形成为,覆盖半导体基板层3的生长面s2的全面。

243.据此,第二半导体层102a中的电场与外延层1a的第一主面s1大致垂直,因此,能够减少第一电荷的向横方向(即,与第一主面s1平行的方向)的移动。因此,光检测器100a成为高灵敏度化。并且,光检测器100a成为低混合色化。

244.接着,参照图10,说明第一电荷的电势。

245.图10是示出图9的xa

‑

xa线以及xb

‑

xb线上的、本公开的实施方式2涉及的光检测器100a的电势的图。而且,图10示出的实线是,图9中的xa

‑

xa线上的电势,第一半导体层101a、倍增区域301以及光电转换层302的电势。

246.如图10示出,光电转换层302的第一电荷的电势梯度,由内建电势形成。因此,在光电转换层302的上下方向的两端,电势几乎不变化。

247.据此,雪崩击穿电压,与倍增区域301的上下方向的两端的电势的差一致。具有这样的电势,据此,与专利文献2以及专利文献3所记载的、以往的结构例的拉通型的apd相比,雪崩击穿电压减少。

248.例如,第一半导体层101a的杂质浓度为,10

19

cm

‑3,倍增区域301中的第二半导体层102a的杂质浓度为,10

16

cm

‑3以上。

249.据此,雪崩击穿电压减少为20v。

250.并且,在与外延层1的第一主面s1大致平行的面内,第一电荷的电势大致恒定。

251.据此,在光电转换层302内,xa

‑

xa线上、与xb

‑

xb线上的第一电荷电势一致。因此,xb

‑

xb线上的杂质浓度曲线(杂质浓度分布),能够由比倍增区域301浅的区域的杂质浓度的曲线控制,因此,能够简单地减少分离区域103的电势差异。据此,光检测器100a的成品率提高。

252.并且,在制造像素6a成为阵列化的、apd图像传感器的情况下,像素6a间的暗电流以及暗计数的差异减少。因此,根据具备多个像素6a的光检测器100a,能够输出差异少的图像。

253.尤其优选的是,与分离区域103的横方向(与第一主面s1平行的方向)的耗尽层宽度(即,分离区域103的宽度的一半左右)相比,倍增区域301的纵方向(与第一主面s1垂直的方向)的耗尽层的宽度宽。根据这样的结构,容易缓和倍增区域301的端部的电场集中,容易使电场强度均匀。因此,能够扩大雪崩倍增的区域,容易提高光灵敏度。

254.接着,参照图11以及图12,说明光检测器100a的杂质浓度。

255.图11是示出图9的xa

‑

xa线上的、本公开的实施方式2涉及的光检测器100a的杂质浓度曲线的图。

256.在第一半导体层101a中,以第一主面s1不成为耗尽的方式,第一主面s1附近以高浓度的杂质浓度形成,随着朝向深度方向,倍增区域301中的杂质浓度减少。并且,在第一半导体层101a与第二半导体层102a之间,形成pn结。

257.另一方面,第二半导体层102a,随着朝向深度方向,杂质浓度逐渐增加。

258.据此,能够使第一电荷从光电转换层302向倍增区域301漂移。

259.并且,在这样的杂质浓度曲线的情况下,优选的是,第一半导体层101a的杂质浓度,比第二半导体层102a的杂质浓度大,并且,第二半导体层102a,比第一半导体层101a浅。具体而言,第一半导体层101a与第二半导体层102a的分界面,被形成在比第二半导体层102a的上表面的一部分,更靠近第二主面s3侧。

260.并且,在包括第一半导体层101a与第二半导体层102a的分界面的区域,第一半导体层101a的杂质浓度,比第二半导体层102a的杂质浓度大。

261.并且,倍增区域301内的第二半导体层102a的杂质浓度的浓度梯度,比光电转换层302内的第二半导体层102a的杂质浓度的浓度梯度小即可。具体而言,第二半导体层102a的杂质浓度的梯度,与外延层1a的表面即第一主面s1侧相比,在半导体基板层3的背面侧即第二主面s3侧,更陡峭。

262.根据这些结构,雪崩击穿电压难以依赖于第一半导体层101a的浓度以及深度。因此,雪崩击穿电压的差异减少。并且,据此,光检测器100a的受光灵敏度的差异减少。

263.并且,第二半导体层102a的杂质浓度的浓度梯度,在外延层1a的深的区域大,在外延层1a的浅的区域小即可。具体而言,第二半导体层102a的杂质浓度的梯度,与外延层1a的表面即第一主面s1侧相比,在半导体基板层3的背面侧即第二主面s3侧,更陡峭。

264.据此,能够使在光电转换层302的深的区域发生的第一电荷,以更高速度漂移,使

在光电转换层302的浅的区域发生的第一电荷,以更低速度漂移。因此,响应时间的差异减少。并且,混合色更减少。

265.并且,第二半导体层102a的杂质浓度分布,在与外延层1a的第一主面s1平行的方向上,大致恒定即可。

266.根据这样的结构,分离区域103的电势,更稳定。

267.图12是示出图9的xa

‑

xa线上的、本公开的实施方式2涉及的光检测器100a的杂质浓度曲线的变形例的图。

268.图12示出的杂质浓度分布,与图11示出的杂质浓度分布不同,第一半导体层101a的杂质浓度,从外延层1a的表面相对于深度方向一次增加,进一步,随着朝向深度方向减少。如此,第一半导体层101a的杂质浓度具有,随着朝向深度方向增加的区域。

269.据此,能够抑制在外延层1a的第一主面s1发生的电荷热扩散到倍增区域301。因此,根据这样的杂质浓度分布,能够更减少暗电流以及暗计数。

270.接着,参照图13以及图14,说明像素6a成为阵列化时的光检测器100a的电流电压特性。

271.图13是示出本公开的实施方式2涉及的光检测器100a的电流电压特性的一个例子的图。图14是用于说明本公开的实施方式2涉及的光检测器100a的雪崩击穿电压的差异减少效果的一个例子的图。

272.如图14示出,在实施方式2涉及的光检测器100a中,雪崩击穿电压,不依赖于光电转换层302的厚度。雪崩击穿电压是,例如24v。

273.另一方面,在专利文献2、以及专利文献3公开的结构的拉通型的apd中,如图14示出的比较例,在光电转换层302的厚度为5μm的情况下(图13示出的比较例1),雪崩击穿电压为37v,在光电转换层302的厚度为15μm的情况下(图13示出的比较例2),雪崩击穿电压为64v。

274.如此,根据实施方式2涉及的光检测器100a,能够减少雪崩击穿电压。

275.在实施方式2中,在光电转换层302的厚度为5μm的情况下,也在光电转换层302的厚度为15μm的情况下,雪崩击穿电压为24v,雪崩击穿电压的标准差为0.15v。另一方面,在专利文献2以及专利文献3的结构的拉通型的apd中,在光电转换层302的厚度为5μm的情况下,雪崩击穿电压为37v,雪崩击穿电压的标准差为0.62v。并且,在光电转换层302的厚度为15μm的情况下,雪崩击穿电压为64v,雪崩击穿电压的标准差为4.7v。

276.如此,根据实施方式2涉及的光检测器100a,能够减少雪崩击穿电压的差异。因此,在多个像素6a成为阵列化的情况下,能够减少各个像素6a的受光灵敏度的差异。进一步,根据实施方式2涉及的光检测器100a,成品率更提高。并且,根据实施方式2涉及的光检测器100a,能够减少制造成本。

277.在此,第一阱104是,第一导电型,在第一阱104与第一半导体层101a的边界,杂质浓度比第一半导体层101a低即可。

278.根据这样的结构,能够减少第一阱104中发生的电场以及电流。因此,能够减少驱动光检测器100a时的电力消耗。

279.并且,第一阱104被形成为,比第一半导体层101a更接近于第二主面s3的一侧即可。

280.根据这样的结构,能够更减少第一阱104中发生的电场。因此,能够更减少电力消耗。

281.而且,第一阱104浅的区域由砷形成,深的区域由磷形成即可。与砷相比磷的热扩散系数大,因此,因热处理而磷扩散,在第二半导体层102a与第一阱104的边界,第一阱104的浓度降低,电场强度降低。据此,第一阱104中流动的电流减少,能够减少电力消耗。

282.[外延层以及半导体层的变形例]

[0283]

接着,参照图15至图22,说明实施方式2涉及的光检测器100a的外延层以及半导体层的变形例。

[0284]

<变形例1>

[0285]

图15是示出本公开的实施方式2涉及的光检测器100a的变形例1的平面图。图16是示出图15的xvi

‑

xvi线的、本公开的实施方式2涉及的光检测器100a的变形例1的截面图。图17是示出图16的xviia

‑

xviia线上的、本公开的实施方式2涉及的光检测器100a的变形例1的杂质浓度曲线的图。

[0286]

如图16示出,实施方式2涉及的光检测器100a的变形例1的像素6c的外延层1c,除了实施方式2涉及的光检测器100a的像素6a的结构以外,还具备第四半导体层107。

[0287]

第四半导体层107,被形成在第一半导体层101a与第二半导体层102a之间。并且,第四半导体层107具有第二导电型。

[0288]

并且,如图17示出,第四半导体层107,在倍增区域301中,具有比第二半导体层102a高浓度的杂质浓度。在此情况下,第四半导体层107,成为耗尽即可。

[0289]

根据这样的结构,倍增区域301中发生的电场大。因此,能够更减少雪崩击穿电压。

[0290]

<变形例2>

[0291]

图18是示出本公开的实施方式2涉及的光检测器100a的变形例2的平面图。图19是示出图18的xix

‑

xix线的、本公开的实施方式2涉及的光检测器100a的变形例2的截面图。图20是示出图19的xxa

‑

xxa线上的、本公开实施方式2涉及的光检测器100a的变形例2的杂质浓度曲线的图。

[0292]

如图19示出,实施方式2涉及的光检测器100a的变形例2的像素6d,与变形例1的像素6c同样,具备第四半导体层107a。

[0293]

在第一半导体层101b之下,形成有第四半导体层107a以及分离区域103。在第四半导体层107a以及分离区域103之下,形成有第二半导体层102b。也就是说,在像素6d的外延层1d中,第一半导体层101b与第二半导体层102b被形成为,不直接接触。

[0294]

并且,如图20示出,第四半导体层107a,在倍增区域301中,具有比第二半导体层102b高浓度的杂质浓度。

[0295]

根据这样的结构,倍增区域301中发生的电场也大。因此,能够更减少雪崩击穿电压。

[0296]

<变形例3>

[0297]

图21是示出本公开的实施方式2涉及的光检测器的变形例3的平面图。图22是示出图21的xxii

‑

xxii线的、本公开的实施方式2涉及的光检测器的变形例3的截面图。

[0298]

光检测器1003,在外延层1g具有的第一半导体层101c具有,导电型与第一半导体层101c不同的层即第二导电型层700。具体而言,光检测器1003,在半导体基板601的比倍增

区域301更位于第一主面s1侧的第一半导体层101c内部具有第二导电型的第二导电型层700。更具体而言,第一半导体层101c包括,与半导体基板601的第一主面s1接触的第二导电型层700。

[0299]

第二导电型层700,与接触件701(电极)连接,经由接触件701被施加电压。第二导电型层700,被施加比第一半导体层101c低的电压。也就是说,第二导电型层700与第一半导体层101c,成为逆向偏压的关系。在此,在第二导电型层700与第一半导体层101c,被施加击穿不发生的程度的逆向偏压。据此,因第一主面s1中存在的缺陷而发生的电荷,从接触件701排出到半导体基板601的外部。因此,能够减少作为噪声的原因的暗电流以及暗计数(dcr)。

[0300]

[像素阵列]

[0301]

接着,参照图23至图35,说明本公开涉及的光检测器具备的像素成为阵列化时的像素阵列的配置布局。而且,在图23至35中,示出像素阵列具有的第一半导体层、分离晶体管、以及垂直信号线等的构成要素,省略示出像素阵列的构成要素的一部分。并且,对于图23至图35示出的像素阵列,也可以采用上述的像素6、63、6a、6c、以及6d的任意一个。也就是说,图23至图35中说明的像素阵列,也可以采用于实施方式1涉及的光检测器100、实施方式2涉及的光检测器100a以及其变形例的任意一个。

[0302]

并且,在图23至图33中,为了说明,会有对作为功能相同的构成要素,附上相同的符号的情况。例如,对于第一半导体层,即使在各个像素阵列中形状不同的情况下,也将符号全部设为101来进行说明。关于分离晶体管、垂直信号线等的其他的构成要素,也会有分别附上共同的符号进行说明的情况。并且,在图34以及图35中,将第一半导体层作为第一半导体层101a示出。

[0303]

<第1例>

[0304]

图23是示出本公开涉及的光检测器的像素的配置布局的第1例的平面图。

[0305]

在图23示出的像素阵列10中分别包括,至少两个以上的第一半导体层101、第一阱104、第二阱105、以及分离晶体管201。一个第二阱105包括一个分离晶体管201。

[0306]

并且,相邻的第一半导体层101之间由分离区域103分离。分离区域103被耗尽。

[0307]

在此,在相邻的第一半导体层101之间,以及在第一半导体层101与第一阱104之间,将分离区域103的电势设为大致一致即可。

[0308]

并且,将相邻的第一半导体层101之间的宽度,以及第一半导体层101与第一阱104之间的宽度设为大致一致即可。特别是,第一半导体层101与第一阱104由相同的掩模形成,从而能够减少第一半导体层101与第一阱104的位置偏差,能够减少每个像素的暗电流的差异。

[0309]

<第2例>

[0310]

图24是示出本公开涉及的光检测器的像素的配置布局的第2例的平面图。

[0311]

图24示出的像素阵列11具备,与四个不同第一半导体层101连接的四个分离晶体管201。四个分离晶体管201,被形成在相同的第二阱105内。

[0312]

据此,能够缩小第二阱105的面积,据此,能够将第一半导体层101的面积形成为更宽,因此,开口率提高,并且,受光灵敏度提高。

[0313]

<第3例>

[0314]

图25是示出本公开涉及的光检测器的像素的配置布局的第3例的平面图。

[0315]

图25示出的像素阵列12具备,与四个不同第一半导体层101连接的四个分离晶体管201。四个分离晶体管201共享漏极。如此,至少两个分离晶体管201,共享与读出电路407(例如,参照图5)连接的漏极。

[0316]

据此,能够更缩小第二阱105的面积。因此,能够将第一半导体层101的面积形成为更宽,因此,开口率更提高,并且,受光灵敏度更提高。

[0317]

<第4例>

[0318]

图26是示出本公开涉及的光检测器的像素的配置布局的第4例的平面图。

[0319]

图26示出的像素阵列13具有,在平面视中呈五边形的第一半导体层101。

[0320]

据此,例如,与第3例所示的、第一半导体层101具有在平面视中呈六个角的形状相比,形成第一半导体层101时使用的保护膜的形状稳定。因此,能够减少形成第一半导体层101时的形状的误差。据此,能够更减少受光灵敏度的差异。

[0321]

<第5例>

[0322]

图27是示出本公开涉及的光检测器的像素的配置布局的第5例的平面图。

[0323]

图27示出的像素阵列14具有,在平面视中呈圆形的第一半导体层101。

[0324]

据此,能够减轻第一半导体层101的端部的电场集中,能够抑制边缘击穿。

[0325]

而且,第一半导体层101的平面视形状,不仅限于上述的四角形、五边形、圆形。第一半导体层101的平面视形状,例如,也可以是椭圆,也可以是三角形。

[0326]

<第6例>

[0327]

图28是示出本公开涉及的光检测器的像素的配置布局的第6例的平面图。

[0328]

图28示出的像素阵列15具有,九个图25示出的像素阵列12。也就是说,像素阵列15是,具有配置为6

×

6的矩阵状的像素的像素阵列。

[0329]

根据这样的结构,第二阱105,分别以隔着两个第一半导体层101的方式而被形成。据此,能够按每两个像素集成垂直信号线404,因此,能够减少基于布线的入射光的反射。因此,受光灵敏度提高。

[0330]

<第7例>

[0331]

图29是示出本公开涉及的光检测器的像素的配置布局的第7例的平面图。

[0332]

图29示出的像素阵列16具有,七个图25示出的像素阵列12、以及像素阵列12具有的四个像素之中的相邻的两个为一组的四个。具体而言,在像素阵列16中,与不同的垂直信号线404连接、且相邻的两个像素阵列12被配置为,在垂直信号线404的延伸方向上偏离一个像素。也就是说,在平面视中,多个第二阱105被配置为交错。

[0333]

根据这样的结构,与第6例同样,第二阱105,分别以隔着两个第一半导体层101的方式而被形成。据此,能够按每两个像素集成垂直信号线404,因此,能够减少基于布线的入射光的反射。因此,受光灵敏度提高。并且,在同一行内或同一列内,欠缺了左下、右上、左上、右下的像素以四像素周期排列,因此,难以按每行或列产生受光灵敏度的差。

[0334]

<第8例>

[0335]

图30是示出本公开涉及的光检测器的像素的配置布局的第8例的平面图。

[0336]

图30示出的像素阵列17,在平面视中呈正六边形。在该正六边形的中心,形成有分离晶体管201被形成的第一阱104以及第二阱105。并且,在平面视中,第一阱104以及第二阱

105,由分别大致梯形的六个第一半导体层101包围。也就是说,像素阵列17具有所谓蜂窝结构。

[0337]

特别是,与六个第一半导体层101连接的六个分离晶体管201,被形成在相同的第二阱105内。换而言之,像素阵列17,在6次旋转对称的图形的旋转中心,形成有第二阱105。

[0338]

如此,本公开涉及的光检测器,在具备多个第一接触件202、以及与多个第一接触件202的任意一个分别连接的多个分离晶体管201的情况下,多个分离晶体管201,被形成在一个电路区域(例如,第一阱104以及第二阱105)内即可。

[0339]

根据这样的结构,本公开的一个形态涉及的光检测器成为更细微化。

[0340]

并且,在本公开涉及的光检测器具备多个分离晶体管201的情况下,多个分离晶体管201之中的至少两个分离晶体管201,共享读出电路407即可。

[0341]

根据这样的结构,本公开的一个形态涉及的光检测器成为更细微化。

[0342]

而且,在图25至图27示出的第3例至第5例中,在4次旋转对称的图形的旋转中心,形成有第二阱105。

[0343]

如此,本公开涉及的像素阵列,以具有m次旋转对称性的n边形为反复周期,以在n边形的内部保持m次旋转对称性的方式,形成n个第一半导体层101,第一阱104以及第二阱105,被形成在n边形的旋转对称中心的周边。而且,n是3以上的自然数,m是2以上的自然数。例如,像素阵列11至14为,n=m=4,像素阵列17为,n=m=6。

[0344]

如此,在平面视中,在具有m(m是2以上的自然数)次旋转对称性的n(n是3以上的自然数)边形内,以保持m次旋转对称性的方式,形成n个第一半导体层101即可。在此情况下,电路区域(第一阱104以及第二阱105),被形成在具有旋转对称性的n边形的旋转对称中心,在该电路区域内,配置n个分离晶体管201即可。

[0345]

据此,本公开涉及的光检测器具备的各个像素能够保持在平面视中对称的形状,因此,能够抑制基于经由读出电路407等读出的电荷形成的图像的变形等。特别是,n越大,在共同的第一阱104以及第二阱105形成的分离晶体管201的数量就越增加,因此,将n设定为更大即可。

[0346]

并且,从对称性的观点来看,n=m即可,将正多边形设为反复周期即可。在此,能够充满无限的平面的正多边形之中的、边的数量最大的图形是,正六边形,因此,以反复周期为正六边形的蜂窝结构(n=m=6)更佳。

[0347]

<第9例>

[0348]

图31是示出本公开涉及的光检测器的像素的配置布局的第9例的平面图。

[0349]

图31示出的像素阵列18具有,七个像素阵列17。

[0350]

根据这样的结构,本公开涉及的光检测器具备的各个像素能够保持对称的形状,因此,能够抑制基于经由读出电路407等读出的电荷形成的图像的变形等。并且,能够更稠密地配置像素,根据像素阵列18的结构,成为更细微化。

[0351]

<第10例>

[0352]

图32是示出本公开涉及的光检测器的像素的配置布局的第10例的平面图。

[0353]

关于图32示出的像素阵列19,在平面视中,以行状形成第一阱104以及第二阱105。并且,在第二阱105内,形成有多个分离晶体管201。以行状排列形成第一阱104以及第二阱105,据此,第一阱104、第二阱105、以及分离区域103的面积减少。据此,能够增大第一半导

体层101的平面视中的面积。因此,根据像素阵列19,开口率更提高,并且,受光灵敏度更提高。

[0354]

<第11例>

[0355]

图33是示出本公开涉及的光检测器的像素的配置布局的第11例的平面图。

[0356]

关于图33示出的像素阵列20,在平面视中,以行状形成第一阱104以及第二阱105。并且,在第二阱105内,形成有多个分离晶体管201。特别是,与第一阱104或第二阱105在附图上下相邻的列的第一半导体层101连接的分离晶体管201,被配置在相同的第二阱105内。以行状排列形成第一阱104以及第二阱105,据此,能够减少第一阱104、第二阱105、以及分离区域103的面积。据此,能够增大第一半导体层101的平面视中的面积。因此,根据像素阵列20,开口率更提高,并且,受光灵敏度更提高。

[0357]

<第12例>

[0358]

图34是示出本公开涉及的光检测器的像素的配置布局的第12例的平面图。图35是示出图34的xxxv

‑

xxxv线的、本公开涉及的光检测器的像素的配置布局的第12例的截面图。

[0359]

图34以及图35示出的像素阵列22具有,以2行2列配置的、三个像素以及一个第一阱104以及第二阱105。

[0360]

据此,像素阵列中包括的像素数庞大,据此,需要将用于形成电路的区域确保为宽,并且,即使在不能缩小第一阱104以及第二阱105的面积的情况下,也难以减少受光灵敏度。特别是,也可以将在信号处理中,用于在形成第一阱104以及第二阱105的区域补充信号,作为图像输出的设备,配置在形成第一阱104以及第二阱105的区域。

[0361]

[电路结构的变形例1]

[0362]

接着,参照图36至图38,说明本公开的一个形态涉及的光检测器的电路结构的变形例1。

[0363]

在图5所示的光检测器100的电路结构中,像素阵列9,与垂直扫描电路406、水平扫描电路408、读出电路407、以及缓冲放大器409连接。然而,本公开涉及的光检测器,不仅限于图5所示的电路结构。

[0364]

图36是示出本公开涉及的光检测器100d的电路结构的变形例1的图。图37是示出本公开涉及的光检测器100d的电路结构的变形例1的具有像素6f的像素阵列23的一个例子的平面图。图38是示出本公开涉及的光检测器100d的电路结构的变形例1的驱动序列的一个例子的图。

[0365]

而且,图36至图38中说明的电路结构,也可以采用于实施方式1涉及的光检测器100、实施方式2涉及的光检测器100a以及其变形例的任意一个。

[0366]

并且,在图36以及图37中,为了说明,会有对作为功能相同的构成要素,附上相同的符号的情况。例如,关于第一半导体层,即使在与实施方式1涉及的光检测器100具备的第一半导体层101的形状不同的情况下,也作为第一半导体层101进行说明。关于第一阱、第二阱等的其他的构成要素,也会有分别附上共同的符号进行说明的情况。并且,对光检测器100d具备的像素阵列21,例如,采用图23至图35示出的像素阵列10至20、22。

[0367]

而且,图38的(a)示出复位晶体管410的栅极电压的时间变化,图38的(b)示出选择晶体管412的栅极电压的时间变化。

[0368]

如图36以及图37示出,电路结构的变形例1的光检测器100d具备,读出电路407、复

位apd的复位晶体管410、放大第一电荷的源极跟随晶体管411、将选择出的列的信号传输给垂直信号线404的选择晶体管412、以及浮置扩散电容413。在此,分离晶体管201,与源极跟随晶体管411对应。

[0369]

并且,如图37示出,复位晶体管410、源极跟随晶体管411、以及选择晶体管412,在平面视中被形成在第二阱105内。

[0370]

如图37示出,复位晶体管410的源极、与源极跟随晶体管411的栅极,由布线连接。并且,源极跟随晶体管411的源极与选择晶体管412的漏极被共享。并且,选择晶体管412的源极,与垂直信号线404连接。

[0371]

根据这些结构,在像素6f内放大基于第一电荷的信号。因此,能够减少后级的电路噪声的影响。

[0372]

而且,源极跟随晶体管411的源极与选择晶体管412的漏极也可以不被共享。

[0373]

图38是读出电路407的驱动方法的一个例子。

[0374]

首先,使复位晶体管410接通,将第一半导体层101复位为vdd。

[0375]

然后,使复位晶体管410截止,使选择晶体管412接通,经由源极跟随晶体管411,读出apd的电位。此时的信号,保存在位于后级的存储器等的电路(图中未示出)。

[0376]

在使复位晶体管410截止后经过曝光时间δt之后,使选择晶体管412接通,经由源极跟随晶体管411,读出apd的电位,取与刚刚复位后的信号的差分。

[0377]

据此,除去与信号重叠的背景噪声。

[0378]

[电路结构的变形例2]

[0379]

接着,参照图39至图42,说明本公开的一个形态涉及的光检测器的电路结构的变形例。

[0380]

在图5所示的光检测器100的电路结构中,像素阵列9,与垂直扫描电路406、水平扫描电路408、读出电路407、以及缓冲放大器409连接。然而,本公开涉及的光检测器,不仅限于图5所示的电路结构。

[0381]

图39是示出本公开涉及的光检测器100b的电路结构的变形例2的图。图40是示出本公开涉及的光检测器100b的电路结构的变形例2的具有像素6e的像素阵列23a的一个例子的平面图。图41是示出本公开涉及的光检测器的电路结构的变形例2的具有像素6e的像素阵列23a的另一个例子的平面图。图42是示出本公开涉及的光检测器100b的电路结构的变形例2的驱动序列的一个例子的图。

[0382]

而且,图42的(a)示出复位晶体管410的栅极电压的时间变化,图42的(b)示出传输晶体管402的栅极电压的时间变化,图42的(c)示出选择晶体管412的栅极电压的时间变化。

[0383]

而且,图39至图42中说明的电路结构,也可以采用于实施方式1涉及的光检测器100、实施方式2涉及的光检测器100a以及其变形例的任意一个。

[0384]

并且,在图40以及图41中,为了说明,会有对作为功能相同的构成要素,附上相同的符号的情况。例如,关于第一半导体层,即使在与实施方式1涉及的光检测器100具备的第一半导体层101的形状不同的情况下,也作为第一半导体层101进行说明。关于第一阱、第二阱等的其他的构成要素,也会有分别附上共同的符号进行说明的情况。并且,对光检测器100b具备的像素阵列23或像素阵列23a,例如,采用图23至图35示出的像素阵列10至20、22。

[0385]

如图39以及图40示出,电路结构的变形例的光检测器100b具备,读出电路407、复

位分离晶体管201的漏极的复位晶体管410,放大第一电荷的源极跟随晶体管411、将选择出的列的信号传输给垂直信号线404的选择晶体管412、以及浮置扩散电容413。

[0386]

并且,如图40示出,复位晶体管410、源极跟随晶体管411、以及选择晶体管412,在平面视中被形成在第二阱105内。

[0387]

而且,关于分离晶体管201,如图40示出的像素阵列23,也可以与位于附图左右两侧的第一半导体层101分别电连接,如图41示出的像素阵列23a,也可以仅与位于附图左右两侧的第一半导体层101的一方电连接。

[0388]

如图41示出,分离晶体管201的漏极、复位晶体管410的源极、以及源极跟随晶体管411的栅极,由布线连接。并且,源极跟随晶体管411的源极与选择晶体管412的漏极被共享。并且,选择晶体管412的源极,与垂直信号线404连接。

[0389]

根据这些结构,在像素6e内放大基于第一电荷的信号。因此,能够减少后级的电路噪声的影响。

[0390]

而且,源极跟随晶体管411的源极与选择晶体管412的漏极也可以不被共享。

[0391]

并且,如图40示出,由两个分离晶体管201,共享漏极。分离晶体管201的漏极、复位晶体管410的源极、以及源极跟随晶体管411的栅极,由布线连接。并且,源极跟随晶体管411的源极与选择晶体管412的漏极被共享。并且,选择晶体管412的源极,与垂直信号线404连接。

[0392]

根据这些结构,在像素6e内放大基于第一电荷的信号。因此,能够减少后级的电路噪声的影响。

[0393]

图42是,读出电路407的驱动方法的一个例子,示出相关双采样的驱动。

[0394]

首先,使复位晶体管410(图42的(a))以及传输晶体管402(图42的(b))接通,将第一半导体层101复位为vdd。

[0395]

然后,使复位晶体管410以及传输晶体管402截止,使选择晶体管412(图42的(c))接通。此时的信号,保存在位于后级的存储器等的电路(图中未示出)。

[0396]

在使复位晶体管410以及传输晶体管402截止后经过曝光时间δt之后,使分离晶体管201接通,据此,蓄积在第一半导体层101的第一电荷,传输到浮置扩散电容413。

[0397]

然后,使选择晶体管412接通,经由源极跟随晶体管411,读出浮置扩散电容413的电位,取与刚刚复位后的信号的差分。

[0398]

据此,除去与信号重叠的背景噪声。

[0399]

[封装体]

[0400]

接着,参照图43至图45,说明本公开涉及的光检测器的封装体结构。

[0401]

而且,图43至图45中说明的封装体结构,也可以采用于实施方式1涉及的光检测器100、实施方式2涉及的光检测器100a以及其变形例的任意一个。而且,在图43至图45中,作为一个例子,示出图9示出的像素6a配置在封装体的例子。

[0402]

并且,图43至图45是示出,例如与图8的ix

‑

ix线对应的截面的截面图。

[0403]

<第1例>

[0404]

图43是示出本公开涉及的光检测器30的第1例的截面图。

[0405]

光检测器30具备,像素6a、以及封装体pkg1。

[0406]

封装体pkg1是,安装像素6a的封装体。pkg1具备,与外部商用电源等的外部的电源

b电连接的金属板501。

[0407]

金属板501,被形成在成为封装体pkg1的母体材料的树脂材料等的成型物上,与半导体基板层3的第二主面s3接触并连接。金属板501,为了能够排除由雪崩倍增发生的电荷,而需要与半导体基板层3欧姆接触。并且,金属板501的尺寸,更小即可。特别是,需要将封装体pkg1上的金属板501与半导体基板层3之间的接触电阻设为,0.1ω至10ω左右。为了实现该情况,用于金属板501的金属的种类为,ag、au、cu、al、ta、pt、ti、tin、si等即可。

[0408]

如图43示出,光检测器30也可以是,从封装体pkg1上的金属板501向半导体基板层3直接施加电压的结构。

[0409]

据此,能够向半导体基板层3的第二主面s3全面施加背面偏压v

back

。因此,根据光检测器30,能够使施加的电压均匀,在将光检测器30用于图像传感器的情况下,能够抑制画质的差异。

[0410]

<第2例>

[0411]

图44是示出本公开涉及的光检测器31的第2例的截面图。

[0412]

光检测器31,与光检测器30,仅半导体基板层3的厚度不同。

[0413]

在此,光检测器31是,使半导体基板层3变薄、且使透过像素6a的光在封装体pkg1的金属板501反射的结构即可。

[0414]

据此,能够由第一半导体层101a以及第二半导体层102a对在金属板501反射的光即反射光进行光电转换。也能够将由该光电转换而发生的电荷,作为信号检测。因此,光检测器31的受光灵敏度,更提高。特别是,硅相对于近红外光的吸收系数小,透过像素6a的光多。例如,在光检测器31,检测具有940nm的峰值波长的光的情况下,在外延层1a以及半导体基板层3的厚度为10μm时,入射的光之中的80%的光不被光电转换而透过像素6a。因此,根据图44的结构,能够再次对在金属板501反射的光进行光电转换,因此,能够将受光灵敏度提高为1.8倍。

[0415]

而且,也可以对半导体基板层3,利用soi(silicon on insulator)基板。在此情况下,即使不进行半导体基板层3的背面研磨等的加工,也能够使外延层1a以及半导体基板层3变薄。因此,没有半导体基板层3的背面(第二主面s3)的加工损坏,从半导体基板层3的背面发生的噪声减少,因此,能够实现低噪声化。

[0416]

<第3例>

[0417]

图45是示出本公开涉及的光检测器32的封装体pkg2的第3例的截面图。

[0418]

光检测器32具备,像素6a以及封装体pkg2。封装体pkg2具备,金属板501a以及金属线501b。

[0419]

像素6a,以布线层2为下的方式,被配置在成为封装体pkg2的母体材料的树脂材料等的成型物上。也就是说,光检测器32是,背面照射型(back side illumination/bsi)的光检测器。

[0420]

在半导体基板层3的第二主面s3,形成有透明的电极即透明金属4。对于透明金属4,例如,采用ito(indium tin oxide)等。

[0421]

并且,在布线层2下,为了加强像素6a,而接合有支撑基板5。像素6a,经由支撑基板5与封装体pkg2接合。对于支撑基板5的材料,没有特别的限定,但是,例如,采用金属基板、陶瓷基板等。

[0422]

电源b,经由金属板501a以及金属线501b,与透明金属4电连接。也就是说,背面偏压v

back

,从电源b,经由封装体pkg2具有的金属板501a以及金属线501b提供到透明金属4。

[0423]

对于金属板501a以及金属线501b的材料,没有特别的限定,但是,例如,采用ag、au、cu、al、ta、pt、ti、tin、si等。

[0424]

(制造方法)

[0425]

接着,参照图46至图52,说明本公开涉及的光检测器的制造方法。

[0426]

图46至图52是,用于说明本公开涉及的光检测器的制造方法的截面图。

[0427]

如图46示出,首先,在生长基板702上形成外延层703。生长基板702是,例如,第二导电型的si基板,形成由在si基板上外延生长的si构成的外延层703。

[0428]

接着,向外延层703注入硼,从而形成第二半导体层704。

[0429]

如图47示出,接着,向外延层703注入磷或砷的任意一个、或双方,从而在第二半导体层704上形成第一半导体层705。

[0430]

如图48示出,接着,在与第一半导体层705以及第二半导体层704相邻的位置,在外延层703的上面(图48的附图上侧)形成阱706。在阱706,例如,形成图2示出的第一阱104以及第二阱105等的像素区域。

[0431]

如图49示出,接着,在阱706上形成栅极电极707。对栅极电极707采用的材料是,例如,多晶硅、铝、ti等。

[0432]

如图50示出,接着,在外延层703的表面形成绝缘膜708。对于绝缘膜708的形成,例如,采用cvd(chemical vapor deposition)法、以及cmp(chemical mechanical polishing)法。

[0433]

如图51示出,接着,形成与阱706连接的接触件709(电极),并且,形成与第一半导体层705连接的接触件709。对接触件709采用的材料是,例如,w、ti、tin、ni等,对接触件709的形成,例如,采用光刻、干蚀、金属cvd法、以及cmp法。

[0434]

如图52示出,接着,形成将与阱706连接的接触件709、以及与第一半导体层705连接的接触件709连接的第一布线710,进一步,形成使图51示出的绝缘膜708变厚的绝缘膜711,从而在外延层703的上面)形成布线层(例如,图2示出的布线层2)。

[0435]

而且,对于图46至图52示出的本公开涉及的光检测器的制造工序,例如,采用一般的双镶嵌法。双镶嵌法是,例如,包括形成薄的绝缘膜708的cvd法、在形成的薄的绝缘膜708形成槽的光刻以及干蚀、形成接触件709的pvd(physical vapor deposition)或cvd法、形成第一布线710的cu镀金法、以及使绝缘膜708变厚来形成绝缘膜711的cmp法的成膜方法。

[0436]

(实施方式3)

[0437]

接着,参照图53至图56,说明实施方式3涉及的光检测器的结构。

[0438]

而且,在实施方式3涉及的光检测器的说明中,对于与实施方式1以及2涉及的光检测器实质上相同的构成要素,附上相同的符号,会有省略或简化说明的一部分的情况。

[0439]

图53是示出本公开的实施方式3涉及的光检测器1000的平面图。图54是示出图53的liv

‑

liv线的、本公开的实施方式3涉及的光检测器1000的截面图。

[0440]

而且,在图53以及图54中示出,光检测器1000具备的构成要素之中的、第一半导体层101、分离区域1030(第一分离区域)、以及第一布线203的一部分即列信号线等的光检测器1000具备的像素60,省略示出光检测器1000的结构的一部分。例如,在图53中,省略示出

与第一布线203连接的布线等的一部分的构成要素。而且,在以后的说明中的其他的图中,也会有省略示出本公开涉及的光检测器的结构的一部分的情况。

[0441]

实施方式3涉及的光检测器1000是,利用apd(avalanche photo diode)的光检测传感器,具备具有外延层(半导体基板)1h以及半导体基板层3的半导体基板6000、以及布线层2。具体而言,光检测器1000具备,第二导电型的外延层1h、形成在半导体基板6000(更具体而言,外延层1h)的第一主面s1上的布线层2、以及形成在外延层1h的背面侧的半导体基板层3。

[0442]

半导体基板6000具有,外延层1h、以及半导体基板层3。

[0443]

外延层1h具备,至少一个第一导电型的第一半导体层101、第二导电型的第二半导体层102、将在外延层1h由光电转换发生的电荷在第一半导体层101以及第二半导体层102进行雪崩倍增的倍增区域301、以及至少分离两个倍增区域301的分离区域1030。

[0444]

第一半导体层101是,形成在外延层1h的第一主面s1侧的具有第一导电型的半导体层。在第一半导体层101上,形成有第一接触件202。

[0445]

第二半导体层102,被形成在第一半导体层101以及半导体基板层3之间。并且,第二半导体层102具有,与第一导电型相反的导电型的第二导电型。第二半导体层102,在与第一半导体层101之间对光电转换后的电荷进行雪崩倍增。

[0446]

布线层2是,包括形成在第一半导体层101的第一主面s1的电极即第一接触件202、以及金属布线即第一布线203的层。

[0447]

半导体基板层3是,用于形成外延层1h的生长基板。半导体基板层3具有,用于形成外延层1h的生长面s2以及生长面s2的相反侧的第二主面s3。在半导体基板层3的背面,即,在半导体基板6000的背面即第二主面s3,形成有背面电极即第二接触件204。若背面偏压v

back

施加到半导体基板层3,则经由半导体基板层3,外延层1h的生长面s2侧的电压,固定为v

back

。

[0448]

在第一半导体层101与第二半导体层102之间,形成与外延层1h的第一主面s1大致平行的倍增区域301。

[0449]

倍增区域301是,将接受的光(图54示出的hν)光电转换而生成的电荷由雪崩倍增来倍增的区域。

[0450]

倍增区域301的电场的大小是,例如,3至5

×

105v/cm,第一半导体层101以及第二半导体层102的杂质浓度是,例如,10

16

cm

‑3至10

20

cm

‑3,外延层1的杂质浓度是,例如,10

14

cm

‑3至10

16

cm

‑3。

[0451]

并且,在此情况下,倍增区域301的深度方向的电势变化量是,例如,20v。

[0452]

而且,在本说明书的各个图中,将本公开涉及的光检测器接受的光(即,入射光)记载为hν。

[0453]

在层叠在倍增区域301下的光电转换层302由光电转换而发生的第二导电型的电荷的载流子即第二电荷,若由漂移到达倍增区域301,则由雪崩倍增,载流子数倍增为1倍至10万倍。此时,由光电转换以及雪崩倍增而发生的第一导电型的载流子即第一电荷,蓄积在第一半导体层101。并且,由光电转换以及雪崩倍增而发生的第二电荷,漂移到第二接触件204,排出到光检测器1000的外侧。也就是说,在第一半导体层101以及第二半导体层102之间由光电转换而发生的电荷之中的、极性与第一电荷不同的第二电荷,经由第二接触件

204,向半导体基板层3的外部流动。

[0454]

在此,优选的是,第二接触件204,被形成在第二主面s3全面。第二接触件204是,形成在第二导电型的半导体层(第二半导体层102)、或背面(即,第二主面s3)的导电性的材料。

[0455]

例如,也可以将用于使外延层1h生长的生长基板即半导体基板层3作为第二接触件204利用。或者,第二接触件204也可以,将第二导电型的半导体层由利用杂质扩散、或离子注入等的方法的载流子密度的调整形成。

[0456]

并且,也可以从形成在半导体基板6000的第一主面s1侧的图中未示出的接触件,经由半导体基板6000向第二接触件204施加电压。

[0457]

据此,作为信号不利用的第二电荷,在短时间内排出到光检测器1000的外侧。因此,能够抑制光检测器1000内部的电压的时间变化以及空间上的不均匀的发生,因此,光检测效率提高。

[0458]

并且,蓄积在第一半导体层101的第一电荷,从半导体基板6000具有的第一半导体层101以及第二半导体层102,经由第一接触件202,传输到读出电路407(参照图12),被处理为信号。据此,光检测器1000,检测入射光。

[0459]

而且,读出电路407的结构,没有特别的限定。读出电路407是,例如,电流放大器或ad(analog to digital)转换电路。

[0460]

而且,也可以是第一导电型为正的导电型(即,p型),第二导电型为负的导电型(即,n型)的结构,但是,将第一导电型设为负的导电型,将第二导电型设为正的导电型即可。换而言之,第一电荷是电子,第二电荷是空穴即可。

[0461]

电子的电离率,比空穴的电离率大,因此,容易产生雪崩倍增。因此,根据这样的结构,光检测器1000的受光灵敏度提高。

[0462]

特别是,在实施方式3涉及的光检测器1000,在分离区域1030上,不形成接触件以及sti(shallow trench isoration),并且,分离区域1030被耗尽且不定电位。具体而言,在形成第一半导体层101以及分离区域1030的区域,没有形成sti。

[0463]

据此,能够缩小分离区域1030的宽度,因此,能够提高光检测器1000的开口率。

[0464]

在专利文献4以及以及专利文献8等所记载的spad(single photon avalanche diode)中,在分离区域形成接触件,因此,在雪崩倍增区域的端部,发生与半导体基板的表面水平的方向的电场,电场集中于雪崩倍增区域的端部。为了防止该电场集中,而形成所谓保护环结构,缓和电场,因此,分离区域扩大,据此,倍增区域缩小。

[0465]

另一方面,在本实施方式中,在分离区域103没有形成sti或接触件,因此,即使没有保护环,也能够抑制横方向的电场。据此,没有电场集中,因此,能够扩大倍增区域301,能够提高光灵敏度。

[0466]

尤其优选的是,与分离区域1030的横方向(与第一主面s1平行的方向)的耗尽层宽度(即,分离区域1030的宽度的一半左右)相比,倍增区域301的纵方向(与第一主面s1垂直的方向)的耗尽层的宽度宽。根据这样的结构,容易缓和倍增区域301的端部的电场集中,容易使电场强度均匀。因此,能够扩大雪崩倍增的区域,容易提高光灵敏度。

[0467]

并且,分离区域1030的宽度是,例如,0.1μm至1μm,杂质浓度是,10

15

cm

‑3至10

18

cm

‑3。分离区域1030的电位,由第一半导体层101的电位、以及背面偏压v

back

决定。

[0468]

在此,若第一半导体层101与分离区域1030的电位差小,则饱和电子数变小,容易发生向相邻像素的电荷漏出,若第一半导体层101与分离区域1030的电位差v大,则在设备表面(例如,第一主面s1)发生的电场变大,存在暗电流以及暗计数(dcr)增大的问题。因此,优选的是,第一半导体层101与分离区域1030的电位差为,0.1至10v左右。

[0469]

并且,实施方式3的光入射面是,外延层1h的第一主面s1面。

[0470]

据此,不需要使用背面加工等的特殊过程,能够减少成本。特别是,近红外光等的长波长的光,吸收系数低,不衰减直到半导体基板层3附近为止,因此,即使光电转换层302被形成在离外延层1h的第一主面s1远的区域,与被形成在第一主面s1附近时比较的受光灵敏度也几乎不变化。例如,针对波长在近红外区的太阳光的谱强度为极小的940nm的光的si(硅)的吸收系数为,1%/μm,因此,即使光电转换层302被形成在从第一主面s1深1μm,受光灵敏度的降低也是1%。

[0471]

而且,也可以在布线层2中的、倍增区域301上设置光波导,进一步,在布线层2上设置微透镜。据此,能够提高聚光效率。

[0472]

接着,参照图55以及图56,说明第一电荷的电势。

[0473]

图55是示出图54的lva

‑

lva线上以及lvb

‑

lvb线上的、本公开的实施方式3涉及的光检测器1000的电势的图。图56是示出图54的lvc

‑

lvc线上的、本公开的实施方式3涉及的光检测器1000的电势的图。

[0474]

而且,图55示出的实线是,图54中的lva

‑

lva线上的电势,第一半导体层101、倍增区域301以及光电转换层302的电势。

[0475]

第一半导体层101,与读出电路407(例如,参照图5)连接,至少暂时固定为读出电路407的电源电压v

dd

。另一方面,外延层1h的生长面s2侧,经由半导体基板层3,固定为v

back

。

[0476]

而且,光电转换层302被耗尽,并且,形成有使电荷向倍增区域301漂移的电势梯度即可。

[0477]

在使光电转换层302被耗尽的情况下,关于光电转换层302的电势变化量,例如,在光电转换层302的厚度为5μm的情况下,为20v左右,在光电转换层302的厚度为15μm的情况下,为40v左右。

[0478]

而且,以后,在本说明书中,将使倍增区域301产生雪崩倍增的阈值电压被施加时的、第一接触件202与第二接触件204的电压差,称为雪崩击穿电压。在此情况下,例如,在光电转换层302的厚度为5μm时,雪崩击穿电压为40v。

[0479]

如图55示出,lva

‑

lva线上、以及lvb

‑

lvb线上的电势,越朝向深度方向、即深度越大,就越接近v

back

。另一方面,越朝向第一主面s1侧、即深度越浅,lva

‑

lva线上、以及lvb

‑

lvb线上的电势就越增大。例如,lva

‑

lva线上的电势,接近v

dd

。而且,优选的是,lvb

‑

lvb线上的电势,在第一主面s1被耗尽、电位不定。

[0480]

如图56示出,相邻的第一半导体层101,分别被偏压为v

dd

。并且,位于相邻的第一半导体层101之间的分离区域1030被耗尽、不定电位,因此,相邻的第一半导体层101电分离。而且,第一半导体层101与分离区域1030之间的电位差为0.1至10v即可。

[0481]

如此,分离区域1030,通过电势使相邻的两个第一半导体层101、即相邻的倍增区域301分离。并且,分离区域1030的电势,由于分离区域1030被耗尽,因此,比基于因雪崩倍增而发生的电荷的第一半导体层101的电压变化大。

[0482]

光检测器1000,根据上述的结构,能够使分离区域1030成为细微化,扩大倍增区域301,受光灵敏度提高。

[0483]

例如,在像专利文献4那样,不使分离区域1030成为耗尽,设置接触件的情况下,为了确保电分离、且缓和与外延层1h大致平行的方向(即,与第一主面s1平行的方向)的电场,典型而言,在与第一主面s1平行的方向上需要1μm以上的分离宽度。

[0484]

对此,在实施方式3涉及的光检测器1000中,分离区域1030被耗尽。根据使分离区域1030成为耗尽的效果,第一半导体层101与分离区域1030之间的电场减少。因此,能够将分离宽度狭窄到0.1μm至1μm。也就是说,根据光检测器1000,能够扩大倍增区域301的面积来提高开口率,因此,能够提高光灵敏度。

[0485]

如上说明,实施方式3涉及的光检测器1000,具备:半导体基板6000,具有第一主面s1以及与第一主面s1相反的一侧的第二主面s3;具有第一导电型的第一半导体层101,被形成在半导体基板6000的第一主面s1侧;具有第二导电型的第二半导体层102,被形成在半导体基板6000的第一半导体层101以及第二主面s3之间,第二导电型是与第一导电型不同的导电型;倍增区域301,在第一半导体层101以及第二半导体层102,对在半导体基板6000由光电转换发生的电荷进行雪崩倍增;以及分离区域1030,至少使两个倍增区域301分离。

[0486]

根据这样的结构,能够使分离区域1030变窄。因此,能够实现光检测器1000的小型化。

[0487]

并且,根据这样的结构,在光电转换层302发生的电荷,在光电转换层302内漂移,进入倍增区域301,产生雪崩倍增。由光电转换发生的电荷,由雪崩倍增放大,因此,即使在入射光的强度小的情况下,也能够进行光检测。也就是说,根据这样的结构,能够提高光检测器1000的灵敏度(即,受光灵敏度)。

[0488]

并且,例如,光检测器1000还具备,形成在第二主面s3的第二接触件204。在第一半导体层101以及第二半导体层102之间由光电转换发生的第一电荷以及极性与第一电荷不同的第二电荷之中的一方,经由第二接触件204,向半导体基板6000的外部流动。

[0489]

根据这样的结构,例如,由光电转换以及雪崩倍增发生的第二导电型的载流子即第二电荷,经由位于半导体基板6000的背面侧即第二主面s3的第二接触件204,排出到光检测器1000的外部。因此,能够减少半导体基板6000背面的电压的基于时间变化、以及位置的不均匀。据此,能够抑制光检测器1000的光检测效率的空间上以及时间上的差异。

[0490]

并且,例如,分离区域1030,通过电势使相邻的两个倍增区域301分离。

[0491]

根据这样的结构,与形成槽等来形成分离区域1030的情况相比,能够提高开口率,能够提高光灵敏度。并且,能够减少暗电流以及dcr。

[0492]

并且,例如,分离区域1030的电势,比基于由雪崩倍增发生的电荷的第一半导体层101的电压变化大。

[0493]

根据这样的结构,即使在第一半导体层101产生电压变化的情况下,也能够由分离区域1030使相邻的第一半导体层101电分离。

[0494]

并且,例如,分离区域1030被耗尽。

[0495]

根据这样的结构,使分离区域1030成为耗尽,从而能够由短的分离宽度分离两个倍增区域301,并且,缓和分离区域1030的电场。据此,光检测器1000,能够确保受光灵敏度,并且,实现细微化。因此,根据光检测器1000,开口率提高。并且,分离区域103被耗尽,因此,

能够抑制电场集中于倍增区域301。因此,不需要将以往的光检测器中必要的保护环形成在倍增区域301的周围。因此,光检测器1000能够,使分离区域1030更变窄,提高开口率,提高光灵敏度。并且,即使像素60成为细微化,灵敏度也难以降低,因此,容易实现细微化。

[0496]

并且,例如,在形成有第一半导体层101以及分离区域1030的区域,没有形成sti以及接触件。

[0497]

根据这样的结构,能够抑制暗电流的发生。

[0498]

(变形例)

[0499]

接着,说明实施方式3涉及的光检测器1000的变形例。而且,在变形例的说明中,以与光检测器1000不同之处为中心进行说明,对于实质上相同的构成要素,会有附上相同的符号,简化或省略说明的一部分的情况。

[0500]

<变形例1>

[0501]

图57是示出本公开的实施方式3涉及的光检测器的变形例1的截面图。

[0502]

变形例1涉及的光检测器1001,在像素61具备与光检测器1000不同的外延层1e。具体而言,外延层1e,与外延层1h相比,第二半导体层1020的平面视中的尺寸不同。更具体而言,变形例1涉及的光检测器1001,与光检测器1000相比,第二半导体层1020的截面视中的宽度不同。换而言之,变形例1涉及的光检测器1001,在与第一主面s1平行的方向上,与光检测器1000相比,第二半导体层1020的宽度不同。

[0503]

在本实施方式中,在截面视中,第二半导体层1020的宽度(附图横方向),与第一半导体层101大致相同。

[0504]

如此,例如,第二半导体层1020,在平面视中,形状与第一半导体层101相同、或比第一半导体层101宽。

[0505]

根据这样的结构,相对于半导体基板6000的与第一主面s1大致平行的方向,电场更均匀,雪崩倍增区域(倍增区域301)被形成为更宽。具体而言,倍增区域301,在截面视中,宽度与第一半导体层101相同、或宽度比第一半导体层101宽。据此,能够更提高开口率,能够更提高光灵敏度。

[0506]

<变形例2>

[0507]

图58是示出本公开的实施方式3涉及的光检测器的变形例2的截面图。

[0508]

变形例2涉及的光检测器1002,在像素62具备与光检测器1000不同的外延层1f。具体而言,外延层1f,与外延层1h相比,第二半导体层1020a的平面视中的尺寸不同。更具体而言,变形例2涉及的光检测器1002,第二半导体层1020a在平面视中扩展在外延层1f的全面。换而言之,例如,光检测器1002具备多个第一半导体层101,第二半导体层1020a,以在平面视中与多个第一半导体层101重叠的方式连续地形成在半导体基板6001。

[0509]

图59是示出图58的lixa

‑

lixa线上、lixb

‑

lixb线上、以及lixc

‑

lixc线上的、光检测器1002的电势的图。

[0510]

如图59示出,可见,在第一半导体层101中,即使位置在与第一主面s1平行的方向上变化,电势的变化的方法也几乎不变化。因此,相对于半导体基板6001的与第一主面s1大致平行的方向,电场更均匀,倍增区域301被形成为更宽。具体而言,倍增区域301,比第一半导体层101宽。据此,能够更提高开口率,能够更提高光灵敏度。

[0511]

而且,本实施方式3、实施方式1以及/或实施方式2所记载的发明的内容的组合,也

包含在本发明的范围内。

[0512]

具体而言,在本实施方式3中也可以构成为,第二半导体层102、1020、1020a的浓度从半导体基板6000、6001的第一主面s1向第二主面s3逐渐增加。并且,第二半导体层102、1020、1020a也可以由外延生长形成。实施方式1以及2示出的任意的电路结构以及布局,也可以适用于实施方式3。

[0513]

(其他)

[0514]

以上,对于本公开的实施方式涉及的光检测器,根据实施方式1、实施方式2、实施方式3以及各个变形例进行了说明,但是,本公开,不仅限于该实施方式。只要不脱离本公开的宗旨,对本实施方式实施本领域技术人员想到的各种变形的形态,或组合不同的实施方式的构成要素来构成的形态,也可以包含在本公开的一个或多个形态的范围内。

[0515]

本公开涉及的光检测器,能够适用于能够检测微弱的光的受光灵敏度高的cmos(complementary metal oxide semiconductor)图像传感器等。

[0516]

符号说明

[0517]

1、1a、1c、1d、1e、1f、1g、1h、1i

ꢀꢀ

外延层

[0518]2ꢀꢀ

布线层

[0519]3ꢀꢀ

半导体基板层

[0520]4ꢀꢀ

透明金属

[0521]5ꢀꢀ

支撑基板

[0522]

6、6a、6c、6d、6e、6f、60、61、62、63

ꢀꢀ

像素

[0523]

9至20、21、22、23、23a

ꢀꢀ

像素阵列

[0524]

30至32、100、100a、100b、100c、100d、1000、1001、1002、1003

ꢀꢀ

光检测器

[0525]

101、101a、101b、101c

ꢀꢀ

第一半导体层

[0526]

102、102a、102b、1020、1020a

ꢀꢀ

第二半导体层

[0527]

103、1030

ꢀꢀ

分离区域

[0528]

104

ꢀꢀ

第一阱(电路区域)

[0529]

105

ꢀꢀ

第二阱(电路区域)

[0530]

107、107a

ꢀꢀ

第四半导体层

[0531]

201

ꢀꢀ

分离晶体管

[0532]

202

ꢀꢀ

第一接触件

[0533]

203

ꢀꢀ

第一布线

[0534]

204

ꢀꢀ

第二接触件

[0535]

205

ꢀꢀ

列信号线

[0536]

301

ꢀꢀ

倍增区域

[0537]

302

ꢀꢀ

光电转换层

[0538]

401

ꢀꢀ

apd

[0539]

402

ꢀꢀ

传输晶体管

[0540]

403

ꢀꢀ

水平信号线

[0541]

404

ꢀꢀ

垂直信号线

[0542]

406

ꢀꢀ

垂直扫描电路

[0543]

407

ꢀꢀ

读出电路

[0544]

408

ꢀꢀ

水平扫描电路

[0545]

409

ꢀꢀ

缓冲放大器

[0546]

410

ꢀꢀ

复位晶体管

[0547]

411

ꢀꢀ

源极跟随晶体管

[0548]

412

ꢀꢀ

选择晶体管

[0549]

413

ꢀꢀ

浮置扩散电容

[0550]

501、501a

ꢀꢀ

金属板

[0551]

501b

ꢀꢀ

金属线

[0552]

600、601、602、6000、6001

ꢀꢀ

半导体基板

[0553]

700

ꢀꢀ

第二导电型层

[0554]

701

ꢀꢀ

接触件

[0555]

702

ꢀꢀ

生长基板

[0556]

703

ꢀꢀ

外延层

[0557]

704

ꢀꢀ

第二半导体层

[0558]

705

ꢀꢀ

第一半导体层

[0559]

706

ꢀꢀ

阱

[0560]

707

ꢀꢀ

栅极电极

[0561]

708、711

ꢀꢀ

绝缘膜

[0562]

709

ꢀꢀ

接触件

[0563]

710

ꢀꢀ

第一布线

[0564]

b

ꢀꢀ

电源

[0565]

s1

ꢀꢀ

第一主面

[0566]

s2

ꢀꢀ

生长面

[0567]

s3

ꢀꢀ

第二主面

[0568]

pkg1、pkg2

ꢀꢀ

封装体

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1