电子装置的制作方法

1.本发明涉及一种电子装置,特别是将包括基板的电子元件,设置在载板上的电子装置。

背景技术:

2.在电子装置的制造过程中,为了要配合制程条件或制作成本,可能会分别使用不同材质的基板来制造。因此,须面临将不同材质的基板组合的技术问题。

技术实现要素:

3.有鉴于此,有必要提出一种载板组合基板的电子装置,以解决现有电子装置制作时所遭遇的技术问题。根据本发明的实施例可提供一种载板组合基板的电子装置,例如具有耐热性较佳的玻璃基板搭配成本较低的载板,从而具有较佳的材料组合优势。

4.本发明的一种电子装置,包括载板、多个电子元件以及至少一接合端子。载板具有至少一连接垫。多个电子元件设置在载板上。多个电子元件中的一个电子元件包括基板与贯穿基板的基板通孔。至少一接合端子位于基板与载板之间,且多个电子元件经由至少一接合端子电连接至少一连接垫。

附图说明

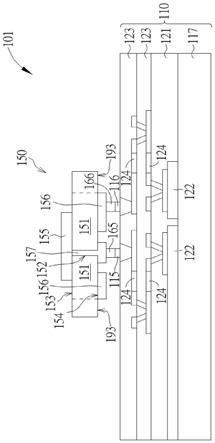

5.图1所示为本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。

6.图2绘示电子装置制程阶段的上视图示意图,图3绘示对应图2的截面图示意图。

7.图4绘示电子装置制程阶段的上视图示意图,图5绘示对应图4的截面图示意图。

8.图6绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。

9.图7绘示电子装置制程阶段的上视图示意图,图8绘示对应图7的上视图示意图。

10.图9绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。

11.图10绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。

12.图11绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。

13.图12绘示对应本发明的图6的变形实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。

14.附图标记说明:100-电子装置;101-电子装置;103-电子装置;104-电子装置;105-电子装置;106-电子装置;110-载板;111-连接垫;112-连接垫;113-连接垫;114-连接垫;115-连接垫;116-连接垫;117-支撑层;118-封装材料;118a-模塑材料;118b-芯片;119a-离

型层;119b-底材;121-介电层;122-金属层;123-重布层;124-导线;130-电子元件;131-基板;132-基板通孔;133-第一面;134-第二面;135-信号端;136-接地端;137-导电连接部;140-电子元件;141-基板;142-基板通孔;143-第一面;144-第二面;146-接合垫;147-接合垫;150-电子元件;151-基板;152-基板通孔;153-第一面;154-第二面;155-信号端;156-接地端;157-导电连接部;161-接合端子;162-接合端子;163-接合端子;164-接合端子;165-接合端子;166-接合端子;170-基板;171-元件区;172-基板通孔;173-切割区;174-切割线;175-电子元件;176-电子元件;177-封装材料;180-载板;181-第一保护层;181a-第一面;182-金属层;182p-图案;182r-凹口;183-介电层;184-第二保护层;184a-第二面;185-连接垫;186-连接垫;187-连接垫;188-连接垫;190-基板;191-元件区;192-基板通孔;193-切割区;194-第一面;195-第二面;196-信号端;197-接地端;198-导电连接部;199-切割线;a1-基板面积。

具体实施方式

15.下文结合具体实施例和附图对本发明的内容进行详细描述,且为了使本发明的内容更加清楚和易懂,下文各附图为可能为简化的示意图,且其中的元件可能并非按比例绘制。并且,附图中的各元件的数量与尺寸仅为示意,并非用于限制本发明的范围。

16.本发明通篇说明书与所附的权利要求中会使用某些词汇来指称特定元件。本领域技术人员应理解,电子设备制造商可能会以不同的名称来指称相同的元件,且本文并未意图区分那些功能相同但名称不同的元件。当在本说明书中使用术语"包括"、"包括"和/或"具有"时,其指定了所述特征、区域、步骤、操作和/或元件的存在,但并不排除一个或多个其他特征、区域、步骤、操作、元件和/或其组合的存在或增加。

17.应理解的是,图式的元件或装置可以所属技术领域的技术人员所熟知的各种形式存在。此外实施例中可能使用相对性用语,例如“下”、“较低”、“底部”、“上”、“较高”或“顶部”,以描述图式的一个元件对于另一元件的相对关系。可理解的是,如果将图式的装置翻转使其上下颠倒,则所叙述在“较低”侧的元件将会成为在“较高”侧的元件。本发明实施例可配合图式一并理解,本发明的图式亦被视为发明说明的一部分。应理解的是,本发明的图式并未按照比例绘制,事实上,可能任意的放大或缩小元件的尺寸以便清楚表现出本发明的特征。再者,当述及一第一材料层位于一第二材料层上或之上时,包括第一材料层与第二材料层直接接触的情形,或者,其间亦可能间隔有一或更多其它材料层的情形,在此情形中,第一材料层与第二材料层之间可能不直接接触。

18.在本发明一些实施例中,关于接合、连接的用语例如“连接”、“互连”等,除非特别定义,否则可指两个结构直接接触,或者亦可指两个结构并非直接接触,其中有其它结构设于此两个结构之间。且此关于接合、连接的用语亦可包括两个结构都可移动,或者两个结构都固定的情况。此外,用语“耦接”包含任何直接及间接的电性连接手段。

19.此外,应理解的是,虽然在此可使用用语“第一”、“第二”、“第三”等来叙述各种元件、组件或部分,这些元件、组件或部分不应被这些用语限定。这些用语仅是用来区别不同的元件、组件、区域、层或部分。因此,以下讨论的一第一元件、组件、区域、层或部分可在不偏离本发明的教示的情况下被称为一第二元件、组件、区域、层或部分。

20.此外,根据本发明实施例,可使用光学显微镜(optical microscopy,om)、扫描式

电子显微镜(scanning electron microscope,sem)、薄膜厚度轮廓测量仪(α-step)、椭圆测厚仪或其它合适的方式测量各元件的厚度、宽度或元件之间的距离。详细而言,在一些实施例中,可于移除液晶层之后,使用扫描式电子显微镜取得结构的任一剖面影像,并测量各元件于影像中的厚度、宽度或元件之间的距离。

21.于文中“约”、“大约”、“实质上”、“大致上”的用语通常表示在一给定值或范围的10%内,或5%内、3%之内、2%之内、1%之内或0.5%之内。在此给定的数量为大约的数量,亦即在没有特定说明“约”、“大约”、“实质上”、“大致上”的情况下,仍可隐含“约”、“大约”、“实质上”、“大致上”的含义。此外,用语“范围介于第一数值及第二数值之间”表示所述范围包括第一数值、第二数值以及它们之间的其它数值。

22.须说明的是,下文中不同实施例所提供的技术方案可相互替换、组合或混合使用,以在未违反本发明精神的情况下构成另一实施例。例如本发明的实施例,可以包含芯片优先(chip-first)或是重布层(rdl)优先的实施态样。芯片优先的实施态样,可以在载板上先使用视情况需要的模塑材料(molding compound)覆盖视情况需要的芯片,进行半导体封装而得到封装元件,然后不移除载板进行增层步骤,再叠加重布层或是例如天线元件的电子元件。重布层优先的实施态样,则可以在载板上先形成重布层。

23.图1所示为本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。本发明一些实施例的电子装置100包括载板110、多个电子元件与至少一接合端子。电子装置可包括显示装置、天线装置、感测装置或拼接装置,但不以此为限。电子装置可为可弯折或可挠式电子装置。电子装置可例如包括液晶(liquid crystal)、发光二极管;发光二极管可例如包括有机发光二极管(organic light emitting diode,oled)、次毫米发光二极管(mini led)、微发光二极管(micro led)或量子点发光二极管(quantum dot,qd,可例如为qled、qdled),荧光(fluorescence)、磷光(phosphor)或其他适合的材且其材料可任意排列组合,但不以此为限。天线装置可例如是液晶天线,但不以此为限。拼接装置可例如是显示器拼接装置或天线拼接装置,但不以此为限。需注意的是,电子装置可为前述的任意排列组合,但不以此为限。下文将以天线装置作为电子装置以说明本发明内容,但本发明不以此为限。

24.载板110可以包括透明或不透明的有机材料或是无机材料,也可以包括硬质的材料或是可挠性的材料。有机材料例如可以包括聚酰亚胺(polyimide,pi)、聚碳酸(polycarbonate,pc)、聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、液晶高分子(lcp)、其他已知适合的材料或上述的组合,但是本发明不限于此。无机材料可以包括介电材料或是金属材料,但是本发明不限于此。硬质的材料可以例如是玻璃、石英、蓝宝石、陶瓷或是塑料,或任何适合的材料。此处的“可挠性的材料”是指材料可以弯曲(curved)、弯折(bent)、折叠(fold)、卷曲(rolled)、挠曲(flexible)、拉伸(stretch)及/或其他类似的变形,来表示上述的至少一种可能的变形方式,可挠性的材料举例可包括上述的有机材料的其中一种,但本发明所指的可挠性的材料不限于上述所提及的材料,且“可挠性”也不限于上述的变形方式。载板110可以包括至少一连接垫,例如一个或多个连接垫111、连接垫112、连接垫113、连接垫114、连接垫115、连接垫116。载板110可以包括支撑层117。支撑层117可以包括透明或不透明的有机材料或是无机材料,也可以包括硬质的材料或是可挠性的材料,来支撑载板110中的其它元件。载板110的支撑层117的面积,可以作为载板面积的

代表。连接垫可以包括一导电材料,例如铜,但本发明不以此为限。视情况需要,载板110可以包括各种用于电子装置的元件,例如介电层121、金属层122、重布层(redistribution layer,rdl)123、电子元件阵列,例如矩阵形天线等,本发明不限于此。其中重布层(redistribution layer,rdl)123可为多层结构,包含导线124、电连接结构、绝缘层、通孔等,本发明不限于此。当电子装置100应用为显示装置时,载板110还可包括开关元件及/或驱动元件(图未示)(例如包括半导体层、源极、汲极)、公共电极(图未示)、像素界定层(图未示)或是限制层(limitation layer)(图未示)等,但本发明的载板110所包含的膜层与电子元件并不以上述为限。重布层123有利于搭配进行扇出型面板级封装(fan-out panel level package,foplp)。载板110中的金属层122、重布层123或导线124可以彼此互连,而有利于走线设计。

25.图1中绘示电子元件130、电子元件140与电子元件150,并以相邻的电子元件130与电子元件140代表电子元件阵列,但本发明不限于此。电子元件130、电子元件140与电子元件150可以设置在载板110上,并分别与载板110电连接。电子元件130、电子元件140与电子元件150可以分别是功能相同或是功能不同的电子元件。

26.电子元件130可以包括基板131与贯穿基板131的基板通孔132。基板131可以包括第一面133与相对于第一面133的第二面134。基板131的第二面134可以比第一面133更接近载板110,例如第二面134可以面对载板110。电子元件140可以包括基板141与贯穿基板141的基板通孔142。基板141可以包括第一面143与相对于第一面143的第二面144。基板141的第二面144可以比第一面143更接近载板110,例如第二面144可以面对载板110。电子元件150可以包括基板151与贯穿基板151的基板通孔152。基板151可以包括第一面153与相对于第一面153的第二面154。基板151的第二面154可以比第一面153更接近载板110,例如第二面154可以面对载板110。基板131、基板141或是基板151可以分别(但不限于)包括无机材料。多个电子元件中的各基板,可以分别具有一基板面积a1。在一些实施例中,载板110上所有的电子元件的基板的基板面积的总和小于载板110的面积,但本发明不以此为限。基板的总和面积小于载板110的面积,有利于降低成本。在一些实施例中,基板131、基板141或是基板151可以包括硬质的材料,例如玻璃、石英,但本发明不以此为限。相邻两个电子元件的基板之间的最小间距p可以不小于300微米(micrometer,um),也就是p≥300微米,但本发明不以此为限。

27.电子装置100包括至少一接合端子,例如一个或多个接合端子161、接合端子162、接合端子163、接合端子164、接合端子165、接合端子166,可以分别位于基板131与载板110之间、基板141与载板110之间、以及基板151与载板110之间。接合端子可以包括导电材料,例如铜,但本发明不以此为限。一个接合端子与一个连接垫可以是一对一关系,但本发明不限于此。例如,接合端子161可以与连接垫111电连接或是直接接触、接合端子162可以与连接垫112电连接或是直接接触、接合端子163可以与连接垫113电连接或是直接接触、接合端子164可以与连接垫114电连接或是直接接触、接合端子165可以与连接垫115电连接或是直接接触、接合端子166可以与连接垫116电连接或是直接接触,但本发明不限于此。

28.一个或是多个电子元件可以经由至少一接合端子电连接至少一连接垫。在一些实施例中,电子元件与接合端子可以是一对一关系。例如,电子元件130可以电连接接合端子161、电子元件130可以电连接接合端子162,但本发明不限于此。电子元件140可以电连接接

合端子163、电子元件140可以电连接接合端子164,但本发明不限于此。电子元件150可以电连接接合端子165、电子元件150可以电连接接合端子166,但本发明不限于此。在一些实施例中,电子元件与接合端子也可以是多个电子元件共享一接合端子(图未示),但本发明不限于此。

29.在一些实施例中,电子元件130可以包括薄膜晶体管或是天线元件等,但本发明不限于此。如果电子元件130是天线元件,电子元件130还可以包括信号端135、接地端136与导电连接部137。信号端135、接地端136与导电连接部137可以分别包括导电材料,例如铜,但本发明不以此为限。在一些实施例中,信号端135可以位于基板131的第一面133,作为发射信号及/或接收信号之用。在一些实施例中,接地端136可以位于基板131的第二面134,另外接地端136可以位于基板131与载板110之间。接地端136可以电连接至少一接合端子,例如电连接接合端子162,并通过接合端子162而电连接载板110,但本发明不以此为限。在一些实施例中,导电连接部137可以至少部分地填入基板通孔132中而有一部分位于基板通孔132中。导电连接部137还可以有一部分位于基板131的第二面134,也就是说导电连接部137还可以有一部分位于基板131与载板110之间。导电连接部137可以是t字形(或可称为倒t字形,如图1所示),但本发明不以此为限。在一些实施例中,导电连接部137可以电连接信号端135与至少一接合端子,例如电连接接合端子161,但本发明不以此为限,使得信号端135可以与载板110电连接。

30.在一些实施例中,电子元件140可以包括薄膜晶体管或是天线元件等,但本发明不限于此。如果电子元件140包括薄膜晶体管,电子元件140还可以包括(但不限于)数据线(data line,图未示)、闸极线(gate line,图未示)、接合垫(bonding pad)146、接合垫147、其他导线或电子元件(例如电容、重置元件、补偿元件、控制元件等,图未示),但本发明不以此为限。在一些实施例中,电子元件140可作为开关元件,通过与载板110电连接,控制作为天线元件之用的电子元件130的信号端135,但本发明不以此为限。举例来说,薄膜晶体管可以是底闸型(bottom gate)晶体管,包括闸极(gate)(例如为闸极线的一部分)、源极(source,图未示)(例如为数据线的一部分)、汲极(drain,图未示)、作为通道的半导体层(semiconductor layer,图未示)以及作为闸极绝缘层(gate insulating layer,图未示)的介电层(dielectric layer)。源极与汲极上可选择性的设置介电层或保护层。介电层、保护层可分别为无机材料或有机材料。薄膜晶体管的接合垫146、或是填入基板通孔142的接合垫147,可以分别经由接合端子163或接合端子164,电连接到载板110的连接垫113或连接垫114,所以电子元件140可以经由电连接到载板110来控制作为天线元件之用的电子元件130。源极、汲极、闸极、数据线与门极线可由导电材料,例如金属,如铝(al)、铜(cu)、钛(ti)、钼(mo)、或适合材料或其组合所形成,但不以此为限。薄膜晶体管131也可以是顶闸型(top gate)晶体管,但不以此为限。

31.在一些实施例中,电子元件150可以是天线元件或是薄膜晶体管等,但本发明不限于此。如果电子元件150是天线元件,电子元件150还可以包括信号端155、接地端156与导电连接部157。作为天线元件用的电子元件150的相关说明,可以参照如前所述的电子元件130,于此不再赘述。在一些实施例中,电子装置100还可以包含封装材料来覆盖多个电子元件与开关元件中的至少一个,用来降低湿气或氧气对于电子元件的伤害。例如,图1绘示本发明一些实施例的电子装置100包含封装材料118来覆盖电子元件150,但本发明不以此为

限。

32.本发明一些实施例的电子装置100,可以是先在大基板(bulk substrate)上制作元件,经过适当的裁切步骤形成具有小尺寸基板片(chip substrate)的独立电子元件后,基板片再与载板110进行对组步骤以形成组装的电子装置100。以下将简述电子装置100的制作流程,但本发明不限于此。

33.图2至图6是根据本发明制作一些实施例的电子装置的方法的流程示意图,图2绘示电子装置制程阶段的上视图示意图,图3绘示对应图2的截面图示意图。首先,如图2所绘示,提供基板190。基板190可以是整片未经裁切的硬质基板材料。硬质基板材料有利于配合某些元件所需的一些高温制程,例如制程温度可能会高达250℃或以上,本发明一些实施例制程温度可于250℃~400℃,但本发明不以此为限。适当的硬质基板材料,例如可以包括玻璃、石英或是其组合,但本发明不以此为限。整片的基板190可以包括元件区191、基板通孔192与切割区193。元件区191的最大宽度范围可以介于5毫米(millimeter,mm)至200毫米之间,切割区193的最小宽度可以小于相邻两个电子元件的基板之间的最小间距p,例如切割区193的最小宽度范围可以介于50微米至300微米间,例如约100微米,但本发明不以此为限。整片的基板190可以已经经过一些高温制程,而形成有一些元件,例如天线元件。例如,整片的基板190可以包括第一面194、相对于第一面194的第二面195、信号端196、接地端197、与导电连接部198。在一些实施例中,整片的基板190可以已经经过一些高温制程,而形成有一些元件,例如薄膜晶体管开关元件或是pin二极管元件,但本发明不以此为限。薄膜晶体管元件的相关说明可以参照如前所述,于此不再赘述。

34.图4绘示电子装置制程阶段的上视图示意图,图5绘示对应图4中切线a-b的截面图示意图。其次,如图4所绘示,可以经由切割区193中的切割线199适当的裁切基板190。基板190在经过适当的裁切制程后,可以得到多个小尺寸基板片,以形成电子元件,例如电子元件130、电子元件140与电子元件150。此时小尺寸的基板片可视为图1中所提及的电子元件中的基板。电子元件130与电子元件150可以包含基板片,例如基板片可以是电子元件130的基板131,或电子元件150的基板151,但本发明不以此为限。电子元件130或电子元件150的基板151可以包括切割区193与切割线199,或是不包括切割区193。图5绘示电子元件130或电子元件150可以包括切割区193与切割线199,图1绘示电子元件130或电子元件150可以不包括切割区193。

35.图6绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。图6亦表示电子装置制程阶段的截面图示意图。图6可以对应于一种重布层优先的实施态样。根据本发明,可以提供载板110,例如可以是一大片的载板110。载板110的相关说明可以参照如前所述,于此不再赘述。载板110可以预先经过低温制程或是包含低分辨率的图案。例如,载板110可以包括至少一连接垫,例如一个或多个连接垫111、连接垫112。电子元件150或载板110上可以设置有至少一接合端子,例如一个或多个接合端子161、接合端子162。接合端子161可以与连接垫111电连接或是直接接触、接合端子162可以与连接垫112电连接或是直接接触。然后,可以将电子元件150接合至载板110上。电子元件150的接地端136可以电连接至少一接合端子,例如电连接接合端子162,但本发明不以此为限。电子元件150的导电连接部157可以电连接信号端155与至少一接合端子,例如电连接接合端子161,但本发明不以此为限,使得信号端155可以与载板110电连接。于是,载板110的至少一

连接垫,即可以经由至少一接合端子电连接至电子元件150而得到电子装置101或是电子装置100。图1绘示本发明的一些实施例的电子元件130或电子元件150可以不包括切割区193,图6绘示本发明的一些实施例的电子元件150可以包括切割区193,电子元件150可以是天线元件或是薄膜晶体管。

36.图7至图8是根据本发明制作电子装置的另一种方法的流程示意图,图7绘示电子装置制程阶段的上视图示意图,图8绘示对应图7的上视图示意图。首先,如图7所绘示,提供基板170。基板170可以是整片未经裁切的硬质基板材料。硬质基板材料有利于配合特殊元件所需的一些高温制程,例如制作薄膜晶体管时,制程温度可能会高达250℃或以上,本发明一些实施例制程温度可于250℃~400℃,但本发明不以此为限。适当的硬质基板材料,例如可以包括玻璃、石英或是其组合,但本发明不以此为限。整片的基板170可以包括元件区171、视情况需要的基板通孔172与切割区173。元件区171的最大宽度范围可以介于0.3毫米至60毫米之间,切割区173的最小宽度可以小于相邻两个电子元件的基板之间的最小间距p,例如切割区173的最小宽度范围可以介于50微米至300微米之间。整片的基板170可以已经经过一些高温制程,而形成有一些元件,例如元件区171可以包括薄膜晶体管元件、pin二极管元件,或是包括天线元件。薄膜晶体管元件或是天线元件的相关说明可以参照如前所述,于此不再赘述。

37.其次,如图8所绘示,经由切割区173中的切割线174适当的裁切基板170。基板170在经过适当的裁切制程后,可以得到多个基板片(chip substrate),以形成电子元件,例如电子元件175或电子元件176。图9绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。电子元件175或电子元件176可以包含前述的基板片,但本发明不以此为限。电子元件175可以包括薄膜晶体管元件,电子元件176可以包括天线元件,但本发明不以此为限。电子元件175或电子元件176可以包括切割区173,或是不包括切割区173。电子元件175或电子元件176可以包括基板通孔,或是不包括基板通孔。

38.然后,如图9所绘示,可以提供载板,例如可以是一大片的载板180。然后,可以将电子元件175或电子元件176接合至载板180上。载板180可以包括透明或不透明的有机材料或是无机材料、导电的材料、硬质的材料或是可挠性的材料的结构。有机材料例如可以包括聚酰亚胺、聚碳酸、聚对苯二甲酸乙二酯、液晶高分子、其他已知适合的材料或上述的组合,但是本发明不限于此。硬质的材料可以是,例如玻璃、石英、蓝宝石、陶瓷或是塑料,或任何适合的材料,但本发明不以此为限。导电的材料可以是铜,但本发明不以此为限。此处的“可挠性的材料”是指材料可以弯曲、弯折、折叠、卷曲、挠曲、拉伸及/或其他类似的变形,来表示上述的至少一种可能的变形方式,但本发明不限于此。在一些实施例中,基板170的材料与载板180的材料可以不同。

39.载板180可以包括叠层结构,例如可以包括第一保护层181、金属层182、介电层183、第二保护层184与至少一连接垫。例如,一个或多个连接垫185、连接垫186、连接垫187、连接垫188。连接垫可以包括导电材料,例如铜,但本发明不以此为限。第一保护层181或第二保护层184可以是叠层结构的最外层,可以分别包括一种绝缘材料,适当地保护位于载板180中的其余各层,例如金属层182、介电层183,但本发明不以此为限。叠层结构可以包括第一面与相对于第一面的第二面,例如第一保护层181的第一面181a,与第二保护层184的第二面184a。介电层183可以是载板180的支撑结构,来支撑载板180中的其它元件。金属层182

可以较为接近第一面181a而形成在介电层183上,并且可以包括一导电材料,例如铜,但本发明不以此为限。在一些实施例中,金属层182可以具有一图案182p,使得图案包括至少一凹口182r。凹口182r可以邻近于第一面181a,或是可以位于载板180的第一面181a,并且可以位于两组相邻的连接垫之间,例如位于相邻的连接垫185/连接垫186与连接垫187/连接垫188之间,但本发明不以此为限。凹口182r可以协助天线元件调整电磁波的波前方向,而具有指向性。载板110可以预先经过低温制程或是包含低分辨率的图案。例如,图案182p与至少一凹口182r即可以是一种低分辨率的图案。

40.电子元件175或电子元件176或载板180上可以设置有至少一接合端子,例如一个或多个接合端子161、接合端子162、接合端子163、接合端子164。接合端子可以包括导电材料,例如铜,但本发明不以此为限。一个接合端子与一个连接垫可以是一对一的关系,但本发明不限于此。例如,接合端子161可以与连接垫185电连接或是直接接触、接合端子162可以与连接垫186电连接或是直接接触、接合端子163可以与连接垫187电连接或是直接接触、接合端子164可以与连接垫188电连接或是直接接触。

41.视情况需要,载板180还可以包括各种元件,例如重布层(图未示)、电子元件阵列、矩阵形天线等,当电子装置应用为显示装置时,载板180还可包括开关元件及/或驱动元件(例如包括半导体层、源极、汲极,图未示)、公共电极(图未示)、像素界定层(图未示)或是限制层(图未示)等,但本发明的载板180所包含的膜层与电子元件并不以上述为限。载板180中的金属层182或重布层可以彼此互连,而有利于走线设计。重布层有利于搭配进行扇出型面板级封装。图9绘示电子元件175与电子元件176的组合来代表电子元件阵列。

42.然后,可以将电子元件175或电子元件176接合至载板180上。电子元件175或电子元件176可以位于载板180的第一面181a,或是可以位于载板180的第二面184a。在一些实施例中,电子元件175或电子元件176可以电连接至少一接合端子,使得接合端子161可以位于基板170与载板180之间、接合端子162可以位于基板170与载板180之间、接合端子163可以位于基板170与载板180之间、接合端子164可以位于基板170与载板180之间。例如,电子元件175可以电连接接合端子161、接合端子162,电子元件176可以电连接接合端子163、接合端子164,但本发明不以此为限,使得电子元件175或电子元件176可以经由至少一接合端子与载板180电连接。于是,载板110的至少一连接垫,即可以经由至少一接合端子电连接至电子元件175及/或电子元件176而得到电子装置103或是电子装置104。本发明的一些实施例,电子元件175与电子元件176分别包含薄膜晶体管、天线元件、开关元件等电子元件,但本发明不以此为限。图9绘示本发明的一些实施例的电子元件175可以包括薄膜晶体管,电子元件176可以包括天线元件或是可变电容二极管。在一些实施例中,电子元件175可以经由接合端子电连接载板180,作为控制作为天线元件或是可变电容二极管的电子元件176的开关元件。

43.一个电子元件可以经由至少一接合端子电连接至少一连接垫。在一些实施例中,电子元件与接合端子可以是一对一关系。例如,电子元件130可以电连接接合端子161、接合端子162,但本发明不限于此。电子元件140可以电连接接合端子163、接合端子164,但本发明不限于此。电子元件150可以电连接接合端子165、接合端子166,但本发明不限于此。在一些实施例中,电子元件与接合端子也可以是多个电子元件共享一接合端子(图未示),但本发明不限于此。在一些实施例中,电子装置103还可以包含封装材料来覆盖至少一天线元件

与开关元件中的至少一个,用来降低湿气或氧气对于电子元件的伤害。图9绘示本发明一些实施例的电子装置103可以包含封装材料177,来覆盖电子元件176,例如可以包括天线元件或是可变电容二极管,但本发明不以此为限。

44.图10绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。上述实施例已公开部分不再多做描述,在一些实施例中,如图10所示,电子装置104中的开关元件189可以内建于载板180中,且可以设置在较为接近载板180的第二面184a,并开关元件189直接与金属层182电连接,而不需要通过接合端子电连接载板180。开关元件189可以包括薄膜晶体管,电子元件176可以包括天线元件或是可变电容二极管。开关元件189可以电连接载板180,作为控制包括天线元件或是可变电容二极管的电子元件176的开关元件。

45.图11绘示根据本发明的一些实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。上述实施例已公开部分不再多做描述,如图11所示,电子装置105中的开关元件189可以内建于载板180中,且可以设置在邻近于载板180的第一面181a,直接与金属层182电连接,而不需要通过接合端子电连接载板180。开关元件189可以包括薄膜晶体管,电子元件176可以包括天线元件或是可变电容二极管。开关元件189可以电连接载板180,作为控制包括天线元件或是可变电容二极管的电子元件176的开关元件。

46.图12绘示对应本发明的图6的变形实施例的电子装置的结构示意图,并以剖视方式表示各元件结构。图12亦表示电子装置制程阶段的截面图示意图。图12可以对应于一种芯片优先的实施态样。上述实施例已公开部分不再多做描述。根据本发明,在一些实施例中,例如图12所绘示,电子装置106可以包含电子元件150与载板110。载板110可以包含支撑层117。支撑层117可以包含视情况需要的模塑材料118a、视情况需要的芯片118b、视情况需要的离型层(release layer)119a、底材(matrix)119b,但本发明不以此为限。底材119b可以包括硬质的材料,例如玻璃、石英,但本发明不以此为限。视情况需要的模塑材料118a可以是一种树脂材料,但本发明不以此为限。模塑材料118a,例如可以覆盖视情况需要的芯片118b,用来降低湿气或氧气对于芯片118b的伤害。图12所示的电子装置106,可以是一种面向上(face up)的封装方式。在图12所绘示的电子装置106中的一个电子元件150,可以经由穿过介电层121、金属层122、重布层123中的导线124,与一个芯片118b电连接。

47.本发明的一种电子装置,包括载板组合耐热性较佳的基板的材料组合优势。载板可以进行制程温度低的制程,基板可以制作成本较高、制作较为复杂或制程温度高的元件或技术。这种材料组合优势,可以增加基板利用率,不受材料温度限制,还可以解决制程复杂、制程困难或是基板成本较高等问题。例如,当整片基板与整片载板进行对组时,两个相邻电子元件之间的间距p,就会成为不能对应电子元件的元件区的非元件区。当两个相邻电子元件之间的间距p越大,非元件区在整片基板中所占的比例就会越大,于是造成对应电子元件的元件区的基板利用率变小。然而本发明提供可以调整或缩小非元件区,例如切割区的整片基板。本发明的整片基板中的切割区,其尺寸与两个相邻电子元件之间的间距p可以没有直接的关联。所以可以在合理的情况下,适当减小或尽量降低本发明的整片基板中的切割区,即非元件区的尺寸,从而可以增加本发明整片基板的基板利用率。本发明的线路可以在1微米到300微米的设计下,把元件做在同一基板上。或是在分开制程后,可使用一片或是多片的玻璃基板,再连结到第二基板上。

48.以上所述仅为本发明的实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1