一种三维芯片的制作方法

本申请涉及芯片,尤其涉及一种三维芯片。

背景技术:

1、三维芯片(3d芯片)是将不同电路单元制作在多个平面晶片或平面芯片上,并通过层间垂直互连技术将多个晶片在垂直方向进行堆叠互连而形成的一种全新的芯片结构。

2、然而,现有的三维芯片的互连结构通常用于实现相邻芯片单元之间的点对点互连,连接方式较为单一,难以实现芯片单元上电路之间的灵活连接,限制了三维芯片的集成度以及电路结构的集成种类。

技术实现思路

1、本申请实施例提供一种三维芯片,能够实现芯片单元上电路之间的灵活连接,提高三维芯片的集成度以及增加电路结构的集成种类。

2、本申请实施例的第一方面,提供一种三维芯片,包括:

3、至少两层芯片单元,所述芯片单元上设置有连接点;

4、3d互连结构,所述3d互连结构包括导电连接部,相邻的两层所述芯片单元上的所述连接点通过所述导电连接部连接,至少一个所述芯片单元的同一表面上的至少两个所述连接点通过所述导电连接部连接。

5、在一些实施方式中,一层所述芯片单元上的一个所述连接点通过所述导电连接部与相邻的另一层所述芯片单元上的至少一个所述连接点连接;和/或,

6、一层所述芯片单元上的至少两个所述连接点通过所述导电连接部与相邻的另一层所述芯片单元上的至少两个所述连接点连接。

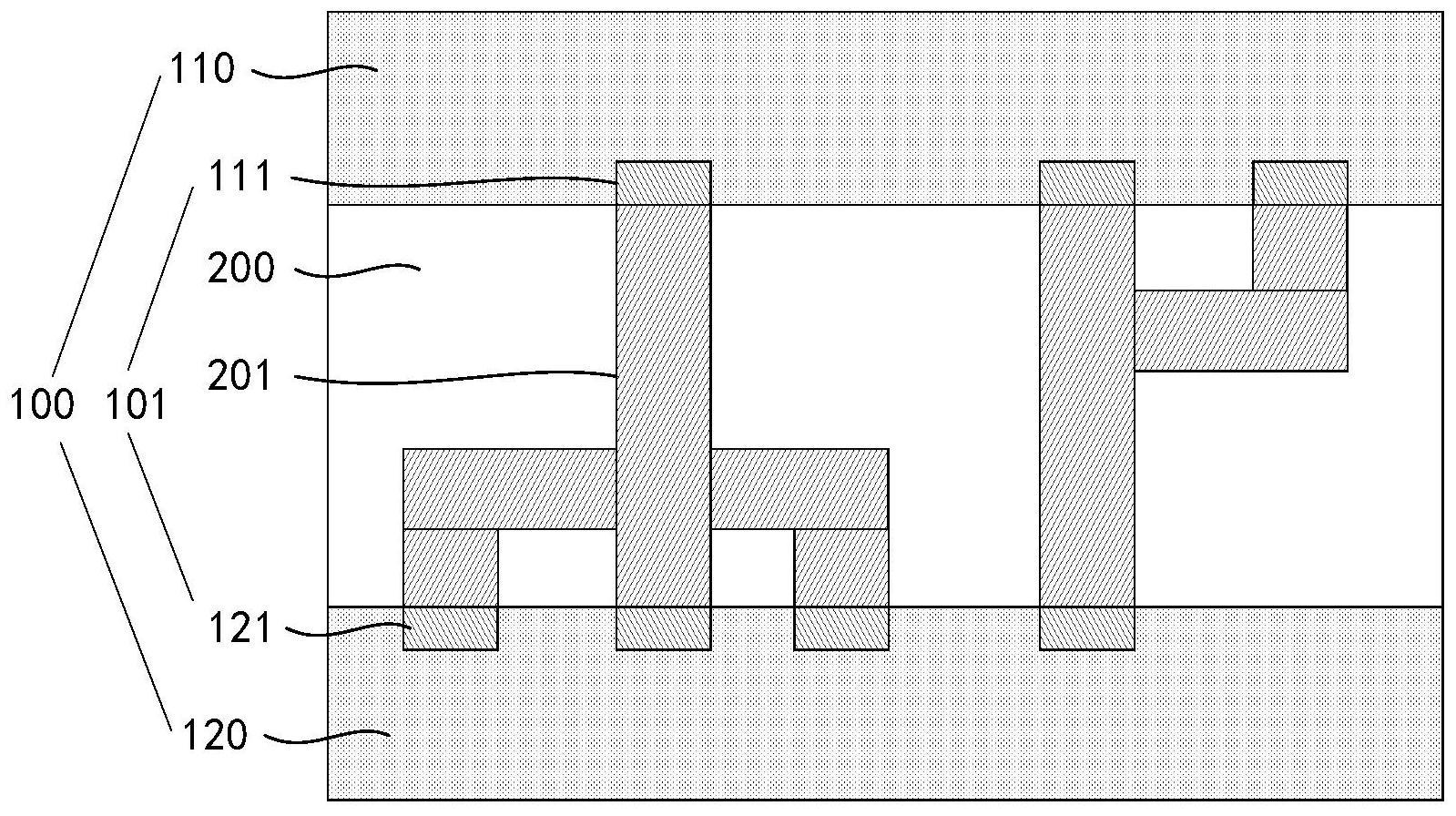

7、在一些实施方式中,所述3d互连结构包括至少两层介质层和至少一层金属层,所述金属层设置于两层所述介质层之间;

8、所述介质层上设置有通孔,所述金属层内设置有所述导电连接部,所述导电连接部与所述连接点通过所述通孔连接。

9、在一些实施方式中,不同所述金属层内的所述导电连接部在所述芯片单元上的正投影存在交叠。

10、在一些实施方式中,所述芯片单元内设置有测试电路,所述测试电路与所述连接点连接,所述测试电路通过所述导电连接部和至少两个所述连接点形成测试回路。

11、在一些实施方式中,所述测试电路包括输出模块和输入模块,所述输出模块与所述连接点连接,所述输入模块与所述连接点连接;

12、属于同一个所述测试电路的所述输出模块和所述输入模块分别连接不同的所述连接点。

13、在一些实施方式中,一个所述连接点分别连接所述输出模块和所述输入模块,连接于同一个所述连接点的所述输入模块和所述输出模块属于不同的所述测试电路。

14、在一些实施方式中,所述测试电路包括:

15、功能模块,所述输入模块和所述输出模块分别与所述功能模块连接;

16、激励模块,所述激励模块与所述功能模块连接,所述激励模块用于发出测试信号,所述测试信号经过所述功能模块的处理后,依次经过所述输出模块、所述连接点、所述导电连接部、所述输入模块,再次经过所述功能模块的处理以形成反馈信号;

17、检测模块,所述检测模块与所述功能模块连接,所述检测模块用于检测所述反馈信号。

18、在一些实施方式中,任一所述芯片单元内的所述测试电路通过所述连接点和所述导电连接部形成芯片内部测试回路,所述芯片内部测试回路用于测试单层所述芯片单元内部的功能。

19、在一些实施方式中,至少两层所述芯片单元内的所述测试电路通过所述连接点和所述导电连接部形成联合芯片测试回路,所述联合芯片测试回路用于测试至少两层所述芯片单元互连后的功能。

20、本申请实施例提供的三维芯片,通过设置3d互连结构以及在3d互连结构内设置导电连接部,导电连接部用于实现单层芯片单元上的不同连接点的互连,导电连接部还用于实现不同芯片单元上连接点的跨芯片互连。导电连接部的设置能够实现连接点的多种连接方式,包括一对一、多对一、多对多,导电连接部的设置还可以用于单层芯片单元内的不同连接点的互连,以实现单层芯片单元的内部互连。本申请实施例提供的三维芯片,能够克服现有的三维芯片的互连结构的点对点互连,连接方式较为单一的问题,可以实现单层芯片单元上电路之间的灵活连接,以及不同芯片单元之间多种互连方式,进而提高三维芯片的集成度以及增加电路结构的集成种类。

技术特征:

1.一种三维芯片,其特征在于,包括:

2.根据权利要求1所述的三维芯片,其特征在于,一层所述芯片单元上的一个所述连接点通过所述导电连接部与相邻的另一层所述芯片单元上的至少一个所述连接点连接;和/或,

3.根据权利要求1所述的三维芯片,其特征在于,所述3d互连结构包括至少两层介质层和至少一层金属层,所述金属层设置于两层所述介质层之间;

4.根据权利要求3所述的三维芯片,其特征在于,不同所述金属层内的所述导电连接部在所述芯片单元上的正投影存在交叠。

5.根据权利要求1所述的三维芯片,其特征在于,所述芯片单元内设置有测试电路,所述测试电路与所述连接点连接,所述测试电路通过所述导电连接部和至少两个所述连接点形成测试回路。

6.根据权利要求5所述的三维芯片,其特征在于,所述测试电路包括输出模块和输入模块,所述输出模块与所述连接点连接,所述输入模块与所述连接点连接;

7.根据权利要求6所述的三维芯片,其特征在于,一个所述连接点分别连接所述输出模块和所述输入模块,连接于同一个所述连接点的所述输入模块和所述输出模块属于不同的所述测试电路。

8.根据权利要求7所述的三维芯片,其特征在于,所述测试电路包括:

9.根据权利要求7所述的三维芯片,其特征在于,任一所述芯片单元内的所述测试电路通过所述连接点和所述导电连接部形成芯片内部测试回路,所述芯片内部测试回路用于测试单层所述芯片单元内部的功能。

10.根据权利要求7所述的三维芯片,其特征在于,至少两层所述芯片单元内的所述测试电路通过所述连接点和所述导电连接部形成联合芯片测试回路,所述联合芯片测试回路用于测试至少两层所述芯片单元互连后的功能。

技术总结

本申请公开一种三维芯片,涉及芯片技术领域,能够实现芯片单元上电路之间的灵活连接,提高三维芯片的集成度以及增加电路结构的集成种类。三维芯片,包括:至少两层芯片单元,所述芯片单元上设置有连接点;3D互连结构,所述3D互连结构包括导电连接部,相邻的两层所述芯片单元上的所述连接点通过所述导电连接部连接,至少一个所述芯片单元的同一表面上的至少两个所述连接点通过所述导电连接部连接。

技术研发人员:左丰国,刘琦

受保护的技术使用者:西安紫光国芯半导体有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!