一种接触插塞的测试结构及其形成方法、测试方法与流程

本公开涉及半导体,尤其涉及一种接触插塞的测试结构及其形成 方法、测试方法。

背景技术:

1、随着技术的发展,集成电路内包含的晶体管等半导体器件的数目越来越多, 为了将半导体器件连接起来,集成电路内一般设置有多个金属层。半导体器件 通过导电插塞与金属层连接,各金属层之间则通过通孔连接。其中,互连金属 层与衬底中的晶体管等半导体器件之间的导通是通过接触插塞实现的。随着半 导体器件特征尺寸不断微缩,运行速度不断提高,接触插塞电阻值的微小变化 就会对整个集成电路产生巨大影响。因此,寻求一种能准确反映接触插塞中工 艺情况的测试结构是本领域技术人员需要解决的课题。

技术实现思路

1、有鉴于此,本公开实施例为解决背景技术中存在的至少一个问题而提供一 种接触插塞的测量方法。

2、为达到上述目的,本公开的技术方案是这样实现的:

3、根据本公开实施例提供了一种接触插塞的测试结构,包括:

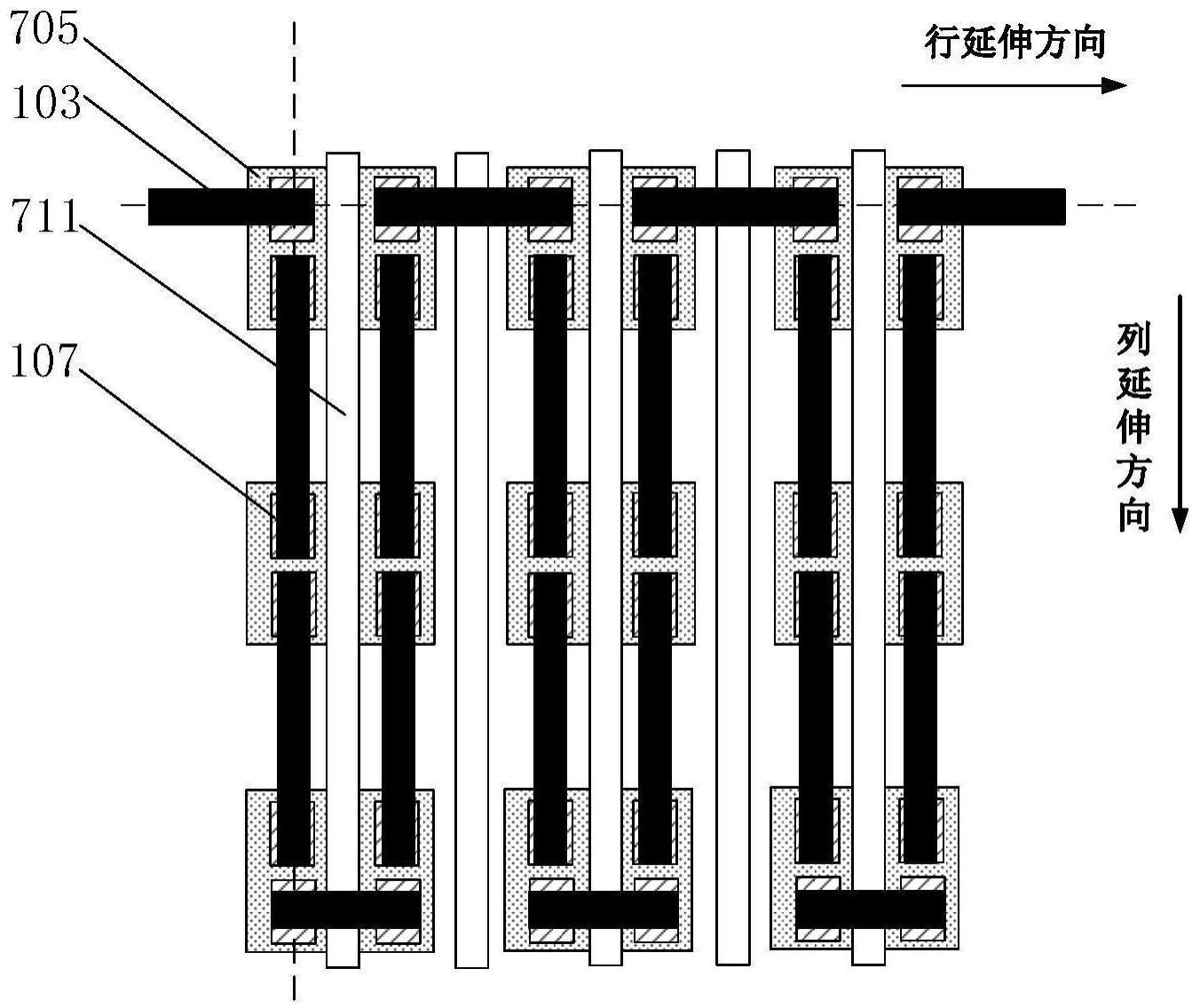

4、衬底;设置于所述衬底上的多个有源区域;设置于所述衬底上的多个接触 插塞,同一所述有源区域上形成至少两个接触插塞,且所述接触插塞的底部与 所述有源区域电连接;多个连接件,每一所述连接件电连接分别位于不同有源 区域上的所述接触插塞,使得所述有源区域、所述接触插塞和所述连接件形成 串联结构;位于所述衬底上的多个伪栅极,所述伪栅极至少位于所述接触插塞 的一侧。

5、上述方案中,多个所述伪栅极相互平行排列,且至少一个所述伪栅极位于 同一所述有源区域上的两个所述接触插塞之间,所述伪栅极部分覆盖所述有源 区域,且所述伪栅极的宽度小于所述有源区域的宽度。

6、上述方案中,多个所述伪栅极相互平行排列,且所述伪栅极位于相邻的所 述有源区域之间,且所述伪栅极的宽度小于相邻所述有源区域的宽度。

7、上述方案中,至少一个所述接触插塞的侧壁具有凹陷部,所述接触插塞的 侧壁在所述凹陷部处沿侧向方向向内凹陷,且所述凹陷部位于所述接触插塞的 朝向相邻的所述伪栅极的一侧。

8、上述方案中,所述有源区域、所述接触插塞和所述连接件以迂回的方式排 列成一蛇形结构。

9、上述方案中,同一接触插塞的两侧存在伪栅极,其中一侧的伪栅极覆盖所 述有源区域。

10、上述方案中,所述接触插塞的材料和所述连接件的材料相同。

11、本公开实施例还提供了一种接触插塞的测试结构,包括:

12、衬底;设置于所述衬底上的多个有源区域,所述有源区域包括两个源漏掺 杂区和位于两个所述源漏掺杂区之间的沟道掺杂区;设置于所述沟道掺杂区上 的栅极,所述栅极、位于所述栅极底部的沟道掺杂区以及位于所述栅极两侧的 源漏掺杂区构成晶体管;设置于所述衬底上的多个接触插塞,所述接触插塞的 底部与所述晶体管的源漏掺杂区电连接;多个连接件,每一所述连接件电连接 相邻两个所述晶体管上的接触插塞,使得所述有源区域、所述接触插塞和所述 连接件形成串联结构。

13、上述方案中,至少一个所述接触插塞的侧壁具有凹陷部,所述接触插塞的 侧壁在所述凹陷部处沿侧向方向向内凹陷,且所述凹陷部位于所述接触插塞的 朝向相邻的所述栅极的一侧。

14、上述方案中,所述有源区域、所述接触插塞和所述连接件以迂回的方式排 列成一蛇形结构。

15、本公开实施例还提供了一种接触插塞的测试结构的形成方法,包括:

16、提供衬底;在所述衬底上形成多个有源区域;在所述衬底上形成伪栅极堆 叠;刻蚀所述伪栅极堆叠,形成多个伪栅极;在所述衬底上形成介质层,所述 介质层覆盖所述伪栅极;刻蚀所述介质层,形成接触孔,同一所述有源区域上 形成至少两个接触孔,所述接触孔至少位于所述伪栅极的一侧;沉积导电材料, 所述导电材料填充所述接触孔形成接触插塞,所述接触插塞的底部与所述有源 区域电连接,继续沉积导电材料形成覆盖所述介质层表面的导电材料覆盖层; 图案化所述导电材料覆盖层,形成多个连接件,每一所述连接件电连接分别位 于不同有源区域上的所述接触插塞,使得所述有源区域、所述接触插塞和所述 连接件形成串联结构。

17、上述方案中,在所述衬底上形成多个有源区域;在所述衬底上形成伪栅极 堆叠,包括:在所述衬底上形成掩膜层,刻蚀所述掩膜层形成有源区域开口; 掺杂从所述有源区域开口暴露的所述衬底,形成有源区域;在形成有源区域之 后,沉积伪栅极堆叠。

18、上述方案中,所述有源区域包括源漏掺杂区,且所述源漏掺杂区的掺杂类 型为n型或者p型的一种。

19、本公开实施例还提供了一种接触插塞的测试结构的形成方法,包括:

20、提供衬底;在所述衬底上形成沟道掺杂区;在所述衬底上形成栅极堆叠; 刻蚀所述栅极堆叠,形成多个栅极;在所述栅极的两侧衬底内形成多个源漏掺 杂区,由位于所述栅极两侧的源漏掺杂区和位于栅极底部的沟道掺杂区构成有 源区域,所述有源区域和所述栅极构成晶体管;在所述衬底上形成介质层,所 述介质层覆盖所述栅极;刻蚀所述介质层,形成接触孔;沉积导电材料,所述 导电材料填充所述接触孔形成接触插塞,所述接触插塞的底部与所述源漏掺杂 区电连接,继续沉积导电材料,形成覆盖所述介质层表面的导电材料覆盖层; 图案化所述导电材料覆盖层,形成多个连接件,每一所述连接件电连接相邻两 个所述晶体管上的接触插塞,使得所述有源区域、所述接触插塞和所述连接件 形成串联结构。

21、上述方案中,在所述栅极的两侧衬底内形成多个源漏掺杂区,包括:形成 覆盖所述栅极侧壁的侧墙结构;以所述栅极与所述侧墙结构为掩膜,自对准离 子注入源漏掺杂离子,形成源漏掺杂区。

22、上述方案中,所述沟道掺杂区通过离子注入掺杂第一离子类型,所述源漏 掺杂区通过离子注入掺杂第二离子类型,所述第一、第二离子类型为n型或者 p型的一种,且所述第一离子与所述第二离子的类型相反。

23、本公开实施例还提供了一种接触插塞的测试方法,上述方案中的测试结构, 所述测试方法包括:

24、在串联结构中选择两个不同的接触插塞,分别作为输入端和输出端;将串 联在所述两个接触插塞之间的晶体管的栅极加工作电压,使得晶体管导通;在 输入端连接第一测试端,在输出端连接第二测试端,第一测试端和第二测试端 分别连接恒流源,形成第一回路,以获取测试电流;在输入端连接第三测试端, 在输出端连接第四测试端,第三测试端和第四测试端分别连接电压表,形成第 二回路,以获取测试电压;由测试电压除以测试电流得出测试电阻;将所述测 试电阻与预先设定的理想电阻范围进行比较,若所述测试电阻在所述理想电阻 范围内则判定接触插塞的性能合格。

25、本公开实施例提供了一种接触插塞的测试结构,包括:衬底;设置于所述 衬底上的多个有源区域;设置于所述衬底上的多个接触插塞,同一所述有源区 域上形成至少两个接触插塞,且所述接触插塞的底部与所述有源区域电连接; 多个连接件,每一所述连接件电连接分别位于不同有源区域上的所述接触插塞, 使得所述有源区域、所述接触插塞和所述连接件形成串联结构;位于所述衬底 上的多个伪栅极,所述伪栅极至少位于所述接触插塞的一侧。如此,使得测试 结构与实际集成电路应用的结构更加接近,这样的测试结构更加能够反映接触 插塞的工艺情况,可以较准确的测试出接触插塞的电阻值。

26、本公开附加的方面和优点将在下面的描述中部分给出,部分将从下面的描 述中变得明显,或通过本公开的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!