半导体装置的制作方法

半导体装置

1.本技术是申请号为201680081551.2的发明专利申请的分案申请,原申请的申请日为2016年2月10日,发明名称为“半导体装置”。

技术领域

2.本发明涉及一种半导体装置,具体而言涉及层叠有半导体芯片的层叠型的半导体装置。

背景技术:

3.为了满足大规模集成电路(large scale integration:lsi)的高集成化和大容量化的要求,三维地层叠多个半导体芯片。

4.三维安装技术中存在一种硅通孔技术(through-silicon-via,tsv)。在该方法中,在半导体芯片上设置微小的孔而形成贯穿电极,用布线在上下方向上将芯片互相连接。但是,由于tsv需要机械加工技术,所以每个芯片的制造成本高,而且,存在起因于应力、热等的机械连接不良等问题。

5.作为三维安装技术的其它方法,存在利用电感耦合的技术(thruchip interface,tci:thruchip接口)。在tci中,利用发送线圈与接收线圈之间的电感耦合,在层叠的芯片之间进行数据通信(例如,参照专利文献1。)。

6.在tci中,层叠的芯片之间的电感耦合接口由收发线圈之间的电感耦合、和对数据通信进行处理的收发电路而构成。在发送电路中,当将发送数据转换为电流,被转换的发送电流流过发送线圈时,根据发送电流的变化,在接收线圈感应出接收电压。这样一来,用接收电路检测感应电压而将发送数据复原。tci中的收发线圈是在半导体集成电路的制造过程中用金属布线制成的,不需要机械加工技术。因此,与tsv相比,tci在成本上是有优势的,此外还能够消除由于机械连接引起的可靠性的问题。

7.现有技术文献

8.专利文献

9.专利文献1:日本特开2005-228981号公报。

10.发明要解决的课题

11.为了实现高性能且低功率的超级计算机,需要在使半导体集成电路小型化的同时,集成度提高至比以往更好。

技术实现要素:

12.本发明是鉴于这方面而完成的。即,本发明的目的在于提供一种在利用了tci的进行三维安装的半导体装置中通过在各半导体芯片高效地配置收发线圈和收发电路、从而能够实现小型化以及高集成化的半导体装置。

13.本发明的其它目的和优点从以下的记载得以明确。

14.用于解决课题的方案

15.(1)本发明的一个方式涉及一种半导体装置,其具有:

16.多个存储器芯片,其分别具有第1收发线圈、第1引线以及第1收发电路并层叠起来,所述第1收发线圈用于通过电感耦合进行通信,所述第1引线是从第1收发线圈的两端引出,所述第1收发电路与第1引线连接并在与第1收发线圈之间进行信号的输入输出;以及

17.中介层,其配置在多个存储器芯片的层叠方向的一端,按多个存储器芯片的每一个具有:第2收发线圈,其通过电感耦合与第1收发线圈耦合;第2引线,其从第2收发线圈的两端引出;以及第2收发电路,其与所述第2引线连接并在与第2收发线圈之间进行信号的输入输出,

18.多个存储器芯片具有以下结构:在俯视时,多个第1收发电路配置在彼此重叠的位置,在这些第1收发电路的周围,第1收发线圈配置在彼此不重叠的位置。

19.(2)本发明的其它方式涉及(1)所述的半导体装置,其中,

20.所述第1收发线圈在俯视时对称地配置在所述第1收发电路的周围。

21.(3)本发明的其它方式涉及(1)所述的半导体装置,其中,

22.第1引线的长度在多个存储器芯片之间是相等的。

23.(4)本发明的其它方式涉及(1)所述的半导体装置,其中,

24.第2收发线圈的中心轴分别与对应的第1收发线圈的中心轴一致。

25.(5)本发明的其它方式涉及(1)所述的半导体装置,其中,

26.在每个存储器芯片配置的第2引线均为相等的长度。

27.(6)本发明的其它方式涉及(1)所述的半导体装置,其中,

28.中介层为在层叠的多个存储器芯片中位于层叠方向的一端的存储器芯片。

29.(7)本发明的其它方式涉及(1)所述的半导体装置,其中,

30.多个存储器芯片被分为多个组单元,构成各组单元的存储器芯片的第1收发线圈、第1引线、以及第1收发电路分别配置在俯视时彼此重叠的位置。

31.(8)本发明的其它方式涉及(7)所述的半导体装置,其中,

32.存储器芯片分别具有:运算电路,其输出彼此不同的识别号码;以及比较电路,其将识别码与用于存储器芯片选择的地址进行比较,从而检测是否一致,地址的信号线在全部的存储器芯片之间是共同的。

33.(9)本发明的其它方式涉及(8)所述的半导体装置,其中,中介层生成地址并输出。

34.发明效果

35.根据本发明,提供一种将收发线圈和收发电路高效率地配置在各半导体芯片从而能够实现小型化和高集成化的半导体装置。

附图说明

36.图1为表示实施方式1中的半导体装置的一个例子的局部剖视图。

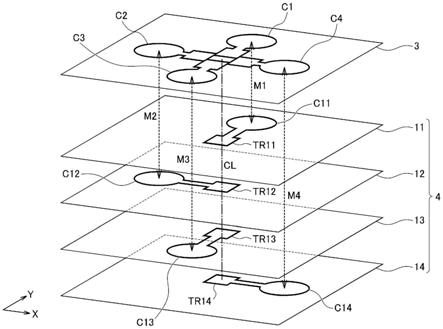

37.图2为示意地表示实施方式1中的中介层和层叠dram的结构的立体图。

38.图3为产生电感耦合的收发线圈的示意图的一个例子。

39.图4(a)~(d)为实施方式1的存储器芯片的示意性局部俯视图。

40.图5为实施方式1的中介层的示意性局部俯视图。

41.图6为表示实施方式2中的半导体装置的一个例子的局部剖视图。

42.图7为实施方式2中的层叠dram的剖视示意图。

43.图8为示意地表示实施方式3中的中介层和层叠dram的结构的立体图。

44.图9(a)~(d)为实施方式3的存储器芯片的示意性局部俯视图。

45.图10为实施方式3的中介层的示意性局部俯视图。

46.图11为将图10的a-a线投影到图8的存储器芯片而成的剖视示意图。

47.图12为将图10的b-b线投影到图8的存储器芯片而成的剖视示意图。

48.图13为实施方式3中的芯片选择电路的结构图。

具体实施方式

49.实施方式1

50.图1为表示本实施方式的半导体装置的一个例子的局部剖视图。在图1的半导体装置1中,在基板5上经由焊料球6安装了处理器2。此外,在基板5上设置有在与基板5垂直的方向上层叠了dram(dynamic random access memory:动态随机存取存储器)的存储器芯片11~14的层叠结构(层叠dram4)。在层叠dram4中的存储器芯片的层叠方向的一端、即存储器芯片11上配置有中介层3。通过设置中介层3,能够防止由处理器2产生的热对dram的工作带来不良影响。另外,半导体装置1例如能够设为在处理器2的周围配置有多个由中介层3和层叠dram4构成的结构体的结构。层叠通过熔融接合(fusion bonding)来实现。层叠也可以利用使用了粘接剂的方法、表面活化常温接合等其它方法。

51.处理器2和层叠dram4的各存储器芯片11~14经由中介层3进行电连接。具体而言,中介层3接收从在上方配置的处理器2的芯片发送的数据,并向在下方配置的层叠dram4中的规定的存储器芯片发送数据。由此,进行数据的写入。另一方面,数据的读取是通过以下方式实施的:中介层3接收从在下方配置的层叠dram4中的规定的存储器芯片发送的数据,并向在上方配置的处理器2的芯片发送数据。

52.另外,在半导体装置1中,例如也可以从处理器2向未图示的其它1个以上的元件发送数据,从这些元件中的任一个向中介层3发送数据。此外,中介层3也可以将从存储器芯片11~14接收的数据发送到未图示的其它元件,而不发送到处理器2。

53.图2为示意地表示图1中的中介层3和层叠dram4的结构的立体图。层叠dram4由4枚dram的存储器芯片11~14层叠而成。各存储器芯片11~14分别具有收发线圈c11~c14。此外,中介层3具有与存储器芯片11~14的收发线圈c11~c14对应的收发线圈c1~c4。在此,收发线圈c11~c14为本发明的第1收发线圈的优选的一个例子。此外,收发线圈c1~c4为本发明的第2收发线圈的优选的一个例子。但是,在本实施方式中,存储器芯片的层叠数并不限于图1和图2的例子。

54.另外,在本说明书中,将发送线圈和接收线圈统称为收发线圈。收发线圈能够采用例如以发送线圈的中心和接收线圈的中心位于同轴的方式配置的结构。收发线圈的匝数能够通过使用多个布线层和连接通孔而设为任意的值。另外,收发线圈的结构并不限于上述的例子,例如也可以采用以下结构:用一层布线形成一匝的发送线圈和接收线圈并将它们连结,利用多个布线层和连接通孔而增加了匝数。在实际的半导体装置中,dram的每一个存储器芯片配置例如1000个左右的收发线圈。各收发线圈之间的距离能够设为例如收发线圈的尺寸的2分之1左右。

55.使用图3对中介层3的收发线圈c1与存储器芯片11的收发线圈c11之间的电感耦合进行说明。另外,在本实施方式中,将收发线圈(c1~c4,c11~c14)的平面形状设为圆形,但不限于此,也可以是多边形或椭圆形等。

56.在图3的例子中,收发线圈c1为如下的双线圈,即:接收线圈c1r设置在发送线圈c1

t

的外侧,并且发送线圈c1

t

和接收线圈c1r以同心的方式配置。此外,收发线圈c11也相同,成为接收线圈c11r设置在发送线圈c11

t

的外侧的结构。而且,收发线圈c1和收发线圈c11以在图3中由虚线表示的中心轴彼此一致的方式配置。

57.从收发线圈c1的两端引出了引线l1,在该引线l1连接了收发电路tr1。收发电路tr1如以下那样与收发线圈c1之间进行信号的输入输出。另外,引线l1为本发明的第2引线的优选的一个例子。此外,收发电路tr1为本发明的第2收发电路的优选的一个例子。

58.收发电路tr1将与向存储器芯片11发送的数据对应地重叠的电流输出到发送线圈c1

t

。当发送电流流过发送线圈c1

t

时,产生与发送线圈c1

t

交链的磁通。由于所产生的磁通还与存储器芯片11中的收发线圈c11的接收线圈c11r交链,所以在接收线圈c11r产生感应电动势而流过接收电流。

59.从收发线圈c11的两端引出了引线l11,在该引线l11上连接了收发电路tr11。收发电路tr11与收发线圈c11之间进行信号的输入输出。在此,当接收线圈c11r流过接收电流时,收发电路tr11再现与所产生的感应电动势对应的数据。另外,引线l11为本发明的第1引线的优选的一个例子。此外,收发电路tr11为本发明的第1收发电路的优选的一个例子。

60.如上所述,从处理器2输出的数据经由中介层3传输到层叠dram4的存储器芯片11。

61.另一方面,在从存储器芯片11读出数据的情况下,存储器芯片11中的收发电路tr11的发送器将与向中介层3发送的数据对应地重叠的电流输出到发送线圈c11。当发送电流流过发送线圈c11

t

时,产生与发送线圈c11

t

交链的磁通。由于所产生的磁通也与中介层3中的收发线圈c1的接收线圈c1r交链,所以在接收线圈c1r产生感应电动势而流过接收电流。当在接收线圈c1r流过接收电流时,与接收线圈c1r电连接的收发电路tr1再现与所产生的感应电动势对应的数据。如以上这样,从层叠dram4的存储器芯片11输出的数据被传输到中介层3。

62.对于中介层的其它收发线圈(c2~c4)和其它存储器芯片的收发线圈(c12~c14),也分别设置有从线圈的两端引出的引线、以及与该引线连接并在与收发线圈之间进行信号的输入输出的收发电路。在此,设置在收发线圈(c2~c4)的引线为本发明的第2引线的优选的一个例子,设置在收发线圈(c12~c14)的引线为本发明的第1引线的优选的一个例子。此外,与收发线圈(c2~c4)电连接的收发电路为本发明的第2收发电路的优选的一个例子,与收发线圈(c12~c14)电连接的收发电路为本发明的第1收发电路的优选的一个例子。

63.在半导体装置1中,在收发线圈c2与收发线圈c12之间、收发线圈c3与收发线圈c13之间、收发线圈c4与收发线圈c14之间分别与上述同样地进行数据的收发。图2的m1~m4为在各线圈之间产生的磁通。此时,优选中介层3的收发线圈c1~c4的各中心轴分别与对应的存储器芯片的收发线圈c11~c14的中心轴一致。由此,能够抑制在进行收发的线圈之间信号衰减而变得无法进行通信的情况。此外,能够避免为了进行通信而需要更大的电力的情况。

64.在本实施方式中,在构成层叠dram的多个存储器芯片中,各存储器芯片的第1收发

电路配置在俯视时彼此重叠的位置。另一方面,各存储器芯片的第1收发线圈配置在俯视时这些第1收发电路的周围的彼此不重叠的位置。此时,中介层的第2收发线圈的中心轴优选像上述那样分别与对应的第1收发线圈的中心轴一致。此外,优选第1收发线圈在俯视时对称地配置,优选第1引线的长度在存储器芯片之间是相等的。

65.图4(a)~(d)为存储器芯片11~14的示意性局部俯视图。在这些图中示出了设置在存储器芯片11~14的收发线圈c11~c14、从这些收发线圈的两端引出的引线l11~l14、与这些引线连接并在与收发线圈c11~c14之间进行信号的输入输出的收发电路tr11~tr14。

66.在图4(a)所示的存储器芯片11中,收发线圈c11与收发电路tr11沿y方向排列。图4(c)所示的存储器芯片13也是相同的,但收发线圈c13与收发电路tr13的位置关系与图4(a)相差180度。此外,在图4(b)所示的存储器芯片12中,收发线圈c12与收发电路tr12沿x方向排列。图4(d)所示的存储器芯片14也是相同的,但收发线圈c14与收发电路tr14的位置关系与图4(b)相差180度。以收发电路tr11~tr14在俯视时重叠的方式层叠这种存储器芯片11~14的结构为图2所示的结构。收发电路tr11~tr14配置在存储器芯片11~14中的共同的位置、即图2的用虚线cl表示的位置。通过像这样形成半导体装置1的平面图(floor-plan),能够将大量的收发电路、进而收发线圈高效率地设置在各存储器芯片11~14。因此,能够使半导体装置小型化、高集成化。

67.此外,根据图2的结构,在俯视层叠dram4时,在彼此重叠的收发电路tr11~tr14的周围,收发线圈c11~c14配置在彼此不重叠的位置。此时,优选收发线圈c11~c14像图2所示的那样在俯视时对称地配置。通过将收发线圈c11~c14配置在彼此不重叠的位置,从而彼此的线圈间的距离增加,因此能够使各收发线圈中的串扰的接收电压减小,从而不会影响到来自中介层3的对应的收发线圈的接收信号电压。进而,如果将收发线圈c11~c14以俯视时成为对称的方式配置,则能够进一步高效率地将不限于这些的大量的收发线圈配置在各存储器芯片11~14。另外,在本说明书中,对称是指线对称或点对称,或者线对称和点对称双方。例如,在图2中,俯视时的收发线圈c11~c14的配置是线对称的配置,并且也是点对称的配置。

68.此外,如图4(a)~4(d)所示,优选引线l11~l14的长度彼此相等。如果引线l11~l14的长度不同,则这些引线的电阻也不同,因此在收发线圈c11~c14与收发电路tr11~tr14之间输入输出的信号的衰减的程度产生差异。通过将引线l11~l14的长度设为相同,无论收发线圈与收发电路是哪种组合,都能够输入输出相同电平的信号。

69.图5为中介层3的示意性局部俯视图。在该图中示出了收发线圈c1~c4、从这些收发线圈的两端引出的引线l1~l4、与这些引线连接并在与收发线圈c1~c4之间进行信号的输入输出的收发电路tr1~tr4。在此,如果将收发线圈c1、引线l1、以及收发电路tr1设为1组,同样地,对其它的收发线圈c2~c4、引线l2~l4、以及收发电路tr2~tr4也进行分组,则能够形成4组由收发线圈、引线、以及收发电路构成的组。如果将这些配置在适当的大小的圆10的圆周上,将收发电路tr1~tr4朝向圆10的内侧对称地配置,将收发线圈c1~c4朝向圆10的外侧对称地配置,则成为如图5所示那样。此时,优选收发线圈c1~c4的中心轴像已经叙述的那样分别与对应的存储器芯片的收发线圈c11~c14的中心轴一致。

70.此外,优选中介层3的引线l1~l4具有彼此相等的长度。如果引线l1~l4的长度不

同,则这些引线的电阻也不同,因此在收发线圈c1~c4与收发电路tr1~tr4之间输入输出的信号的衰减的程度产生差异。通过将引线l1~l4的长度设为相同,无论收发线圈与收发电路为哪种组合,都能够输入输出相同电平的信号。

71.另外,在图2和图5中,中介层3的收发电路tr1~tr4配置在彼此不重叠的位置,但本实施方式并不限于此。例如,也可以在图5的圆10的中心设置1个收发电路,该收发电路具有与收发线圈c1~c4分别对应的4个电路部分、以及被这些收发线圈c1~c4共同使用的电路部分。

72.实施方式2

73.图6为表示本实施方式的半导体装置的一个例子的局部剖视图。在图6的半导体装置101中,在基板105上经由焊料球106安装了处理器102,此外,设置有在与基板105垂直的方向上层叠了dram(dynamic random access memory:动态随机访问存储器)的5枚存储器芯片111、11~14而成的层叠dram104。

74.图7为层叠dram104的剖面示意图。在该图中,示出了与图2相同的符号的部分意味着具有相同的结构。另外,层叠dram104是在存储器芯片111的下方层叠4枚存储器芯片11~14而成的,但在存储器芯片111的下方层叠的芯片数并不限于此。

75.层叠dram104的最上层的存储器芯片111兼具作为存储器芯片的本来的功能和作为中介层的功能。根据该结构,不需要将中介层作为与层叠dram不同的部件而设置,因此能够减小在基板105上设置的层叠体整体的厚度。

76.为了使存储器芯片111作为中介层发挥功能,存储器芯片111具有与各dram的存储芯片11~14的收发线圈c11~c14对应的收发线圈c1~c4。收发线圈c11~c14、c1~c4与实施方式1中叙述的收发线圈c11~c14、c1~c4相同,分别与本发明的第1收发线圈和第2收发线圈对应。

77.在存储器芯片111的收发线圈(c1~c4)和其它的存储器芯片11~14的收发线圈(c11~c14),分别设置有从线圈的两端引出的引线(l1~l4、l11~l14),并且,在引线上分别连接有与对应的收发线圈之间进行信号的输入输出的收发电路(tr1~tr4、tr11~tr14)。在此,引线l1~l4为本发明的第2引线的优选的一个例子,引线l11~l14为本发明的第1引线的优选的一个例子。此外,收发电路tr1~tr4为本发明的第2收发电路的优选的一个例子,收发电路tr11~tr14为本发明的第1收发电路的优选的一个例子。

78.如图7所示,在收发线圈c1与收发线圈c11之间,通过如由箭头m1所示那样的磁通而产生电磁耦合,由此进行数据的收发。此外,在收发线圈c2与收发线圈c12之间、收发线圈c3与收发线圈c13之间、收发线圈c4与收发线圈c14之间也分别通过由箭头m2~m4所示的磁通而产生电磁耦合,从而进行数据的收发。此时,优选存储器芯片111的收发线圈c1~c4的各中心轴分别与对应的存储器芯片的收发线圈c11~c14的中心轴一致。由此,能够抑制在进行收发的线圈之间信号衰减而变得无法进行通信的情况。此外,能够避免为了进行通信而需要更大的电力。

79.存储器芯片11~14的收发电路tr11~tr14配置在俯视时彼此重叠的位置。即,收发电路tr11~tr14配置在存储器芯片11~14中共同的位置,具体而言,配置在图7的用虚线cl表示的位置。另一方面,存储器芯片11~14的收发线圈c11~c14配置在俯视时这些收发电路tr11~tr14的周围的彼此不重叠的位置。此时,优选存储器芯片111的收发线圈c1~c4

的中心轴像上述那样分别与对应的存储器芯片11~14的收发线圈c11~c14的中心轴一致。此外,优选收发线圈c11~c14在俯视时对称地配置,优选引线的长度l11~l14在存储器芯片11~14之间是相等的。

80.通过像上述那样形成半导体装置101的平面图,能够将大量的收发电路、进而收发线圈高效率地设置在各存储器芯片11~14。因此,能够使半导体装置小型化、高集成化。此外,通过将收发线圈c11~c14配置在彼此不重叠的位置,从而彼此的线圈间的距离增加,因此能够使各收发线圈中的串扰的接收电压减小,从而不会影响到来自存储器芯片111的对应的收发线圈的接收信号电压。进而,如果将收发线圈c11~c14以俯视时成为对称的方式配置,则能够进一步高效率地将不限于这些的大量的收发线圈配置在存储器芯片11~14。此外,通过将引线l11~l14的长度设为彼此相等,能够使在收发线圈c11与收发电路tr11之间、收发线圈c12与收发电路tr12之间、收发线圈c13与收发电路tr13之间、或者收发线圈c14与收发电路tr14之间输入输出的各信号的电平相同。

81.作为中介层发挥功能的存储器芯片111的平面图与在实施方式1中使用图5叙述的中介层3的平面图相同。即,如果将存储器芯片111的收发线圈c1、引线l1、以及收发电路tr1设为1组,同样地,对其它的收发线圈c2~c4、引线l1~l4、以及收发电路tr2~tr4也进行分组,则能够形成4组由收发线圈、引线、以及收发电路构成的组。如果将这些配置在适当的大小的圆的圆周上,将收发电路tr2~tr4朝向圆的内侧对称地配置,将收发线圈c1~c4朝向圆的外侧对称地配置,则成为如图7所示那样。此时,优选收发线圈c1~c4的中心轴像已经叙述的那样分别与对应的存储器芯片的收发线圈c11~c14的中心轴一致。

82.此外,优选存储器芯片111的引线l1~l4具有彼此相等的长度。如果引线l1~l4的长度不同,则这些引线的电阻也不同,因此在收发线圈c1~c4与收发电路tr1~tr4之间输入输出的信号的衰减的程度产生差异。通过将引线l1~l4的长度设为相同,无论收发线圈与收发电路是哪种组合,都能够输入输出相同电平的信号。

83.另外,在图7中,存储器芯片111的收发电路tr1~tr4配置在彼此不重叠的位置,但本实施方式并不限于此。例如,也可以在上述圆的中心设置1个收发电路。在该情况下,收发电路能够具有例如与收发线圈c1~c4分别对应的4个电路部分、以及被这些收发线圈c1~c4共同使用的电路部分。

84.实施方式3

85.本实施方式的半导体装置与实施方式1中叙述的图1同样地,能够采用在基板上经由焊料球安装处理器的结构。在该基板上设置在与基板垂直的方向上层叠了dram(dynamic random access memory:动态随机存取存储器)的存储器芯片的层叠结构(层叠dram)。此外,在层叠dram中的存储器芯片的层叠方向的一端配置中介层。并且,处理器和dram经由中介层进行电连接。

86.图8为示意地表示中介层20和层叠dram204的结构的立体图。在该图中,层叠dram204是由8枚dram的存储器芯片21~28构成的,但存储器芯片的层叠数并不限于此。

87.在图8中,在中介层20配置有收发线圈c21~c24、从这些收发线圈的两端引出的引线l21~l24、与这些引线连接并在与收发线圈c21~c24之间进行信号的输入输出的收发电路tr21~tr24。这些与实施方式1中叙述的中介层3的收发线圈c1~c4、引线l1~l4、收发电路tr1~tr4相同。另外,收发线圈c21~c24为本发明的第2收发线圈的优选的一个例子。此

外,引线l21~l24为本发明的第2引线的优选的一个例子。进而,收发电路tr21~tr24为本发明的第2收发电路的优选的一个例子。

88.在图8中,配置在存储器芯片21~28的收发线圈、引线、以及收发电路均被省略,但这些与实施方式1中使用图2说明的存储器芯片11~14相同。即,在存储器芯片21、22配置有与存储器芯片11相同的收发线圈、引线、以及收发电路。此外,在存储器芯片23、24配置有与存储器芯片12相同的收发线圈、引线、以及收发电路。进而,在存储器芯片25、26配置有与存储器芯片13相同的收发线圈、引线、以及收发电路。此外,在存储器芯片27、28配置有与存储器芯片14相同的收发线圈、引线、以及收发电路。这些存储器芯片21~28与中介层20的配置关系也与图2相同。

89.像这样,本实施方式在具有收发线圈、引线、以及收发电路的配置相同的多个存储器芯片的方面与实施方式1不同。具体而言,构成层叠dram204的存储器芯片21~28被分割为4个(多个)组单元,构成各组单元g1~g4的存储器芯片的收发线圈、引线、以及收发电路分别配置在俯视时彼此重叠的位置。即,图8中构成组g1的存储器芯片22的收发线圈、引线、以及收发电路的配置与同组g1的存储器芯片21相同。同样地,构成组g2的存储器芯片23和24、构成组g3的存储器芯片25和26、构成组g4的存储器芯片27和28的收发线圈、引线、以及收发电路的配置也分别相同。根据这种结构,不需要按每个存储器芯片设置不同配置的收发线圈、引线、以及收发电路。因此,能够容易地在层叠了4枚dram的存储器芯片的产品与层叠了8枚dram的存储器芯片的产品之间进行切换,使半导体装置的制造工艺简化。

90.图9(a)~图9(d)为存储器芯片21~28的示意性局部俯视图。在这些图中示出了设置在存储器芯片21~28的收发线圈c221~c228、从这些收发线圈的两端引出的引线l221~l228、与这些引线连接并在与收发线圈c221~c228之间进行信号的输入输出的收发电路tr221~tr228。在此,收发线圈c221~c228为本发明的第1收发线圈的优选的一个例子。此外,引线l221~l228为本发明的第1引线的优选的一个例子。进而,收发电路tr221~tr228为本发明的第1收发电路的优选的一个例子。

91.在图9(a)所示的存储器芯片21(22)中,收发线圈c221(c222)与收发电路tr221(tr222)沿y方向排列。图9(c)所示的存储器芯片25(26)也是相同的,但收发线圈c225(c226)与收发电路tr225(tr226)的位置关系与图9(a)相差180度。

92.此外,在图9(b)所示的存储器芯片23(24)中,收发线圈c223(c224)与收发电路tr223(tr224)沿x方向排列。图9(d)所示的存储器芯片27(28)也是相同的,但收发线圈c227(c228)与收发电路tr227(tr228)的位置关系与图9(b)相差180度。

93.层叠dram204是以收发电路tr11~tr14在俯视时重叠的方式层叠这种存储器芯片21~28而构成的。即,收发电路tr221~tr228配置在存储器芯片21~28中共同的位置。通过像这样形成半导体装置的平面图,能够将大量的收发电路、进而收发线圈c221~c228高效率地设置在各存储器芯片21~28。因此,能够使半导体装置小型化、高集成化。

94.此外,根据上述的结构,在俯视层叠dram204时,在彼此重叠的收发电路tr221~tr228的周围,收发线圈c221~c228配置在彼此不重叠的位置。此时,优选收发线圈c221~c228与实施方式1同样地在俯视时对称地配置。通过将收发线圈c221~c228配置在彼此不重叠的位置,从而彼此的线圈间的距离增加,因此能够使各收发线圈中的串扰的接收电压减小,从而不会影响到来自中介层20的对应的收发线圈的接收信号电压。进而,如果将收发

线圈c221~c228以俯视时成为对称的方式配置,则能够进一步高效率地将不限于这些的大量的收发线圈配置在各存储器芯片21~28。

95.此外,优选图9(a)~9(d)所示的引线l221~l228的长度彼此相等。如果引线l221~l228的长度不同,则这些引线的电阻也不同,因此在收发线圈c221~c228与收发电路tr221~tr228之间输入输出的信号的衰减的程度产生差异。通过将引线l221~l228的长度设为相同,无论收发线圈与收发电路是哪种组合,都能够输入输出相同电平的信号。

96.图10为中介层20的示意性局部俯视图。在图10中,如果将收发线圈c21、引线l21、以及收发电路tr21设为1组,同样地,对其它的收发线圈c22~c24、引线l22~l24、以及收发电路tr22~tr24也进行分组,则能够形成4组由收发线圈、引线、以及收发电路构成的组。如果将这些配置在(与图5的圆10相同的)适当的大小的圆的圆周上,将收发电路tr21~tr24朝向圆的内侧对称地配置,将收发线圈c21~c24朝向圆的外侧对称地配置,则成为如图10所示那样。

97.此外,优选中介层20的引线l21~l24具有彼此相等的长度。如果引线l21~l24的长度不同,则这些引线的电阻也不同,因此在收发线圈c21~c24与收发电路tr21~tr24之间输入输出的信号的衰减的程度产生差异。通过将引线l21~l24的长度设为相同,无论收发线圈与收发电路是哪种组合,都能够输入输出相同电平的信号。

98.图11为表示将图10的a-a线投影到图8的存储器芯片21~28时的、中介层20和层叠dram204的剖面结构的示意图。另外,在该图中,为了进行说明仅示出了收发线圈。

99.如图11所示,在收发线圈c21与收发线圈c221之间、以及收发线圈c21与收发线圈c222之间,通过分别由图11的箭头所示的磁通m21、m22而产生电磁耦合。如该图所示,优选中介层20的收发线圈c21以其中心轴与存储器芯片21的收发线圈c221和存储器芯片22的收发线圈c222的各中心轴一致的方式配置。

100.此外,在收发线圈c24与收发线圈c227之间、以及收发线圈c24与收发线圈c228之间,通过分别由图11的箭头所示的磁通m27、m28而产生电磁耦合。优选中介层20的收发线圈c24以其中心轴与存储器芯片27的收发线圈c227和存储器芯片28的收发线圈c228的各中心轴一致的方式配置。

101.图12为表示将图10的b-b线投影到图8的存储器芯片21~28时的、中介层20和层叠dram204的剖面结构的示意图。另外,在该图中,为了进行说明仅示出了收发线圈。

102.如图12所示,在收发线圈c22与收发线圈c223之间、以及收发线圈c22与收发线圈c224间,通过分别由图12的箭头所示的磁通m23、m24而产生电磁耦合。如该图所示,优选中介层20的收发线圈c22以其中心轴与存储器芯片23的收发线圈c223和存储器芯片24的收发线圈c224的各中心轴一致的方式配置。

103.此外,在收发线圈c23与收发线圈c225之间、以及收发线圈c23与收发线圈c226之间,通过分别由图12的箭头所示的磁通m25、m26而产生电磁耦合。优选中介层20的收发线圈c23以其中心轴与存储器芯片25的收发线圈c225和存储器芯片26的收发线圈c226的各中心轴一致的方式配置。

104.这样,通过使中介层20的收发线圈c21~c24的各中心轴与对应的存储器芯片21~28的收发线圈c221~c228的中心轴一致,能够抑制信号在进行收发的线圈之间衰减而变得无法进行通信的情况。此外,能够避免为了进行通信而需要更大的电力。

105.另外,在图8和图10中,中介层20的收发电路tr21~tr24配置在彼此不重叠的位置,但本实施方式并不限于此。例如,也可以在上述的圆的中心设置1个收发电路,该收发电路具有与收发线圈c21~c24分别对应的4个电路部分、以及被这些收发线圈c1~c4共同使用的电路部分。

106.具有收发线圈、引线、以及收发电路的配置相同的多个存储器芯片的层叠dram204与中介层20之间的数据通信能够通过例如以下那样来进行。

107.各存储器芯片21~28除了分别具有存储器电路之外,还能够分别具有如图13所示的芯片选择电路31~38。

108.如图13所示,芯片选择电路31~38彼此连接,分别生成向对应的存储器芯片赋予的识别码s1。此外,芯片选择电路31~38将从外部经由中介层20而通过共同的信号线60输入的用于芯片选择的地址s2与芯片的识别码s1进行比较,从而输出芯片选择信号s3。另外,中介层20也可以具有生成地址s2并输出的功能。

109.芯片选择电路31~38针对存储器芯片21~28分别具有输出彼此不同的识别码s1的运算电路、和对识别码s1和地址s2进行比较而输出芯片选择信号s3的比较电路39~46。在图13中,运算电路为进行将输入值加1的增量运算的3位(bit)的增量电路47~54。

110.在芯片选择电路31中,构成识别码sn的3位α1、α2、α3均被接地。因此,0被输入到增量电路47,赋予0作为存储器芯片21的识别码s1。从增量电路47向芯片选择电路32输入将0和1相加而得到的值,因此存储器芯片22的识别码变为1。向增量电路48输入1,并输出与1相加后的数、即2。以下,同样地对存储器芯片23~28分别赋予2~7的识别码。

111.为了进行3位的增量运算,增量电路47~54具有3个1位增量电路。向各1位增量电路输入构成芯片识别码的3位α1、α2、α3,从各1位增量电路输出3位β1、β2、β3。

112.比较电路39~46具有3个exor电路和1个and电路。对1个exor电路输入识别码s1的位α1和地址s2的位β1。对另1个exor电路输入识别码s1的位α2和地址s2的位β2。对剩余的1个exor电路输入识别码s1的位α3和地址s2的位β3。各exor电路在所输入的位不一致时输出0,在位一致时输出1。对and电路输入来自3个exor电路的输出值。当检测为3个exor电路全部一致时,and电路输出1,芯片选择信号s3变为高(high)。另一方面,当检测为3个exor电路中的任一个不一致时,and电路输出0,芯片选择信号s3变为低(low)。

113.根据以上的结构,即使收发线圈、引线、以及收发电路的配置相同的存储器芯片存在多个,也能够选择所期望的存储器芯片而在与中介层之间进行数据通信。另外,芯片选择电路并不限于图13的结构,只要是能够从相同的容量以及结构的存储器芯片中选择出特定的存储器芯片的芯片选择电路,就可以采用其它公知的结构。

114.另外,本发明并不限定于上述各实施方式,能够在不脱离本发明的主旨的范围内进行各种变形来实施。

115.此外,在上述各实施方式中,省略了对装置结构、控制方法等、对于本发明的说明而言并不直接需要的部分的记载,但能够酌情选择并使用半导体装置所需要的装置结构、控制方法是不言自明的。另外,具有本发明的要素、本领域技术人员可酌情变更设计的全部的半导体装置均包含于本发明的范围。

116.附图标记说明

117.1,101:半导体装置;

118.2,102:处理器;

119.3,20:中介层;

120.4,104,204:层叠dram;

121.5,105:基板;

122.6,106:焊料球;

123.11~14、21~28、111:存储器芯片。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1