一种基于IPD技术的小型化高性能零点可控带通滤波器的制作方法

一种基于ipd技术的小型化高性能零点可控带通滤波器

技术领域

1.本发明属于射频/微波/通信技术领域,具体涉及一种基于ipd技术的小型化高性能零点可控带通滤波器。

背景技术:

2.滤波器几乎是所有电子系统中普遍存在的器件,尤其在无线通信系统中发挥着重要作用,也正因如此,高性能、小型化的滤波器设计一直是电子行业研究的热点。而带通滤波器是一个允许特定频段的波通过同时屏蔽其他频段的设备。一个理想的带通滤波器应该有一个完全平坦的通带,即在通带内没有衰减,并且在通带之外所有频率都被完全衰减掉,另外,通带外的转换在极小的频率范围完成。目前的带通滤波器设计主要有以下问题:随着频率增大,寄生效应也随之产生,通带中将出现谐波,这使滤波器的通带性能受到了影响;基于微带线结构的平面带通滤波器虽然体积较小,但是通常插损较大,带外抑制较差;基于波导结构的带通滤波器虽然性能较好,但是通常体积较大,可集成度较低,不能满足射频前段对小型化的需求;基于高介电常数的陶瓷带通滤波器,虽然带外抑制较好、温度系数稳定,但是对制作工艺要求较高,故成本较高。除此之外,当前大多数的带通滤波器的零点都是由交叉耦合形成的,并没有可以控制零点的单独电路。

技术实现要素:

3.本发明的目的在于针对背景技术中所提到的带通滤波器性能较差、成本较高、尺寸较大、缺少单独控制零点电路的问题,设计了一种基于ipd技术的小型化高性能零点可控带通滤波器,采用ipd工艺设计和新型电路拓扑结构,具有成本低、集成度高、性能好、有单独控制零点电路的优点,可以满足当前射频/微波/通信技术领域的需求。本发明采用的技术方案如下:

4.一种基于ipd技术的小型化高性能零点可控带通滤波器,主要包括:

5.介质层(2);

6.金属层(1);

7.接地底板(3),位于介质层(2)的下表面;

8.贯穿介质层(2)的接地过孔,用于连接金属层(1)和接地底板(3);

9.主体电路;

10.输入输出端口;

11.其中,所述输入端口包括第一输入端口焊盘(5-1)、第二输入端口焊盘(5-2)、第三输入端口焊盘(5-3);输出端口包括第一输出端口焊盘(5-4)、第二输出端口焊盘(5-5)、第三输出端口焊盘(5-6);第一输入端口焊盘(5-1)通过第一接地过孔(4-1)穿过介质层(2),与接地地板(3)相连;所述的第三输入端口焊盘(5-3)通过第二接地过孔(4-2)穿过介质层(2),与接地地板(3)相连;所述的第一输出端口焊盘(5-4)通过第三接地过孔(4-3)穿过介质层(2),与接地地板(3)相连;所述的第三输出端口焊盘(5-6)通过第四接地过孔(4-4)穿

过介质层(2),与接地地板(3)相连。所述第二输入端口焊盘(5-2)为信号接入端,第二输出端口焊盘(5-5)为信号接出端。

12.所述主体电路包括第一串联电容(6)、第一并联电感(7)、第一串联电感(8)、第二并联电感(9)、第二串联电容(10)、第三串联电容(14)、第四串联电容(15)、零点调控部件;第一串联电容(6)的一端与第三串联电容(14)的一端连接后接第二输入端口焊盘(5-2),第一串联电容(6)的另一端与第一并联电感(7)的一端、第一串联电感(8)的一端连接,第一并联电感(7)的另一端接第三输入端口焊盘(5-3),第一串联电感(8)的另一端与第二并联电感(9)的一端、第二串联电容(10)的一端连接,第三串联电容(14)的另一端与第四串联电容(15)的一端连接,第二并联电感(9)的另一端接第三输出端口焊盘(5-6),第四串联电容(15)的另一端与第二串联电容(10)的另一端连接后接零点调控部件的输入端;

13.所述零点调控部件包括第一并联电容(11)、第二串联电感(12)和第二并联电容(13);

14.当第一并联电容(11)的一端与第二串联电感(12)的一端连接后作为零点调控部件的输入端,接第四串联电容(15)的另一端与第二串联电容(10)的另一端;第一并联电容(11)的另一端接第三输出端口焊盘(5-6),第二串联电感(12)的另一端与第二并联电容(13)的一端连接后接第二输出端口焊盘(5-5),第二并联电容(13)的另一端接第一输出端口焊盘(5-4)时,在高边带形成一个零点;

15.当第一并联电容(11)的一端与第二串联电感(12)的一端连接后作为零点调控部件的输入端,接第四串联电容(15)的另一端与第二串联电容(10)的另一端;同时第二串联电感(12)的一端接第二输出端口焊盘(5-5);第一并联电容(11)的另一端接第三输出端口焊盘(5-6),第二串联电感(12)的另一端与第二并联电容(13)的一端连接,第二并联电容(13)的另一端接第一输出端口焊盘(5-4)时,在低边带形成一个零点;

16.作为优选,第一并联电感(7)、第一串联电感(8)、第二并联电感(9)、第二串联电感(12)采用螺旋电感,其形状不仅限于圆形、椭圆形、矩形、六边形、八边形等多边形;

17.作为优选,第一串联电容(6)、第二串联电容(10)、第三串联电容(14)、第四串联电容(15)、第一并联电容(11)、第二并联电容(13)采用平面电容,其结构不仅限于平行板结构、交指型、分形结构;

18.作为优选,所述介质层采用gaas工艺、si工艺或玻璃等半导体工艺实现。

19.本发明的有益效果为:

20.1、采用ipd工艺的设计,用螺旋电感和平面电容结构代替传统的分立元件结构的电容电感,在提高滤波器性能的同时实现小型化,且具有成本低、集成度高的优点,适合批量生产;

21.2、本发明第三串联电容14与第四串联电容15通过串联的方式减小电容值,从而减小工艺的误差,且引入交叉耦合在左右边带各形成一个零点;

22.3、采用独立控制零点的电路,可以在低边带或者高边带加入一个零点,提高带外抑制,减少谐波干扰;

23.4、本发明通过改变螺旋电感和平面电容的个数和数值来改变滤波器的工作频率,适用于vhf、uhf、700&800mhz、wifi以及5g等各个频段。

附图说明

24.图1(a)为本发明的可控零点在高边带的等效电路图;

25.图1(b)为本发明的可控零点在低边带的等效电路图;

26.图2为本发明的馈电结构结构示意图;

27.图3(a)为本发明的可控零点在高边带的电路拓扑结构示意图;

28.图3(b)为本发明的可控零点在低边带的电路拓扑结构示意图;

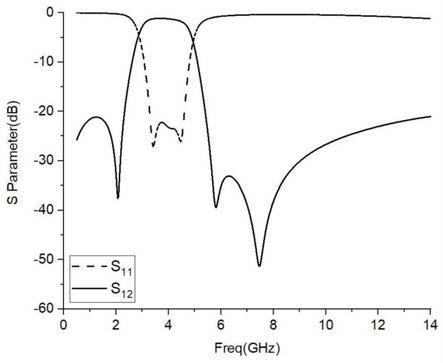

29.图4为本发明的可控零点在高边带的s参数结果图;

30.图5为本发明的可控零点在低边带的s参数结果图;

31.图中介质层2和其上表面的金属层1、接地底板3、第一接地过孔4-1、第二接地过孔4-2、第三接地过孔4-3、第四接地过孔4-4、第一输入端口焊盘5-1、第二输入端口焊盘5-2、第三输入端口焊盘5-3、第一输出端口焊盘5-4、第二输出端口焊盘5-5、第三输出端口焊盘5-6、第一串联电容6、第一并联电感7、第一串联电感8、第二并联电感9、第二串联电容10、第一并联电容11、第二串联电感12、第二并联电容13、第三串联电容14、第四串联电容15。

具体实施方式

32.为了更加清楚地说明本发明解决的问题、采用的技术方案和有益效果,下面结合图示说明本发明的具体实施方式,这里所描述的优选实施例子仅用于说明和解释本发明,并不用以限制本发明,凡是在本发明的精神和原则之内所做的修改、等同替换和改进等,均应在本发明的保护范围之内。

33.如图2所示,一种基于ipd技术的小型化高性能零点可控带通滤波器包括介质层2;金属层1;接地底板3,位于介质层(2)的下表面;贯穿介质层(2)的接地过孔,用于连接金属层(1)和接地底板(3);主体电路;输入输出端口;

34.其中,所述输入端口包括第一输入端口焊盘5-1、第二输入端口焊盘5-2、第三输入端口焊盘5-3;输出端口包括第一输出端口焊盘5-4、第二输出端口焊盘5-5、第三输出端口焊盘5-6;第一输入端口焊盘5-1通过第一接地过孔4-1穿过介质层2,与接地地板3相连;所述的第三输入端口焊盘5-3通过第二接地过孔4-2穿过介质层2,与接地地板3相连;所述的第一输出端口焊盘5-4通过第三接地过孔4-3穿过介质层2,与接地地板3相连;所述的第三输出端口焊盘5-6通过第四接地过孔4-4穿过介质层2,与接地地板3相连。所述第二输入端口焊盘5-2为信号接入端,第二输出端口焊盘5-5为信号接出端。

35.所述主体电路包括第一串联电容6、第一并联电感7、第一串联电感8、第二并联电感9、第二串联电容10、第三串联电容14、第四串联电容15、零点调控部件;第一串联电容6的一端与第三串联电容14的一端连接后接第二输入端口焊盘5-2,第一串联电容6的另一端与第一并联电感7的一端、第一串联电感8的一端连接,第一并联电感7的另一端接第三输入端口焊盘5-3,第一串联电感8的另一端与第二并联电感9的一端、第二串联电容10的一端连接,第三串联电容14的另一端与第四串联电容15的一端连接,第二并联电感9的另一端接第三输出端口焊盘5-6,第四串联电容15的另一端与第二串联电容10的另一端连接后接零点调控部件的输入端;

36.所述零点调控部件包括第一并联电容11、第二串联电感12和第二并联电容13;

37.如图3(a)所示,当第一并联电容11的一端与第二串联电感12的一端连接后作为零

点调控部件的输入端,接第四串联电容15的另一端与第二串联电容10的另一端;第一并联电容11的另一端接第三输出端口焊盘5-6,第二串联电感12的另一端与第二并联电容13的一端连接后接第二输出端口焊盘5-5,第二并联电容13的另一端接第一输出端口焊盘5-4时,在高边带形成一个零点。

38.如图3(b)所示,当第一并联电容11的一端与第二串联电感12的一端连接后作为零点调控部件的输入端,接第四串联电容15的另一端与第二串联电容10的另一端;同时第二串联电感12的一端接第二输出端口焊盘5-5;第一并联电容11的另一端接第三输出端口焊盘5-6,第二串联电感12的另一端与第二并联电容13的一端连接,第二并联电容13的另一端接第一输出端口焊盘5-4时,在低边带形成一个零点。

39.图1(a)为图3(a)所示主体电路的可控零点在高边带的等效电路图;

40.图1(b)为图3(b)所示主体电路的可控零点在低边带的等效电路图;

41.第一串联电容6等效电容c1,第一并联电感7等效电感l3、第一串联电感8等效电感l1、第二并联电感9等效电感l4、第二串联电容10等效电容c2、第三串联电容14等效电容c3、第四串联电容15等效电容c4、第一并联电容11等效电容c5、第二串联电感12等效电感l2、第二并联电容13等效电容c6;

42.如图1(a)、(b)所示,该电路的工作原理为:由电容c1、电感l1、电感l2、电感l3、电容c2构成基本的谐振电路,该谐振电路与传统的带通滤波器谐振电路有所不同;然后在谐振电路的首尾两端串联接入电容c3和电容c4,从而在高、低边带各引入一个零点;在谐振电路末端加入一个单独控制零点的电路,由电感l2和电容c5、电容c6构成的图1(a)所示电路使得零点在高边带,由电感l2和电容c5、电容c6构成的图1(b)所示电路使得零点在低边带。

43.如图4所示,本实施例的带通滤波器的插损较小,约为1.2db;通带内的回波损耗约为-23db;零点可控电路形成的零点在高边带,抑制了高次谐波,带外抑制较好。

44.如图5所示,本实施例的带通滤波器的插损较小,约为1.5db;通带内的回波损耗约为-18db;零点可控电路形成的零点在低边带,抑制了高次谐波,带外抑制较好。

45.上述实施例并非是对于本发明的限制,本发明并非仅限于上述实施例,只要符合本发明要求,均属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1