套刻标记结构及其形成方法与流程

本发明涉及半导体制造,尤其涉及一种套刻标记结构及其形成方法。

背景技术:

1、光刻是通过对准、曝光等一系列步骤将掩膜图案图形转移到晶圆上的工艺过程。在半导体芯片的制造过程中,通常需要通过多层光刻工艺才能完成整个制造过程。套刻误差(overlay,ovl)是指在光刻制造工艺中,当层图形和前层图形的相对位置偏差。实现套刻精度补偿和精确控制是确保半导体器件性能的关键。

2、晶圆上专门用来测量套刻误差的图形被称为套刻标记(overlay mark)。这些图形在设计掩模时已经被放置在了指定的区域,通常是在曝光区域的边缘,通常为切割道(scribeline)中。为了节省位置,套刻标记从一开始的大于20μm左右的图形,缩小到15μm×15μm的图形,又进一步缩小成了10μm×10μm的更小的图形。

3、随着先进制程的推进,半导体器件的特征尺寸的不断缩小,光刻工艺套刻精度窗口越来越小,现有的套刻标记方法有待于进一步提高。

技术实现思路

1、本发明解决的技术问题是提供一种套刻标记结构及其形成方法,以提高测量精度。

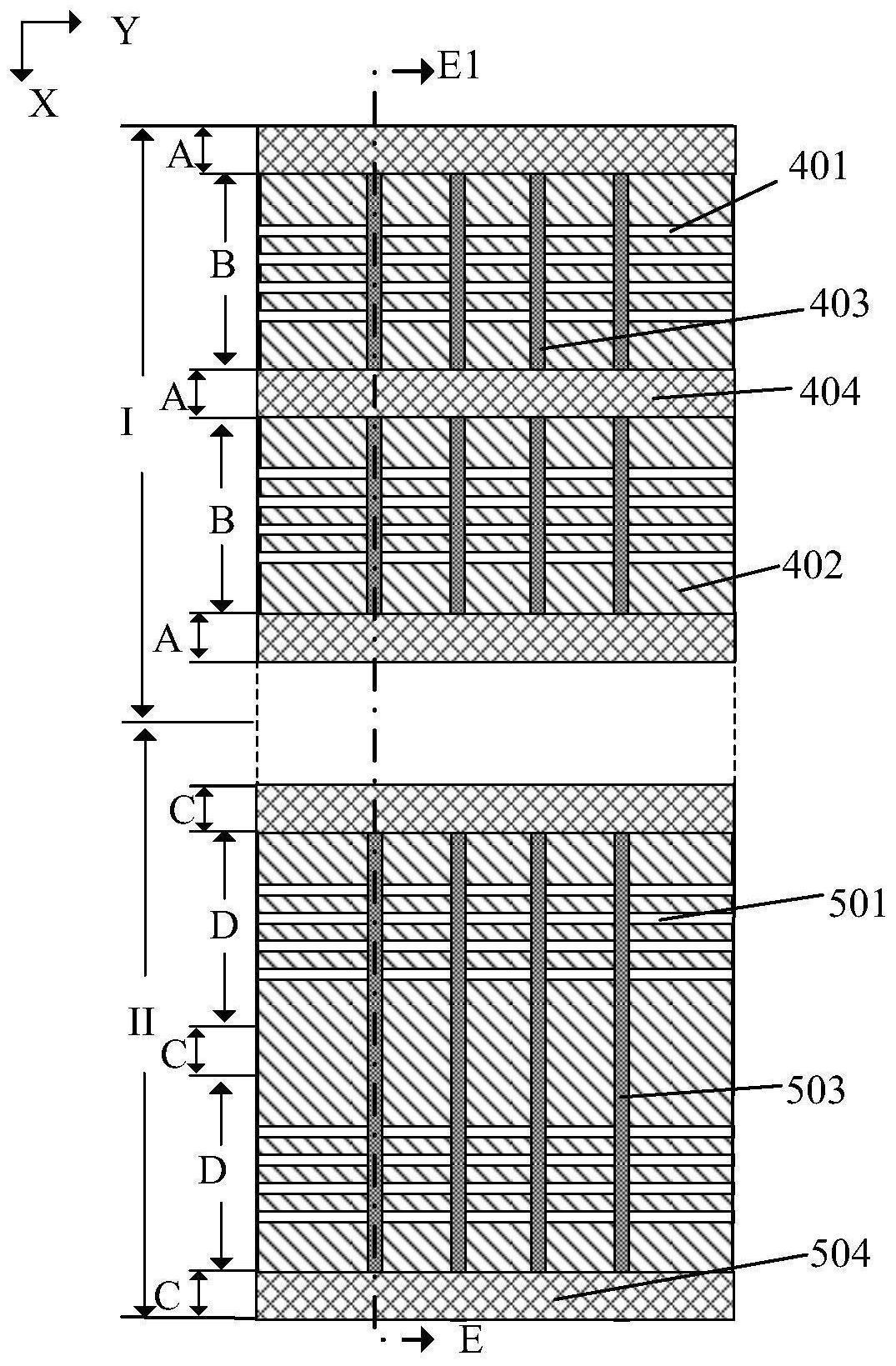

2、为解决上述技术问题,本发明的技术方案提供一种套刻标记结构,包括:基底,所述基底包括若干芯片区,各芯片区包括结构区和与所述结构区相邻的至少一个伪结构区,各伪结构区内包括至少一个标记区;位于基底上的至少两层重叠的器件层,每层器件层内具有若干标记结构,且每层器件层内的每个标记结构位于至少一个标记区上。

3、可选的,至少两层重叠的器件层中包括位于基底表面的第一器件层,所述第一器件层内的标记结构包括若干标记鳍部,所述若干标记鳍部平行于第二方向,且沿第一方向排布。

4、可选的,沿第一方向上,相邻标记鳍部之间的距离范围为30nm至500nm。

5、可选的,各个标记鳍部包括若干第一鳍部,所述若干第一鳍部平行于第二方向,且沿第一方向排布。

6、可选的,所述第一器件层内还具有位于所述伪结构区上的若干伪鳍部。

7、可选的,所述第一器件层内还具有位于所述结构区上的若干第二鳍部。

8、可选的,至少两层重叠的器件层中包括位于基底表面的第二器件层,所述第二器件层内的标记结构包括若干标记隔离条纹,各所述标记隔离条纹平行于第二方向,且沿第一方向排布,所述标记隔离条纹在所述基底表面的投影位于相邻的标记鳍部在所述基底表面的投影的中间。

9、可选的,沿所述第一方向上,相邻的所述标记隔离条纹之间的距离范围为60nm至1000nm。

10、可选的,所述第一器件层和所述第二器件层之间还具有衬底层,所述衬底层包括横跨所述标记鳍部,且位于所述标记鳍部部分侧壁和顶部表面,所述若干辅助栅极平行于第二方向,且沿第一方向排布,且各所述标记隔离条纹在沿着所述第二方向切断所述若干辅助栅。

11、可选的,所述第二器件层的还具有位于所述伪结构区上的若干伪栅。

12、可选的,所述标记结构包括具有当层器件层的部分结构特征;所述标记结构包括接触孔、侧墙、隔离层中的一种或多种。

13、相应的,本发明的技术方案还提供一种套刻标记的方法,包括:提供基底,所述基底包括若干芯片区,各芯片区包括结构区和与所述结构区相邻的至少一个伪结构区,各伪结构区内包括至少一个标记区;在位于基底上形成至少两层重叠的器件层,每层器件层内具有若干标记结构,且每层器件层内的每个标记结构位于至少一个标记区上。

14、可选的,获取所述标记区的方法包括:设定标记结构;根据曝光区中各芯片内器件的布局,获取各芯片中需要设置伪栅的伪结构区;根据所述设定标记尺寸,在所述伪结构区获取若干初始标记区位置;确认所获取的初始标记区位置是否遵从伪栅在芯片中的设计规则,去除不符合所述设计规则的部分初始标记区位置,获取若干预定标记区位置;根据标记区的分布与套刻精度之间的关系进行数据模拟,自所述若干预定标记区位置中获取最优化的标记区位置;根据模拟获得的最优化标记区位置,将标记结构插入到芯片设计模板中,获取标记结构设计数据文件。

15、可选的,至少两层重叠的器件层中包括位于基底表面的第一器件层,所述第一器件层内的标记结构包括若干标记鳍部,所述若干标记鳍部平行于第二方向,且沿第一方向排布。

16、可选的,所述第一器件层内还具有位于所述伪结构区上的若干伪鳍部。

17、可选的,沿所述第一方向上所述标记区包括若干第一区和若干第二区,所述第一区两侧与所述第二区相邻,所述若干标记鳍部位于所述第二区;所述若干标记鳍部的形成方法包括:在所述基底上形成若干第一牺牲层,所述若干第一牺牲层平行于第二方向,且沿第一方向排布;在所述若干第一牺牲层侧壁形成若干第一鳍部;去除不需要的第一鳍部,以所述第二区上的第一鳍部形成标记鳍部。

18、可选的,至少两层重叠的器件层中包括位于基底表面的第二器件层,所述第二器件层内的标记结构包括若干标记隔离条纹,各所述标记隔离条纹平行于第二方向,且沿第一方向排布,所述标记隔离条纹在所述基底表面的投影位于相邻的标记鳍部在所述基底表面的投影的中间。

19、可选的,所述若干标记鳍部的形成工艺包括自对准多图案工艺。

20、可选的,所述第一器件层和所述第二器件层之间还具有衬底层,所述衬底层包括若干辅助栅,所述若干辅助栅横跨所述标记鳍部,且位于所述标记鳍部部分侧壁和顶部表面,且各所述标记隔离条纹在沿着所述第二方向切断所述若干辅助栅。

21、可选的,所述衬底层和所述若干标记隔离条纹的形成方法包括:形成所述第一器件层后,在所述标记区上形成横跨所述若干第一鳍部的若干辅助栅;形成所述若干辅助栅后,在所述辅助栅上形成介质材料层;在所述第一区上的所述介质材料层内形成若干隔离沟槽,所述隔离沟槽在沿所述第二方向上贯穿所述若干辅助栅;在所述隔离沟槽内形成所述标记隔离条纹。

22、可选的,所述辅助栅的形成工艺包括自对准多图案工艺。

23、可选的,所述第一器件层内还具有位于所述伪结构区上的若干伪鳍部。

24、可选的,所述第二器件层的还具有位于所述伪结构区上的若干伪栅。

25、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

26、本发明技术方案提供的一种套刻标记结构中,各芯片区包括结构区和与所述结构区相邻的至少一个伪结构区,各伪结构区内包括至少一个标记区,将标记结构放到标记区,所述标记区与伪栅均放在伪结构区,不占用放置器件的结构区的位置,因此不受芯片模式分布的影响,仅需要遵从伪栅的设计规则,由于各个芯片中均具有形成伪栅的区域,在整个曝光区有大量的分布于各个曝光位置的伪栅区域,所述伪栅区域总的分布面积甚至可以达到整个曝光区50%以上,利于现有的在曝光区广泛分布的伪栅的区域,即在伪结构区形成标记结构,不占用芯片中器件的位置,提高了芯片集成度;另一方面,由于伪栅的尺寸相对现有的套刻标记小的多,将标记结构设计成类似伪栅的结构,可以在一个曝光区内形成相对自由分布的若干标记结构,标记结构的数量足够满足高的套刻精度需求,增加了套刻标记设置的自由度,且利于提高套刻测量精度。

27、进一步,在所述伪结构区上,所述若干伪鳍部与所述若干标记鳍部相邻,由于标记鳍部包括若干第一鳍部,所述第一鳍部和所述伪鳍部具有相同的特征尺寸,减少了套刻标记与临近的器件区的之间因特征尺寸差异带来的应力,而导致的标记鳍部弯曲问题。

- 还没有人留言评论。精彩留言会获得点赞!