半导体封装装置的制作方法

本公开涉及半导体封装,具体涉及半导体封装装置。

背景技术:

1、在被动组件(例如电容)配置于上、下基板夹层的设计中,被动组件的电极可做为上、下基板的互联结构,然而若连接电容电极的锡量控制不好,容易发生一侧端的焊锡合并,且与上、下基板的焊盘浸润拉扯导致空焊现象。

技术实现思路

1、本公开提供了一种半导体封装装置。

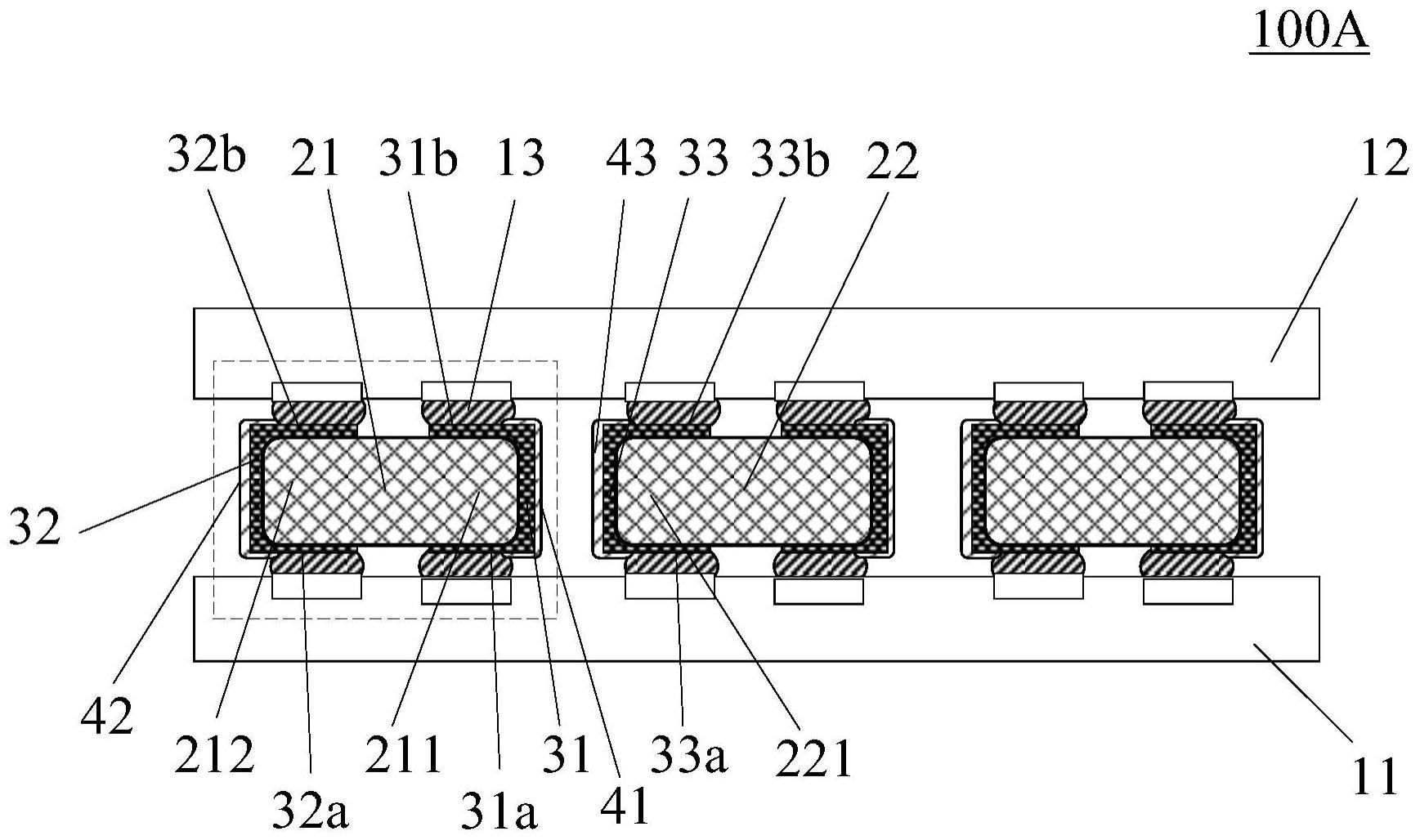

2、第一方面,本公开提供了一种半导体封装装置,包括:

3、第一基板;

4、第二基板;

5、第一元件,设置于所述第一基板与所述第二基板之间,所述第一元件具有第一端部,所述第一端部设置有第一电极,所述第一电极表面设置有第一阻隔层,所述第一阻隔层将所述第一电极表面区隔为近所述第一基板的第一电极面和近所述第二基板的第二电极面,所述第一电极面和所述第二电极面通过焊料对应电连接所述第一基板与所述第二基板。

6、在一些可选的实施方式中,所述第一元件具有相对所述第一端部的第二端部,所述第二端部设置有第二电极,所述第二电极表面设置有第二阻隔层,所述第二阻隔层将所述第二电极表面区隔为近所述第一基板的第三电极面和近所述第二基板的第四电极面。

7、在一些可选的实施方式中,所述第三电极面和所述第四电极面通过焊料对应电连接所述第一基板与所述第二基板。

8、在一些可选的实施方式中,所述第一阻隔层和所述第二阻隔层为一体。

9、在一些可选的实施方式中,所述第一阻隔层的材料和所述第二阻隔层的材料为阻焊材料

10、在一些可选的实施方式中,所述装置还包括:

11、第二元件,相邻所述第一元件设置,具有第三端部,所述第三端部设置有第三电极,所述第三电极表面设置有第三阻隔层,所述第三阻隔层将所述第三电极表面区隔为近所述第一基板的第五电极面和近所述第二基板的第六电极面。

12、在一些可选的实施方式中,所述第五电极面和所述第六电极面通过焊料对应电连接所述第一基板与所述第二基板。

13、在一些可选的实施方式中,所述第二元件的第三端部与所述第一元件的第一端部相对。

14、在一些可选的实施方式中,所述装置还包括:

15、第三元件,叠设于所述第一元件上,具有第四端部,所述第四端部设置有第四电极,所述第四电极表面设置有第四阻隔层,所述第四阻隔层将所述第四电极表面区隔为近所述第一基板的第七电极面和近所述第二基板的第八电极面,所述第七电极面和所述第八电极面通过焊料对应电连接所述第二电极面和所述第二基板。

16、在一些可选的实施方式中,所述第一阻隔层至少包覆所述第一电极对应所述第一端部端面的表面,所述第四阻隔层至少包覆所述第四电极对应所述第四端部端面的表面。

17、在一些可选的实施方式中,所述第一端部与所述第四端部相对应。

18、在本公开提供的半导体封装装置,通过设计半导体封装装置包括:第一基板;第二基板;第一元件,设置于第一基板与第二基板之间,第一元件具有第一端部,第一端部设置有第一电极,第一电极表面设置有第一阻隔层,第一阻隔层将第一电极表面区隔为近第一基板的第一电极面和近第二基板的第二电极面,第一电极面和第二电极面通过焊料对应电连接第一基板与第二基板;第一阻隔层能够阻隔第一电极面和第二电极面上的焊料合并,进而避免焊锡合并导致的空焊问题。

技术特征:

1.一种半导体封装装置,包括:

2.根据权利要求1所述的装置,其中,所述第一元件具有相对所述第一端部的第二端部,所述第二端部设置有第二电极,所述第二电极表面设置有第二阻隔层,所述第二阻隔层将所述第二电极表面区隔为近所述第一基板的第三电极面和近所述第二基板的第四电极面。

3.根据权利要求2所述的装置,其中,所述第三电极面和所述第四电极面通过焊料对应电连接所述第一基板与所述第二基板。

4.根据权利要求2所述的装置,其中,所述第一阻隔层和所述第二阻隔层为一体。

5.根据权利要求2所述的装置,其中,所述第一阻隔层的材料和所述第二阻隔层的材料为阻焊材料。

6.根据权利要求1所述的装置,其中,所述装置还包括:

7.根据权利要求6所述的装置,其中,所述第五电极面和所述第六电极面通过焊料对应电连接所述第一基板与所述第二基板。

8.根据权利要求6所述的装置,其中,所述第二元件的第三端部与所述第一元件的第一端部相对。

9.根据权利要求1所述的装置,其中,所述装置还包括:

10.根据权利要求9所述的装置,其中,所述第一阻隔层至少包覆所述第一电极对应所述第一端部端面的表面,所述第四阻隔层至少包覆所述第四电极对应所述第四端部端面的表面。

技术总结

本公开提供了一种半导体封装装置,包括:第一基板;第二基板;第一元件,设置于所述第一基板与所述第二基板之间,所述第一元件具有第一端部,所述第一端部设置有第一电极,所述第一电极表面设置有第一阻隔层,所述第一阻隔层将所述第一电极表面区隔为近所述第一基板的第一电极面和近所述第二基板的第二电极面,所述第一电极面和所述第二电极面通过焊料对应电连接所述第一基板与所述第二基板。

技术研发人员:叶昶麟,高仁杰

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!