超薄型LED元件、包含此的喷墨用墨水及光源

超薄型led元件、包含此的喷墨用墨水及光源

技术领域

1.本发明涉及led元件,更详细地说,涉及超薄型led元件、包含此的喷墨用墨水及光源。

背景技术:

2.微型led和纳米型led可以实现优秀的色彩和高效率,并且是环保材料,因此正在用作显示器的核心材料。根据该市场情况,近来正在进行用于开发新的纳米棒led结构或者通过新的制造工艺具有外壳涂层的纳米线led的研究。再则,也在进行为了实现覆盖纳米棒外部面的保护膜的高效率和高稳定性而对保护膜材料的研究,或有利于后续工艺的配体材料的研究和开发。

3.配合这种材料领域的研究,最近大型的红、绿、蓝微型led显示tv已经商业化,未来将通过蓝色子像素和红色及绿色子像素实现全色彩的tv的商业化,所述蓝色子像素利用蓝色微型led或纳米led实现,所述红色及绿色子像素通过所述蓝色led发光量子点实现的。再则,红、绿、蓝纳米led显示tv也在计划商业化。

4.微型led显示屏具有高性能特性、理论性长寿命、效率非常长且高等的优点,但是若开发成8k分辨率的显示屏,则需要与近1亿个子像素分别一一对应红色微型led、绿色微型led、蓝色微型led,因此对于制造微型led显示器的拾放技术考虑高成本、高工艺不合格率、低生产率时,存在工艺技术的局限性,处于从智能手机到电视都很难制造出真正意义上的高分辨率商用显示器。再则,也处于利用与微型led相同的拾放技术将纳米-led一个一个配置在子像素是更加困难的实情。

5.为了克服这种困难,授权专利公报第10-1436123号公开了一种显示器,所述显示器通过如下的方法制造:将混合纳米棒型led的溶液投入于子像素,之后在两个排列的电极之间形成电场(electric field),将纳米棒型led元件磁排列在电极上,进而形成子像素。

6.然而,公开的技术是通过电场排列led元件,从而led元件必须具有单向延长形成的纵横大的棒形状,据此led元件容易在溶剂内快速沉淀,因此难以墨水化。另外,元件在电极上平躺组装,即与元件内半导体层的层叠方向平行组装,从而存在光提取面积小、效率差的问题。

7.具体地说,纳米棒型led元件的已知制造方法有混合纳米图案工艺和干蚀刻/湿蚀刻以自上而下(top-down)的方法制造led晶片,或者在基板上以至下而上(bottom-up)直接生长的方法。这种纳米棒状led为led长轴与层叠方向,即在p-gan/ingan多量子阱(mqw)/n-gan层叠结构中与各层的层叠方向一致,因此发光面积小,由于发光面积小,表面缺陷对降低效率造成的影响大,并且由于难以优化电子-空穴的复合速度,因此存在发光效率相比于原来的晶片所具备的效率出现大幅度降低的问题。

8.从而,处于迫切开发一种新型led材料,以适合墨水化、具有大发光面积、最小化或防止表面缺陷导致的效率降低,优化电子-空穴复合速度的实情。

技术实现要素:

9.(要解决的问题)

10.本发明是为了解决上述的问题而提出的,目的在于提供一种超薄型led元件、包含此的喷墨用墨水及光源,适合墨水化、发光面积大、最小化或防止表面缺陷导致的效率降低,优化电子-空穴复合速度。

11.(解决问题的手段)

12.为了解决上述课题,本发明提供一种超薄型led元件,所述超薄型led元件至少包括:第一导电性半导体层、光活性层及第二导电性半导体层,作为层的层叠方向的厚度和垂直于所述层叠方向的横截面中的长轴的长度之间的比例为1:0.5~1.5。

13.根据本发明的一实施例,所述第一导电性半导体层及所述第二导电性半导体层中任意一个可以是n型iii族氮化物半导体层,而另一个可以是p型iii族氮化物半导体层。

14.另外,超薄型led元件最大面积可以是16μm2以下;

15.另外,所述超薄型led元件的厚度可以是2.7μm以下,更加优选为厚度可以是2.0μm以下,进一步更加优选为可以是0.2~1.0μm。

16.更加优选为可以是4μm2以下,进一步更加优选为可以是0.1μm2~2.5μm2

17.另外,所述第一导电性半导体层为n型iii族氮化物半导体层,在第一导电性半导体层下部还可包括电子延迟层,以使在所述光活性层复合的电子和空穴的数量达到平衡。

18.另外,所述电子延迟层可包含从由cds、gas、zns、cdse、case、znse、cdte、gate、sic、zno、znmgo、sno2、tio2、in2o3、ga2o3、si、聚对苯撑乙烯撑(poly(paraphenylene vinylene))及其衍生物、聚苯胺(polyaniline)、聚(3-烷基噻吩)(poly(3-alkylthiophene))及聚对苯撑(poly(paraphenylene))组成的群组中选择的一种以上。

19.另外,所述第一导电性半导体层为掺杂的n型iii族氮化物半导体层,所述电子延迟层可以是掺杂浓度低于所述第一导电性半导体层的掺杂浓度的iii族氮化物半导体。

20.另外,所述超薄型led元件还可包括保护膜,所述保护膜包围超薄型led元件的暴露的侧面。

21.另外,所述第一导电性半导体层为n型iii族氮化物半导体层,所述第二导电性半导体层为p型iii族氮化物半导体层;所述超薄型led元件还可包括空穴推膜及电子推膜中的至少一种膜,所述空穴推膜包围第二导电性半导体层的暴露的侧面或者第二导电性半导体层的暴露的侧面和光活性层至少一部分的暴露的侧面以向中心侧移动暴露的侧面表面侧的空穴;所述电子推膜包围所述第一导电性半导体层的暴露的侧面以向中心侧移动暴露的侧面表面侧的电子。

22.另外,所述超薄型led元件可全部包括所述空穴推膜和电子推膜,所述电子推膜可设置为最外层膜,所述最外层膜包围第一导电性半导体层、光活性层及第二导电性半导体层的侧面。

23.另外,所述空穴推膜可包含从由aln

x

、zro2、moo、sc2o3、la2o3、mgo、y2o3、al2o3、ga2o3、tio2、zns、ta2o5及n-mos2组成的群组中选择的一种以上。

24.另外,所述电子推膜可包含从由al2o3、hfo2、sin

x

、sio2、zro2、sc2o3、aln

x

及ga2o3组成的群组中选择的一种以上。

25.另外,超薄型led元件还可包括:第二电极层,配置在第一导电性半导体层上;第一

电极层,配置在第二导电性半导体层上。

26.另外,在超薄型led元件的最上部层或者最下部层上还包括选择性结合层,所述选择性结合层用于在驱动电极的目标位置以厚度方向竖立超薄型led元件来进行组装;所述选择性结合层可以是磁性层或者化学键诱导层。

27.另外,本发明提供一种喷墨用墨水组合物,所述喷墨用墨水组合物包含有多个本发明的超薄型led元件。

28.另外,本发明提供一种安装有本发明的超薄型led元件的光源。

29.以下,对在本发明中使用的用语进行定义。

30.在说明本发明的实现例中,在记载于形成在各层、区域、图案或者基板、各层、区域、图案的“上(on)”、“上部”、“下(under)”、“下部”中,“上(on)”、“上部”、“下(under)”、“下部”是指“直接”和“间接”的两种含义全部包括。

31.(发明的效果)

32.相比于以往的棒状led元件,本发明的超薄型led元件增加发光面积,因此有利于实现高亮度和光效率。另外,增加发光面积的同时还大幅度缩小暴露于表面的光活性层面积,进而防止或者最小化由表面缺陷引起的效率下降。进一步地,可将电子及空穴速度不平衡导致的电子-空穴复合效率的降低及由此导致的发光效率的降低最小化。再则,在溶剂中无需单独的分散剂等的添加剂也具有优秀的分散保持性能,因此适合实现为喷墨用墨水,从而可广泛用作显示器等的各种光源的材料。

33.本发明是在以下国家研发事业的支持下进行研究的,国家研发事业的详细信息如下。

34.【课题固有编号】1711105790

35.【课题编号】2016r1a5a1012966

36.【部门名称】科学技术信息通信部

37.【课题管理(专业)机构名称】韩国国家研究基金会

38.【研究事业名称】工程学领域(s/erc)

39.【研究课题名称】使用混合设备的昼夜节律ict研究中心

40.【课题执行机构名称】国民大学产学合作团

41.【研究期间】2021-01-01~2021-12-31

42.【课题固有编号】1415174040

43.【课题编号】20016290

44.【部门名称】产业通商资源部

45.【课题管理(专业)机构名称】韩国产业技术评价管理院

46.【研究事业名称】电子部件产业技术开发-超大型微led模块化显示器

47.【研究课题名称】用于模块化显示器的亚微米蓝光光源技术开发

48.【课题执行机构名称】国民大学产学合作财团

49.【研究期间】2021-04-01~2024-12-31

附图说明

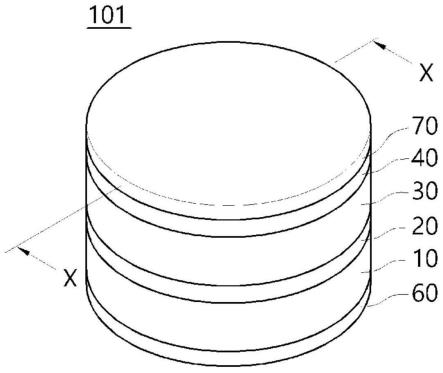

50.图1是本发明的一实施例的超薄型led元件的立体图。

51.图2是沿着图1的x-x’边界线的剖面图。

52.图3a至图3c是在本发明的一实施例的超薄型led元件可具备的选择性结合层的各种实施例的图。

53.图4是用于说明led元件中的电子和空穴的平衡的模式图。

54.图5是本发明的一实施例的超薄型led元件的立体图。

55.图6是本发明的一实施例的超薄型led元件的剖面图。

56.图7是本发明的一实施例的超薄型led元件的制造方法1的模式图。

57.图8是在本发明的一实施例包括的树脂层的制造工艺模式图。

58.图9是本发明的一实施例的超薄型led元件的制造方法1的模式图。

59.图10是本发明的一实施例的超薄型led元件的制造方法2的模式图。

60.图11是本发明的一实施例的超薄型led元件的制造方法的模式图。

61.图12至13是本发明的一实施例的超薄型led元件制造方法中的特定步骤中的sem照片。

62.图14是通过本发明的一实施例的超薄型led元件制造方法获得的超薄型led元件的sem照片。

63.图15是通过本发明的一实施例的超薄型led元件制造方法制造超薄型led元件之后剩下的led晶片的sem照片。

64.图16及图17是将实施例1和比较例1的led元件集合体分散于丙酮之后分时间段测量的各个波长的吸光度曲线图。

65.图18是利用将实施例1和比较例1的led元件集合体分散于丙酮之后分时间段检测的吸光度计算的各时段的分散保持性(dr)曲线图。

具体实施方式

66.以下,对于本发明的实施例进行说明,以使在本发明所属技术领域中具有常规知识的人可容易实施。本发明可实现为各种不同的形态,不限于在此说明的实施例。

67.参照图1及图2进行说明,本发明的超薄型led元件101包括:第一导电性半导体层10、光活性层20及第二导电性半导体层30。除此之外,还可包括:形成在第一导电性半导体层10下的第二电极层60、形成在第二导电性半导体层30上的第一电极层40及形成在所述第一电极层40上的选择性结合层。

68.上述的层以任意一个方向层叠,作为层叠方向的厚度和垂直于所述层叠方向的横截面中的长轴的长度之间的比例满足1:0.5~1.5,优选为可满足1:0.8~1.2,更加优选为可满足1:0.9~1.1,据此在将超薄型led元件实现为喷墨用墨水时,分散介质内发挥优秀的分散性,可有利于保持长时间的分散状态而不沉淀。另外,因为适合于这种墨水化的几何结构无需用于保持分散状态的单独的添加剂,因此具有可提前预防因为单独的添加剂导致驱动电极或者电路基板污染的优点。进一步地,在将含有超薄型led元件的墨水印刷于驱动电极上时,以往纵横比大的纳米棒型led元件大部分几乎是平躺在驱动电极上,而超薄型led元件具有可降低平躺在驱动电极上的概率的优点。另外,降低以厚度方向组装在驱动电极上时降低多个元件组装方向相互不同的概率,换句话说,降低p型导电性半导体层和n型导电性半导体层的方向以相互不同的方向组装的概率,因此可降低因为反向排列引起的漏

电,据此具有可提高寿命的优点。在此,所述长轴的长度是指在横截面形状为圆形的情况下的直径、椭圆的情况下的长轴的长度、多边形的情况下最长边的长度。

69.另外,在所述横截面中短轴的长度和长轴的长度之间的比例也是1:0.5~1.5,优选为可满足1:0.8~1.2,更加优选为可满足1:0.9~1.1,据此可更加有利于达到上述的本发明的目的。如果,即使厚度和长轴的长度之间的比例满足1:0.5~1.5,若横截面中短轴长度和长轴长度之间的比例超出1:0.5~1.5,则led元件也难以在分散介质中保持长时间的分散状态,因此可不适合于墨水化。另外,为使这种具有不适合墨水化的几何结构的led元件在分散介质中保持长时间分散,还需含有添加剂,因此存在因为使用添加剂引起驱动电极或者电路基板被污染的问题的风险。

70.另一方面,对于在图1示出的超薄型led元件101示出了与层的层叠方向垂直的横截面的大小相同,但是不限于此,而是横截面的大小根据厚度可有所不同。

71.另外,须注意的是超薄型led元件101的形状可以是在图1示出的圆柱形,但是不限于此,不仅是六面体、八面体、十面体等多面体,而是也可具有星星形状的面的不规则形状。

72.根据本发明的一实施例,在墨水化时沉降速度缓慢可持续保持分散状态的分散保持性能优秀,因此超薄型led元件101最大面可以是16μm2以下,优选为可以是9μm2以下,更加优选为可以是4μm2以下,进一步更加优选为可以是0.1μm2~2.5μm2。在此,最大面积是指垂直投影led元件的面积中的最大值。如果,最大面积超过16μm2时,沉降速度加快,存在降低分散保持性能的风险,因此不适合制造成墨水,或者存在为了墨水化还要含有额外的添加剂或者使用特定的分散介质的限制。

73.根据本发明的一实施例,超薄型led元件101的厚度可以是2.7μm以下,更加优选为可以是2.0μm以下,进一步更加优选为可以是0.2~1.0μm。

74.更加优选为可以是1μm以下,据此更加适合在墨水化时保持长时间的分散状态。

75.但是,对于led元件的情况,在实现薄厚度时,实现电子和空穴之间结合的位置脱离光活性层20,可降低发光效率。尤其是,在蚀刻大面积的led晶片实现超薄型led元件的情况下,对于第一导电性半导体层、光活性层、第二导电性半导体层的厚度,在led晶片状态下已经决定,而且与晶片的厚度不同,只蚀刻一部分来实现超薄型led元件,因此必然会出现这种问题。这种实现电子和空穴之间的结合的位置变化起因于移动于导电性半导体层的电子和空穴的速度差异,例如在n型gan的导电性半导体层中电子的迁移率为200cm2/vs,与此相反p型gan的导电性半导体层中空穴的迁移率仅为5cm2/vs,因为如此的电子-空穴速度不平衡,电子和空穴沿着p型gan的导电性半导体层的厚度和n型gan的导电性半导体层的厚度结合的位置发生变化可超出光活性层。

76.对此参照图4进行说明,在n型gan的导电性半导体层210、光活性层220及p型gan的导电性半导体层230层叠直径约600nm的led元件200中,为了考虑到n型gan的导电性半导体层210的电子迁移率及p型gan的导电性半导体层230的空穴迁移率使在光活性层220内的点a2复合的电子和空穴的数量达到平衡,在设计时n型gan的导电性半导体层210的厚度h必然要厚,因此除非将p型gan的导电性半导体层230的厚度实现得非常薄,否则led元件实现具有以厚度方向延长的长度的棒状led元件的可能性非常高。换句话说,为使复合的电子和空穴的数量达到平衡的位置位于光活性层220而设计各层的厚度的led元件的情况下,即使可以将与厚度方向垂直的横截面的长轴长度实现得较小,也难以将led元件的厚度减小至预

定以下,最终不得不实现以led元件的厚度方向延长形成的棒状led元件,因此即使在光活性层复合的空穴和电子的数量达到平衡,也不适合实现为墨水。另外,为了适合实现为墨水而实现薄厚度的n型gan导电性半导体层210时,复合的电子和空穴的数量达成平衡的位置发生变动,从光活性层220变为p型gan导电性半导体层230内的一点a3,从而可降低发光效率。

77.据此,本发明的一实施例的超薄型led元件还可包括电子延迟层,所述电子延迟层与n型导电性半导体层侧相邻,以具有适合实现为墨水的几何结构的同时在所述光活性层复合的空穴和电子的数量达到平衡,进而防止发光效率降低。参照图5进行说明,在第一导电性半导体层为n型导电性半导体时,超薄型led元件102可在第一导电性半导体层10下部具备电子延迟层50,据此即使实现厚度薄的第一导电性半导体层10也可防止发光效率降低。另外,第一导电性半导体层10的变薄的厚度降低电子以第一导电性半导体层10的厚度方向移动中因为表面缺陷而被捕获的概率,进而具有可将发光损失最小化的优点。

78.举一示例,所述电子延迟层50可含有从由cds、gas、zns、cdse、case、znse、cdte、gate、sic、zno、znmgo、sno2、tio2、in2o3、ga2o3、si、聚对苯撑乙烯撑(poly(paraphenylene vinylene))及其衍生物、聚苯胺(polyaniline)、聚(3-烷基噻吩)(poly(3-alkylthiophene))及聚对苯撑(poly(paraphenylene))组成的群组中选择的一种以上。另外,举另一示例,在所述第一导电性半导体层10为掺杂的n型iii族氮化物半导体层的情况下,所述电子延迟层50可以是掺杂浓度低于所述第一导电性半导体层10的掺杂浓度的iii族氮化物半导体。

79.所述电子延迟层50的厚度可以是1nm~100nm,但是不限于此,而是考虑n型导电性半导体层的材料、电子延迟层的材料等可做适当的改变该厚度。

80.以下,具体说明本发明的一实施例的超薄型led元件101、102的各层。

81.在第一导电性半导体层10及第二导电性半导体层30中的任意一个为n型半导体层,而另一个可以是p型半导体层,所述n型半导体层及p型半导体层为发光二极管采用的公知的半导体层的情况下,可无限制使用。举一示例,所述n型半导体层和p型半导体层可包含称为iii族氮化物材料的iii-v族半导体,尤其是镓、铝、铟和氮的二元、三元和四元合金。

82.举一示例,第一导电性半导体层10可以是n型半导体层,在该情况下,n型半导体层可以是具有in

x

alyga

1-x-y

n(0≤x≤1、0≤y≤1、0≤x+y≤1)的组成式的半导体材料,例如可在inalgan、gan、algan、ingan、aln、inn等中选择一种以上,并且可掺杂第一导电掺杂剂(例如,si、ge、sn)。根据本发明的优选的实现例,所述第一导电性半导体层10的厚度可以是100nm~1800nm,但是不限于此。

83.另外,第二导电性半导体层30可以是p型半导体层,在该情况下,所述p型半导体层可以是具有in

x

alyga

1-x-y

n(0≤x≤1、0≤y≤1、0≤x+y≤1)的组成式的半导体材料,例如可在inalgan、gan、algan、ingan、aln、inn等选择一种以上,并且可掺杂第二导电掺杂剂(例如,mg)。根据本发明的优选的一实现例,所述第二导电性半导体层30的厚度可以是50nm~150nm,但是不限于此。

84.另外,位于所述第一导电性半导体层10和第二导电性半导体层30之间的光活性层20可形成为单一或者多重量子阱结构。所述光活性层20为包含于使用于照明、显示器等的通常的led元件的光活性层的情况下,可无限制使用。在所述光活性层20的上及/或者下也

可形成掺杂导电掺杂剂的包覆层(未示出),掺杂所述导电掺杂剂的包覆层可用algan层或者inalgan层实现。除此之外,algan、alingan等物质也可用于光活性层20。对于这种光活性层20,在元件施加电场时,从分别位于光活性层上、下的导电性半导体层向光活性层移动的电子和空穴在光活性层发生电子-空穴对的结合,因此可发光。本发明的优选的一实施例,所述光活性层20的厚度可以是50nm~200nm,但是不限于此。

85.另一方面,在上述的第一导电性半导体层10下部可具有第二电极层60。或者,在第一导电性半导体层10和第二电极层60之间还可具有电子延迟层50。另外,在上述的第二导电性半导体层30上部可具有第一电极层40。

86.所述第一电极层40及所述第二电极层60为在使用于照明、显示器等的通常的led元件所包含的电极层的情况下,可无限制使用。所述第一电极层40及所述第二电极层60可以是各自独立且用cr、ti、al、au、ni、ito及这些的氧化物或者合金中的一种形成的单独层,或者是混合其中两种以上形成的单独层、用其中两种以上的材料分别形成层的复合层。举一示例,如图5所示,超薄型led元件102在第二导电性半导体层30上可具有层叠ito层的第一电极层40及ti/au复合层41的第一电极层42。另外,所述第一电极复合层40及所述第二电极层60可以是各自独立且具有10nm~500nm的厚度,但是不限于此。

87.另外,在第一电极层40、42上还可包括选择性结合层70。在所述选择性结合层70上执行用于在驱动电极的目标位置组装超薄型led元件的功能。所述选择性结合层70的层材料根据具体的结合方式可有所不同。例如,选择性结合层70可以是化学键诱导层;具体地说,如图3a所示,选择性结合层71可以是离子键诱导层,在驱动电极上通过离子键与带有相反电荷的离子键诱导层组装。另外,如图3b所示,选择性结合层72可以是共价键诱导层,可通过共价键合与具有能够与已具备的官能团共价键合的其他官能团的驱动电极上的共价键诱导层组装。另外,如图3c所示,所述选择性结合层70可以是磁性层73,利用磁特性可在驱动电极上组装磁性层73。

88.另一方面,在图1及图2中示出选择性结合层70的位置在第二电极层60上,但是不限于此,而是也可配置成位于第一电极层40上。换句话说,选择性结合层70可以是成为超薄型led元件的最上部层或者最下部层地配置在超薄型led元件。

89.另外,超薄型led元件101还可包括保护膜80,所述保护膜80在与层叠方向平行的面为侧面时包围元件侧面。所述保护膜80执行保护第一导电性半导体层10、光活性层20及第二导电性半导体层30的表面的功能。另外,与后述的一制造方法相同,可执行在以厚度方向蚀刻led晶片之后分离多个led柱的工艺中保护第一导电性半导体层10的作用。举一示例,所述保护膜80可包含氮化硅(si3n4)、二氧化硅(sio2)、氧化铝(al2o3)、氧化铪(hfo2)、氧化锆(zro2)、氧化钇(y2o3)、二氧化钛(tio2)、氮化铝(aln)及氮化镓(gan)中的任意一种以上。所述保护膜80的厚度可以是5nm~100nm,更加优选为可以是30nm~100nm,据此有利于在后述的分离led柱的工艺中保护第一导电性半导体层10。

90.另一方面,如图6所示,为了在除了作为保护膜的保护功能以外还具有更加优秀的发光效率,本发明的一实施例的超薄型led元件103可具有由空穴推膜81和电子推膜82构成的保护膜80’,所述空穴推膜81包围第二导电性半导体层30的暴露的侧面或者第二导电性半导体层30暴露的侧面和光活性层20至少一部分的暴露的侧面,以向中心侧移动暴露的侧面表面侧的空穴,所述电子推膜82包围第一导电性半导体层10的暴露的侧面以向中心侧移

动暴露的侧面表面侧的电子,以在除了作为保护膜的保护功能以外还具有更加优秀的发光效率。

91.从第一导电性半导体层10向光活性层20移动的电荷的一部分和从第二导电性半导体层30向光活性层20移动的空穴的一部分可沿着侧面的表面移动,在该情况下因为存在于表面的缺陷发生电子或者空穴的淬火,因此存在降低发光效率的风险。在该情况下,存在即使具备保护膜也无法避免因为在具备保护膜之前在元件表面产生的缺陷而引起的淬火的问题。然而,在由空穴推膜81和电子推膜82构成保护膜80’时,向元件中心侧集中电子和空穴以引导向光活性层方向移动,从而具有即使在形成保护膜之前在元件表面存在缺陷也可防止因为表面缺陷导致发光效率损失的优点。

92.举一示例,所述空穴推膜81可包含由aln

x

、zro2、moo、sc2o3、la2o3、mgo、y2o3、al2o3、ga2o3、tio2、zns、ta2o5及n-mos2组成的群组中选择的一种以上;所述电子推膜82可包含从由al2o3、hfo2、sin

x

、sio2、zro2、sc2o3、aln

x

及ga2o3组成的群组中选择的一种以上。

93.另外,如图6所示,在超薄型led元件将空穴推膜81和电子推膜82全部具备的情况下,电子推膜82可配置成包围第一导电性半导体层10、光活性层20及第二导电性半导体层30的侧面的最外层膜。

94.另外,所述空穴推膜81和电子推膜82可以是各自独立且具有1nm~50nm的厚度。

95.另一方面,上述的第一导电性半导体层10、光活性层20、第二导电性半导体层30可作为超薄膜led器件的最少构成元素包含在内,须注意的是在各层的上/下还可包括其他荧光体层、量子点层、有源层、半导体层、空穴阻挡层及/或者电极层。

96.包括上述的本发明的一实施例的超薄型led元件101的超薄型led元件集合体100可通过在图7示出的制造方法1或者在图10示出的制造方法2制造。对于制造方法1,在n型iii族氮化物半导体层为掺杂的n型iii族氮化物半导体层时选择更有用,如果是未掺杂n型iii族氮化物半导体层的情况则制造方法2是有用的。

97.制造方法1和制造方法2从制造led晶片100a至制造包含多个led结构的晶片(图1的100h、图10的100h)的工艺是相同的,在从晶片分离led结构的方法存在差异。对于从制造led晶片100a至制造包括多个led结构的晶片(图1的100h、图10的100h)的工艺将通过制造方法1进行说明。

98.首先,参照图7说明制造方法1。

99.制造方法1可包括:步骤(1),准备led晶片100a(图7的(a));步骤(2),将led晶片100a上部图案化,以在单个led结构中与层叠层的方向垂直的平面具有目标形状和大小(图7的(b)、(c)),之后以垂直方向蚀刻至第一导电性半导体层10至少一部分厚度,以形成多个led结构(图7的(d)~(h));步骤(3),形成保护膜,以包围多个led结构各个的暴露面而且使相邻的led结构之间的第一部分上部面暴露在外部(图7的(i)~(j));步骤(4),将led晶片浸入电解液之后与电源的任意一个端子电连接,并且将电源的另一个端子电连接于浸入所述电解液的电极,之后施加电源以形成多个气孔(图7的(k));及步骤(5),对所述led晶片施加超声波以从形成多个气孔的第一部分分离多个led结构(图7的(o))。

100.作为在步骤(1)中准备的led晶片100a,只要是可商业性获得的,就可无限制使用。举一示例,所述led晶片100a可以是最少包括基板1、第一导电性半导体层10、光活性层20、第二导电性半导体层30而成的。此时,所述第一导电性半导体层10可以是n型iii族氮化物

半导体层,第二导电性半导体层30可以是p型iii族氮化物半导体层。另外,为了达到目标厚度,在蚀刻n型iii族氮化物半导体层之后通过步骤(3)至(5)在led晶片上可分离蚀刻之后剩下的led结构,因此对于led晶片内n型iii族氮化物半导体层10的厚度也没有限制,而对于是否存在单独的牺牲层可以在选择晶片时不予以考虑。

101.另外,所述led晶片100a内各层可具有c-plane晶体结构。另外,所述led晶片100a可以经过清洗工艺,清洗工艺可适当采用通常的晶片清洗溶液和清洗工艺,因此对此本发明不做特别限制。举一示例,所述清洗溶液可以是异丙醇、丙酮及盐酸,但是不限于此。

102.然后,在执行步骤(2)之前可执行在p型iii族氮化物半导体层30上形成第一电极层40的步骤。所述第一电极层40可通过在半导体层上形成电极的通常的方法形成,举一示例可通过利用溅射的沉积形成。所述第一电极层40的材料与上述的相同,例如可以是ito,并且可形成约150nm的厚度。所述第一电极层40在沉积工艺之后还可经过急速热处理(rapid thermal annealing)工艺,举一示例能够以600℃处理10分钟,但是考虑电极层的厚度、材料等可适当进行调整,因此对此本发明不做特别限制。

103.之后,作为步骤(2),可将led晶片上部图案化,以使在单个的led结构中与层叠层的方向垂直的平面具有目标形状和大小(图7的(b)~(c))。具体地说,在第一电极层40上部面可形成掩膜图案层,所述掩膜图案层可用在蚀刻led晶片时使用的公知的方法及材料,图案层的图案可适当应用通常的光刻法或者纳米压印法等形成。

104.举一示例,如图7的(f)所示,掩膜图案层可以是在第一电极层40上形成预定图案的第一掩膜层2、第二掩膜层3及树脂图案层4’的层叠体。简单说明形成掩膜图案层的方法,举一示例,可通过如下的内容形成:在第一电极层40上通过沉积形成第一掩膜层2及第二掩膜层3,在第二掩膜层3形成作为树脂图案层4’的由来的树脂层4(图7的(b)、(c)),之后利用诸如rie(reactive ion etching;反应离子蚀刻)等的通常的方法去除树脂层4的残留树脂部分4a(图7的(d)),沿着树脂图案层4’的图案分别依次蚀刻第二掩膜层3和第一掩膜层2(图7的(e)、(f))。此时,举一示例,第一掩膜层2可用二氧化硅形成,第二掩膜层3可以是铝、镍等的金属层,这些的蚀刻分别可通过rie及icp(inductively coupled plasma;电感耦合等离子体)执行。另一方面,在蚀刻第一掩膜层2时也可去除树脂图案层4’(参照100f)。

105.另外,如图8所示,作为树脂图案层4’的由来的树脂层4可以是通过纳米压印法形成,制造与目标的预定图案模型6a相应的模具6b(图8的(a)),之后在模具6b处理树脂来形成树脂层4(图8的(b)),之后将树脂层4转移于第一电极层40上,以使树脂层4位于形成第一掩膜层2和第二掩膜层3的晶片层叠体100b上,之后去除模具6b,从而可实现形成有树脂层4的晶片层叠体100c。

106.另一方面,说明了通过纳米压印法形成图案的方法,但是不限于此,而是也可通过利用公知感光性物质的光刻或者公知的激光干涉光刻、电子束光刻等形成。

107.之后,如图7的(g)所示,沿着在第一电极层40上形成的掩膜图案层2、3的图案以与led晶片100f的面垂直的方向蚀刻至n型iii族氮化物半导体层,即第一导电性半导体层10的一部分厚度,进而可制造形成有led结构的led晶片100g,此时蚀刻可通过诸如icp的通常的干式蚀刻法和koh/tamh湿式蚀刻执行。在这种蚀刻过程可去除构成掩膜图案层的铝,即第二掩膜层3,之后去除构成在led晶片100g内的各个led结构的第一电极层40上存在的掩膜图案层的二氧化硅,即第一掩膜层2,从而可制造出形成有多个led结构的led晶片100h。

108.之后,作为步骤(3),执行形成保护膜80a以在形成多个led结构的led晶片100h中以预定厚度包围多个led结构各个的暴露面,而且使相邻的led结构之间的第一部分a的上部面s1暴露在外部的步骤(图7的(i)、(j))。所述保护膜80a是用于防止因为执行步骤(4)导致led结构受损,与此同时还执行在从led晶片分离的led结构的侧面持续残留时可保护单个分离的led结构的侧面表面免受外部刺激的功能。

109.对于步骤(3)至(5)参照图9进行说明,具体地说,所述步骤(3)可通过如下的步骤执行:在形成有多个led结构的led晶片100h上沉积保护膜材料,以使保护膜80a以预定厚度包围多个led结构各个的暴露面(步骤3-1);及去除在相邻的led结构之间的第一部分a上部面s1沉积的保护膜,以向外部暴露led结构之间的第一部分a的上部面s1(步骤3-2)。

110.所述步骤3-1是将保护膜材料沉积于形成有多个led结构的led晶片100h上的步骤(图9的(a))。此时,保护膜材料可以是不受后述的步骤(4)的电解液的化学性侵蚀的公知的材料。举一示例,对于上述的保护膜80的材料的情况,可无限制使用,具体地说,可包含从由氮化硅(si3n4)、二氧化硅(sio2)、氧化铝(al2o3)、氧化铪(hfo2)、氧化锆(zro2)、氧化钇(y2o3)、氧化镧(la2o3)、氧化钪(sc2o3)及二氧化钛(tio2)、氮化铝(aln)、氮化镓(gan)组成的群组中选择一种以上。另外,通过沉积保护膜材料形成的保护膜80a的厚度可以是5nm~100nm,更加优选为可以是30μm~100nm。如果,保护膜80a的厚度小于5nm,则难以防止通过后述的步骤(2)的电解液侵蚀led结构;在所述厚度大于100nm时,可存在增加制造成本、连接led结构之间的问题。

111.之后,步骤3-2是去除在相邻的led结构之间的第一部分a上部面s1沉积的保护膜以将led结构之间的第一部分a上部面s1暴露到外部的步骤(图9的(b))。因为执行步骤3-1,在相邻的led结构之间的第一部分a上部面s1也沉积保护膜材料,因此电解液无法接触于n型iii族氮化物半导体,即第一导电性半导体层10,进而在第一部分a可无法形成目标气孔。据此,执行去除覆盖于所述第一部分a的上部面s1的保护膜材料来暴露到外部的步骤,此时对于保护膜材料的去除可考虑保护膜材料通过公知的干式或者湿式蚀刻方法执行。

112.另一方面,根据本发明的一实施例,在步骤(3)中形成的保护膜80a是用于防止因为执行步骤(3)导致led结构受损的临时保护膜,在步骤(4)和步骤(5)之间还可包括去除所述临时保护膜之后形成包围led结构的侧面的表面保护膜的步骤。即,如图7所示,在步骤(3)保护膜5’只用作用于防止在步骤(4)中led结构受损的临时保护膜(图7的(i)~(k)),在执行步骤(5)之前去除该保护膜5’,之后可形成用于执行防止led结构表面受损的功能的表面保护膜80,使表面保护膜80覆盖led结构的侧面(图7的(m))。

113.另一方面,如图7所示的一部分实施例存在形成两次保护膜的麻烦,但是可考虑制造的led结构的平面形状、大小、led结构之间的间隔可选择该次数。另外,在执行后述的步骤(4)时,可部分性出现保护膜的侵蚀,在将出现侵蚀的保护膜残留于最终获取的单个led结构用作表面保护膜时,可发生难以适当执行表面保护功能的情况,因此在去除执行步骤(4)的保护膜之后重新形成保护膜根据情况可以是有利的。

114.说明如上所述的在图7示出的制造工艺,将临时保护膜材料5沉积于形成多个led结构的led晶片100h上(图7的(i)),之后蚀刻在沉积保护膜5的led晶片100i的相邻的led结构之间掺杂的n型iii族氮化物半导体层10的第一部分a上部面s1上沉积的临时保护膜材料5,可形成保护多个led结构的侧面和上部的临时保护膜,即保护膜5’。之后,执行后述的步

骤(4)(图7的(k)),之后通过蚀刻去除保护膜5’(图7的(l)),将作为用于保护led结构表面的表面保护膜,即保护膜材料沉积于led晶片100l上,之后去除形成在led结构各个上部的保护膜材料,可形成包围led结构侧面的保护膜80(图7的(m))。此时,不仅是形成在led结构上部的保护膜材料,还可一同去除在led晶片100m的相邻的led结构之间的掺杂的n型iii族氮化物半导体层10的第一部分a上部面s1上沉积的保护膜材料,据此在后述的步骤(5)中起泡溶剂可接触于第一部分a上部面s1,通过超声波产生的气泡渗透形成在第一部分a的气孔p,因此可通过气泡分离led结构。

115.另一方面,临时保护膜材料及表面保护膜材料与上述的保护膜的材料的说明相同,实现的薄膜厚度也可在上述的保护膜的厚度范围内实现。

116.之后,作为制造方法1的步骤(4),执行将led晶片浸入电解液之后与电源的任意一个端子电连接,并且将电源的另一个端子电连接于浸入所述电解液的电极,之后施加电源以在所述第一部分形成多个气孔的步骤。

117.具体地说,参照图9进行说明,将形成有保护膜80a的led晶片100h2电连接于电源的任意一个端子,例如阳极,而将电源的剩余端子,例如阴极电连接于浸入电解液的电极之后施加电源,进而可制造在掺杂的n型iii族氮化物半导体,即第一导电性半导体层10的第一部分a形成有多个气孔p的led晶片100h3。此时,气孔p从与电解液直接接触的掺杂的n型iii族氮化物半导体,即第一导电性半导体层10的第一部分a的上部面s1开始可向厚度方向及与多个led结构各个下部相对应的第一部分a侧的侧面方向形成。

118.在所述步骤(4)中使用的电解液可包含从由草酸、磷酸、亚硫酸、硫酸、碳酸、乙酸、亚氯酸、氯酸、溴酸、亚硝酸和硝酸组成的群组中选择的一种以上的含氧酸;更加优选为可使用草酸,据此具有可将第一导电性半导体层的受损最小化的优点。另外,所述电极可使用铂(pt)、碳(c)、镍(ni)及金(au)等,举一示例可以是铂电极。另外,步骤(4)可以是将3v以上的电压作为电源施加1分钟~24小时,据此气孔p可顺利形成至与多个led结构各个下部相对应的第一部分a侧,据此通过步骤(5)可更加容易从晶片分离led结构。更加优选为,电压可以是10v以上,更加优选为可施加30v以下。如果,在施加小于3v的电压时,即使增加施加电源的时间,在与led结构各个的下部相对应的第一部分a侧也无法顺利形成气孔,因此难以通过步骤(5)进行分离,或者即使分离多个led结构各个的分离的一端面的形状也各不相同,因此多个led结构可能难以发挥均匀的特性。优选为,电压可以是10v以上,更加优选为可施加30v以下。如果,施加小于3v的电压时,即使增加电源施加时间,也无法在与led结构各个下部相对应的第一部分a侧顺利形成气孔,因此难以通过步骤(5)分离,或者即使分离多个led结构各个分离的一端面形状可各不相同,因此多个led结构可能难以发挥均匀的特性。另外,在施加超过30v的电压的情况下,气孔可形成至接连于掺杂的n型iii族氮化物半导体层的第一部分a的led结构的下端部,即第二部分b,因此可引起发光特性降低。另外,在后述的步骤(5)中优选为掺杂的n型iii族氮化物半导体层的第一部分a和第二部分b之间的边界点进行在led结构的分离,但是因为在第二部分b侧形成的气孔而超出所述边界点可在第二部分b侧某一点产生分离,因此存在可获取具有厚度小于最初设计的n型半导体层厚度的n型半导体层的led结构的风险。另外,电源施加时间也与电压强度带来的效果类似,施加时间延长的情况下,存在气孔形成至目标部分以外的第二部分b的风险,相反地施加时间短的情况下,气孔形成不顺利,因此可能难以分离led结构。

119.在步骤(4)之后后述的步骤(5)之前还可执行制造在保护膜80a中去除在led结构各个的上部面形成的保护膜的led晶片100h4,以在从晶片分离led结构之后可电连接到第一电极层40侧的步骤。另外,只去除在led结构的上部面形成的保护膜,因此残留在led结构侧面形成的保护膜80,可执行从外部保护led结构的侧面的功能。

120.另外,在步骤(4)之后后述的步骤(5)之前还可执行在led结构第一电极层40上形成其他层的步骤,举一示例,所述其他层可以是在ito层,即第一电极层40还可形成第一电极层材料的ti/au复合层或者选择性结合层70(参照图7的(n))。

121.之后,作为制造方法1的步骤(5),执行对led晶片100h4施加超声波从形成多个气孔p的第一部分a分离多个led结构的步骤。

122.此时,超声波可直接施加于形成气孔的led晶片100h4或者将形成有气孔的led晶片100h4浸入溶剂可间接施加超声波。但是,利用因为超声波本身产生的物理性外力塌陷第一部分a的气孔p的方式无法顺利塌陷气孔,在为了顺利塌陷而过度形成气孔时则存在气孔形成至led结构的第二部分b的风险,因此可导致降低led结构的品质的副作用。

123.据此,根据本发明的一实施例,所述步骤(5)可利用超声波化学(sonochemistry)性方法执行,具体地说将led晶片100h4浸入起泡溶液76(或者,溶液),并且对所述起泡溶液76(或者,溶液)施加超声波,通过超声波化学性机制生成及成长的气泡在气孔爆裂时产生的能量塌陷气孔,进而可分离多个led结构。对此进行具体说明,超声波以声波的传播方向交替产生在相对高压力部分和相对低压力部分,产生的气泡通过高压力部分和低压力部分的同时反复压缩和膨胀,同时生长成具有更高温度和压力的气泡之后塌陷,在塌陷时成为产生例如4000k水平的高温度和1000大气压水准的高压力的局部热点,利用该能量塌陷在led晶片产生的气孔,进而可从晶片分离led结构。最终,超声波不仅执行在起泡溶液(或者,溶液)生成气泡、成长气泡、将产生的气泡移动及渗透至第一部分a的气孔p的功能,还可以通过在之后渗透于气孔p的具有高温和高压的不稳定状态的气泡爆裂时产生的外力塌陷气孔p的气孔塌陷机制容易从led晶片分离多个led结构,据此可获取包含多个超薄型led元件101’的led集合体100’。

124.对于所述起泡溶液76(或者,溶液),若是在施加超声波时产生气泡并且生长具有高压和高温的溶液(或者,溶液)则可无限制使用,优选为起泡溶液(或者,溶液)可使用蒸汽压力在100mmhg(20℃)以下,举另一示例可使用在80mmhg(20℃)以下、60mmhg(20℃)以下、50mmhg(20℃)以下、40mmhg(20℃)以下、30mmhg(20℃)以下、20mmhg(20℃)以下或者10mmhg(20℃)以下的。如果使用蒸汽压力超过100mmhg(20℃)的溶剂时,不可能在短时间内正常分离,因此存在延长制造时间、增加生产成本的风险。对于满足如上所述的物理性质的起泡溶液76,举一示例可以是从由γ-丁内酯、丙二醇单甲醚醋酸酯、甲基吡咯烷酮及2-甲氧基乙醇组成的群组中选择的一种以上。另一方面,也可使用起泡溶液(或者,溶液)的常温,例如20℃下的蒸汽压力为100mmhg的溶液(或者,溶液),然而须注意的是通过与此不同的调整执行步骤(5)的条件,从所述条件调节为起泡溶液(或者,溶液)的蒸汽压力在100mmhg以下(举一示例,低温条件等)也可执行步骤(3)。对于在该情况下可使用的溶剂的种类可更加放宽限制,举一示例也可使用诸如水、丙酮、氯仿、酒精等的溶剂。

125.另外,对于在步骤(5)中施加的超声波的波长,能够以可成为可引起超声波化学反应的区域,具体地说能够以可生长及塌陷起泡以成为在气泡塌陷时产生高压和高温的局部

热点的频率施加,举一示例可以是10khz~2mhz,超声波施加时间可以是1分钟~24小时,据此可容易从led晶片分离led结构。即使施加的超声波的波长在范围内,强度低或者施加时间短的情况下,存在从led晶片未分离的led结构或者未分离的led结构的个数增加的风险。另外,如果施加的超声波的强度大或者施加时间长的情况下,可存在led结构受损的风险。

126.另一方面,为了在第一导电性半导体层10上形成第二电极层60,在执行上述的步骤(5)之前,还可执行将支撑薄膜9附着在led晶片100n上以在第一导电性半导体层10上形成其它层,例如第二电极层60或者电子延迟层(未示出)的步骤(图7的(o)),之后执行步骤(5)能够以附着支撑薄膜9的状态分离多个led结构(图7的(p))。之后,通过以附着支撑薄膜9的状态在多个led结构的上部沉积第二电极层60等的公知方法形成(图7的(q)),之后去除支撑薄膜时可获得多个超薄型led元件101集合体100。

127.之后,参照图10,说明通过制造方法2制造超薄型led元件的方法。

128.如上所述,与从led晶片形成具有多个led结构的led晶片100h与制造方法1相同。之后,对于形成有多个led结构的led晶片100h可执行如下的步骤:步骤(i),形成绝缘膜8,以覆盖多个led结构的暴露的侧面(图10的(b));步骤(

ⅱ

),为使相邻的led结构之间的第一导电性半导体层10上部面s1暴露,去除形成在第一导电性半导体层10上部的绝缘膜的一部分(图10的(c));步骤(

ⅲ

),通过暴露的第一导电性半导体层上部面s1以厚度方向进一步蚀刻所述第一导电性半导体层10,在形成有绝缘膜8’的微型纳米针led柱的第一导电性半导体层下方形成预定厚度的暴露侧面的第一导电性半导体层部分(图10的(c));步骤(

ⅳ

),从两侧面向中心侧蚀刻暴露侧面的所述第一导电性半导体层部分(图10的(d));步骤(

ⅴ

),去除所述绝缘膜8(图10的(e));步骤(

ⅵ

),在多个led结构侧面形成保护膜80(图10的(f));步骤(

ⅶ

),去除形成在多个led结构上部的保护膜以暴露第一电极层40(图10的(g));步骤(

ⅷ

),在第一电极层40上形成选择性结合层70(图10的(h));及步骤(

ⅸ

),从led晶片分离多个led结构以制造包括多个超薄型led元件101’的超薄型led集合体100’。另一方面,上述的制造方法2可适当利用制造led元件的公知的方法执行,对此的具体说明以本发明的发明人的专利申请号第2020-0050884号为前提,作为本发明的参照插入,本发明省略了制造方法2的各步骤的具体说明。

129.此时,在步骤(

ⅸ

)中,多个led结构的分离可以是利用切割工具的切割或者利用粘贴膜的剥离。

130.另一方面,通过图6所述,作为保护膜可形成由提高发光效率的空穴推膜81和电子推膜82构成的保护膜80’,对此的制造方法将参照图11进行说明。

131.与上述的图7、9及10的区别点在于将如下的过程执行2次(图11的(b)、(d)、(e)):在以垂直方向蚀刻时不蚀刻至作为n型半导体的第一导电性半导体层10一部分,而是第一次蚀刻至第二导电性半导体层30或者第二导电性半导体层30和光活性层20的一部分或者全部(图11的(a)),之后第二次蚀刻至第一导电性半导体层10的一部分厚度(图11的(c)),并沉积薄膜材料,去除多个led结构之间的薄膜材料。

132.具体地说,执行如下的工艺:在以垂直方向蚀刻led晶片时,不蚀刻至作为n型半导体的第一导电性半导体层10的一部分,而是第一次只蚀刻至第二导电性半导体层30或者第二导电性半导体层30和光活性层20的一部分或者全部(图11的(a)),之后沉积空穴推膜材料81a(图11的(b)),之后去除在led结构之间形成的空穴排斥材料。之后,可执行如下的工

艺:重新将第一导电性半导体层10第二次蚀刻至预定厚度(图11的(c)),接着在形成有空穴推膜81b的led结构上沉积电子推膜材料82a(图11的(d)),之后重新去除在led结构之间上部面s1形成的电子排斥材料(图11的(e))。之后,执行在上述的图7及图9中分离led结构的工艺(图7的(k)以下,图9的(d)以下)或者在图10中分离led结构的工艺(图10的(d)以下),进而可从led晶片分离超薄型led元件103。

133.通过上述的方法获取的超薄型led元件101、102、103可实现为喷墨用墨水组合物。所述墨水组合物还可包含公知的喷墨用墨水组合物包含的分散介质、其他添加剂等,并且本发明对此不做特别限定。

134.另外,本发明包括含有上述的超薄型led元件101、102、103的光源。举一示例,所述光源可以是家用/汽车用等各种led照明、显示器、医疗设备、美容设备、各种光学设备及构成这些设备的一零部件。

135.以下,通过以下的实施例更加具体说明本发明,但是以下的实施例不限制本发明的范围,而是应该解释为用于理解本发明。

136.(实施例1)

137.准备了在基板上依次层叠未掺杂的n型iii族氮化物半导体层、掺杂si的n型iii族氮化物半导体层(厚度为4μm)、光活性层(厚度为0.45μm)及p型iii族氮化物半导体层(厚度为0.05μm)的通常的led晶片(epistar)。在已准备的led晶片上依次沉积ito(厚度为0.15μm)作为第一电极层、sio2(厚度为1.2μm)作为第一掩膜层、al(厚度为0.2μm)作为第二掩膜层,之后使用纳米压印设备将转移图案的sog树脂层转移到第二掩膜层上。之后,使用rie硬化sog树脂层,通过rie蚀刻树脂层的残留树脂部分形成了树脂图案层。之后,利用icp沿着图案蚀刻第二掩膜层,利用rie蚀刻了第一掩膜层。之后,利用icp蚀刻第一电极层、p型iii族氮化物半导体层、光活性层,接着将掺杂的n型iii族氮化物半导体层蚀刻至厚度为0.78μm,之后为了实现蚀刻的掺杂的n型iii族氮化物半导体层侧面垂直于层侧面,通过koh湿式蚀刻制造了形成有多个led结构(直径为850nm、高度为850nm)的led晶片。之后,在形成有多个led结构的led晶片上沉积了保护膜材料,即sin

x

(参照图12的sem照片,以led结构侧面为准,沉积厚度为52.5nm、72.5nm),之后通过反应离子刻蚀机去除在多个led结构之间形成的保护膜材料,暴露了掺杂的n型iii族氮化物半导体层的第一部分a的上部面s1。

138.之后,将形成有临时保护膜的led晶片浸入电解液,即0.3m草酸水溶液,之后连接于电源的阳极端子,在浸入电解液的铂电极连接阴极端子,之后将10v电压施加5分钟,如图13的sem照片所示,从掺杂的n型iii族氮化物半导体层第一部分a的表面至深度为600nm的点形成了多个气孔。之后,通过rie去除临时保护膜,之后以led结构侧面为准在led晶片再沉积厚度为50nm的表面保护膜,即al2o3,通过icp去除在多个led结构上部形成的表面保护膜和掺杂的n型iii族氮化物半导体层第一部分a的上部面s1形成的表面保护膜,暴露了掺杂的n型iii族氮化物半导体层第一部分a的上部面s1和led结构上部面。之后将led晶片浸入起泡溶液,即γ-丁内酯,之后将超声波以40khz频率照射10分钟生成气泡,利用该气泡塌陷在掺杂的n型iii族氮化物半导体层形成的气孔,进而如图14的sem照片制造了从晶片分离多个led结构而成的包含超薄型led元件的超薄型led元件集合体。另外,如图15可确认到在晶片上不存在未分离的led结构。

139.(比较例1)

140.通过通常的方法从led晶片制造了具有与直径为650nm、高度为4.2μm的实施例1相同的层叠结构的棒状led元件集合体。

141.(实验例1)

142.将通过实施例1和比较例1制造的led元件集合体分别投入于丙酮,之后以100w条件照射超声波进行分散,之后间隔15分钟测量吸光度,检测且确认了led元件2小时的分散状态,实施例1的超薄型led元件集合体的各个检测时间段的吸光度曲线图在图16示出,比较例1的棒状led元件集合体的各个检测时间段的吸光度曲线图在图17示出,在检测结果中将380nm~780nm可视光区域的光谱面积标准化,如图18示出了各时间段吸光度曲线图。

143.通过图18可以确认到,实施例1的超薄型led元件对比于比较例1的棒状led元件在丙酮溶剂中具有优秀的长时间分散保持性。

144.以上,对本发明的一实施例进行了说明,但是本发明的思想不限于在本说明书提出的实施例,理解本发明的思想的技术人员在相同的思想范围内通过构成元素的附加、改变、删除、增加等可容易提出其他实施例,而且这也包括在本发明的思想范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1