发光元件的制作方法

发光元件

1.本技术是中国发明专利申请(申请号:201810058016.6,申请日:2018年01月22日,发明名称:发光元件)的分案申请。

技术领域

2.本发明涉及一种发光元件的一结构,且特别是涉及一种包含一半导体结构及一焊垫位于半导体结构上的发光元件。

背景技术:

3.发光二极管(light-emittingdiode,led)为固态半导体发光元件,其优点为功耗低,产生的热能低,工作寿命长,防震,体积小,反应速度快和具有良好的光电特性,例如稳定的发光波长。因此发光二极管被广泛应用于家用电器,设备指示灯,及光电产品等。

技术实现要素:

4.一种发光元件包含一半导体结构,其包含一第一半导体层,一第二半导体层,及一活性层位于第一半导体层和第二半导体层之间;一环绕部位于半导体结构上及/或环绕半导体结构以露出第一半导体层的一表面;一第一绝缘结构位于半导体结构上,包含多个凸出部以覆盖第一半导体层的表面的一部分及多个凹陷部以露出第一半导体层的表面的其它部分;一第一接触部分形成在环绕部上,并通过多个凹陷部以接触第一半导体层的表面的其它部分;一第一焊垫形成在半导体结构上;以及一第二焊垫形成在半导体结构上。

附图说明

5.图1为本发明一实施例中所揭示的一发光元件2的上视图;

6.图2为沿着图1的线b-b’所揭示的发光元件2的剖视图;

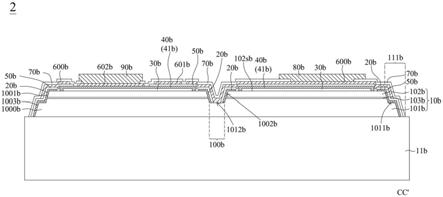

7.图3为沿着图1的线c-c’所揭示的发光元件2的剖视图;

8.图4为图1所揭示的发光元件2的各层上视图;

9.图5为本发明一实施例中所揭示的发光元件2的烧毁区域的上视图;

10.图6为传统发光元件3的烧毁区域的上视图;

11.图7为一突波(surge)于过度电性应力(electricaloverstress,eos)测试下的电压波型图;

12.图8为突波(surge)的最大施加电压对可导通的正向电压(forwardvoltage,vf)的一图表;

13.图9为突波(surge)的最大施加电压对反向电流(reversecurrent,ir)的一图表;

14.图10为本发明一实施例的发光装置30的示意图;

15.图11为本发明一实施例的发光装置4的示意图。

16.符号说明

17.2发光元件

18.3传统发光元件

19.4发光装置

20.10b半导体叠层

21.11b基板

22.20b、20b'第一绝缘结构

23.30发光装置

24.30b透明导电层

25.40b反射层

26.41b阻障层

27.50b、50b'第二绝缘结构

28.60b接触层

29.60b'接触层

30.70b第三绝缘结构

31.80b第一焊垫

32.90b第二焊垫

33.100b通孔

34.101b第一半导体层

35.102b第二半导体层

36.102sb表面

37.103b活性层

38.111b环绕部

39.201b环绕绝缘部分

40.203b环形覆盖区

41.301tb开口

42.401tb开口

43.411tb开口

44.501b开口

45.503b开口

46.505b外围

47.600b第一接触部分

48.601b第二接触部分

49.602b第三接触部分

50.701b第一开口

51.702b第二开口

52.1000b半导体结构

53.1002b内侧壁

54.1001b第二外侧壁

55.1003b第一外侧壁

56.1011b第一表面

57.1012b第二表面

58.2011b凸出部

59.2012b凹陷部

60.5051b凸出部

具体实施方式

61.为了使本发明的叙述更加详尽与完备,请参照下列实施例的描述并配合相关附图。但是,以下所示的实施例用于例示本发明的发光元件,并非将本发明限定于以下的实施例。又,本说明书记载于实施例中的构成零件的尺寸、材质、形状、相对配置等在没有限定的记载下,本发明的范围并非限定于此,而仅是单纯的说明而已。且各附图所示构件的大小或位置关系等,会由于为了明确说明有加以夸大的情形。更且,在以下的描述中,为了适切省略详细说明,对于同一或同性质的构件用同一名称、符号显示。

62.如图1至图4所示,图1为本发明一实施例中所揭示的一发光元件2的上视图。图2为沿着图1的线b-b’所揭示的发光元件2的剖视图。图3为沿着图1的线c-c’所揭示的发光元件2的剖视图。图4为图1所揭示的发光元件2的流程图。

63.发光元件2包含一基板11b;一或多个半导体结构1000b位于基板11b上;一环绕部111b位于一或多个半导体结构上及/或环绕一或多个半导体结构1000a;一第一绝缘结构20b位于半导体结构1000b上,并沿着环绕部111b形成;一透明导电层30b位于一或多个半导体结构1000b上;一反射结构包含一反射层40b及一阻障层41b位于透明导电层30b上;一第二绝缘结构50b覆盖反射层40b及阻障层41b;一接触层60b位于第二绝缘结构50b上;一第三绝缘结构70b位于接触层60b上;以及一第一焊垫80b和一第二焊垫90b位于接触层60b上。

64.如图1至图4所示,在发光元件2的制造流程中包含,首先在基板11b上形成半导体叠层10b。基板11b可以是蓝宝石基板,但并不限于此。在一实施例中,基板11b包含一图案化表面。图案化表面包括多个图案。图案的形状包括圆锥(cone),角锥(pyramid)或半球形。

65.在本发明的一实施例中,基板11b为一成长基板,用以外延成长半导体叠层10b,包括用以成长磷化铝镓铟(algainp)的砷化镓(gaas)晶片,或用以成长氮化铟镓(ingan)的蓝宝石(al2o3)晶片、氮化镓(gan)晶片或碳化硅(sic)晶片。

66.在本发明的一实施例中,基板11b包含一图案化表面位于半导体结构1000b和基板11b之间,其可提高发光元件的光取出效率。基板11b的裸露面可包含一图案化表面(图未示)。图案化表面可为各种图案,例如不规则图案、微透镜、微阵列、散射区域或其他种光学区域。例如,图案化表面包括多个凸部,各凸部包含一高度位于0.5~2.5μm之间,一宽度位于1~3.5μm之间,多个凸部之间包含一间距(pitch)位于1~3.5μm之间。

67.在本发明的一实施例中,基板11b包含一侧壁,其包含一平坦表面和/或一粗糙表面,以提高发光元件的光取出效率。在本发明的一实施例中,基板11b的侧壁倾斜于基板11b与半导体结构1000b邻接的一表面,以调整发光元件的光场分布。

68.在本发明的一实施例中,半导体叠层10b包括光学特性,例如发光角度或波长分布,以及电学特性,例如正向电压或向电流。半导体叠层10b通过有机金属化学气相沉积法(mocvd)、分子束外延(mbe)、氢化物气相沉积法(hvpe)、物理气相沉积法(pvd)或离子电镀方法,以形成于基板11b上,其中物理气象沉积法包含溅镀(sputtering)或蒸镀

(evoaporation)法。

69.一或多个半导体结构1000b各包含一半导体叠层10b,其包含一第一半导体层101b,一第二半导体层102b,及一活性层103b位于第一半导体层101b和第二半导体层102b之间。半导体结构1000b还包含一或多个通孔100b穿过第二半导体层102b和活性层103b以露出第一半导体层101b。第一半导体层101b和第二半导体层102b可各由单层或多个次层所构成。此外,活性层103b可为单量子阱结构或者多重量子阱结构。半导体叠层10b可通过金属有机化学气相沉积(mocvd),分子束外延(mbe)或物理气相沉积法(pvd),在基板11b上形成iii族氮化物化合物半导体层。

70.在本发明的一实施例中,在形成半导体叠层10b之前,可先形成一缓冲结构(图未示)于基板11b上,用以改善基板11b与半导体叠层10b之间的晶格不匹配。缓冲结构可由氮化镓(gan)系列的材料构成,例如氮化镓和氮化铝镓,或氮化铝(aln)系列的材料。缓冲结构可以是单层或多层。缓冲结构可以通过金属有机化学气相沉积(mocvd),分子束外延(mbe)或物理气相沉积(pvd)来形成。物理气相沉积(pvd)包括溅镀(sputter)法,例如反应性溅镀,或蒸镀法,例如电子束蒸镀法和热蒸镀法。在一实施例中,缓冲结构包括氮化铝(aln)缓冲层,并由溅镀(sputter)法形成。氮化铝(aln)缓冲层形成在具有图案化表面的成长基板上。溅镀(sputter)法可形成具有高均匀性的致密缓冲层,因此氮化铝(aln)缓冲层可共形地沉积在基板11b的图案化表面上。

71.在本发明的一实施例中,第一半导体层101b和第二半导体层102b,可为包覆层(cladding layer),两者具有不同的导电型态、电性、极性,或依掺杂的元素以提供电子或空穴。例如,第一半导体层101b为n型电性的半导体层,第二半导体层102b为p型电性的半导体层。活性层103b形成在第一半导体层101b和第二半导体层102b之间,电子与空穴于一电流驱动下在活性层103b内复合,并将电能转换成光能以发出一光线。通过改变半导体叠层10b的一层或多层的物理及化学组成以调整发光元件2所发出光线的波长。半导体叠层10b的材料包含

ⅲ‑ⅴ

族半导体材料,例如al

x

inyga

(1-x-y)

n或al

x

inyga

(1-x-y)

p,其中0≤x,y≤1;(x+y)≤1。依据活性层103b的材料,当半导体叠层10b的材料为alingap系列时,活性层103b可发出波长介于610nm及650nm之间的红光,或是波长介于530nm及570nm之间的黄光。当半导体叠层10b的材料为ingan系列时,活性层103b可发出波长介于400nm及490nm之间的蓝光、深蓝光,或是波长介于490nm及550nm之间的绿光。当半导体叠层10b的材料为algan系列时,活性层103b可发出波长介于250nm及400nm之间的紫外光。活性层103b可为单异质结构(single heterostructure,sh),双异质结构(double heterostructure,dh),双侧双异质结构(double-side double heterostructure,ddh),或多层量子阱结构(multi-quantum well,mqw)。活性层103b的材料可为中性、p型或n型电性的半导体。

72.在半导体叠层10b形成在基板11b之后,通过光刻(photolithography)和蚀刻工艺以图案化半导体叠层10b,以形成多个通孔100b以及环绕部111b。通过光刻(photolithography)和蚀刻工艺,第二半导体层102b和活性层103b的内部的一部分被移除以形成多个通孔100b,并且多个通孔100b对应地裸露出第一半导体层101b的第二表面1012b。于此,通孔100b由一内侧壁1002b和第二表面1012b所定义。内侧壁1002b的一端连接至第一半导体层101b的第二表面1012b,而内侧壁1002b的另一端连接至第二半导体层102b的表面102sb。

73.在相同或另一个光刻(photolithography)和蚀刻工艺,围绕半导体结构1000b周围的第二半导体层102b和活性层103b被移除以形成环绕部111b,且环绕部111b露出第一半导体层101b的第一表面1011b。在另一实施例中,在光刻(photolithography)和蚀刻工艺中,第一半导体层101b的一部分进一步地被蚀刻至更深的蚀刻深度,以露出第二表面1012b和第一表面1011b。具体而言,环绕部111b包含基板11b的裸露面,第一半导体层101b露出的第一表面1011b,以及由第二半导体层102b,活性层103b和第一半导体层102b露出的侧表面所构成的第一外侧壁1003b和第二外侧壁1001b,其中第一表面1011b的一端连接至第一外侧壁1003b,第一表面1011b的另一端连接至第二外侧壁1001b。第一外侧壁1003b和第二外侧壁1001b倾斜于第一表面1011b。环绕部111b沿着半导体结构1000b的一外围而形成,位于及/或围绕一或多个半导体结构1000b的外围。在一实施例中,第一外侧壁1003b倾斜于基板11b的裸露面(图未示)。第一外侧壁1003b与基板11b的裸露面之间包含一锐角。在一实施例中,第一外侧壁1003b与基板11b的裸露面之间包含一钝角。

74.在半导体结构1000b形成之后,第一绝缘结构20b形成于半导体叠层10b上,覆盖第二半导体层102b的表面102sb的一部分,并延伸至第二外侧壁1001b,且覆盖第一表面1011b。换言之,第一绝缘结构20b覆盖环绕部111b的多个部分。第一绝缘结构20b保护半导体结构1000b的侧壁,防止活性层103b为后续制作工艺所破坏。如图4所示,在一上视图中,第一绝缘结构20b包含一环绕绝缘部分201b以及多个环形覆盖区203b。于此,在一上视图中,环绕绝缘部分201b包含多个凸出部2011b以及多个凹陷部2012b。多个环形覆盖区203b为环绕绝缘部分201b所围绕,且多个环形覆盖区203b分别形成于多个通孔100b内,并且与多个通孔100b相对应。多个环形覆盖区203b中的每一个具有一开口(图未标号)以露出第一半导体层101b的第二表面1012b。在一实施例中,第一绝缘结构20b的环绕绝缘部分201b沿着第一半导体层101b的第一表面1011b而设置,并且围绕半导体结构1000b。在本实施例中,环绕绝缘部分201b的多个凸出部2011b和多个凹陷部2012b沿着环绕部111b交替配置,并且多个环形覆盖区203b的位置与多个通孔100b的位置相对应,但是本发明并不限于此。在一实施例中,位于两个凸出部2011b之间的一区域构成凹陷部2012b。在另一实施例中,环绕绝缘部分201b还包含一次凸出部延伸自凸出部2011b,及/或还包括一次凹陷部自凹陷部2012b凹陷。在本实施例中,多个凸出部2011b延伸自第二半导体层102b的上表面102sb,直接接触并覆盖第一半导体层101b的第一表面1011b的多个部分以及第一半导体层102b的第一表面1011b的多个角落。多个凹陷部2012b露出未被多个凸出部2011b所覆盖的第一半导体层101b的第一表面1011b的其他部分。在一实施例中,多个凹陷部2012b露出位于半导体结构1000b的多个边上的第一表面1011b。如图2所示,在一剖视图中,第一绝缘结构20b的凹陷部2012b露出第一半导体层101b的第一表面1011b的一部分。如图3所示,在一剖视图中,第一绝缘结构20b的凸出部2011b覆盖第一半导体层101b的第一表面1011b以及半导体结构1000b的多个侧壁。换言之,多个凸出部2011b和多个凹陷部2012b交替地覆盖第一半导体层101b的第一表面1011b的一部分并露出第一半导体层101b的第一表面1011b的另一部分。在本实施例中,第一表面1011b的露出部分是不连续的,并且第一表面1011b的露出部分的总面积小于第一表面1011b的总面积。大部分的第二半导体层102b未被第一绝缘结构20b所覆盖。在一上视图中,环绕绝缘部分201b的形状包含环状,例如矩形、圆形或多边形。多个凸出部2011b或多个凹陷部2012b之一的形状包含三角形、矩形、半圆形、圆形或多边形。第一绝

缘结构20b的材料包含非导电材料。非导电材料包含有机材料,无机材料或是介电材料。有机材料包含su8、苯并环丁烯(bcb)、过氟环丁烷(pfcb)、环氧树脂(epoxy)、丙烯酸树脂(acrylic resin)、环烯烃聚合物(coc)、聚甲基丙烯酸甲酯(pmma)、聚对苯二甲酸乙二酯(pet)、聚酰亚胺(pi)、聚碳酸酯(pc)、聚醚酰亚胺(polyetherimide)或氟碳聚合物(fluorocarbon polymer)。无机材料包含硅胶(silicone)或玻璃(glass)。介电材料包含氧化铝(al2o3)、氮化硅(sin

x

)、氧化硅(sio

x

)、氧化钛(tio

x

)、或氟化镁(mgf

x

)。第一绝缘结构20b包含一层或多层。第一绝缘结构20b可以保护半导体结构1000b的侧壁,防止活性层103b为后续制作工艺所破坏。当第一绝缘结构20b包含多层时,第一绝缘结构20b可为包含多对膜层的布拉格反射镜(dbr)结构以保护半导体结构1000b的侧壁及选择性地反射活性层103b所发出的特定波长的光至发光元件2的外部以提高亮度,并且每一膜层具有一折射率与相邻膜层的折射率不同。具体而言,第一绝缘结构20b可以通过交替堆叠sio

x

层和tio

x

层来形成。通过调整每对膜层的高折射率和低折射率之间的折射率差异,以使布拉格反射镜(dbr)对特定波长或在特定波长范围内具有高反射率。每对膜层中的两层具有不同的厚度。每对膜层中具有相同材料的层的厚度可以相同或不同。

75.在第一绝缘结构20b形成之后,透明导电层30b形成于第二半导体层102b上,包含多个开口301tb以露出第一半导体层101b的第二表面1012b。在本实施例中,在一上视图中,透明导电层30b的形状对应于第二半导体层102b的形状,并且多个开口301tb的位置对应于多个环形覆盖区203b和多个通孔100b的位置。透明导电层30b接触并覆盖第二半导体层102b以扩散电流,并将电流注入于第二半导体层102b。此外,透明导电层30b不与第一半导体层101b相接触。在一实施例中,发光元件2包含另一个透明导电层(图未标示)与环绕部111b的第一半导体层101b相接触。透明导电层30b的材料包括对从活性层103b所发射的光线为透明的透明材料,例如氧化铟锌(izo)或氧化铟锡(ito)。透明导电层30b可与第二半导体层102b形成低电阻接触,例如欧姆接触(ohmic contact)。透明导电层30b包含一层或多个次层。例如,当透明导电层30b包含多个次层时,透明导电层30b可为包含多对次层的布拉格反射镜(dbr)结构,并且每一个次层具有一折射率与相邻次层的折射率不同。具体而言,透明导电层30b可以通过交替堆叠具有不同折射率的两个次层来形成布拉格反射镜(dbr)结构。

76.在透明导电层30b形成之后,反射结构包含反射层40b及阻障层41b对应形成于透明导电层30b上。在一实施例中,反射结构对准于透明导电层30b,反射结构的多边对准于透明导电层30b的多边。在一实施例中,反射结构不与透明导电层30b对齐,并且反射结构的多边位于透明导电层30b的多边以内或以外。在一实施例中,透明导电层30b和反射结构延伸至第一绝缘结构20b上。

77.反射层40b及阻障层41b分别包含多个开口401tb和411tb。反射层40b的多个开口401tb及阻障层41的多个开口411tb露出多个环形覆盖区203b、多个通孔以及第一半导体层101b的第二表面1012b。阻障层41b形成并覆盖于反射层40b上,阻障层41b可以防止反射层40b的金属元素的迁移、扩散或氧化。反射结构的反射层40b和阻障层41b的形状对应于透明导电层30b的形状。在一实施例中,反射结构的反射层40b和阻障层41b的形状接近于矩形,并且反射层40b和阻障层41b的角落为弧形。反射层40b包含单层结构或者多层结构,并且反射层40b的材料包含对于活性层103b所发射的光线具有高反射率的金属材料,例如银(ag),

金(au),铝(al),钛(ti),铬(cr),铜(cu),镍(ni),铂(pt)或上述材料的合金。阻障层41b包含单层结构或多层结构,阻障层的材料包括铬(cr),铂(pt),钛(ti),钨(w)或锌(zn)。当阻障层41b为多层结构时,阻障层41b是由第一阻障层(图未示)和第二阻障层(图未示)交替堆叠而形成,例如cr/pt,cr/ti,cr/tiw,cr/w,cr/zn,ti/pt,ti/w,ti/tiw,ti/zn,pt/tiw,pt/w,pt/zn,tiw/w,tiw/zn,或w/zn。反射结构可还包含一布拉格反射镜(dbr)形成在反射层40b之下。布拉格反射镜(dbr)结构包含多对次层,并且每一次层具有一折射率与相邻次层的折射率不同。在一实施例中,多对次层可以通过交替堆叠sio

x

层和tio

x

层来形成。通过调整每对次层的高折射率和低折射率之间的折射率差异,以使布拉格反射镜(dbr)对特定波长或在特定波长范围内具有高反射率。每对次层的其中两层具有不同的厚度。每对次层中具有相同材料的层的厚度可以相同或不同。

78.在反射结构形成之后,第二绝缘结构50b形成在反射结构上以覆盖反射结构(反射层40b或阻障层41b)的上表面的一部分,并且位于反射结构与第一绝缘结构20b之间的第二半导体层102b的周围区域。第二绝缘结构50b接触并覆盖第一绝缘结构20b,使得环绕部111b的第一外侧壁1003b和第二外侧壁1001b以及为第一绝缘结构20b所覆盖的第一表面1011b的部分也被第二绝缘结构50b所覆盖。第二绝缘结构50b可保护半导体结构1000b的侧壁,防止活性层103b为后续制作工艺所破坏。由于第二绝缘结构50b覆盖第一绝缘结构20b,因此第二绝缘结构50b能够防止第一绝缘结构20b于后续制作工艺中被蚀刻移除。如图4所示,第二绝缘结构50b包含多个开口501b以及一开口503b。于此,第二绝缘结构50b包含一外围505b具有多个凸出部5051b和多个凹陷部5052b。开口503b露出反射结构的反射层40b或阻障层41b的一部分,并且多个开口501b露出第一半导体层101b的第二表面1012b。如图2至图4所示,在本实施例中,第二绝缘结构50b的外围505b接触、覆盖并对齐于第一绝缘结构20b。多个开口501b的位置与多开口401tb,411tb,301tb,以及多个通孔100b的位置对应。此外,位于第二绝缘结构50b外围505b的多个凸出部5051b和多个凹陷部5052b沿着第一绝缘结构20b的环绕绝缘部分201b或环绕部111b交替排列以分别覆盖及暴露第一半导体层101b的第一表面1011b的不同部分。在一实施例中,位于两个凸出部5051b之间的区域构成凹陷部5052b。在另一实施例中,第二绝缘结构50b还包含一次凸出部延伸自凸出部5051b,及/或还包括一次凹陷部自凹陷部5052b凹陷。此外,在一实施例中,第二绝缘结构50b的外围505b的形状对应于第一绝缘结构20b的环绕绝缘部分201b的形状,用以不连续地露出位于环绕部111b上的第一半导体层101b的第一表面1011b的部分。换言之,多个凸出部5051b和多个凹陷部5052b的形状和位置对应于环绕绝缘部分201b的多个凸出部2011b和多个凹陷部2012b的形状和位置。为多个凹陷部2012b所露出的第一表面1011b的部分也为多个多个凹陷部5052b所露出。为多个凸出部2011b所覆盖的第一表面1011b的部分也为多个凸出部5051b所覆盖。当第一表面1011b为第一绝缘结构20b和第二绝缘结构50b所不连续地露出时,在一实施例中,凸出部5051b和凹陷部5052b的形状或位置可与凸出部2011b和凹陷部2012b的形状或位置不同。在一实施例中,凸出部5051b和凹陷部5052b的面积可大于或小于凸出部2011b和凹陷部2012b的面积。为凹陷部2012b及凹陷部5052b所露出的第一表面1011b的部分通过凸出部2011b,5051b和凹陷部2012b,5052b的形状、位置或面积来调整。

79.如图2所示,在一剖视图中,第一半导体层101b的第一表面1011b的一部分为第一绝缘结构20b的多个凹陷部2012b所露出,并且为第二绝缘结构50b的多个凹陷部5052b所露

出。换言之,第二绝缘结构50b的多个凹陷部5052b露出第一半导体层101b的第一表面1011b上未被多个凸出部2011b,5051b覆盖并且为多个凹陷部2012b所露出的部分。如图3所示,在一剖视图中,多个凸出部5051b于第一半导体层101b的第一表面1011b上覆盖第一绝缘结构20b的多个凸出部2011b,并且覆盖形成在第一外侧壁1003b和第二外侧壁1001b上的环绕绝缘部分201b以及第一半导体层101b的第一表面1011b的角落,其中第一外侧壁1003b和第二外侧壁1001b是由第二半导体层102b,活性层103b和第一半导体层101b所露出的侧表面所构成。具体而言,在本实施例中,多个凸出部5051b直接接触第一绝缘结构20b的多个凸出部2011b,多个凹陷部5052b露出第一半导体层101b的第一表面1011b,且多个凸出部5051b及多个凹陷部5052b彼此交替排列以不连续地露出第一半导体层101b的第一表面1011b的部分。换言之,为多个凹陷部5052b所露出的第一表面1011b的部分是不连续的,并且第一表面1011b具有一总裸露面积。第一表面1011b的总裸露面积小于第一表面1011b的整体面积。

80.在一实施例中,多个凸出部5051b之一的形状包含三角形、矩形、半圆形、圆形或多边形。第二绝缘结构50b的材料包含非导电材料。非导电材料包含有机材料,无机材料或介电材料。有机材料包含su8、苯并环丁烯(bcb)、过氟环丁烷(pfcb)、环氧树脂(epoxy)、丙烯酸树脂(acrylic resin)、环烯烃聚合物(coc)、聚甲基丙烯酸甲酯(pmma)、聚对苯二甲酸乙二酯(pet)、聚酰亚胺(pi)、聚碳酸酯(pc)、聚醚酰亚胺(polyetherimide)或氟碳聚合物(fluorocarbon polymer)。无机材料包含硅胶(silicone)或玻璃(glass)。介电材料包含氧化铝(al2o3)、氮化硅(sin

x

)、氧化硅(sio

x

)、氧化钛(tio

x

)、或氟化镁(mgf

x

)。第二绝缘结构50b包含一层或多层。第二绝缘结构50b可保护半导体结构1000b的侧壁,防止活性层103b为后续制作工艺所破坏,以及选择性地反射活性层103b所发出的特定波长的光至发光元件2的外部以提高亮度。当第二绝缘结构50b包含多层时,第二绝缘结构50b可为包含多对膜层的布拉格反射镜(dbr)结构,并且每一膜层具有一折射率与相邻膜层的折射率不同。在一实施例中,第二绝缘结构50b可以通过交替堆叠sio

x

层和tio

x

层来形成。通过调整每对膜层的高折射率和低折射率之间的折射率差异,以使布拉格反射镜(dbr)对特定波长或在特定波长范围内具有高反射率。每对膜层中的两层具有不同的厚度。每对膜层中具有相同材料的层的厚度可以相同或不同。

81.参考图1至图4,接触层60b位于第二绝缘结构50b及反射结构(反射层40b及阻障层41b)上,包含一第一接触部分600b,一第二接触部分601b及一第三接触部分602b。在一实施例中,其中于一上视图下,第二接触部分601b位于半导体结构的一几何中心上。第一接触部分600b及第三接触部分602b彼此分离。第三接触部分602b为第一接触部分600b所围绕。第一接触部分600b电连接至第一半导体层101b,第三接触部分602b电连接至第二半导体层102b,且第二接触部分601b与第一半导体层101b及第二半导体层102b电性绝缘。在一实施例中,第二接触部分601b电连接至第一接触部分600b及第三接触部分602b的其中之一。在一实施例中,第一接触部分600b通过第二绝缘结构50b的多个开口501b及多个凹陷部5052b以接触第二表面1012b及第一表面1011b,并电连接至第一半导体层101b。此外,在环绕部111b的一剖视图中,第一接触部分600b沿着第一绝缘结构20b或第二绝缘结构50b的一外围505b具有一凹凸上表面。第一接触部分600b沿着外围505b而形成在多个凸出部5051b和多个凹陷部5052b上,并且凹凸上表面对应于多个凸出部5051b和多个凹陷部5052b而形成。第一接触部分600b通过环绕绝缘部分201b的多个凹陷部2012b及第二绝缘结构50b的多个凹

陷部5052b以不连续地接触第一表面1011b。第一接触部分600b与第一半导体层101b的第一表面1011b包含多个不连续的第一接触区域(图未示)。第一接触部分600b与第一半导体层101b的第二表面1012b包含多个第一接触区域(图未示)。

82.在本实施例中,第二接触部分601b及第三接触部分602b为第一接触部分600b所环绕,并且于一上视图中,第二接触部分601b的形状包含一几何形状,例如矩形、圆形或不规则形。第三接触部分602b通过第二绝缘结构50b的开口503b以接触反射结构并电连接至第二半导体层102b。第三接触部分602b与反射结构之间具有一第二接触区域(图未示)。在一实施例中,第二接触部分601b可连接至第一接触部分600b或第三接触部分602b。接触层60b可为单层或多个次层组成。接触层60b包含金属材料,例如铝(al),铬(cr),铂(pt),钛(ti),钨(w)或锌(zn)。

83.参考图1至图4,在接触层60b形成之后,第三绝缘结构70b形成在接触层60b上并覆盖接触层60b。第三绝缘结构70b包含一第一开口701b及一第二开口702b。第三绝缘结构70b的第一开口701b露出接触层60b的第一接触部分600b。第二开口702b露出接触层60b的第三接触部分602b。第三绝缘结构70b的材料包含非导电材料。非导电材料包含有机材料,无机材料或是介电材料。有机材料包含su8、苯并环丁烯(bcb)、过氟环丁烷(pfcb)、环氧树脂(epoxy)、丙烯酸树脂(acrylic resin)、环烯烃聚合物(coc)、聚甲基丙烯酸甲酯(pmma)、聚对苯二甲酸乙二酯(pet)、聚酰亚胺(pi)、聚碳酸酯(pc)、聚醚酰亚胺(polyetherimide)或氟碳聚合物(fluorocarbon polymer)。无机材料包含硅胶(silicone)或玻璃(glass)。介电材料包含氧化铝(al2o3)、氮化硅(sin

x

)、氧化硅(sio

x

)、氧化钛(tio

x

)、或氟化镁(mgf

x

)。第一绝缘结构20b,第二绝缘结构50b及第三绝缘结构70b可通过网印,蒸镀或溅镀而形成。

84.在第三绝缘结构70b形成之后,第一焊垫80b和第二焊垫90b形成在半导体叠层10b上以完成发光元件2的制造。第一焊垫80b及第二焊垫90b的位置分别对应于第三绝缘结构70b的第一开口701b及第二开口702b的位置。在一实施例中,第一焊垫80b及第二焊垫90b的位置及形状分别对应于第三绝缘结构70b的第一开口701b及第二开口702b的位置及形状。第一焊垫80b通过第三绝缘结构70b的第一开口701b以与接触层60b的第一接触部分600b相接触,并电连接至第一半导体层101b。第二焊垫90b通过第三绝缘结构70b的第二开口702b以与接触层60b的第三接触部分602b相接触,并电连接至第二半导体层102b。在一实施例中,由发光元件的一上视图观之,第一焊垫80b包含与第二焊垫90b相同的形状,例如第一焊垫80b及第二焊垫90b包含梳状,但发明并不限于此。在一实施例中,第一焊垫80b的形状或大小可与第二焊垫90b的形状或大小不同。例如,第一焊垫80b的形状为矩形,第二焊垫90b的形状为梳状,且第一焊垫80b的面积大于第二焊垫90b的面积。在一实施例中,第一焊垫80b和第二焊垫90b包含一结构具有单层或多层。第一焊垫80b和第二焊垫90b包含金属材料,例如铬(cr),钛(ti),钨(w),铝(al),铟(in),锡(sn),镍(ni),铂(pt)或上述材料的合金。当第一焊垫80b和第二焊垫90b包含多层时,第一焊垫80b包含一第一上焊垫和第一下焊垫,并且第二焊垫90b包括第二上焊垫和第二下焊垫。上焊垫和下焊垫具有不同的功能。上焊垫的功能是用于焊接和接线。发光元件2可通过上焊垫通过焊料(solder)或ausn共晶接合、翻转并安装至一封装基板上。上焊垫包含一具有高延展性的金属材料,例如镍(ni),钴(co),铁(fe),钛(ti),铜(cu),金(au),钨(w),锆(zr),钼(mo),钽(ta),铝(al),银(ag),铂(pt),钯(pd),铑(rh),铱(ir),钌(ru),锇(os)。上焊垫可以是上述材料的单层,多层或合

金。在本发明的一实施例中,上焊垫的材料较佳的包含镍(ni)及/或金(au),且上焊垫可为单层或多层。下焊垫的功能是与接触层60b、反射层40b或阻障层41b形成稳定介面,例如改善第一下焊垫和接触层60b之间的介面接合强度,或改善第二下焊垫与反射层40b或阻障层41b之间的介面接合强度。下焊垫的另一个功能是防止焊料或ausn中的锡(sn)扩散至反射结构中,破坏反射结构的反射率。因此,下焊垫较佳的包含金(au)和铜(cu)以外的金属元素,例如镍(ni),钴(co),铁(fe),钛(ti),钨(w),锆(zr),钼(mo),钽(ta),铝(al),银(ag),铂(pt),钯(pd),铑(rh),铱(ir),钌(ru),锇(os)。下焊垫可以是上述材料的单层,多层或合金。在本发明的一实施例中,下焊垫较佳的包括钛(ti)和铝(al)的多层膜,或铬(cr)和铝(al)的多层膜。

85.在一实施例中,当操作发光元件2之时,一外部电源分别电连接至第一焊垫80b和第二焊垫90b。此时电流被注入至发光元件2中,通过第一接触部分600b和第三接触部分602b以扩散电流,分别经由第一接触区域和第二接触区域注入第一半导体层101b和第二半导体层102b中。为了改善发光元件2的电流分布,可以调整第一接触部分600b以及第一半导体层101b的第一表面1011b之间的第一接触区域的面积和位置,避免电流集中于第一表面1011b的某些区域,例如第一表面1011b的角落。在一实施例中,由于第一绝缘结构20b的环绕绝缘部分201b和第二绝缘结构50b的外围505b覆盖第一半导体层101b的第一表面1011b的一部分,所以接触层60b和第一表面1011b间的第一接触区域的面积和位置可通过环绕绝缘部分201b和第二绝缘结构50b来调整。换言之,第一接触区域的面积和位置通过环绕绝缘部分201b和第二绝缘结构50b的凹陷部2012b,5052b所露出的第一表面1011b的露出部分来调整。然而,在设计第一绝缘结构20b的环绕绝缘部分201b和第二绝缘结构50b时,发光元件2的正向电压(vf)和电流分布必须同时考虑有所取舍。具体而言,第一接触区域的面积越大,发光元件2的正向电压越低。然而,若第一接触区域的面积越大,发光元件2将产生电流壅塞效应。为了达到可接受的正向电压(vf)和较佳的电流分布,第一接触部分600b被设计通过多个凹陷部2012b,5052b以不连续地接触第一表面1011b,通过多个凸出部2011b,5051b以与第一表面1011b的部分电性绝缘。在一实施例中,第一接触部分600b被设计成避免接触第一半导体层101b的第一表面1011b的角落。依此,电流通过第一接触部分600b的不连续的第一接触区域而注入至第一半导体层101b,且不能直接注入至为第一绝缘结构20b和第二绝缘结构50b所覆盖的区域中。因此,电流可以通过第一接触部分600b扩散,并进一步通过不连续的第一接触区域扩散。换言之,环绕绝缘部分201b和第二绝缘结构50b的外围505b设计可影响正向电压值,并改变电流路径,迫使电流流入为多个凹陷部2012b及多个凹陷部5052b所露出的第一表面,改变电流分布。在本实施例中,第一接触部分600b的面积足够以达到可接受的正向电压值,例如2.15v~2.4v,并且在此第一接触区域下可以达到期望的电流分布,细节将于下描述。

86.如图5和图6所示,图5是发光元件2的烧毁区域的上视图。图6是现有发光元件3的烧毁区域的上视图。发光元件2与传统的发光元件3之间的差异在于传统发光元件3的第一绝缘结构20b'与第二绝缘结构50b'不具有如发光元件2的多个凸出部2011b,5051b和多个凹陷部2012b,5052b。在传统发光元件3中,第一半导体层101b的第一表面1011b整体被暴露以与接触层60b接触,使得接触层60b是连续的接触第一半导体层101b的第一表面1011b,并且直接接触第一半导体层101b的第一表面1011b的角落(图未标示)。

87.如图6所示,当传统的发光元件3被施以一突波时,传统的发光元件3无法承受此高电压并有效地分散电流,使电流集中于角落,因此传统的发光元件3容易烧毁。参考图6,突波的电压超过传统发光件3的正常工作电压,并且此突波通过标号为f3的多个故障区域以烧毁传统的发光元件3。相较于其他区域,传统发光件3的电流更倾向于聚集在角落处。当发光元件2被施以一超过其可承受的突波时,如图5所示,发光元件2的故障区域标号为f2。故障区域f2的分布与传统发光元件3的故障区域f3的分布不同,发光元件2的电流未聚集在第一半导体层101b的第一表面1011b的角落,发光元件2的电流分布比传统的发光元件3的电流分布更均匀,并可承受更高电压的突波。

88.在本实施例中,接触层60b与第一半导体层101b的第一表面1011b间的不连续第一接触区有益于发光元件2的电流扩散,并且避免发光元件2被击穿(breakdown)。此外,通过不连续的第一接触区,发光元件2具有可接受的正向电压,例如,2.15v-2.4v,和预期的电流分布。在一实施例中,发光元件2和传统的发光元件3在不同施加电压下进行过度电性应力(electrical over stress,eos)测试。请参考图7、图8和图9。图7是一突波(surge)于过度电性应力(electrical over stress,eos)测试下的电压波型图。图8是发光元件2与现有发光元件3于过度电性应力(electrical over stress,eos)测试下,最大施加电压的突波(surge)对可导通的正向电压(forward voltage,vf)的一图表。图9是发光元件2与现有发光元件3于过度电性应力(electrical over stress,eos)测试下,突波(surge)的最大施加电压对反向电流(reverse current,ir)的一图表。为了进一步比较本发明的发光元件2和传统的发光元件3,如图8所示,发光元件2的样品1,2和传统发光元件3的样品1,2于过度电性应力(electrical over stress,eos)测试。在eos测试中(符合iec 61000-4-5标准),如图7所示,具有一电压波形的突波分别施加到发光元件2和传统的发光元件3。每一突波的电压随时间而变化,并且每一突波具有一最大施加电压va(max)。如图8所示,多个样品被施以不同的最大施加电压va(max),例如0v,20v,30v,35v,40v,45v,50v,55v,60v和65v。对每一最大施加电压va(max),以每秒1次的频率施加5次突波,每一突波约持续10-4

秒。每一样品的大小约为38

×

38mil2。经最大施加电压进行突波测试之后,在固定电流10μa下驱动每个样品,测量每个样品的正向电压(vf)并记录于图8的表格中。如图8所示,发光元件2的样品1,2分别在最大施加电压65v和60v的突波下进行eos测试,其所测量到的正向电压vf小于2.15v。传统发光元件3的样品1,2在最大施加电压50v的突波下进行eos测试,其所测量到的正向电压vf小于2.15v。此外,由于可接受的正向电压值在2.15v和2.4v之间,发光元件2的样品1在施加等于或小于60v的最大施加电压的突波之后,所测量到的正向电压大于2.15v及小于2.4v,即发光元件2的样品1于eos测试之后仍能正常操作。发光元件2的样品2在施加等于或小于55v的最大施加电压的突波之后,所测量到的正向电压大于2.15v及小于2.4v,即样品2于eos测试之后仍能正常操作。相较于传统的发光元件3,发光元件2可承受60v的最大施加电压的突波,因此发光元件2于过度电性应力(electrical over stress,eos)测试中的表现比传统的发光元件3佳。

89.在一实施例中,与上述实施例类似,如图9所示,将发光元件2的样品1,2,3,4以及现有的发光元件3的样品1,2,3,4用于过度电性应力(electrical over stress,eos)测试。通过施加不同的最大电压0v,60v,65v,70v,75v和80v以对每一样品施以一突波(surge)测试。经施以最大电压后的突波(surge)测试之后,在反向电压-5v下驱动样品,并测量每一样

品的反向电流(ir),将测量值纪录于图9中。在本实施例中,发光元件的可接受的反向电流(ir)小于0.3μa。如图9所示,当发光元件受到损伤,例如击穿,则反向电流(ir)将会发生,且在本实施例会被量测到如图9所示的100μa的读值。在最大施加电压75v和80v的突波(surge)下进行过度电性应力(electrical over stress,eos)测试,发光元件2的样品1,2,3,4的反向电流ir(μa)为100μa大于0.3μa。换言之,发光元件2可承受的突波(surge)的最大施加电压在75v以下。在最大施加电压65v至80v的突波(surge)下进行过度电性应力(electrical over stress,eos)测试,发光元件3的样品1,2,3,4的反向电流ir(μa)大于0.3μa。换言之,发光元件3可承受的突波(surge)的最大施加电压在65v以下。此外,由于可接受的反向电流(ir)小于0.3μa,在施以等于或小于70v的最大施加电压的突波(surge)之后,发光元件2的样品1,2,3,4的测试结果显示反向电流ir为零,即发光元件2的样品1,2,3,4仍可正常操作并通过过度电性应力(electrical over stress,eos)测试。相较于发光元件3,发光元件2可承受70v的最大施加电压,因此发光元件2于过度电性应力(electrical over stress,eos)测试中的表现比传统的发光元件3佳。

90.如图8及图9所示,发光元件2在过度电性应力(electrical over stress,eos)测试下的可靠度优于传统的发光元件3。在本发明的实施例中,通过第一绝缘结构的环绕绝缘部分201b和第二绝缘结构50b的外围505b设计,本发明的发光元件2可避免电流集中于角落。并且,可通过调整接触层60b的第一接触区域的面积和位置,以达到可接受的正向电压。由此可以达到2.15v~2.4v之间的正向电压,改善发光元件2的电流分布,提高发光元件2的可靠度。

91.图10为依本发明一实施例的发光装置30的示意图。将前述实施例中的发光元件2以倒装芯片的形式安装于封装基板51的第一垫片511、第二垫片512上。第一垫片511、第二垫片512之间通过一包含绝缘材料的绝缘部53做电性绝缘。倒装芯片的安装将与焊垫形成面相对的成长基板11b侧朝上设置,使成长基板侧为主要的光取出面。为了增加发光装置30的光取出效率,可于发光元件2的周围设置一反射结构54。

92.图11为依本发明一实施例的发光装置4的示意图。发光装置4为一球泡灯包括一灯罩602、一反射镜604、一发光模块610、一灯座612、一散热片614、一连接部616以及一电连接元件618。发光模块610包含一承载部606,以及多个发光单元608位于承载部606上,其中多个发光单元608可为前述实施例中的发光元件2或发光装置30。

93.本发明所列举的各实施例仅用以说明本发明,并非用以限制本发明的范围。任何人对本发明所作的任何显而易知的修饰或变更都不脱离本发明的精神与范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1