半导体器件结构及电子设备的制作方法

1.本申请各实施例属于半导体领域,具体涉及半导体器件结构及电子设备。

背景技术:

2.在半导体芯片的封装工艺无论是打线还是其它工艺步骤,都会对顶层金属产生一定的拉力,这样导致金属层与下方氧化层或介质层会进行分层。

技术实现要素:

3.本申请实施例目的在于克服上述问题或者至少部分地解决或缓解上述问题,本申请提供的技术方案可以降低半导体器件结构中的金属层与介质层分层的风险。

4.第一方面,本申请实施例提供了一种半导体器件结构,包括,半导体器件本体,所述半导体器件本体上表面设置有介质层,在所述介质层上方对应位置间隔设置有栅极金属层与源极金属层,在所述介质层中与栅极金属层对应的位置至少设置一个第一接触孔和第二接触孔,在所述介质层中与源极金属层对应的位置至少设置一个第三接触孔,所述第一接触孔、所述第二接触孔和所述第三接触孔中填充有导电金属。

5.与现有技术相比,本申请实施例通过在金属层下方排布多个接触孔,来增加金属与介质层的接触面积,这样可以降低半导体器件结构中的金属层与介质层分层的风险。

6.第二方面,本申请实施例还提供了一种电子设备,包括第一方面所述的一种半导体器件结构。

7.与现有技术相比,本申请第二方面提供实施例的有益效果与上述任一方面技术方案的有益效果相同,在此不再赘述。

附图说明

8.此处所说明的附图用来提供对本申请的进一步理解,构成本申请的一部分,本申请的示意性实施例及其说明用于解释本申请,并不构成对本申请的不当限定。后文将参照附图以示例性而非限制性的方式详细描述本申请的一些具体实施例。附图中相同的附图标记标示了相同或类似的部件或部分,本领域技术人员应该理解的是,这些附图未必是按比例绘制的,在附图中:

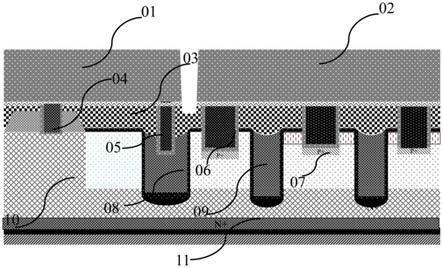

9.图1为本申请实施例中的一种半导体器件结构。

具体实施方式

10.为了使本技术领域的人员更好地理解本申请方案,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分的实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本申请保护的范围。

11.本申请实施例提供了一种半导体器件结构,包括,半导体器件本体,所述半导体器件本体上表面设置有介质层03,介质层03可以为氧化层sio2,在所述介质层03上方对应位置间隔设置有栅极金属层01与源极金属层02,在所述介质层03中与栅极金属层01对应的位置至少设置一个第一接触孔04和第二接触孔05,第一接触孔04和第二接触孔05中填充有有导电金属,如金属铝,在所述介质层03中与源极金属层02对应的位置至少设置一个第三接触孔06,第三接触孔06中也填充有有导电金属,如金属铝,所述半导体本体中与所述栅极金属层01对应位置设置有第一沟槽08,在所述半导体本体中与所述源极金属层02对应位置设置有第二沟槽09,所述第一沟槽08和所述第二沟槽09中填充有多晶硅,所述第二接触孔05设置在所述第一沟槽08中,所述第一接触孔04设置在介质层03中或延伸至所述半导体本体中的外延层10中,第三接触孔06延伸至所述半导体本体中的外延层10中,所述第三接触孔06底部与所述半导体本体接触的位置设置注入区07,注入区07都为p

+

注入区,外延层10为n型。

12.此半导体器件结构可为mos管或者igbt功率半导体芯片。

13.在本申请实施例中,源极金属层设置在半导体本体的背面。

14.本申请提供的技术方案可以降低半导体器件结构中的金属层与介质层分层的风险。

15.最后应说明的是:以上各实施例仅用以说明本申请的技术方案,而非对其限制;尽管参照前述各实施例对本申请进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例技术方案的范围。

技术特征:

1.一种半导体器件结构,其特征在于,包括,半导体器件本体,所述半导体器件本体上表面设置有介质层,在所述介质层上方对应位置间隔设置有栅极金属层与源极金属层,在所述介质层中与栅极金属层对应的位置至少设置一个第一接触孔和第二接触孔,在所述介质层中与源极金属层对应的位置至少设置一个第三接触孔,所述第一接触孔、所述第二接触孔和所述第三接触孔中填充有导电金属。2.如权利要求1所述的一种半导体器件结构,其特征在于,在所述半导体本体中与所述栅极金属层对应位置设置有第一沟槽,在所述半导体本体中与所述源极金属层对应位置设置有第二沟槽,所述第一沟槽和所述第二沟槽中填充有多晶硅。3.如权利要求2所述的一种半导体器件结构,其特征在于,所述第二接触孔设置在所述第一沟槽中,所述第一接触孔设置在所述介质层中或延伸至所述半导体本体中的外延层中,所述第三接触孔延伸至所述半导体本体中的外延层中。4.如权利要求3所述的一种半导体器件结构,其特征在于,所述第三接触孔底部与所述半导体本体接触的位置设置注入区。5.一种电子设备,其特征在于,包括如权利要求1至4任一项所述的一种半导体器件结构。

技术总结

本申请实施例提供了一种半导体器件结构及电子设备,包括,半导体器件本体,所述半导体器件本体上表面设置有介质层,在所述介质层上方对应位置间隔设置有栅极金属层与源极金属层,在所述介质层中与栅极金属层对应的位置至少设置一个第一接触孔和第二接触孔,在所述介质层中与源极金属层对应的位置至少设置一个第三接触孔,所述第一接触孔、所述第二接触孔和所述第三接触孔中填充有导电金属,本申请提供的技术方案可以降低半导体器件结构中的金属层与介质层分层的风险。属层与介质层分层的风险。属层与介质层分层的风险。

技术研发人员:诸舜杰 岳瑞芳 阮孟波

受保护的技术使用者:上海韦尔半导体股份有限公司

技术研发日:2021.02.27

技术公布日:2022/1/11

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1