叠片式压敏电阻的制作方法

1.本技术涉及压敏电阻技术领域,具体涉及一种叠片式压敏电阻。

背景技术:

2.压敏电阻一般适用于浪涌和瞬变防护的电路中,当电路中出现过电压或瞬态操作过电压达到压敏电阻的导通电压时,压敏电阻以纳秒级时长由高电阻变为低电阻,释放异常电压导致的瞬时过电流,同时把电压钳制在安全范围内以保护后级电路,从而使电路中的设备及元器件免遭过电压的冲击。当前,电子设备趋于小型化设计,有限的空间及材料性能限制了压敏电阻的尺寸,导致压敏电阻的电极个数受到了较大限制,压敏电阻的通流能力存在极限值,浪涌防护能力得到较大限制,被过电流导致烧毁甚至炸裂的风险较高。

技术实现要素:

3.本技术实施例提供一种叠片式压敏电阻,用于改善压敏电阻的通流能力以及浪涌防护能力。

4.本技术实施例提供的一种叠片式压敏电阻,包括第一盖板、第二盖板、引出电极、两个端电极、多个压敏电阻层和多个内电极,多个压敏电阻层和多个内电极设置于第一盖板和第二盖板之间,内电极和压敏电阻层沿第三方向依次交替层叠设置,引出电极与内电极一一连接,两个端电极分别位于叠片式压敏电阻沿第二方向的相对两侧,分别连接于相邻两个内电极的引出电极位于叠片式压敏电阻沿第二方向的相对两侧、并分别与两个端电极电连接;沿第一方向,引出电极的长度小于内电极的长度,第一方向、第二方向和第三方向两两垂直。

5.在一些实施例中,沿第一方向引出电极的长度为w1,沿第二方向内电极的长度为w0,w1<w0。

6.在一些实施例中,w1和w0满足:0.4*w0≤w1<1.0*w0。

7.在一些实施例中,沿第三方向,多个内电极的边缘对齐。

8.在一些实施例中,内电极与端电极之间的距离为h,相邻两个内电极之间的距离为d,h>d。

9.在一些实施例中,h和d满足:1.25*d≤h≤1.5*d。

10.在一些实施例中,沿第一方向,内电极与压敏电阻层的边缘最小距离为c,0.5*d≤c≤0.99*d。

11.在一些实施例中,第一盖板和第二盖板的厚度为g,1.1*d≤g≤1.3*d。

12.在一些实施例中,压敏电阻层的材料包括氧化锌、以及铋、钴、钛、镍、锰中至少一种的氧化物。

13.在一些实施例中,氧化锌的质量占比为α,85%≤α≤90%。

14.如上所述,本技术实施例的叠片式压敏电阻,分别连接于相邻两个内电极的引出电极位于叠片式压敏电阻的相对两侧、并分别与两个端电极电连接,沿第一方向引出电极

的长度小于内电极的长度,即内电极呈t型,内电极的相交面积较大,从而可以改善压敏电阻的通流能力以及浪涌防护能力,降低内电极之间以及内电极与端电极之间的被过电流击穿失效的概率,降低被过电流导致烧毁甚至炸裂的风险。

附图说明

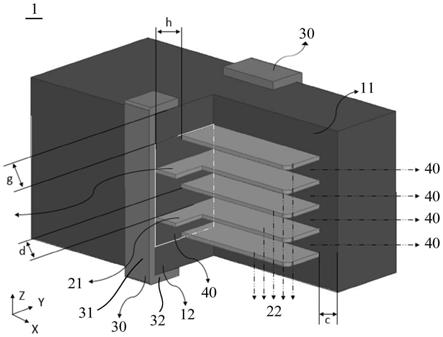

15.图1为本技术一实施例的叠片式压敏电阻的结构示意图;

16.图2为图1所示的叠片式压敏电阻的局部俯视图;

17.图3为现有技术的一种叠片式压敏电阻的局部俯视图。

具体实施方式

18.为使本技术的目的、技术方案和优点更加清楚,下面将结合具体实施例及相应的附图,对本技术的技术方案进行清楚地描述。显然,下文所描述实施例仅是本技术的一部分实施例,而非全部的实施例。在不冲突的情况下,下述各个实施例及其技术特征可相互组合,且亦属于本技术的技术方案。

19.应理解,在本技术实施例的描述中,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术相应实施例的技术方案和简化描述,而非指示或暗示装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

20.请一并参阅图1和图2,为本技术一实施例的叠片式压敏电阻的结构示意图。叠片式压敏电阻1包括:第一盖板11、第二盖板12、引出电极21、多个内电极22、两个端电极30和多个压敏电阻层40。

21.叠片式压敏电阻1的形状,本技术实施例不予以限定,例如可以为图1所示的长方体、或者矩形等类四方体,需要说明的是,图1所示的为一部分叠片式压敏电阻1,具体为长方体的叠片式压敏电阻1被去除一个顶角部分的结构,从而暴露叠片式压敏电阻1的内部元件。可选地,长方体可以为4532尺寸,即叠片式压敏电阻1(沿图1所示的第一方向x)的长度为4.5mm、宽度(沿图1所示的第二方向y)为3.2mm、高度(沿图1所示的第三方向z)为2.0mm;类四方体可以类似于2016尺寸,即叠片式压敏电阻1的长度为2.2mm、宽度为1.8mm、高度为1.85mm。第一方向x、第二方向y和第三方向z两两垂直,可视为三维直角坐标系的三条坐标轴。图2为叠片式压敏电阻1去除一个盖板(例如第一盖板11)后的结构俯视示意图,图2所示和图1所示的端电极30的形状不同,便于说明端电极30的可适应性设置。

22.多个压敏电阻层40和多个内电极22设置于第一盖板11和第二盖板12之间,内电极22和压敏电阻层40沿第三方向z依次交替层叠设置,例如,第二盖板12上设置第一个压敏电阻层40,第一个压敏电阻层40上设置第一个内电极22,第二个压敏电阻层40设置于第一个内电极22上,第二个内电极22设置于第二个压敏电阻层40上,依次类推。

23.压敏电阻层40可以为具有非线性特性的半导体材料构成,例如可以为采用多个流延的陶瓷膜片层叠而成的结构体,构成陶瓷膜片的主体成分可以为氧化锌(zno),并含有形成具有非线性特性的副成分铋(bi)、钴(co)、钛(ti)、镍(ni)、锰(mn)、铬(cr)、锑(sb)等至少一种的氧化物,例如bi2o3、co2o3、mno2、sb2o3、tio2、cr2o3、ni2o3等多种添加剂。在一些实施

例中,氧化锌的质量占比为α,85%≤α≤90%,有利于确保压敏电阻层40的非线性特性、以及使得电阻值对外加电压敏感变化的特性良好。

24.引出电极21的数量可以与内电极22的数量相等,引出电极21与内电极22一一对应连接。沿第一方向x,引出电极21的长度小于内电极22的长度,如图2所示,使得引出电极21和内电极22呈t型结构。在一实施例中,引出电极21与内电极22可以为一体成型结构,两者的导电材料相同,例如导电材料可由银、钯、铂、或者银钯、银铂合金组成。

25.分别连接于相邻两个内电极22的引出电极21位于叠片式压敏电阻1沿第二方向y的相对两侧、并分别与两个端电极30电连接,叠片式压敏电阻1可以通过两个端电极30电连接于相适应的电路中。

26.在本技术实施例的叠片式压敏电阻1中,引出电极21和内电极22呈t型结构,沿第二方向y内电极22的相交面积较大,从而可以改善叠片式压敏电阻1的通流能力以及浪涌防护能力,降低内电极22之间以及内电极22与端电极30之间的被过电流击穿失效的概率,降低被过电流导致烧毁甚至炸裂的风险。

27.在一些实施例中,沿第一方向x,引出电极21的长度为w1,沿第二方向y,内电极22的长度为w0,w1<w0。可选地,0.4*w0≤w1<1.0*w0。引出电极21的宽度较小,可以节省引出电极21的耗用量,节省成本。

28.在一些实施例中,沿第三方向z,多个内电极22的边缘对齐,以尽可能提高内电极22的相交面积。

29.在一些实施例中,内电极22与端电极30之间沿第二方向y的距离为h,即内电极22在宽度方向上的留边量、或者说引出电极21沿第二方向y的长度为h,相邻两个内电极22之间沿第三方向z的距离为d,h>d。可选地,h和d满足:1.25*d≤h≤1.5*d。留边量h大于相邻两个内电极22的间距,为了保障相邻两个内电极22所形成的电容,距离d通常较小,因此以距离d作为参照标准将留边量h控制在上述阈值范围内,不仅可以降低内电极22外露的风险以保护内电极22,而且可以使得留边量h较小,有利于叠片式压敏电阻1的小型化设计。同理,在一些实施例中,沿第一方向x,内电极22与压敏电阻层40的边缘最小距离为c,0.5*d≤c≤0.99*d。

30.第一盖板11和第二盖板12又可分别称为上盖板和下盖板,两者形成叠片式压敏电阻1的壳体,于此两者的形状与尺寸与叠片式压敏电阻1的形状与尺寸适应性设定,不仅可以限定叠片式压敏电阻1的外观,还可以保护叠片式压敏电阻1的内部结构元件,例如多个内电极22和压敏电阻层40。第一盖板11和第二盖板12(沿图1所示的第二方向y)的厚度可以相等,均为g,可选地,1.1*d≤g≤1.3*d,不仅可以保护内电极22和压敏电阻层40,而且可以使得壳体厚度较小,有利于叠片式压敏电阻1的小型化设计。

31.两个端电极30分别位于叠片式压敏电阻1沿第二方向y的相对两侧。可选地,两个端电极30可以固定于第一盖板11和第二盖板12的外表面,如图1所示,两个端电极30包括主体部31和两个定位部32,主体部31沿第三方向z延伸设置并固定于叠片式压敏电阻1的侧方,主体部31与内电极22之间的距离较小,引出电极21沿第二方向y的长度等于该距离,使得引出电极21长度较小;两个定位部32分别设置于主体部31沿第三方向z的相对两端,一个定位部32固定于第一盖板11上,另一个定位部32固定于第二盖板12上,端电极30呈门型,有利于增强与盖板之间的装配稳定性。

能力耐量(et)0.55j0.55j0.4j额定脉冲电流(ip)75a75a50a

43.表1

44.实施例3

45.叠片式压敏电阻1为4532尺寸的长方体,即,如图1和图2所示的长度为4.5mm、宽度为3.2mm、高度为2.0mm的叠片式压敏电阻1。

46.对比例2

47.对比例2为现有技术的一种叠片式压敏电阻,与实施例3的叠片式压敏电阻1的规格相同,均为4532尺寸的长方体。对比例1与实施例3的区别在于:如图3所示,内电极22和引出电极21的宽度w1相等,即,内电极22和引出电极21呈矩形,两个端电极30位于叠片式压敏电阻沿第一方向x的相对两侧。对比例2的叠片式压敏电阻中各个结构元件的尺寸,请参阅下表2所示。

[0048][0049][0050]

表2

[0051]

根据结果表明,对于相同尺寸规格的叠层片式压敏电阻,本技术可以增大单层内电极22的通流面积,从而提高总通流面积(总通流面积等于单层内电极22的通流面积与压敏电阻层40数量的乘积),以及浪涌防护能力;另外,引出电极21的尺寸较小,可以节省引出电极21的耗用量以节省成本。

[0052]

应理解,以上所述仅为本技术的部分实施例,并非因此限制本技术的专利范围,对于本领域普通技术人员而言,凡是利用本说明书及附图内容所作的等效结构变换,均同理包括在本技术的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1