一种封装体的制作方法

1.本技术涉及半导封装领域,特别涉及一种封装体。

背景技术:

2.在封装产品中,当同一个封装里面有多个芯片进行功能组合时候,由于连接的复杂,会导致同一个产品中需要使用多个铜桥或引线进行连接。

3.图1a、图1b和图1c分别为本领域中常见的包含多个芯片的三种封装产品。

4.在图1a所示的封装体1000中包含第一芯片1010和第二芯片1020,如图1a所示,所述第一芯片1010的顶面上设置所述第一芯片1010的栅极金属层1011和源极金属层1012,而所述第一芯片1010的底面,即,图1a中所述第一芯片1010贴附于引线框架1030的表面上设置所述第一芯片1010的漏极金属层。相似地,所述第二芯片1020的顶面上设置所述第二芯片1020的栅极金属层1021和源极金属层1022,而所述第二芯片1020的底面,即,图1a中所述第二芯片1020贴附于所述引线框架1030的表面上设置所述第二芯片1020的漏极金属层。

5.在如图1a所示的封装体1000中存在大量引线:(1)所述第一芯片1010的栅极金属层1011和所述第二芯片1020的栅极金属层1021均通过引线与所述引线框架1030的引脚电性连接;(2)所述第一芯片1010的漏极金属层通过所述引线框架1030及多条引线,与所述第二芯片1020的源极金属层1022电性连接;(3)所述第一芯片1010的源极金属层1012通过多条引线与所述引线框架1030电性连接。因此,在图1a中所述的封装体1000中存在引线密集的问题,同时,由于引线的阻抗高,致使所述封装体1000的总体电性能无法达到设计要求或者无法达到最佳。

6.如图1b所示的封装体1100中包含第一芯片1110、第二芯片1120和第三芯片1130。所述第一芯片1110的顶面上设置所述第一芯片1110的栅极金属层1111和源极金属层1112,而所述第一芯片1110的底面,即,图1b中所述第一芯片1110贴附于引线框架1140的表面上设置所述第一芯片1110的漏极金属层。相似地,所述第二芯片1120的顶面上设置所述第二芯片1120的栅极金属层1121和源极金属层1122,而所述第二芯片1120的底面,即,图1b中所述第二芯片1120贴附于所述引线框架1140的表面上设置所述第二芯片1120的漏极金属层。

7.如图1b所示,所述第一芯片1110的源极金属层1112与所述第二芯片1120的源极金属层1122通过一金属片1150电性连接,同时,所述第一芯片1110的栅极金属层1111也通过一金属片1150与所述引线框架1140电性连接。因此,在图1b所示的封装体1110中存在金属片1150数量较多的问题,增加了工艺难度、提高了制作成本,还有更高的良率损失风险。

8.如图1c所示的封装体1200中包含第一芯片1210、第二芯片1220和第三芯片1230。所述第一芯片1210的顶面上设置所述第一芯片1210的栅极金属层1211和源极金属层1212,而所述第一芯片1210的底面,即,图1c中所述第一芯片1210贴附于引线框架1240的表面上设置所述第一芯片1210的漏极金属层。相似地,所述第二芯片1220的顶面上设置所述第二芯片1220的栅极金属层1221和源极金属层1222,而所述第二芯片1220的底面,即,图1c中所述第二芯片1220贴附于所述引线框架1240的表面上设置所述第二芯片1220的漏极金属层。

9.如图1c所示,所述第二芯片1220的源极金属层1222通过一金属片1250及所述引线框架1240,与所述第一芯片1210的漏极金属层电性连接;所述第一芯片1210的源极金属层1212通过一金属片1250与所述引线框架1240电性连接;同时,所述第一芯片1210的栅极金属层1211也通过一金属片1250与所述引线框架1240的引脚电性连接。因此,在图1c所示的封装体1210中存在金属片1250数量较多的问题,增加了工艺难度、提高了制作成本,还有更高的良率损失风险。

10.因此,有必要提供一种新的封装体的结构,以克服上述缺陷。

技术实现要素:

11.本技术的目的在于提供一种新的封装体,通过结构设计以获得一种结构简化且总体电性能良好的封装体。

12.为了达到上述目的,根据本技术的一方面提供一种封装体,包括第一芯片和第二芯片;其中,所述第一芯片具有栅极金属层、源极金属层和漏极金属层;所述第二芯片具有栅极金属层、源极金属层和漏极金属层;所述第一芯片的栅极金属层与漏极金属层设置于所述第一芯片的同一表面;并且,所述第二芯片的栅极金属层与源极金属层设置于所述第二芯片的同一表面。

13.在一些实施例中,所述第一芯片的源极金属层及所述第一芯片的漏极金属层中的一者与所述第二芯片的源极金属层及所述第二芯片的漏极金属层中的一者通过一金属片电性连接。

14.在一些实施例中,所述金属片的表面上设有凸起面,其中,所述第一芯片的源极金属层及所述第一芯片的漏极金属层中的一者对应一个凸起面,并通过导电材料与该对应的凸起面贴合;以及,所述第二芯片的源极金属层及所述第二芯片的漏极金属层中的一者对应一个凸起面,并通过导电材料与该对应的凸起面贴合。

15.在一些实施例中,所述封装体还包括引线框架,所述引线框架具有相互独立的第一基岛、第二基岛和多个引脚的引线框架;其中,所述第一芯片的源极金属层及所述第一芯片的漏极金属层中的一者通过导电材料贴附于所述第一基岛上;并且,所述第二芯片的源极金属层及所述第二芯片的漏极金属层中的一者通过导电材料贴附于所述第二基岛上。

16.在一些实施例中,所述第一芯片的栅极金属层通过导电材料贴附于一引脚上,或者,所述第一芯片的栅极金属层通过一引线与一引脚电性连接。

17.在一些实施例中,所述第二芯片的栅极金属层通过导电材料贴附于一引脚上,或者,所述第二芯片的栅极金属层通过一引线与一引脚电性连接。

18.在一些实施例中,所述封装体还包括:独立的第三基岛,以及设置于所述第三基岛上的第三芯片。

19.在一些实施例中,所述第三芯片具有至少一焊盘通过一引线与一引脚电性连接。

20.在一些实施例中,所述封装体还包括塑封所述引线框架、第一芯片、第二芯片、金属片、引脚及引线的塑封层。

21.在本技术构建的封装体中,通过芯片的电极互换,将需要电性连接的芯片的电极金属层设置于各自芯片的同一侧表面,同时在必要时结合芯片倒装结构,实现封装体内设置金属片数量的最小化。

附图说明

22.为了更清楚地阐述本技术专利的具体实施例的特点,下面将对实施例的附图进行简要介绍。显而易见地,下面描述的附图仅为本技术的一些实施例,对于本领域的普通研究或从业人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他类似的图片。

23.图1a至图1c分别为现有技术中的三种常规封装产品的结构示意图;

24.图2是根据本技术一实施例构建的封装体1的结构示意图;

25.图3a和图3b为图2中所述封装体1的第一芯片的结构示意图;图3c和图3d为图2中所述封装体1的第二芯片的结构示意图;

26.图4a为图2中a-a’处剖视图;图4b为图2中b-b’处剖视图;

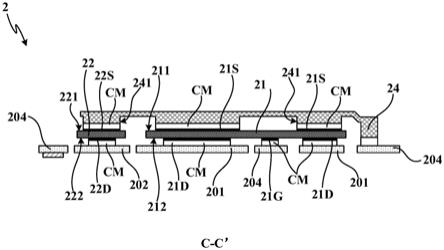

27.图5a为根据本技术另一实施例构建的封装体2的结构示意图;图5b为图5a中c-c’28.处剖视图;以及

29.图6a为根据本技术再一实施例构建的封装体3的结构示意图;图6b为图6a中d-d’30.处剖视图。

具体实施方式

31.下面结合具体实施例,进一步阐述本技术。显然,所描述的实施例仅为本技术的一部分应用,而并非全部。应理解,这些实施例仅用于说明本技术的特性而并非用于限制本技术的范围。本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术的保护范围。

32.在本技术构建的封装体中,通过芯片的电极互换,将需要电性连接的芯片的电极金属层设置于各自芯片的同一侧表面,同时在必要时结合芯片倒装结构,实现封装体内设置金属片数量的最小化。因此,本领域技术人员可以理解的是,本技术构建的封装体结构可以适用于包含至少两个需要电性连接的芯片的任意类型的封装体,而非仅限制于本技术说明书附图中记载的具体封装体。

33.实施例1.封装体1

34.图2描述了根据本技术一具体实施例构建的封装体1。

35.如图2所示,所述封装体1包括引线框架10、第一芯片11、第二芯片12,以及下文中将详细描述的用于电性连接所述第一芯片11及所述第二芯片12的金属片13。所述引线框架10具有相互独立的第一基岛101和第二基岛102,以及多个引脚103。所述第一芯片11设置于所述第一基岛101上,所述第二芯片12设置于所述第二基岛102上。

36.定义所述第一芯片11背离所述第一基岛101的一侧表面为第一芯片11的第一表面111,所述第一芯片11朝向所述第一基岛101的一侧表面为第一芯片11的第二表面112。相似地,定义所述第二芯片12背离所述第二基岛102的一侧表面为第二芯片12的第一表面121,所述第二芯片12朝向所述第二基岛102的一侧表面为第二芯片12的第二表面122。因此,如图2中绘示出所述第一芯片11的第一表面111和所述第二芯片12的第一表面121。

37.以下结合图3a至图3d详细描述所述第一芯片11和第二芯片12的表面电极设置,并结合图4a和图4b详细描述本实施例所述封装体1的连接结构。

38.如图3a和图4a所示,在所述第一芯片11背离所述第一基岛101的第一表面111上设

置所述第一芯片11的源极金属层11s;同时,如图3b和图4a所示,在所述第一芯片11朝向所述第一基岛101的第二表面112上设置所述第一芯片11的漏极金属层11d和所述第一芯片11的栅极金属层11g。即,所述第一芯片11的栅极金属层11g与漏极金属层11d设置于所述第一芯片11的同一表面(朝向图2中所示第一基岛101的第二表面112)。

39.由此,在本实施例构建的封装体1中,将所述第一芯片11设置于所述第一基岛101上时,如图3b和图4a所示,所述第一芯片11的漏极金属层11d通过导电材料cm贴附于所述第一基岛101上,所述第一芯片11的栅极金属层11g通过导电材料cm贴附于一引脚103上。而如图3a和图4a所示,所述第一芯片11的源极金属层11s则通过导电材料cm与所述金属片13连接。优选地,如图4a所示,所述金属片13在对应所述第一芯片11的源极金属层11s设有一凸起面131,所述第一芯片11的源极金属层11s通过导电材料与所述金属片13的凸起面131贴合。

40.如图3c所示和图4b所示,在所述第二芯片12背离所述第二基岛102的第一表面121上设置所述第二芯片12的漏极金属层12d;同时,如图3d和图4b所示,在所述第二芯片12朝向所述第二基岛102的第二表面122上设置所述第二芯片12的栅极金属层12g和源极金属层12s。即,所述第二芯片12的栅极金属层12g与和源极金属层12s设置于所述第二芯片12的同一表面(朝向图2中所示第二基岛102的第二表面122)。

41.由此,在本实施例构建的封装体1中,将所述第二芯片12设置于所述第二基岛102上时,如图3d和图4b所示,所述第二芯片12的源极金属层12s通过导电材料cm贴附于所述第二基岛102上,所述第二芯片12的栅极金属层12g通过导电材料cm贴附于一引脚103上。而如图3c和图4b所示,所述第二芯片12的漏极金属层12d则通过导电材料cm与所述金属片13连接。优选地,如图4b所示,所述金属片13在对应所述第二芯片12的漏极金属层12d设有一凸起面131,所述第二芯片12的漏极金属层12d通过导电材料与所述金属片13的凸起面131贴合。

42.如上所示,在本实施例构建的封装体1中,所述第一芯片11的源极金属层11s与第二芯片12的漏极金属层12d通过金属片13电性连接,并且,所述第一芯片11的栅极金属层11g及所述第二芯片12的栅极金属层12g分别通过导电材料cm直接贴附于一引脚103上。与图1a所示的同类产品相比,本实施例构建的封装体1不包含用于电性连接两芯片的电极金属层的多引线结构,以及用于电性连接芯片与引线框架的引脚的引线,因而本实施例构建的所述封装体1没有引线密集的问题,也同时解决了引线阻抗高的问题,使得封装体的总体电性能得到提升。

43.实施例2.封装体2

44.图5a和图5b描述了根据本技术另一具体实施例构建的封装体2。

45.如图5a所示,所述封装体2包括引线框架20、第一芯片21、第二芯片22、第三芯片23,以及下文中将详细描述的用于电性连接所述第一芯片21及所述第二芯片22的金属片24。所述引线框架20具有相互独立的第一基岛201、第二基岛202及第三基岛203,以及多个引脚204。所述第一芯片21设置于所述第一基岛201上,所述第二芯片22设置于所述第二基岛202上,所述第三芯片23设置于所述第三基岛203上。

46.如图5a所示,所述第三芯片23具有多个焊盘231,所述焊盘231通过一引线l与一引脚204电性连接。当然,本领域技术人员可以理解的是,所述第三芯片23的部分焊盘231可以

通过引线l与所述第一芯片21和/或所述第二芯片22的电性连接。例如,在本实施例中,如图5a所示,所述第三芯片23的部分焊盘231通过引线l与所述第二芯片22电性连接。

47.与封装体1相似地,如图5b所示,定义所述第一芯片21背离所述第一基岛201的一侧表面为第一芯片21的第一表面211,所述第一芯片21朝向所述第一基岛201的一侧表面为第一芯片21的第二表面212。相似地,定义所述第二芯片22背离所述第二基岛202的一侧表面为第二芯片22的第一表面221,所述第二芯片22朝向所述第二基岛202的一侧表面为第二芯片22的第二表面222。因此,图5a所示为所述第二芯片22的第一表面221及所述第一芯片21的第一表面(图5a中未示)。

48.与实施例1中第一芯片11相似地,在本实施例中,如图5b所示,在所述第一芯片21背离所述第一基岛201的第一表面211上设置所述第一芯片21的源极金属层21s;而在所述第一芯片22朝向所述第一基岛201的第二表面212上设置所述第一芯片21的栅极金属层21g和漏极金属层21d。即,在本实施例中,所述第一芯片21的栅极金属层21g与漏极金属层21d设置于所述第一芯片21的同一表面(图5b中朝向所述第一基岛201的第二表面212)。

49.如图5a和图5b所示,在本实施例中,在所述第二芯片22背离所述第二基岛202一侧的第一表面221上设置所述第二芯片22的源极金属层22s和第二芯片22的栅极金属层22g;而在所述第二芯片22朝向所述第二基岛202的第二表面222上设置所述第二芯片22的漏极金属层22d。即,在本实施例中,所述第二芯片22的栅极金属层22g与源极金属层22s设置于所述第二芯片22的同一表面(图5a和图5b中所述第二芯片22背离所述第二基岛202一侧的第一表面221)。

50.由此,在本实施例构建的封装体2中,如图5b所示,将所述第一芯片21设置于所述第一基岛201上时,所述第一芯片21的漏极金属层21d通过导电材料cm贴附于所述第一基岛201上,所述第一芯片21的栅极金属层21g通过导电材料cm贴附于一引脚204上。而将所述第二芯片22设置于所述第二基岛202上时,如图5b所示,所述第二芯片22的漏极金属层22d通过导电材料cm贴附于所述第二基岛202上,所述第二芯片22的源极金属层22s通过所述金属片24与所述第一芯片21的源极金属层21s电性连接。而所述第二芯片22的栅极金属层22g则通过引线l与一引脚204连接。

51.与实施例1相似地,优选地,所述金属片24对应所述第一芯片21的源极金属层21s和对应所述第二芯片22的源极金属层22分别设有凸起面241,所述第一芯片21的源极金属层21s及所述第二芯片22的源极金属层22s分别通过导电材料cm与所述金属片24的凸起面241贴合,如图5b所示。

52.与图1b所示的本领域的同类产品相比,本实施例构建的封装体2中通过将所述第一芯片21的栅极金属层21g直接与所述引线框架20的引脚204贴合,以省略连接所述第一芯片的栅极金属层21g与所述引线框架20的引脚204的单独引线或单独金属片,以降低产品设计难度。同时,与图1b所示的本领域的同类产品相比,本实施例构建的封装体2通过将所述第一芯片21的漏极金属层21d与栅极金属层21g设置于所述第一芯片21的同一表面,以在满足所述第一芯片的栅极金属层21g直接贴附所述引脚204的同时,以一片所述金属片24电性连接所述第一芯片21的源极金属层21s和第二芯片22的源极金属层22s,以减少产品的金属片24的数量和设计难度。

53.实施例3.封装体3

54.图6a和图6b描述了根据本技术另一具体实施例构建的封装体3。

55.如图6a所示,所述封装体3包括引线框架30、第一芯片31、第二芯片32、第三芯片33,以及下文中将详细描述的用于电性连接所述第一芯片31及所述第二芯片32的金属片34。所述引线框架30具有相互独立的第一基岛301、第二基岛302及第三基岛303,以及多个引脚304。所述第一芯片31设置于所述第一基岛301上,所述第二芯片32设置于所述第二基岛302上,所述第三芯片33设置于所述第三基岛303上。

56.如图6a所示,所述第三芯片33具有多个焊盘331,所述焊盘331通过一引线l与一引脚304电性连接。当然,本领域技术人员可以理解的是,所述第三芯片33的部分焊盘331可以通过引线l与所述第一芯片31和/或所述第二芯片32的电性连接。例如,在本实施例中,如图6a所示,所述第三芯片33的部分焊盘331通过引线l与所述第二芯片32电性连接。

57.与封装体1相似地,如图6b所示,定义所述第一芯片31背离所述第一基岛301的一侧表面为第一芯片31的第一表面311,所述第一芯片31朝向所述第一基岛301的一侧表面为第一芯片31的第二表面312。相似地,定义所述第二芯片32背离所述第二基岛302的一侧表面为第二芯片32的第一表面321,所述第二芯片32朝向所述第二基岛302的一侧表面为第二芯片32的第二表面322。因此,图6a所示为所述第二芯片32的第一表面321及所述第一芯片31的第一表面311。

58.在本实施例中,如图6a和图6b所示,在所述第一芯片31背离所述第一基岛301的第一表面311上设置所述第一芯片31的漏极金属层31d和栅极金属层31g;而在所述第一芯片32朝向所述第一基岛301的第二表面312上设置所述第一芯片31的源极金属层31s。即,在本实施例中,所述第一芯片31的栅极金属层31g与漏极金属层31d设置于所述第一芯片31的同一表面(图6a和图6b中所述第一芯片31背离所述第一基岛301一侧的第一表面311)。

59.如图6a和图6b所示,在本实施例中,在所述第二芯片32背离所述第二基岛302的第一表面321上设置所述第二芯片32的源极金属层32s和第二芯片32的栅极金属层32g;而在所述第二芯片32朝向所述第二基岛302的第二表面322上设置所述第二芯片32的漏极金属层32d。即,在本实施例中,所述第二芯片32的栅极金属层32g与源极金属层32s设置于所述第二芯片32的同一表面(图6a和图6b中所述第二芯片32背离所述第二基岛302的第一表面321)。

60.由此,在本实施例构建的封装体3中,如图6b所示,将所述第一芯片31设置于所述第一基岛301上时,所述第一芯片31的源极金属层31s通过导电材料cm贴附于所述第一基岛301上;同时,如图6a所示,所述第一芯片31的栅极金属层31g通过一引线与一引脚304电性连接。将所述第二芯片32设置于所述第二基岛302上时,如图6b所示,所述第二芯片32的漏极金属层22d通过导电材料cm贴附于所述第二基岛302上;同时,如图6a所示,所述第二芯片32的栅极金属层32g则通过引线l与一引脚304连接。

61.与实施例2中所述封装体2不同的是,在本实施例中构建的封装体3中,如图6b所示,所述第一芯片31的漏极金属层31d通过一金属片34与所述第二芯片32的源极金属层32s电性连接。

62.优选地,所述金属片34对应所述第一芯片31的漏极金属层31d和对应所述第二芯片32的源极金属层32分别设有凸起面341,所述第一芯片31的漏极金属层31d及所述第二芯片32的源极金属层32s分别通过导电材料cm与所述金属片34的凸起面341贴合,如图6b所

示。

63.因此,在本实施例构建的封装体3中,通过将所述第一芯片31的漏极金属层31d与栅极金属层31g设置于所述第一芯片31的同一表面,使得以一片金属片34即可以实现所述第一芯片31的漏极金属层31d与第二芯片32的源极金属层32d的电性连接,并实现所述第一芯片31的源极金属层31s及所述第二芯片32的源极金属层32s同时接地。与图1c所示的同类产品相比,本实施例构建的封装体3中,显然金属片34的数量明显下降,以简化金属片的结构设计并降低封装体的制造成本和工艺难度。

64.综上几个实施例,本领域技术人员可以清晰地知晓,本技术所述封装体的结构尤其适用于需要电性连接不同芯片的电极金属层的封装产品,而不仅限于附图所示的实施例。

65.此外,本领域技术人员可以理解的是,为了图式清晰的目的,在本技术附图中未在封装体1、封装体2和封装体3中示意出塑封层,然而本技术所述封装体包含塑封第一芯片、第二芯片、第三芯片、引线框架、引线及金属片以形成封装体的塑封层。

66.本技术已由上述相关实施例加以描述,然而上述实施例仅为实施本技术的范例。必需指出的是,已公开的实施例并未限制本技术的范围。相反地,包含于权利要求书的精神及范围的修改及均等设置均包括于本技术的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1