具有芯片插针式柱凸块的集成电路的制作方法

1.本实用新型涉及芯片制造技术领域,尤其是指一种具有芯片插针式柱凸块的集成电路。

背景技术:

2.芯片上都会设置针脚用于芯片和电路板连接。传统的针脚形成需要经初始结构

→

金属层溅射

→

涂胶

→

显影

→

铜凸电镀

→

去胶

→

金属层蚀刻

→

回流的流程。传统芯片制造中将针脚焊接在芯片的引脚或端子上,这种针脚和芯片的连接方式需要经过多个工序,工艺成本高昂,技术难度大。

技术实现要素:

3.有鉴于此,本实用新型针对现有技术存在之缺失,其主要目的是提供一种具有芯片插针式柱凸块的集成电路,其铜针脚与芯片的连接简单,所需工序较少,从而克服现有技术的不足。

4.为实现上述目的,本实用新型采用如下之技术方案:

5.本技术提供一种具有芯片插针式柱凸块的集成电路,包括

6.集成电路:有多层叠层结构,每层叠层结构均有引脚,引脚通过引出导体引至集成电路之底面暴露;

7.插针式柱凸块:叠置于所述集成电路之底层,所述插针式柱凸块包括基板和铜针脚,所述基板上采用阵列的方式设置有若干的安装孔;所述铜针脚插装于所述安装孔,且与安装孔过盈配合;所述铜针脚直径在0.12-0.2mm之间;相邻两铜针脚之间的针距在0.24-0.4之间;各铜针脚与所述引出导体电性连接;

8.封装体:封装体将所述集成电路和插针式柱凸块封装。

9.优选的,所述基板的长度l1介于3-12mm之间,所述基板的宽度w1介于2-10mm之间,所述基板的厚度t1介于0.2-0.35mm之间。

10.优选的,所述安装孔采用格栅阵列的方式排列。

11.优选的,铜针脚的总长度l2介0.4-0.6mm之间;其中铜针脚的一端从基板凸出的长度l3介于0.1-0.2mm,铜针脚的另外一端从基板凸出的长度l4介于0.03-0.1mm之间。

12.优选的,所述铜针脚的一端向另一端逐渐变小。

13.优选的,所述铜针脚的其中一端为尖头,铜针脚的另一端为连接面。

14.优选的,所述封装体之间设置有绝缘层。

15.优选的,所述封装体为塑封层。

16.一种具有芯片插针式柱凸块的集成电路,以插针式柱凸块作为电极引脚,所述插针式柱凸块包括基板和铜针脚,所述基板上采用阵列的方式设置有若干的安装孔;所述铜针脚插装于所述安装孔,且与安装孔过盈配合;所述铜针脚直径在0.12-0.2mm之间;相邻两铜针脚之间的针距在0.24-0.4之间。

17.本实用新型与现有技术相比具有明显的优点和有益效果,具体而言,由上述技术方案可知,所述具有芯片插针式柱凸块的集成电路包括基板、封装体、集成电路芯片、铜针脚。封装体内设置集成电路芯片。多层封装体之间采用叠层的方式设置。引出导体一端连接集成电路芯片的引脚,然后引出导体的另一端在最底层所述封装体的底面暴露。铜针脚插在基板,然后基板与最底层的封装体结合在一起使得铜针脚与引出导体连接,从而将铜针脚和集成电路芯片连接在一起,使得铜针脚的连接工艺变得简单,降低了成本。

18.尤其是:铜针脚的直径在0.12-0.2mm之间;相邻两铜针脚之间的针距在0.24-0.4之间。由于铜针脚的尺寸都非常小,且针距也非常窄,因此在一块小尺寸的基板上可以插很多铜针脚。又因为这种密集的小尺寸结构,使之能很好的适应芯片的尺寸结构。

19.又因为铜针脚采用过盈配合的方式装配在基板,铜针脚的一端向另一端逐渐变小,使得基板和最底层的封装体结合在一起的时候铜针脚能与引出导体连接紧密,且不容易松动。

20.为更清楚地阐述本实用新型的结构特征和功效,下面结合附图与具体实施例来对本实用新型进行详细说明。

附图说明

21.图1是本实用新型之实施例的基板示意图。

22.图2是本实用新型之实施例的基板和铜针脚组合示意图。

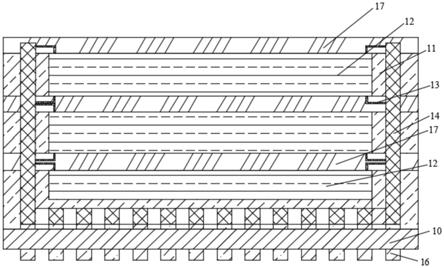

23.图3是本实用新型之实施例的剖面示意图。

24.附图标识说明:

25.10、基板

ꢀꢀꢀꢀ

11、封装体

ꢀꢀꢀꢀ

12、集成电路芯片

26.13、引脚

ꢀꢀꢀꢀ

14、引出导体

ꢀꢀ

15、安装孔

27.16、铜针脚

ꢀꢀ

17、绝缘层

ꢀꢀꢀꢀ

18、长边

28.19、宽边。

具体实施方式

29.请参照图1至图3所示,其显示出了本实用新型之较佳实施例的具体结构,是一种具有芯片插针式柱凸块的集成电路。

30.其中,基板10插有铜针脚16。基板10与封装体11封装在一起,使得铜针脚16与引出导体14连接在一起,替代了传统的针脚连接工艺,使得铜针脚16与集成电路芯片12的连接工艺变得简单,降低了成本。

31.本技术提供一种具有芯片插针式柱凸块的集成电路,包括基板10和至少一层封装体11;所述封装体11采用叠层的方式设置,且每层所述封装体11内设置有集成电路芯片12;所述集成电路芯片12上设置有引脚13;引出导体14一端连接所述引脚13,所述引出导体14的另一端在最底层所述封装体11的底面暴露;所述基板10上采用阵列的方式设置有若干的安装孔15;铜针脚16过盈配合地设置在所述安装孔15之中,且所述铜针脚16的两端分别从基板10上凸出;所述基板10与最底层的所述封装体11封装在一起,使得铜针脚16的一端与引出导体14连接在一起。优选的,所述基板10为pa46材料制作的配件。pa46(聚己二酰丁二胺)是一种具有高熔点和高结晶度的新型聚酰胺树脂,很适合集成电路芯片12的高温使用

环境。集成电路芯片12设置在封装体11内。优选的,所述封装体11为塑封层,塑封装为可研磨的、绝缘的、便于打磨的塑料。封装体11之间设置有绝缘层17,可以提高封装体11之间的绝缘性。其中,绝缘层17的材料优选为环氧树脂。底层的封装体11上设置有凹槽,凹槽放置集成电路芯片12的放置。底层集成电路芯片12的上表面上设置有引脚13,其他层的集成电路芯片12上的顶面和底面都可以设置引脚13。引脚13连接在对应的引出导体14上。引出导体14的下端在可以贴合在底层的封装体11的底面上,也可以是引出导体14一体成型在封装体11,然后通过打磨而露出连接位置。封装体11之间在堆叠的时候集成电路芯片12连接对应的引出导体14上端。所述基板10与最底层的所述封装体11封装在一起,使得铜针脚16的一端与引出导体14的下端连接在一起。其中,铜针脚16凸出基板10的较短一端连接引出导体14,铜针脚16凸出基板10的较长一端则用于插在电路板上。基板10和最底层的所述封装体11可以采用胶水封装、也可以采用热封装。基板10和最底层的所述封装体11封装的时候,由于铜针脚16凸出基板10一定的长度,因此可以借助基板10弹性形变而产生的弹力使得铜针脚16和引出导体14连接得更加紧密。

32.优选的,所述基板10的长度l1介于3-12mm之间,所述基板10的宽度w1介于2-10mm之间,所述基板10的厚度t1介于0.2-0.35mm之间。优选的,所述安装孔15采用格栅阵列的方式排列。优选的,所述安装孔15中心之间的横向孔距s1和纵向孔距s2均介于0.38mm至0.42mm之间。优选的,铜针脚16的总长度l2介0.4-0.6mm之间;其中铜针脚16的一端从基板10凸出的长度l3介于0.1-0.2mm,铜针脚16的另外一端从基板10凸出的长度l4介于0.03-0.1mm之间。优选的,所述基板10为矩形,所述基板10的长边18到相邻安装孔15的距离s4介于0.10mm-0.12mm之间,所述基板10的宽边19到相邻安装孔15的距离s3的距离介于0.247mm-0.253mm之间。基板10和铜针脚16的尺寸都较小,适合芯片的尺寸结构。此外,安装孔15之间的间距也很小,可以排布很多的铜针脚16。铜针脚16是采用过盈配合的工艺插在基板10上的,因此基板10会给铜针脚16提供一定的摩擦力,从而保证铜针脚16不会松动。铜针脚16插在基板10后基板10和芯片封装在一起。封装后,铜针脚16在基板10凸出较短的一端与芯片连接,铜针脚16在基板10凸出较长的一端则作为针脚插在电路板上。铜针脚16和基板10都是预制的,能提高生产的效率,同时避免了复杂的工艺降低了生产成本。铜针脚16在基板10的数量和铜针脚16在基板10上的位置也可以根据需要设置,调整起来也非常的方便。此外,铜针脚16到基板10边缘还留有保护距离,避免了安装孔15影响基板10的强度。铜针脚16尺寸稳定可以控制住0.01mm的误差。基板10耐磨疲劳测试稳定。铜针脚16的尺寸更小,且铜针脚16两端的凸出长度可以自由调整,灵活设置,稳定性能控制在0.01mm以内。基板和铜针脚都是可以预制的,减少了工序,能降低成本。此外,铜针脚的数量以及铜针脚在基板上的位置都是可以根据需要灵活布置的,还可减少针脚损坏的问题并可增加脚位。

33.进一步的,所述基板10上设置有至少一列安装孔15。优选的,所述安装孔15采用格栅阵列的方式排列。安装孔15可以设置多排或者多列,具体根据使用环境设置。格栅阵列是一种集成电路的表面安装技术。其特点在于其铜针脚16是位于基板10上而非集成电路上。与传统针脚在集成电路上的封装方式相比,可减少针脚损坏的问题并可增加脚位。进一步的,所述铜针脚16的其中一端为尖头,铜针脚16的另一端为连接面。尖头方便插在电路板上。连接面设置为平面有利于让铜针脚16与引出导体14保持良好的接触,保证封装质量。

34.优选的,所述铜针脚16的一端向另一端逐渐变小。进一步的,所述铜针脚16的其中

一端为尖头,铜针脚16的另一端为连接面。尖头方便插在电路板上。连接面设置为平面有利于让铜针脚16与芯片保持良好的接触,保证封装质量。

35.综上所述,本实用新型的设计重点在于,其引出导体14一端连接集成电路芯片12的引脚13,然后引出导体14的另一端在最底层所述封装体11的底面暴露。基板10与最底层的封装体11结合在一起使得铜针脚16与引出导体14连接,从而将铜针脚16和集成电路芯片12连接在一起,使得铜针脚16的连接工艺变得简单,降低了成本。

36.以上所述,仅是本实用新型的较佳实施例而已,并非对本实用新型的技术范围作任何限制,故凡是依据本实用新型的技术实质对以上实施例所作的任何细微修改、等同变化与修饰,均仍属于本实用新型技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1