一种TVS二极管的制作方法

一种tvs二极管

技术领域

1.本实用新型涉及半导体领域,尤其涉及一种tvs二极管。

背景技术:

2.随着半导体技术的发展,电子器件的工作电压不断降低,但是电路中以静电放电(esd)以及其他一些电压浪涌形式存在的瞬态电压的存在会对电子器件的正常工作产生冲击,严重的甚至会导致器件烧毁失效,因此保护电路显得越来越重要,瞬态电压抑制器(transient voltage suppressor)简称tvs,就是一种基于二极管形式的保护器件用来保护电路中的器件不受各种形式的瞬态高压的冲击。

3.tvs二极管是专门为保护电子器件免受瞬态电压破坏性影响所设计的固态pn结半导体电子器件。瞬态保护电路的电特性取决于pn结面积,掺杂浓度,衬底电阻等因素。tvs二极管作为并行的保护器件。在正常工作条件下,tvs二极管在被保护的电路上呈现高阻抗状态。理想情况下是呈现开路状态,虽有少量的漏电流存在。当过冲电压超过保护电路的正常工作电压时,tvs二极管在pn结的雪崩击穿效应为瞬态电流提供一个低阻抗路径。因此,瞬态电流被分流通过并联的tvs二极管,从而起到对电子器件的保护作用。作为一个钳位元器件,tvs二极管能有效抑制住所有超过自身雪崩击穿电压(钳位电压)的外来瞬态过冲电压。瞬态过冲威胁过去后,tvs器件会自动复位到高阻抗状态。

4.tvs二极管的一个主要优势是它的反应时间。理论上雪崩击穿发生在皮秒。因此,tvs二极管通常指为响应“几乎是在瞬间”。另一个与钳位电压密切相关的参数是在瞬态电压抑制器件的工作电压。工作电压,有时也被称为反向隔离电压(vrwm),低于该电压使tvs器件呈现高阻抗状态,在电路版图上几乎是“透明”的。当线路电压超过工作电压,也就是当瞬态电压经过时,tvs二极管的保护作用开始启动“钳位”电压尖峰。工作电压不能与钳位电压相混淆,它是处在一个高阻抗状态和低阻抗分流状态之间的拐点。

5.保护器件工作电压的高低决定了是否能快速的响应瞬态效应的能力,因此,具有一个较低的工作电压及钳位电压对保护器件来说至关重要。现有的tvs二极管响应时间长、钳位电压较高且可靠性不足。因此,现有技术还有待于改进和发展。

技术实现要素:

6.本实用新型所要解决的技术问题是提供一种tvs二极管,解决现有的tvs二极管响应时间长且可靠性不足的问题。

7.本实用新型为解决上述技术问题而采用的技术方案是提供一种tvs二极管,包括二极管本体,所述二极管本体包括半导体衬底,所述半导体衬底上形成有多个第一p阱,多个所述第一p阱纵向排列,每个所述第一p阱中设置有多个n+注入区,在两个相邻的所述n+注入区之间设置有p+注入区;在多个所述第一p阱的一侧形成有多个横向排列的n阱,相邻的两个n阱之间设置有第二p阱,多个所述第二p阱与n阱中设置有多个n+注入区和p+注入区,所述p+注入区设置在相邻的所述n+注入区之间;每个所述第一p阱由深槽单独包围分

隔,多个所述n阱和第二p阱一同由深槽包围分隔;所述半导体衬底上形成有接触孔,所述接触孔表面金属淀积形成金属层,所述金属层并联连接多个p+注入区形成正极,所述金属层并联多个n+注入区形成负极。

8.进一步地,所述第一p阱呈矩形,所述第一p阱数目为四个,四个所述第一p阱沿宽度方向对齐纵向排列;每个所述第一p阱中设置的n+注入区数目为七个,七个所述n+注入区之间间隔设置有六个p+注入区,所述n+注入区和p+注入区沿第一p阱的长度方向纵向排列。

9.进一步地,所述第二p阱与n阱为形状且尺寸相同的长条形,所述n阱数目为四个,四个所述n阱之间间隔设置有三个第二p阱;所述第二p阱与n阱中一共设置有十个n+注入区和九个p+注入区,九个所述p+注入区与十个所述n+注入区间隔设置。

10.进一步地,位于边缘位置的所述n阱设置有一个n+注入区和一个p+注入区,位于中间位置的所述n阱依次设置有一个n+注入区、一个p+注入区和一个n+注入区或者依次设置有一个p+注入区、一个n+注入区和一个p+注入区,所述第二p阱依次设置有一个n+注入区、一个p+注入区和一个n+注入区或者依次设置有一个p+注入区、一个n+注入区和一个p+注入区,使得九个所述p+注入区间隔设置在相邻的十个所述n+注入区之间。

11.进一步地,所述第一p阱和第二p阱具有浓度差。

12.进一步地,所述金属层上方形成有钝化层,所述金属层的材质为铝,所述金属层的厚度为4um。

13.进一步地,所述半导体衬底为p型衬底。

14.进一步地,所述二极管本体的正向导通电压为0.9v,所述二极管本体在5v 工作电压下的反向漏电小于10na,所述二极管本体在1ma 电流下的击穿电压为7v。

15.本实用新型对比现有技术有如下的有益效果:本实用新型提供的tvs二极管,在半导体衬底上注入有一定的浓度差的p型杂质形成第一p阱和第二p阱,注入n型杂质形成n阱;再注入浓度较高的n型杂质形成n+注入区,浓度较高的p型杂质形成p+注入区,减少响应时间,提高可靠性,并在采用p 型衬底,电阻率小,得到较小的tvs 串连电阻从而降低钳位电压。

附图说明

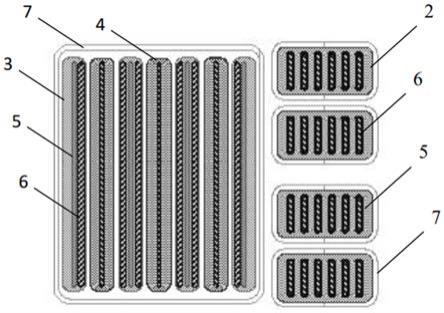

16.图1为本实用新型实施例的tvs二极管的结构示意图;

17.图2为本实用新型实施例的二极管本体有源区示意图;

18.图3为本实用新型实施例的第一p阱示意图;

19.图4为本实用新型实施例的第二p阱示意图;

20.图5为本实用新型实施例的n阱示意图;

21.图6为本实用新型实施例的n+注入区示意图;

22.图7为本实用新型实施例的p+注入区示意图;

23.图8为本实用新型实施例的金属层示意图;

24.图9为本实用新型实施例的钝化层示意图;

25.图10为本实用新型实施例的tvs二极管峰值电流测试曲线;

26.图11为本实用新型实施例的tvs二极管不同偏置电压下的电容曲线。

27.图中:

28.1、半导体衬底;2、第一p阱;3、n阱;4、第二p阱;5、n+注入区;6、p+注入区;7、深槽;8、金属层;9、钝化层。

具体实施方式

29.下面结合附图和实施例对本实用新型作进一步的描述。

30.图1为本实用新型实施例的tvs二极管结构示意图;图2为本实用新型实施例的二极管本体有源区示意图。

31.请参见图1和图2,本实用新型实施例的tvs二极管,包括二极管本体,二极管本体包括半导体衬底1,半导体衬底1上形成有多个第一p阱2,多个第一p阱2纵向排列,每个第一p阱2中设置有多个n+注入区5,在两个相邻的n+注入区5之间设置有p+注入区6;在多个第一p阱2的一侧形成有多个横向排列的n阱3,相邻的两个n阱3之间设置有第二p阱4,多个第二p阱4与n阱3中设置有多个n+注入区5和p+注入区6,p+注入区6设置在相邻的n+注入区5之间;每个第一p阱2由深槽7单独包围分隔,多个n阱3和第二p阱4一同由深槽7包围分隔。

32.请同时参见图2-图7,本实用新型实施例的tvs二极管,第一p阱2呈矩形,第一p阱2数目为四个,四个第一p阱2沿宽度方向对齐纵向排列;每个第一p阱2中设置的n+注入区5数目为七个,七个n+注入区5之间间隔设置有六个p+注入区6,n+注入区5和p+注入区6沿第一p阱2的长度方向纵向排列。

33.请继续参见图2-图7,本实用新型实施例的tvs二极管,第二p阱4与n阱3为形状且尺寸相同的长条形,n阱3数目为四个,四个n阱3之间间隔设置有三个第二p阱4;第二p阱4与n阱3中一共设置有十个n+注入区5和九个p+注入区6,九个p+注入区6与十个n+注入区5间隔设置。

34.具体地,位于边缘位置的n阱3设置有一个n+注入区5和一个p+注入区6,位于中间位置的n阱3依次设置有一个n+注入区5、一个p+注入区6和一个n+注入区5或者依次设置有一个p+注入区6、一个n+注入区5和一个p+注入区6,第二p阱4依次设置有一个n+注入区5、一个p+注入区6和一个n+注入区5或者依次设置有一个p+注入区6、一个n+注入区5和一个p+注入区6,使得九个p+注入区6间隔设置在相邻的十个n+注入区5之间。

35.具体地,第一p阱2和第二p阱4具有浓度差。

36.请同时参见图8,本实用新型实施例的tvs二极管,半导体衬底1上形成有接触孔,接触孔表面金属淀积形成金属层8,金属层8并联连接多个p+注入区6形成正极,金属层8并联多个n+注入区5形成负极。

37.请同时参见图9,本实用新型实施例的tvs二极管,金属层8上方形成有钝化层9,金属层8的材质为铝,金属层8的厚度为4um,4um的厚铝金属层8能够减小体电阻。钝化层9是金属层8钝化的那部分,钝化使金属表面转化为不易被氧化的状态,而延缓金属的腐蚀速度。

38.具体地,半导体衬底1为p型衬底,其电阻率2mohm.cm,重掺杂的衬底可以得到较小的串连电阻从而降低钳位电压。

39.具体地,二极管本体的正向导通电压为0.9v,二极管本体在5v 工作电压下的反向漏电小于10na,二极管本体在1ma 电流下的击穿电压为7v。

40.请参见图10,本实用新型实施例的tvs二极管,采用国际常用的8/20us 脉冲波形进行峰值电流测试,在钳制电压为11.5v 时峰值电流约为6.3a,二极管的放电特性良好。

41.请参见图11,本实用新型实施例的tvs二极管,采用交流信号频率为1mhz测试电容,电容是影响工作速度的重要参数,由图11可知二极管分别在0v、2.5v、5v 直流偏置下的电容,小电容值提高二极管的工作速度。

42.综上所述,本实用新型实施例的tvs二极管,在半导体衬底1上注入有一定的浓度差的p型杂质形成第一p阱2和第二p阱4,注入n型杂质形成n阱3;再注入浓度较高的n型杂质形成n+注入区5,浓度较高的p型杂质形成p+注入区6,降低电容值,减少响应时间,提高可靠性;采用p 型衬底,电阻率小,得到较小串连电阻从而降低钳位电压。

43.虽然本实用新型已以较佳实施例揭示如上,然其并非用以限定本实用新型,任何本领域技术人员,在不脱离本实用新型的精神和范围内,当可作些许的修改和完善,因此本实用新型的保护范围当以权利要求书所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1