包括碳化硅材料的电子装置以及相关方法及系统与流程

包括碳化硅材料的电子装置以及相关方法及系统

1.优先权主张

2.本技术案主张2020年1月23日申请的名为“包括碳化硅材料的电子装置以及相关方法及系统(electronic devices comprising silicon carbide materials and related methods and systems)”的第16/751,049号美国专利申请案的申请日期的权益。

技术领域

3.本文中公开的实施例涉及电子装置及电子装置制作。更特定地说,本公开的实施例涉及包括一或多种碳化硅材料的电子装置,且涉及相关方法及系统。

背景技术:

4.电子装置(例如,半导体装置、存储器装置)设计人员通常期望通过缩减单个特征的尺寸且通过缩减相邻特征之间的分离距离来形成提高电子装置内的特征(例如,组件)的集成水平或密度。电子装置设计人员还期望设计不仅紧凑,而且还提供性能优势以及简化设计的架构。缩减特征的尺寸及间距对用于形成电子装置的方法提出越来越高的要求。一种解决方案是形成三维(3d)电子装置,例如3d交叉点存储器装置,其中特征为垂直而非水平布置的。为了形成特征,将多种材料彼此上下定位并蚀刻以形成材料的堆叠。堆叠的材料包含硫属化物材料及电极材料。堆叠的材料中的一些对后续进行的处理动作敏感,例如对后续处理动作的处理温度或蚀刻条件敏感。堆叠的材料可为例如热敏感的或对蚀刻化学品及其它过程条件敏感的。

5.为了在形成电子装置期间保护堆叠的材料,在堆叠上方形成衬里。在常规电子装置中,衬里包含氮化硅(sin)层及氧化硅(sio

x

)层。然而,当使用侵蚀性蚀刻化学品来形成电子装置时,衬里可无法提供足够保护。另外,用于在氮化硅上形成氧化硅的过程条件可损坏衬里的氮化硅。氧化硅层通过基于氧等离子体的过程(例如peald过程)形成在氮化硅层上,所述过程损坏(例如,氧化)氮化硅层。

6.为了进一步保护堆叠的材料,可在堆叠上方,例如在堆叠的衬里上方形成密封件。在常规电子装置中,密封件包含与氧化硅组合的氮化硅。然而,密封件可不均匀地覆盖衬里的侧壁以充分保护堆叠的材料。

7.随着特征的纵横比不断增加,且相邻堆叠之间的间距随着存储器密度的增加而持续减小,衬里及/或密封件的材料可会形成瓶颈或夹断,从而在相邻堆叠的上部部分之间导致所谓的“面包条化(bread loafing)”效应。然而,如果衬里及/或密封件的材料形成为较低厚度,那么衬里及/或密封件的材料可无法提供所要保护性质。当随后在相邻堆叠之间形成介电材料时,衬里及/或密封件的任何瓶颈部分皆会阻止介电材料完全填充堆叠之间的开口并在介电材料中形成空隙。

技术实现要素:

8.公开一种电子装置,所述电子装置包括堆叠结构,所述堆叠结构包括一或多个材

料堆叠及一或多种碳化硅材料。所述一或多个堆叠的所述材料包括单一硫属化物材料以及导电碳材料、导电材料及硬掩模材料中的一或多者。一或多种碳化硅材料相邻于一或多个材料堆叠且包括碳化硅、羰基硅、碳氮化硅、羰基氮化硅或硼氮碳化硅。一或多种碳化硅材料还包括硅-碳共价键,且一或多种碳化硅材料经配置为衬里或密封件。

9.还公开一种形成电子装置的方法。所述方法包括形成包括一或多种材料的材料堆叠,所述堆叠中的一或多种材料包括硫属化物材料。碳化硅材料是通过自由基化学气相沉积形成的,且相邻于所述材料堆叠。填充材料经形成相邻于碳化硅材料且介于材料堆叠中的相邻堆叠之间。填充材料大体上无空隙。

10.公开一种形成电子装置的额外方法。所述方法包括形成包括硫属化物材料及一或多种额外材料的材料堆叠。材料堆叠中的相邻堆叠由开口间隔开。第一碳化硅材料通过自由基化学气相沉积保形地形成,且相邻于材料堆叠。移除第一碳化硅材料的相邻于材料堆叠中的导电材料相邻的部分,且通过开口移除导电材料的经暴露部分。通过自由基化学气相沉积保形地形成第二碳化硅材料。第二碳化硅材料相邻于第一碳化硅材料且在开口中。在相邻材料堆叠之间形成填充材料,所述填充材料大体上无空隙。

11.还公开一种包括存储器单元阵列的电子装置。存储器单元包括材料堆叠,所述材料堆叠包括硫属化物材料及一或多种额外材料。碳化硅材料中的一或多者相邻于材料堆叠,一或多种碳化硅材料包括硅原子及碳原子,且一或多种碳化硅材料包括硅-碳共价键。

12.公开一种系统,所述系统包括输入装置、输出装置以及可操作地耦合到输入装置及输出装置的处理器。电子装置可操作地耦合到处理器,且包括存储器单元,所述存储器单元包括材料堆叠,所述材料堆叠包括单一硫属化物材料及一或多种额外材料。至少一种碳化硅材料垂直相邻于材料堆叠且在单一硫属化物材料的侧壁上。至少一种碳化硅材料的厚度沿着其长度大体上均匀。

附图说明

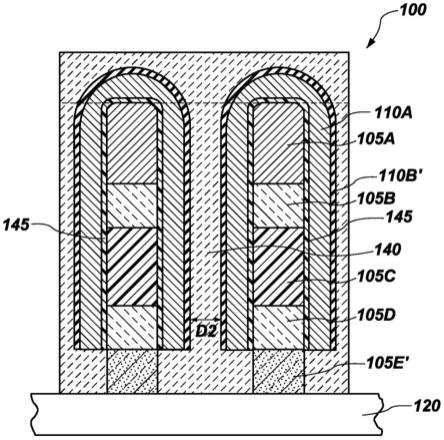

13.图1到4为根据本公开的实施例的在形成堆叠结构的各种阶段处的包含含有碳化硅材料的衬里的堆叠结构的剖面图;

14.图5到7为根据本公开的实施例的在形成堆叠结构的各种阶段处的包含含有碳化硅材料的衬里及包含碳化硅材料的密封剂的堆叠结构的剖面图;

15.图8为根据本公开的实施例的包含堆叠结构的存储器单元阵列的透视图;

16.图9为根据本公开的实施例的包含堆叠结构的电子装置的功能框图;

17.图10为根据本公开的实施例的包含堆叠结构的系统的简化框图;

18.图11为展示根据本公开的实施例的碳化硅材料的碳含量随硅-碳前体:o2的比率而变的曲线图;

19.图12为展示根据本公开的实施例的碳化硅材料的氧含量随硅-碳前体:o2的比率而变的曲线图;

20.图13a到13d为展示根据本公开的实施例的碳化硅材料使用200:1的hf(图13a及13b)、100:1的hf(图13c)及10:1hf(图13d)的湿式蚀刻速率的曲线图;且

21.图14及15为展示根据本公开的实施例的碳化硅材料的硫属化物损失的曲线图。

具体实施方式

22.公开一种电子装置(例如,设备、半导体装置、存储器装置),其包含相邻于一或多个材料堆叠(例如,在其上方)的衬里。衬里包含含有硅原子及碳原子的材料(例如,碳化硅材料)。堆叠包含一或多种热敏材料及/或一或多种氧化敏感性材料,且衬里的碳化硅材料形成在堆叠的材料上方,以在随后的过程动作期间保护敏感性材料。使用大体上不影响(例如,损坏)堆叠的材料或电子装置的其它暴露材料的低温、非氧化过程,在堆叠上方保形地形成衬里的碳化硅材料。含有相同或不同碳化硅材料的密封件可任选地形成在含有碳化硅材料的衬里上方。衬里及/或密封件的碳化硅材料通过使用硅-碳前体的自由基化学气相沉积(cvd)过程形成。在形成之后,可取决于衬里及/或密封件的碳化硅材料的所要特性(例如,蚀刻速率、抗蚀刻性、保形性等)来裁适(例如,调谐)碳化硅材料中的碳量。通过对初始形成的碳化硅材料进行处理动作,可裁适电子装置中的碳化硅材料的碳含量以提供所要的性质。

23.以下描述提供特定细节,例如材料类型、材料厚度及过程条件,以便提供对本文中所描述的实施例的全面描述。然而,所属领域的技术人员将理解,可在无需使用这些特定细节的情况下实践本文中所公开的实施例。实际上,可结合半导体行业中使用的常规制作技术来实践实施例。另外,本文中所提供的描述不形成对电子装置的完整描述或用于制造电子装置的完整处理流程,且下文所描述的结构不形成完整的电子装置。下文仅详细描述理解本文中所描述的实施例所需要的那些处理动作及结构。可通过常规技术来执行形成完整电子装置的额外动作。

24.除非另有指示,否则本文中所描述的材料可由常规技术形成,包含但不限于旋涂、覆盖涂层、化学气相沉积(“cvd”)、原子层沉积(“ald”),等离子体加强ald、物理气相沉积(“pvd”)(包含溅射、蒸发、离子化pvd及/或等离子体加强cvd)或外延生长。替代地,可原位生长所述材料。取决于欲形成的特定材料,用于沉积或生长材料的技术可由所属领域的技术人员选择。材料的移除可通过任何合适的技术来完成,包含但不限于蚀刻(例如,干式蚀刻、湿式蚀刻、气相蚀刻)、离子铣切、磨料平坦化(例如,化学机械平坦化))或其它已知方法,除非上下文另有说明。

25.本文中所呈现的附图仅出于说明目的,并不意味着为任何特定材料、组件、结构、电子装置或电子系统的实际视图。可预期由于例如制造技术及/或公差而在附图中描绘的形状的偏差。因此,本文中所描述的实施例不应被解释为限于所说明的特定形状或区域,而是包含例如由制造导致的形状偏差。举例来说,经说明或描述为盒形的区域可具有粗糙及/或非线性特征。经说明或描述为圆形的区域可包含一些粗糙及/或线性的特征。此外,所说明锐角可为圆形的,且反之亦然。因此,图中所说明的区域本质上为示意性的,且其形状不意欲说明区域的精确形状,且不限制本权利要求书的范围。图式不一定按比例。另外,图之间共同的元件可保持相同的数字标记。

26.如本文中所使用,除非上下文另有明确指示,否则单数形式“一(a)”、“一(an)”及“所述”旨在还包含复数形式。

27.如本文中所使用,术语“及/或”包含相关联所列物项中的一或多者的任何及全部组合。

28.如本文中所使用,对于特定参数的数值,“约”或“大约”包含数值且来自所属领域

的技术人员将理解的数值的变异程度在特定参数的可接受公差范围内。举例来说,对于数值的“约”或“大约”可包含在从数值的90.0%到110.0%范围内的额外数值,例如在从数值的95.0%到105.0%的范围内,在从数值的97.5%到102.5%的范围内,在从数值的99.0%到101.0%的范围内,在从数值的99.5%到100.5%的范围内,或在从数值的99.9%到100.1%的范围内。

29.如本文中所使用,空间相对术语,例如“下方”、“下面”、“下部”、“底部”、“上面”、“上部”、“顶部”、“前方”、“后方”、“左侧”、“右侧”及其类似物为了便于描述可用于来描述一个元件或特征与另一元件或特征的关系,如图中所说明。除非另有规定,否则空间相对术语旨在囊括除了图中所描绘的定向之外的材料的不同定向。举例来说,如果图中的材料倒置,那么描述为在其它元件或特征的“下面”或“下方”或“之下”或“底部”的元件将经定向在其它元件或特征的“上面”或“顶部上”。因此,取决于使用所述术语的上下文,术语“在...下方”可囊括在上面及在下面两个定向,这对于所属领域的技术人员来说为显而易见的。可以其它方式定向材料(例如,旋转90度、倒置、翻转),且相应地解释本文中使用的空间相对描述语。

30.如本文中所使用,术语“经配置”是指至少一个结构及至少一个设备中的一或多者的大小、形状、材料组成及布置,其有助于以预定方式操作结构及设备中的一或多者。

31.如本文中所使用,术语“电子装置”包含但不限于存储器装置,以及可并入或不并入存储器的其它半导体装置,例如逻辑装置、处理器装置、射频(rf)装置。此外,除了其它功能之外,电子装置还可并入存储器,例如包含处理器及存储器的所谓的“片上系统”(soc),或包含逻辑及存储器的半导体装置。电子装置可为包含敏感材料的3d电子装置,例如3d交叉点存储器装置。

32.如本文中所使用,术语“衬里材料”或“衬里”意指且包含碳化硅材料,所述碳化硅材料经配制以在经受相同蚀刻条件时展现在碳化硅材料与其它暴露材料之间的蚀刻选择性。衬里可包含彼此相邻定位且经配制以展现所要蚀刻选择性性质的一或多种材料,例如碳化硅材料及一或多种额外材料。衬里的厚度小于密封件的厚度。

33.如本文中所使用,将一元件称为在另一元件“上”或“上方”意指且包含所述元件直接位于另一元件顶部、相邻于(例如,侧向相邻于、垂直相邻于)另一元件、在另一元件下面或与另一元件直接接触。还包含所述元件间接地位于另一元件顶部、相邻于(例如,侧向相邻于,垂直地相邻于)另一元件,在另一元件下方或在另一元件附近,其中在其之间存在其它元件。相比来说,当将一元件称为“直接连在”另一元件“上”或“直接相邻于”另一元件时,不存在任何介入元件。

34.如本文中所使用,术语“密封材料”或“密封件”意指且包含经配制为表现出阻挡性质的碳化硅材料,例如缩减或大体上防止水穿过所述材料。密封件可包含彼此相邻定位且经配制以展现所要屏障性质的一或多种材料,例如碳化硅材料及一或多种额外材料。密封件的厚度大于衬里的厚度。

35.如本文中所使用,术语“碳化硅材料”意指并包含包含硅原子及碳原子的材料。碳化硅材料可任选地包含氧原子,氮原子或硼原子中的一或多者。碳化硅材料可包含但不限于碳化硅、羰基硅、碳氮化硅、羰基氮化硅,或硼氮碳化硅。碳化硅材料可为化学计量化合物或非化学计量的化合物。术语“羰基硅”或“氧掺杂碳化硅”用于指具有通用化学式sico

x

的

碳化硅材料,术语“碳氮化硅”或“氮掺杂碳化硅”用于指具有通用化学式sicny的碳化硅材料,且术语“羰基氮化硅”或“氧氮掺杂的碳化硅”用于指具有通用化学式sico

x

ny的碳化硅材料。术语“碳化硅材料”用于统称为碳化硅、碳氮化硅、羰基硅,或羰基氮化硅中的一或多者。碳化硅材料的定义不包括仅包含硅原子及氧原子的氧化硅(sio

x

)。

36.如本文中所使用,术语“可选择性蚀刻”意指且包括材料,所述材料相对于暴露于给定蚀刻化学品及/或过程条件的另一材料响应于暴露于相同蚀刻化学品及/或其它材料而展现较大蚀刻速率。举例来说,材料可展现为另一材料的蚀刻速率的至少约五倍大的蚀刻速率,例如为另一材料的蚀刻速率的约十倍大,约二十倍大或约四十倍大的蚀刻速率。所属领域的技术人员可选择用于选择性地蚀刻所要材料的蚀刻化学品及蚀刻条件。

37.如本文中所使用,术语“堆叠”意指并包含具有经定位彼此处置相邻的多种材料的特征。堆叠的材料中的至少一者可对热及/或水敏感:堆叠的材料可包含一或多种导电(例如,导电)材料,一或多种硫属化物材料,以及硬掩模材料或其组合。

38.如本文中所使用,关于给定参数、性质或条件的术语“大体上”意指且包含所属领域的技术人员将理解给定参数、性质或条件满足变异程度,例如在可接受的制造公差范围内。举例来说,取决于大体上满足的特定参数、性质或条件,参数、性质或条件可至少90.0%满足、至少95.0%满足、至少99.0%满足,或甚至至少99.9%满足。

39.如本文中所使用,术语“衬底”意指并包含在其上形成额外材料的材料(例如,基底材料)或构造。衬底可为电子衬底、半导体衬底、在支撑结构上的基底半导体层、电极,在其上形成有一或多种材料、层、结构或区域的电子衬底,或其上形成有一或多个材料、层、结构或区域的半导体衬底。电子衬底或半导体衬底上的材料可包含但不限于半导体材料、绝缘材料、导电材料等。衬底可为常规硅衬底或包括半导电材料层的其它块状衬底。如本文中所使用,术语“块状衬底”不仅意指且包含硅晶片,而且意指且包含绝缘体上硅(soi)衬底(例如,蓝宝石上硅(sos)衬底及玻璃上硅(sog)衬底)、在基底半导体底座上的外延硅层及其它半导体或光电材料(例如,硅锗、锗、砷化镓、氮化镓及磷化铟)。衬底可为经掺杂或未经掺杂。

40.如本文中所使用,术语“垂直”、“纵向”、“水平”及“横向”是指结构的主平面,且不一定由地球的重力场界定。“水平”或“横向”方向为大体上平行于结构的主平面的方向,而“垂直”或“纵向”方向为大体上垂直于结构的主平面的方向。结构的主平面由结构的表面界定,结构的表面与结构的其它表面相比具有相对大的面积。

41.在图1及2中展示堆叠结构100,其包含堆叠105,相邻于(例如,垂直相邻于,在其上方)堆叠105的衬里110,以及开口115。衬里110可包含一或多个衬里部分,例如衬里部分110a、110b。堆叠结构100经形成相邻于(例如,垂直相邻于,在其上方)衬底120。堆叠105通过开口115彼此分开,且相邻堆叠105彼此分开距离d1。距离d1可取决于形成堆叠结构100的堆叠105的节距,所述节距取决于含有堆叠结构100的电子装置中的堆叠结构100的预期用途来选择。每一堆叠105包含多种材料,例如一或多种导电材料、一或多个硫属化物材料及硬掩模材料。如下文更详细描述,堆叠结构100可存在于电子装置的存储器单元中。

42.图1及2将堆叠105展示为包含四种材料105a到105d及导电材料105e。然而,堆叠105中的材料的数目可大于或小于五。堆叠105的材料中的一或多者可为热敏的或对氧化敏感的。堆叠105可例如包含导电材料105e、一或多种硫属化物材料、一或多种导电碳材料、除

导电材料105e之外的一或多种导电材料,以及硬掩模材料。仅作为实例,堆叠105可包含在衬底120上方的导电材料105e,在导电材料105e上方的第一导电碳材料,在第一导电碳材料上方的一或多种硫属化物材料,在一或多种硫属化物材料上方的第二导电碳材料,及在第二导电碳材料上方的硬掩模材料。堆叠105可例如包含对热或氧化(例如,氧化条件)敏感的一或多种硫属化物材料及一或多种导电碳材料,在形成堆叠105期间及之后或在形成衬里110或密封件125(参见图5)期间材料可暴露于所述条件。在一些实施例中,堆叠105包含在衬底120上方的导电材料105e,在导电材料105e上方的第一导电碳材料,在第一导电碳材料上方的硫属化物材料,在硫属化物材料上方的第二导电碳材料以及在第二导电碳材料上方的硬掩模材料。在其它实施例中,堆叠105包含在衬底120上方的导电材料105e,在导电材料105e上方的第一导电碳材料,在第一导电碳材料上方的第一硫属化物材料,在第一硫属化物材料上方的第二硫属化物材料,在第二硫属化物材料上方的第二导电碳材料及在第二导电碳材料上方的硬掩模材料。

43.堆叠105的导电材料105e可包含导电材料,所述导电材料包含但不限于钨、铝、铜、钛、钽、铂、其合金、重掺杂半导体材料、多晶硅、导电硅化物、导电氮化物、导电碳、导电碳化物或其组合。导电材料105e可以如经配置为存取线、字线、触点、数字线、位线等。在一些此类实施例中,导电材料105e为钨。替代地,导电材料105e可经配置为电极。在一些此类实施例中,导电材料105e为导电碳。

44.堆叠105的导电碳材料可包含但不限于导电碳材料。

45.堆叠105的硫属化物材料可为硫属化物玻璃、硫属化物金属离子玻璃或其它含硫属化物材料。硫属化物材料可为包含至少一个硫属化物原子及至少一或多种正电性元素的二元或多元(三元、四元等)化合物。如本文中所使用,术语“硫属化物”意指并包含元素周期表的第vi族的元素,例如氧(o)、硫(s)、硒(se)或碲(te)。正电性元素可包含但不限于氮(n)、硅(si)、镍(ni)、镓(ga)、锗(ge)、砷(as)、银(ag)、铟(in)、锡(sn)、锑(sb)、金(au)、铅(pb)、铋(bi)或其组合。仅作为实例,硫属化物材料可包含包含ge、sb及te的化合物(即,gst化合物),例如ge2sb2te5,然而,本公开不限于此,且硫属化物材料可包含其它化合物,包含至少一种硫属元素。硫属化物材料可经掺杂或未经掺杂且可在其中混合有金属离子。仅作为实例,硫属化物材料可为包含铟、硒、碲、锑、砷、铋、锗、氧、锡或其组合的合金。在一些实施例中,堆叠105包含一种(例如,单一)硫属化物材料。在其它实施例中,堆叠105包含两种硫属化物材料。两种硫属化物材料可彼此相邻,或可由堆叠105的其它材料中的一或多者间隔开。

46.堆叠105的硬掩模材料可相对于堆叠105中的其它材料以及相对于在后续过程动作期间形成在堆叠105上的一或多种其它导电材料展现出不同的蚀刻选择性。硬掩模材料可包含但不限于氮化硅或非晶碳。可在进行后续过程动作之前任选地移除硬掩模材料。在一些实施例中,硬掩模材料为氮化硅。

47.堆叠105的材料经定位成彼此相邻(例如,垂直相邻)。堆叠105的材料可通过常规技术彼此垂直相邻地形成,且所述材料经图案化以形成通过开口115彼此分离的堆叠105。可通过常规技术,例如通过使用常规光刻及蚀刻技术来蚀刻材料,来图案化材料(例如,移除材料的一部分)。可例如将材料暴露于各向同性蚀刻过程,例如干式等离子体蚀刻过程或反应性离子蚀刻过程,以形成堆叠105可使用常规蚀刻化学品及蚀刻条件来形成堆叠105及

开口115。所得堆叠105可为高纵横比(har)特征,其纵横比(即,宽度与深度的比)大于或等于大约5:1,例如从约5:1到约100:1、从约5:1到约50:1、从约10:1到约40:1、从约10:1到约30:1、从约10:1到约20:1,从约20:1到约50:1,从约20:1到约40:1或从约20:1到约30:1。开口115还可展现出高纵横比。可依从约3nm到约100nm(例如从约10nm到约30nm、从约15nm到约25nm或从约15nm到约20nm)的半节距形成堆叠105。在一些实施例中,堆叠105以20nm的半节距形成。在其它实施例中,堆叠105以14nm的半节距形成。除了将堆叠105经配置为线之外,还可使用其它几何形状,例如支柱。堆叠105的导电材料105e可与堆叠105的其它材料同时经图案化,或可以在图案化材料105a到105d之后经图案化,如图3中所展示。

48.如在图2中所展示,衬里110a、110b可经形成为相邻于堆叠105(例如,在堆叠105上方)。虽然图式将衬里110展示为包含两个衬里部分110a、110b,但衬里110可包含单个衬里部分110b,或可取决于欲实现的保护程度而包括三个或多于三个部分。衬里110a、110b以足够的厚度保形地形成在堆叠105的材料105a到105d的侧壁上,以在堆叠105的形成期间或之后或在相邻于衬里110a、110b(例如,在其上方)形成任选密封件125(参见图5)之前或之后进行的过程动作期间保护堆叠105的材料105a到105d。后续过程动作可包含但不限于蚀刻过程(例如,干式蚀刻过程、湿式蚀刻过程)或基于等离子体的过程,例如处理过程或致密化过程。衬里110a、110b还可在进行以清洁堆叠105的过程动作期间保护堆叠105的材料。衬里110a、110b还形成在导电材料105e的水平表面上以保护导电材料105e。

49.如图2中所展示,堆叠结构100的相邻堆叠105彼此分离小于距离d1的距离d2。距离d2的范围可从约3nm到约300nm,例如从约20nm到约60nm,从约20nm到约40nm,或从约40nm到约60nm,取决于形成堆叠结构100的堆叠105的节距及衬里110a、110b的厚度。相邻堆叠105之间的距离d2可等于厚度d1减去衬里110、110b的厚度的两倍。

50.衬里110a由例如氮化硅(sin)的介电材料形成。衬里110a可通过常规技术,例如通过pecvd,保形地形成在堆叠105上方。衬里110a可提供对衬里110的粘附性质或保护性质。衬里部分110a具有从约到约的厚度。衬里110b可保形地形成在衬里110a上方,例如直接在衬里110a上方(例如,与其接触)形成衬里110b。替代地,衬里110可仅包含衬里部分110b的碳化硅材料,其中衬里110b的碳化硅材料直接在堆叠105上方(例如,与其接触)。例如,随着堆叠结构100的相邻堆叠105之间的间隔减小,碳化硅材料可直接形成在堆叠105上,使得仅存在衬里110b。

51.衬里110b可由碳化硅材料形成。衬里110b由自由基cvd过程形成,所述过程利用一种(例如,单个)硅-碳前体,所述硅-碳前体包含硅-碳前体的硅原子与碳原子之间的共价键。因此,所得的碳化硅材料在硅原子及碳原子之间包括共价键,且较之由其它方法形成的常规碳化硅材料更稳定(例如,热力学稳定)。初始形成的衬里110b的碳化硅材料可包含介于约2原子百分比(at.%)与约50at.%之间的碳,例如介于约2at.%与约40at.%之间的碳,介于约2at.%与约30at.%之间的碳,介于约5at.%与约50at.%之间的碳,介于约5at.%与约40at.%之间的碳,介于约5at.%与约30at.%之间的碳,介于约10at.%与约50at.%之间的碳,介于约15at.%与约50at.%之间的碳,介于约20at.%与约50at.%之间的碳,介于约25at.%与约50at.%之间的碳,介于约30at.%与约50at.%之间的碳,介于约35at.%与约50at.%之间的碳,介于约40at.%与约50at.%之间的碳,介于约45at.%到约50at.%之间的碳,介于约10at.%与约30at.%之间的碳,介于在约15at.%与约30at.%之

间的碳,介于在约20at.%与约30at.%之间的碳,介于在约25at.%与约30at.%之间的碳,介于约30at.%与约50at.%之间的碳,介于约35at.%与约50at.%之间的碳,介于约40at.%与约50at.%之间的碳,介于约35at.%与约45at.%之间的碳或介于约10at.%与约25at.%之间的碳。自由基cvd过程可为不影响(例如,损坏)衬里110b的非氧化过程。衬里110b的碳化硅材料可展现高度的保形性且展现对随后的过程动作中使用的蚀刻化学品的高抵抗性。衬里部分110b具有从约到约的厚度。

52.为了形成衬里110b,可将包括堆叠105及衬里110a的堆叠结构100放置到反应室中,且可通过自由基cvd过程形成衬里110b的碳化硅材料。反应室可为半导体工业中使用的常规设备。将硅-碳前体、自由基物种及任选载气引入到含有堆叠结构100的反应室。硅-碳前体可在硅-碳前体的硅原子与碳原子之间含有一或多个硅-碳(si-c)共价键。硅-碳前体还可含有一或多个硅-氢(si-h)共价键及/或一或多个硅-硅(si-si)共价键。硅-碳前体可为在形成衬里110b的碳化硅材料的温度下的气体。通过使用包含硅-碳共价键的硅-碳前体,衬里110b的还包含硅-碳共价键的碳化硅材料可在低温下且使用较少侵蚀性过程条件形成,这是因为形成si-c共价键在热力学上为不利的。硅-碳前体可包含约2at.%到约45at.%之间的硅,约2at.%到约50at.%之间的碳,约0at.%到约45at.%之间的氧,以及在约0at.%到约45at.%之间的氮。

53.取决于碳化硅材料的所要材料组合物,除了在硅原子与碳原子之间的共价键之外,硅-碳前体还可任选地包含介于硅-碳前体的硅原子与氮原子之间的共价键或介于硅-碳前体的硅原子与氧原子之间的共价键。如果例如碳化硅材料包含氧,那么硅-碳前体可包含一或多个硅-氢(si-h)共价键,一或多个si-c共价键,一或多个硅-硅(si-si)共价键及一或多个硅-氧(si-o)共价键。如果例如碳化硅材料包含氮,那么硅-碳前体可包含一或多个硅-氢(si-h)共价键,一或多个si-c共价键,一或多个硅-硅(si-si)共价键及一或多个硅-氮(si-n)共价键。如果例如碳化硅材料包含氧及氮,那么硅-碳前体可包含一或多个硅-氢(si-h)共价键,一或多个si-c共价键,一或多个硅-硅(si-si)共价键,一或多个硅-氮(si-n)共价键及一或多个硅-氧(si-o)共价键。硅-碳前体可为线性硅氧烷,环状硅氧烷,甲硅烷,烷基硅烷,烷氧基硅烷或硅氮烷。替代地,硅-碳前体可具有通用化学式si-r,其中r为烷基;si-ar,其中ar为芳基;或si-or或si-oar。此类硅-碳前体在所属领域中为已知的,且可从许多来源(例如从科林研发公司(lam research corp.)(加利福尼亚州弗利蒙市))商购获得。通过适当地选择含有共价键(例如,si-c共价键、si-si共价键、si-o共价键、si-n共价键)的硅-碳前体存在于所得碳化硅材料中,可使用单一类型的硅-碳前体来形成碳化硅材料。换句话说,在形成自由基物种之前,在硅-碳前体中形成(例如,存在)si-c共价键、si-si共价键、si-o共价键、si-n共价键。

54.自由基物种可例如包含氢自由基(h)、氧自由基物种,或氮自由基物种。氢自由基可通过常规技术产生,例如使氢气(h2)经受远程等离子体源中的等离子体。由氢气产生氢自由基为常规的,且在本文中不再详细描述。等离子体源可包含但不限于:电容耦合等离子体(ccp)、电感耦合等离子体(icp)、微波(mw)等离子体、dc等离子体或激光产生等离子体。氢自由基为使用高功率远程icp源在高压下产生。当与硅-碳前体反应时,氢自由基可处于足够低的能量状态,使得硅-碳前体中的si-c共价键在在堆叠105上形成碳化硅材料期间不会与氢自由基发生反应(例如,不会被氢自由基破坏)。氢自由基最初可处于激发能态,其松

弛成低能态氢自由基(例如,基能态氢自由基)。硅-碳前体及氢自由基可彼此充分反应,使得不使用等离子体条件来形成衬里110b的碳化硅材料。低能态氢自由基可与硅-碳前体反应以损坏si-si共价键及/或si-h共价键,活化硅-碳前体并形成硅-碳前体的自由基。经活化硅-碳前体包含反应性位点,且氢自由基引发在硅-碳前体的反应性位点处的交联,使得活化的硅-碳前体的分子彼此反应以形成衬里110b的碳化硅材料。经活化硅-碳前体的自由基可展现较低的粘附系数。由于在基于自由基的反应中不使用氧化反应环境,因此能够通过具有低滞留时间反应且在低温下的自由基cvd过程来形成碳化硅材料。大体上所有的氢自由基可处于低能态或基态,且可与硅-碳前体起反应。仅作为实例,大于约90%或大于约95%的氢自由基可处于低能态或基态。因此,包含堆叠105及衬里110a的堆叠结构100暴露于高密度的氢自由基。

55.如果硅-碳前体还包含si-o共价键,那么氢自由基可处于足够低的能量状态,使得si-c共价键及si-o共价键在形成碳化硅材料期间不与氢自由基发生反应(例如,不会由氢自由基破坏)。如果硅-碳前体还包含si-n共价键,那么氢自由基可处于足够低的能量状态,使得si-c共价键及si-n共价键在形成碳化硅材料期间不与氢自由基发生反应(例如,不会由氢自由基破坏)。如果硅-碳前体还包括si-o共价键及si-n共价键,那么氢自由基可处于足够低的能量状态,使得si-c共价键、si-o共价键及si-n共价键在碳化硅材料的形成期间不与氢自由基反应(例如,不会由氢自由基破坏)。

56.低能态氢自由基与硅-碳前体起反应,以在堆叠105上,例如在堆叠105的材料的侧壁上形成碳化硅材料。选择过程条件使得硅-碳前体中的si-si共价键及si-h共价键选择性地破坏,而si-c共价键及si-o共价键及/或si-n共价键未破坏。硅-碳前体中的si-c键以及si-o共价键及/或si-n共价键(如果存在)在自由基cvd过程的过程条件下相对于硅-碳前体中的si-si共价键及si-h共价键为热力学稳定的。硅-碳前体的硅及碳有利于初始形成的碳化硅材料中的大体上全部硅及碳。如果硅-碳前体包含氧及氮中的一或多者,那么硅-碳前体有利于在初始形成的碳化硅材料的大体上全部氧及氮。

57.自由基cvd过程的过程条件大体上保留硅-碳前体的si-c共价键。换句话说,在硅-碳前体及低能态氢自由基反应之后,碳化硅材料中存在si-c共价键。如果碳化硅材料为羰基硅,那么在碳化硅材料中可存在si-c共价键及si-o共价键。如果碳化硅材料为碳氮化硅,那么在碳化硅材料中可存在si-c共价键及si-n共价键。如果碳化硅材料为羰基氮化硅,那么在碳化硅材料中可存在si-c共价键、si-o共价键及si-n共价键。可以足够流速、温度、压力、滞留时间,rf功率等将反应性物种及硅-碳前体引入到反应室中,以将氢自由基维持在低能态或基态。仅作为实例,反应室内的堆叠结构100的温度可为从约50℃到约500℃,例如从约50℃到约450℃。反应室内的压力可小于或等于约35托。

58.所形成的碳化硅材料可为大体上均质的化学组合物或可为异质化学组合物,例如包含碳在碳化硅材料的整个厚度上的梯度。仅作为实例,碳化硅材料可包含在堆叠105附近的富硅部分,其中碳化硅材料的碳含量在堆叠105的远侧增加。替代地,碳化硅材料在其整个厚度上可为大体上均质组合物。衬里110b可展现大于或等于约75%、大于或等于约80%、大于或等于约85%、大于或等于约90%、大于或等于约95%,或大于或等于约99%的阶梯覆盖率。

59.通过自由基cvd过程形成衬里110b的碳化硅材料使得能够在不使用直接等离子体

的情况下形成碳化硅材料,这减少等离子体对堆叠结构100的损坏。由于硅-碳前体包含所要共价键,因此能够在较低温度下且仅使用单个硅-碳前体来形成碳化硅材料。由于在自由基cvd过程的过程条件下热力学上不利于形成si-c共价键,因此衬里110b的碳化硅材料中存在大体上相同的存在于硅-碳前体中的共价键。另外,自由基的低粘附系数使得碳化硅材料能够以高阶梯覆盖率(例如以大于或等于约85%的阶梯覆盖率)形成。

60.根据本公开的实施例的碳化硅材料不同于分别使用分离的硅前体及碳前体作为硅及碳的来源形成的碳化硅材料。通过自由基cvd过程形成的碳化硅材料包含si-c共价键,而使用单独的硅前体及碳前体形成的碳化硅材料不包含si-c共价键。类似地,通过自由基cvd过程形成的碳化硅材料包含si-c共价键、si-o共价键及si-n共价键,而使用单独的硅前体、碳前体、氮前体及氧形成前体形成的碳化硅材料不包含si-c共价键。

61.虽然本文中的实施例将碳化硅材料描述为通过自由基cvd过程形成,但可替代地使用例如等离子体加强ald过程的原子层沉积(ald)过程。仅作为实例,可使用si2cl6的等离子体及ch4的等离子体形成碳化硅材料,以在o2等离子体处理之后形成碳化硅(sic)或羰基硅(sico

x

)。羧基氮化硅(sico

x

ny)还可通过ald使用顺序的si2cl6及ch3nh2等离子体流形成。

62.如在图3中所展示,可对堆叠105的导电材料105e进行图案化以形成导电材料105e

′

。衬里110b的碳化硅材料可大体上抵抗在形成相邻于堆叠105(例如,在其上方)的衬里110a、110b之后用于对导电材料105e进行图案化的干式蚀刻化学品。然而,可从导电材料105e的水平表面移除衬里110的一部分,且可从堆叠105的顶部部分移除衬里110a、110b中的一或多者的一部分。例如,可移除衬里110a、110b的相邻于堆叠105的顶部表面(例如,在其上方)且相邻于导电材料105e的水平表面(例如,在其上方)的一部分,而衬里110a、110b的一部分保留在堆叠105的材料105a到105d的侧壁上。蚀刻化学品及蚀刻条件可例如从堆叠105的顶部移除衬里110b,例如在硬掩模上方,而衬里110a、110b保留在堆叠105的材料105a到105e中的硫属化物材料及/或导电碳材料的侧壁上。可通过相同蚀刻品及蚀刻条件来蚀刻导电材料105e,从而形成导电材料105e

′

。虽然图2将衬里110a、110b展示为大体上连续的材料,但由于所使用的蚀刻化学品及蚀刻条件,如图3中所展示,在导电材料105e的图案化期间,衬里110a、110b可变得不连续。

63.衬里110b的碳化硅材料还可大体上抵抗水性氟化氢(hf)湿式蚀刻化学品,例如用于在图案化导电材料105e之后移除残留(例如,清洁)堆叠结构100的蚀刻化学品。衬里110b的碳化硅材料还可大体上抵抗过氧化氢、柠檬酸或氢氧化铵湿式蚀刻化学品。

64.衬里110b可经受一或多种处理动作,所述处理行为改变(例如,缩减)衬里110b的碳含量,这与初始形成的衬里110b的介电常数相比,改变衬里110b的介电常数。在处理动作之后,衬里110b被称为经处理衬里110b

′

,且在图4及随后的附图中被说明为衬里110b

′

,致使已经进行处理动作。衬里110b的碳化硅材料的介电常数可低于氮化硅的介电常数(约8)。根据本公开的实施例的碳化硅材料的较低介电常数可使得含有碳化硅材料的电子装置能够减轻由于碳化硅材料的高电容而引起的高尖峰电流。处理动作还可使得衬里110b致密化,从而将密度从约1.8g/cm3增加到约2.0g/cm3。可进行处理动作以裁适经处理衬里110b

′

的碳含量并提供经处理衬里110b

′

的所要性质。处理动作可包含使衬里110b暴露于氧气(o2)处理动作,例如o2等离子体处理动作。不受任何理论的束缚,据信在氧等离子体处理的氧化环境中的氧原子与碳化硅材料中的碳起反应以形成挥发性的二氧化碳。因此,在氧等

离子体处理动作之后,可从碳化硅材料移除碳化硅材料的碳的一部分。因此,经处理衬里110b

′

的碳化硅材料包含少于初始形成的碳化硅材料的碳含量的碳。为了在随后的过程动作期间提供所要蚀刻选择性,在氧等离子体处理动作之后,碳化硅材料可含有至少最小量的碳。

65.氧处理动作的过程条件,例如温度、压力、rf功率等,可取决于经处理衬里110b

′

中所要的碳含量来选择。过程条件可为常规。可在将衬里110b的碳化硅材料形成为所要总厚度之后进行处理动作(例如,氧处理)。替代地,可在形成碳化硅材料的初始部分之后进行氧处理,后续接着形成碳化硅材料的一或多个额外部分,后续接着额外氧处理动作。为了防止损坏碳化硅材料,可初始以低氧化速率进行氧处理,后续接着在将碳化硅材料形成为足够厚度之后增加氧化速率。与进行单个氧处理动作相比,进行多个氧处理动作可增加衬里110b的密度。仅通过实例,衬里110b的密度可通过使氧处理动作的次数加倍而从约1.8g/cm3到1.9g/cm3增加到约2.0g/cm3。取决于所使用的处理条件,经处理衬里110b

′

可包含介于约2at.%到约50at.%之间的碳。如果例如每一碳化硅材料部分的形成后续接着进行氧等离子体处理,那么碳化硅材料可包含介于约2at.%到约5at.%之间的碳。相反地,如果将碳化硅材料形成为所要总厚度,后续接着单个等离子体氧处理,那么碳化硅材料可包含更多的碳,例如从约15at.%到约50at.%的碳。

66.经处理衬里110b

′

的碳化硅材料不同于分别使用单独的硅前体及碳前体作为硅及碳的来源并暴露于相似的处理作用而形成的碳化硅材料。通过自由基cvd过程形成的经处理碳化硅材料包含si-c共价键,而使用单独的硅前体及碳前体形成的经处理碳化硅材料不包含si-c共价键。

67.除了氧气以外,处理动作还可包含氮气(n2)、氨气(nh3)或氢气(h2)。处理动作还可包含载体气体(例如,惰性气体),例如氦气。由于在处理动作期间使用氧气并将其并入到碳化硅材料中,因此即使硅-碳前体不包含氧原子,也可形成包含氧的碳化硅材料。换句话说,包含氧的碳化硅材料中的氧的来源可来自处理动作中使用的氧气。类似地,如果处理动作包含氮气,那么包含氮的碳化硅材料中的氮的来源可来自在处理动作中使用的氮气。除了氧气以外,处理动作还可包含氮气(n2)、氨气(nh3)或氢气(h2)。

68.如图4中所展示,可在开口115中形成填充材料140。开口115的距离d2可足以在开口115中形成填充材料140而在填充材料140中不形成空隙。填充材料140可例如为电绝缘材料,例如介电材料。填充材料140可为部分的牺牲材料,因为在完成包含堆叠结构100的电子装置之前,随后部分地移除填充材料140。可例如在电子装置的第一叠组(deck)完成之前部分地移除填充材料140。替代地,填充材料140可存在于包含堆叠结构100的电子装置中。填充材料140例如可为二氧化硅、氮化硅、氮氧化硅、羰基硅、旋涂介电材料(sod)、bpsg、bsg、气隙或另一介电材料。根据本公开的实施例的碳化硅材料还可用作填充材料140,使得碳化硅材料大体上完全填充开口115。在一些实施例中,填充材料140为旋涂式二氧化硅。在其它实施例中,填充材料140为高质量二氧化硅。然而,可使用其它填充材料140,例如通过在相邻堆叠105之间形成气隙。

69.填充材料140可大体上完全填充开口115,如在图4中所展示。随后可例如通过化学机械平坦化(cmp)来移除堆叠105上方的过量填充材料140。衬里110的一部分还可例如从堆叠105的上部表面移除,从而暴露硬掩模材料或堆叠105的电极材料,如由图4中的虚线所展

示。然而,衬里110保留在堆叠105的侧壁上。如果填充材料140为介电材料,那么介电材料可使电子装置的存储器单元彼此隔离,且还可在后续过程动作期间提供机械支撑以形成包含碳化硅材料的电子装置。

70.如在图5中所展示,根据本公开的实施例的碳化硅材料还可用作堆叠结构100中的密封件125。密封件125可经形成为相邻于堆叠结构100的衬里110(例如在其上方)。密封件125的碳化硅材料可展现与衬里110b的碳化硅材料相同的化学组合物或不同的化学组合物。密封件125可大体上囊封堆叠105的材料以及衬里110a、110b的其余部分。密封件125的碳化硅材料可经选择为相对于随后形成在堆叠105上方的导电材料可选择性地蚀刻,所述导电材料的一部分通过稍后的过程动作被移除以形成例如位线。密封件125可大体上围绕(例如,囊封)堆叠105及衬里110a、110b,例如在其顶部表面及侧壁上方。密封件125可存在于堆叠105的三个表面上,从而提供密封屏障,可防止水穿过密封件125并进入堆叠105中。密封件125可直接接触衬里110b,或如果不存在衬里110a、110b,那么可以直接接触堆叠105。随后图式说明密封件125与衬里110b直接接触。然而,如果在堆叠结构100中不存在衬里110,那么密封件125可直接接触堆叠105。尽管在图5中将密封件125说明为单一材料,但密封件125可包含多种材料,例如氮化硅材料及碳化硅材料,其中碳化硅材料经形成为相邻于密封件125(例如,氮化硅材料)的初始部分(例如,在其上方)。

71.根据本公开的实施例的密封件125可通过上文针对衬里110b所描述的大体上相同的自由基cvd过程形成。然而,较之衬里110b的碳化硅材料,密封件125可包含相同量的碳、较少的碳或较多的碳。硅-碳前体及氢自由基可彼此充分起反应,使得不使用等离子体条件来形成密封件125。为了形成密封件125,可将包含堆叠105及衬里110a、110b(如果存在)的堆叠结构100放置在常规反应室中,且如上所述将硅-碳前体及氢自由基引入到反应室中。可形成密封件125的碳化硅材料,直到获得所要厚度的密封件125。

72.可以足够厚度形成密封件125,以保护堆叠105的材料105a到105d以及衬里110a、110b免受随后的过程动作影响,所述过程动作在堆叠105的材料在随后过程动作期间保持暴露的情况下可氧化或以其它方式损坏所述材料。密封件125的厚度足以提供屏障性质,而不会在相邻堆叠105之间形成所谓的“瓶颈”、“夹断”或“面包条化”。密封件125还可在含有密封件125的电子装置的使用及操作期间提供保护,例如当可存在高温及电场时。例如,堆叠105的碳及/或硫属化物材料在暴露于水或暴露于用于形成堆叠105或衬里110a、110b的过程条件时,例如在导电材料105e的图案化期间,可经氧化或以其它方式损坏。当在堆叠105之间形成填充材料140(参见图6)时,可以足以提供所要屏障性质而不会在堆叠105的上部部分周围形成瓶颈或面包条化的最小厚度形成密封件125。密封件125的厚度可在从约到约的范围内。密封件125的碳化硅材料还可通过大体上完全填充开口115

′

来用作填充材料140。

73.密封件125可保形地形成在衬里110b上方且可在堆叠105的侧壁及上部部分上方形成大体上连续材料。密封件125可大体上无针孔或其它不连续。密封件125可形成在开口115中,所述开口由衬里110b的侧壁或在不存在衬里110的情况下由堆叠105的侧壁界定。密封件125可形成在堆叠105或衬里110b上(例如,与其相邻),从而缩减开口115到开口115

′

的大小。在形成密封件125之后,堆叠105彼此分开距离d3,所述距离d3小于距离d1及d2。距离d3足以在开口115

′

中形成填充材料140(参见图6)而无需在填充材料140中形成空隙。密封

件125可展现高度的保形性及高度的厚度均匀性(例如,高台阶覆盖率),从而缩减或消除堆叠105之间的瓶颈及所谓的“面包条化”。由于在形成密封件125之后在堆叠105之间保留足够的空间,因此在堆叠105的上部部分处或其之间大体上无瓶颈或面包条化。密封件125可展现至少约95%的保形性,例如大于约98%或大于约99%。密封件125的厚度覆盖率(例如,侧壁上的密封件125的厚度与上部部分上的密封件125的厚度的比)可以为约1:1。

74.在稍后过程动作期间,可与堆叠结构100的其它暴露的材料(例如,硬掩模材料或另一导电材料)相比,取决于密封件125的蚀刻速率选择性来选择密封件125的碳化硅材料。可选择密封件125的碳含量以展现与在稍后过程动作期间欲移除的其它暴露材料大体上相似的蚀刻速率。选择密封件125,以使得可较之其它经暴露材料在较高蚀刻选择性的情况下以相对较快的蚀刻速率移除密封件125的一部分。通过增加或减少密封件125的碳含量,可裁适密封件125的蚀刻速率及蚀刻速率选择性。仅通过实例,对于给定的干式蚀刻化学品及/或过程条件,较之在碳化硅材料包含较低量的碳,在碳化硅材料包含较高量的碳的情况下,可以较快蚀刻速率蚀刻密封件125。例如,密封件125及硬掩模材料可展现相似的蚀刻速率及蚀刻速率选择性,以使得可在随后的过程动作期间大体上同时移除密封件125及硬掩模材料。密封件125的碳化硅材料还可在进行后续过程动作之前对用于清洁堆叠结构100的湿式蚀刻化学品及/或过程条件提供抗蚀刻性。例如,密封件125的碳化硅材料可大体上抵抗水性氟化氢(hf)湿式蚀刻化学品,例如用于清洁堆叠结构100的蚀刻化学品。

75.填充材料140可形成在相邻堆叠105之间的开口115

′

中,如在图6中所展示。填充材料140可例如为电绝缘材料,例如介电材料。填充材料140可为部分的牺牲材料,因为在完成包含堆叠结构100的电子装置之前,随后部分地移除填充材料140。可例如在电子装置的第一叠组完成之前部分地移除填充材料140。替代地,填充材料140可存在于包含堆叠结构100的电子装置中。填充材料140例如可为二氧化硅、氮化硅、氮氧化硅、羰基硅、旋涂介电材料(sod)、bpsg、bsg、气隙或另一介电材料。根据本公开的实施例的碳化硅材料还可用作填充材料140,使得碳化硅材料大体上完全填充开口115

′

。在一些实施例中,填充材料140为旋涂式二氧化硅。在其它实施例中,填充材料140为高质量二氧化硅。由于根据本公开的实施例的密封件125不产生瓶颈或面包条化,因此填充材料140可大体上完全填充开口115

′

,如在图6中所展示。开口115

′

可经大体上完全填充而无需在填充材料140中形成空隙。随后可例如通过化学机械平坦化(cmp)来移除堆叠105上方的过量填充材料140。还可将密封件125的一部分及任选罩盖135从堆叠105的上部表面移除,从而暴露出堆叠105的硬掩模材料或电极材料,如由图6中的虚线所展示。然而,密封件125及罩盖135保留在堆叠105的侧壁上。如果填充材料140为介电材料,那么介电材料可使电子装置的存储器单元彼此隔离,且还可在形成电子装置的后续过程动作期间提供机械支撑。

76.堆叠结构100还可在密封件125的上部表面上包含任选罩盖135,如在图6中所展示。罩盖135可原位或非原位形成在密封件125上。出于说明的目的,在图6中夸大罩盖135相对于密封件125的厚度的厚度。罩盖135可在密封件125与随后形成的填充材料140之间提供经改善的界面性质,从而使得填充材料140能够形成在开口115

′

中而不会形成空隙。罩盖135可例如为高质量的氧化硅材料。罩盖135可通过例如常规ald过程的ald过程形成在密封件125上方。罩盖135可为高度保形的且展现高度的厚度均匀性。

77.根据本公开的实施例的密封件125的碳化硅材料向堆叠结构100提供屏障性质,从

而使得能够形成密封件125而不会在相邻堆叠105之间造成面包条化。由于使用较少侵蚀性的过程条件来形成密封件125,因此甚至当密封件125直接形成在堆叠105的材料上时,根据本公开的实施例的密封件125的形成也不会损坏或以其它方式影响堆叠105的材料,例如硫属化物材料或碳材料。因此,与用常规密封材料观察到的硫属化物损失相比,硫属化物材料的损失可大体上缩减或消除。

78.可使包含堆叠105、衬里110b及/或密封件125的碳化硅材料以及填充材料140的堆叠结构100经受常规额外处理动作以形成包含堆叠结构100的电子装置。通过使用衬里110b的碳化硅材料,当暴露于干式蚀刻化学品时可选择性地蚀刻导电材料105e以图案化导电材料105e。另外,当在进行额外的过程动作之前,当暴露于用于从堆叠结构100移除残留物的湿式蚀刻化学品时,衬里110b及/或密封件125的碳化硅材料的抗蚀刻性可增加。包含堆叠105、衬里110b的碳化硅材料及/或密封件125的碳化硅材料的堆叠结构100还可向包含堆叠结构100的电子装置提供减小的寄生电容。

79.由于衬里110及/或密封件125包含碳化硅材料而非常规氧化硅材料,因此根据本公开的实施例的碳化硅材料可向含有碳化硅材料的电子装置提供蚀刻选择性、抗蚀刻性、屏障性质或硫属化物损失中的一或多者。通过形成包含碳化硅材料的衬里110及/或密封件125,缩减堆叠中的敏感材料(例如,硫属化物材料,碳材料)的损失。堆叠105的材料上方的衬里110及/或密封件125可缩减堆叠105的材料的再沉积,这不合意地造成泄漏。通过在碳化硅材料中包含碳,碳化硅材料在电子装置的制作期间相对于电子装置的其它暴露材料提供蚀刻选择性。碳化硅材料的蚀刻选择性可介于氧化硅的蚀刻选择性与例如氧化铝或氧化铪的高k介电材料的蚀刻选择性(从约19到约20)之间。如所属领域中已知的,由于高电容,使用氧化铝或氧化铪导致高尖峰电流。使用根据本公开的实施例的碳化硅材料可减少与高尖峰电流及高电容相联关的问题。与常规氧化硅衬里材料相比,根据本公开的实施例的碳化硅材料可通过干式蚀刻化学品选择性地蚀刻,所述干式蚀刻化学品用于形成含有碳化硅材料的电子装置。与常规氧化硅衬里材料相比,根据本公开的实施例的碳化硅材料还较耐受湿式蚀刻化学品,所述湿式蚀刻化学品用于形成含有碳化硅材料的电子装置。

80.在随后的过程动作期间,可通过常规技术移除堆叠105的硬掩模材料,在堆叠105的其余材料上方形成另一导电材料(例如,导电材料)。可通过常规技术将另一导电材料图案化以形成例如位线(例如,数字线)或在堆叠结构100上触点。另一导电材料可直接接触堆叠105的导电材料,例如经配置为堆叠105的电极的导电材料。如图8中所展示且下文所描述,另一导电材料可经配置为包含堆叠结构100的电子装置的位线806(例如,数字线)。阵列800可包含多个存储器单元804,所述存储器单元布置成行及列且包含堆叠结构100,其每一存储器单元804通过衬里110及/或密封件125及堆叠结构100的填充材料140与其它存储器单元804隔离(例如,电隔离)。包含堆叠结构100的存储器单元804定位于存取线802(例如,字线)与位线806(例如,数字线)之间。

81.因此,公开一种电子装置,其包括堆叠结构,所述堆叠结构包括一或多个材料堆叠及一或多种碳化硅材料。所述一或多个堆叠的所述材料包括单一硫属化物材料以及导电碳材料、导电材料及硬掩模材料中的一或多者。一或多种碳化硅材料相邻于一或多个材料堆叠且包括碳化硅、羰基硅、碳氮化硅、羰基氮化硅或硼氮碳化硅。一或多种碳化硅材料还包括硅-碳共价键,且一或多种碳化硅材料经配置为衬里或密封件。

82.因此,公开一种形成电子装置的方法。所述方法包括形成包括一或多种材料的材料堆叠,所述堆叠中的一或多种材料包括硫属化物材料。碳化硅材料是通过自由基化学气相沉积形成的,且相邻于所述材料堆叠。填充材料经形成相邻于碳化硅材料且介于材料堆叠中的相邻堆叠之间。填充材料大体上无空隙。

83.因此,公开一种形成电子装置的方法。所述方法包括形成包括硫属化物材料及一或多种额外材料的材料堆叠。材料堆叠中的相邻堆叠由开口间隔开。第一碳化硅材料通过自由基化学气相沉积保形地形成,且相邻于材料堆叠。移除第一碳化硅材料的相邻于材料堆叠中的导电材料相邻的部分,且通过开口移除导电材料的经暴露部分。通过自由基化学气相沉积保形地形成第二碳化硅材料。第二碳化硅材料相邻于第一碳化硅材料且在开口中。在相邻材料堆叠之间形成填充材料,所述填充材料大体上无空隙。

84.可进行额外处理动作以形成包含存储器单元804的阵列800的电子装置900,所述存储器单元包含根据本公开的实施例的堆叠结构100,如图9中所展示。通过常规技术进行后续的过程动作,本文中不对其进行详细描述。包含堆叠结构100的存储器单元804定位于存取线802(例如,字线)与位线806(例如,数字线)之间。存取线802可与例如堆叠105的导电材料105e(例如钨)或电极(例如,底部电极)电接触,且位线806可与堆叠105的另一电极(例如,顶部电极)电接触。位线806可直接覆盖包含堆叠结构100的存储器单元804的行或列,并与其顶部电极接触。存取线802中的每一者可在第一方向上延伸且可连接一行存储器单元804(例如,相变存储器单元)。位线806中的每一者可在至少大体上垂直于第一方向的第二方向上延伸,且可连接一列存储器单元804。可控制施加到存取线802及位线806的电压,使得可在至少一个存取线802及至少一个位线806的相交点处选择性地施加电场,从而使得包含根据本公开的实施例的堆叠结构100的存储器单元804能够选择性地操作。包含存储器单元804阵列800的电子装置900可包含含有一或多个材料堆叠的存储器单元804,其中材料中的一或多者对氧化、热等敏感。如上文所论述,敏感材料可包含硫属化物材料、碳材料等。仅通过实例,电子装置可为3d电子装置,例如3d交叉点存储器装置,pcram存储器装置或包含一或多种对氧化及/或热敏感的材料的其它存储器装置。根据本公开的实施例的碳化硅材料还可用于期望保护敏感材料的其它电子装置中,例如用于dram存储器装置中。

85.因此,公开包括存储器单元阵列的电子装置。存储器单元包括材料堆叠,所述材料堆叠包括硫属化物材料及一或多种额外材料。碳化硅材料中的一或多者相邻于材料堆叠,一或多种碳化硅材料包括硅原子及碳原子,且一或多种碳化硅材料包括硅-碳共价键。

86.在图9的功能框图中示意性地展示根据本公开的实施例的电子装置900(例如,pcram存储器装置)。电子装置900可包含在至少一个位线806与至少一个源极线922之间的至少一个存储器单元804。存储器单元804可大体上类似于上文参考图8所描述的存储器单元804。存储器单元804可耦合到存取装置910。存取装置910可充当用于启用及停用穿过存储器单元804的电流的开关。通过非限制性实例,存取装置910可为晶体管(例如,场效应晶体管、双极结型晶体管等),其栅极连接到存取线(例如,存取线802)。存取线802可在大体上垂直于位线806的方向的方向上延伸。位线806及源极线922可连接到用于编程及读取存储器单元804的逻辑。控制多路复用器930可具有连接到位线806的输出。控制多路复用器930可由控制逻辑线932控制,以在连接到脉冲产生器926的第一输入与到读取感测逻辑928的第二输入之间进行选择。

87.在编程操作期间,可将大于存取装置910的阈值电压的电压施加到存取线802,以接通存取装置910。接通存取装置910通过存储器单元804完成源极线922与位线806之间的电路。在接通存取装置910之后,偏压产生器929可通过脉冲产生器926在位线806与源极线922之间建立偏压电压电位差。在读取操作期间,偏压产生器929可通过读取感测逻辑928在位线806与源极线922之间建立读取偏压电压电位差。读取偏压电压可低于重设偏压电压。读取偏压电压使得电流能够流动穿过存储器单元804。举例来说,对于给定的读取偏压电压,如果堆叠105的硫属化物材料处于高电阻状态(例如,重设状态),那么较之在堆叠105的硫属化物材料处于低电阻状态(例如,设定状态)的情况下,相对较小电流流动穿过存储器单元804。可在读取操作期间流动穿过存储器单元804的电流量与由读取感测逻辑928(例如,感测放大器)的参考输入进行比较,以区分存储在存储器单元804中的数据是逻辑“1”还是逻辑“0”。在一些实施例中,源极线922可与存取线802重合,且存取装置910可不存在。脉冲产生器926及读取感测逻辑920可以足以使存储器单元804自选的电压对存取线802加偏压。

88.如图10中所展示,还公开系统1000,且其包含根据本公开的实施例的一或多个存储器单元804。图10为根据本文中所描述的一或多个实施例实施的系统1000的简化框图。系统1000可包括例如计算机或计算机硬件组件、服务器或其它网络硬件组件、蜂窝电话、数字相机、个人数字助理(pda),便携式媒体(例如,音乐)播放器,具有wi-fi或蜂窝功能的平板计算机,例如或平板计算机、电子书、导航装置等。系统1000包含至少一个电子装置900,所述电子装置包含存储器单元804,所述存储器单元包含如先前所描述的堆叠结构100。系统1000可进一步包含至少一个处理器1002,例如微处理器,以控制系统1000中的系统功能及请求的处理。处理器1002及系统1000的其它子组件可包含根据本公开的实施例的存储器单元804。处理器1002可任选地包含一或多个如先前所描述的电子装置900。

89.系统1000可包含与处理器1002可操作地通信的电源1004。举例来说,如果系统1000为便携式系统,那么电源1004可包含燃料电池、功率清除装置、永久电池、可更换电池及可再充电电池中的一或多者。电源1004还可包含ac适配器。因此,举例来说,系统1000可插入到壁式插座中。举例来说,电源1004还可包含dc适配器,使得系统1000可插入到车载点烟器或车载电源端口。

90.各种其它装置可耦合到处理器1002,这取决于系统1000执行的功能。举例来说,输入装置1006可耦合到处理器1002。输入装置1006可包含输入装置,例如按钮、开关、键盘、光笔、鼠标、数字板及手写笔、触摸屏、语音辨识系统、麦克风,或其组合。显示器1008也可耦合到处理器1002。显示器1008可包含lcd显示器、sed显示器、crt显示器、dlp显示器、等离子体显示器、oled显示器、led显示器、三维投影、音频显示器或其组合。此外,rf子系统/基带处理器1010也可耦合到处理器1002。rf子系统/基带处理器1010可包含耦合到rf接收器并耦合到rf发射器的天线(未展示)。通信端口1012或多于一个通信端口1012也可耦合到处理器1002。举例来说,通信端口1012可经调适以耦合到一或多个外围装置1014(例如,调制解调器、打印机、计算机、扫描仪或相机),或耦合到网络(例如,局域网、远程区域网络、内联网或互联网)。

91.处理器1002可通过实施存储在存储器中的软件程序来控制系统1000。举例来说,

软件程序可包含操作系统、数据库软件、绘图软件、字处理软件、媒体编辑软件或媒体播放软件。存储器可操作地耦合到处理器1002以存储并促进各种程序的执行。举例来说,处理器1002可耦合到系统存储器1016,所述系统存储器可包含相变随机存取存储器(pcram)及其它已知存储器类型。系统存储器1016可包含易失性存储器、非易失性存储器或其组合。系统存储器1016通常较大,使得其可存储动态加载的应用程序及数据。在一些实施例中,系统存储器1016可包含电子装置,例如图9的电子装置900,及存储器单元,例如上文参考图8所描述的存储器单元804。

92.处理器1002还可耦合到非易失性存储器1018,这并不暗示系统存储器1016必须为易失性。非易失性存储器1018可包含欲与系统存储器1016结合使用的pcram。非易失性存储器1018的大小通常经选择为以正好大到足以存储任何必要操作系统、应用程序及固定数据。另外,举例来说,非易失性存储器1018可包含高容量存储器,例如磁盘驱动器存储器,例如混合式驱动器(包含电阻式存储器)或其它类型的非易失性固态存储器。在一些实施例中,非易失性存储器1018可包含电子装置,例如图9的电子装置900,及存储器单元,例如上文参考图8所描述的存储器单元804。

93.因此,公开一种系统,所述系统包括输入装置、输出装置及可操作地耦合到输入装置及输出装置的处理器。电子装置可操作地耦合到处理器,且包括存储器单元,所述存储器单元包括材料堆叠,所述材料堆叠包括单一硫属化物材料及一或多种额外材料。至少一种碳化硅材料垂直相邻于材料堆叠且在单一硫属化物材料的侧壁上。至少一种碳化硅材料的厚度沿着其长度大体上均匀。

94.以下实例用于更详细地阐释本公开的实施例。对于本公开的范围来说,这些实例不应解释为是穷举的或排他性。

95.实例

96.实例1

97.通过使用于形成碳化硅材料的硅-碳前体的量及在等离子体处理动作中使用的o2的量变化,来形成展现不同碳含量的羰基硅材料的十个样本。在空白晶片(blanket wafer)上形成羰基硅材料。表1中展示硅-碳前体的量与o2的量的比率。硅-碳前体为液体前体、八甲基环四硅氧烷(c8h

24

o4si4,摩尔质量296.62,蒸气压力:在25℃下约为124.5pa+/-约6.2pa),且可从西格玛奥瑞奇公司(sigma-aldrich)(密苏里州圣路易斯市)商购。还使o2等离子体处理循环的数目(例如,单个及/或多个沉积及处理循环)变化以确定对羰基硅材料的碳含量的影响。

98.表1:用于形成羰基硅材料的条件

[0099][0100]

在范围从约200w到约2kw的rf功率下,远离晶片的表面产生远程氢等离子体。使用远程等离子体设计,其具有所谓的“下游等离子体”配置,使用法拉第栅格过滤掉不需要的离子电子,及不需要的uv辐射。远程等离子体设计仅使得所要自由基及中性物种(例如,氢自由基)与硅-碳前体起反应以形成反应产物。液体硅-碳前体从整体货柜供应,并在大于或等于约20psig(+/-约10psig)(大于或等于约239,248帕)(+/-约170,301帕))的压力下以大于或等于约50ml/分钟的流速引入到包含空白晶片的腔室中,其中从整体货柜内部对液体递送流施加额外推动压力。液态硅-碳前体的引入发生在空白晶片的表面附近或上方。随后用氢自由基、自由基反应及o2等离子体处理活化硅-碳前体产生羰基硅薄膜。

[0101]

如在图11中所展示,形成包含在15at.%与26at.%之间的碳的碳化硅材料。碳化硅材料的氧含量在图12中展示,且范围在约34at.%与45at.%之间。

[0102]

实例2

[0103]

通过常规技术测量实施例1的羰基硅材料中的一者在不同浓度的hf水溶液中的湿式蚀刻速率。在空白晶片(blanket wafer)上形成羰基硅材料。hf水溶液包含200:1hf、100:1hf及10:1hf。如在图13a到13d中所展示,即使使用最浓hf水溶液,也大体上未观察到碳化硅材料的蚀刻(约)。

[0104]

实例3

[0105]

通过常规技术计算或测量羰基硅材料(实施例1中的样本1到10)的密度、泄漏密度及介电常数,并将其展示于表2中。在空白晶片(blanket wafer)上形成羰基硅材料。

[0106]

表2:羰基硅材料的性质

[0107][0108]

如表2中所展示,增加o2等离子体处理循环的数目增加羰基硅材料的密度。暴露于x数目个循环的样本具有在约1.8g/cm3与1.9g/cm3之间的密度,而暴露于2x数目个循环的样本具有约2.0g/cm3的密度。羰基硅材料的介电常数低于氮化硅的介电常数(约8)。

[0109]

实例4

[0110]

通过常规技术确定由在包含硫属化物材料的堆叠上方形成羰基硅材料引起的硫属化物损失的程度。羰基硅材料形成在堆叠的侧壁上。包含硫属化物材料的堆叠类似于图1中示意性说明的堆叠,且为高纵横比的堆叠。羰基硅材料包含5at.%的碳、13at.%的碳、14at.%的碳或15at.%的碳。如在图14中所展示,对于在堆叠材料上方形成羰基硅材料,在堆叠材料上方形成经处理羰基硅材料,以及在堆叠材料上方形成常规氧化硅材料,锗损失百分比为相当的。如在图15中所展示,与在堆叠材料上方形成常规氧化硅材料相比,对于在堆叠材料上方形成羰基硅材料及在堆叠材料上方形成经处理羰基硅材料,铟损失百分比较少。

[0111]

本公开的额外非限制性实例实施例在下文进行阐述。

[0112]

实施例1.一种电子装置,其包括:堆叠结构,其包括:一或多个材料堆叠,所述一或多个堆叠的所述材料包括单一硫属化物材料以及导电碳材料、导电材料及硬掩模材料中的一或多者;及一或多种碳化硅材料,其相邻于所述一或多个材料堆叠,所述一或多个碳化硅材料包括碳化硅、羰基硅、碳氮化硅、羰基氮化硅或硼氮碳化硅,所述一或多个碳化硅材料包括硅-碳共价键,且所述一或多个碳化硅材料经配置为衬里或密封件。

[0113]

实施例2.根据实施例1所述的电子装置,其中所述一或多种碳化硅材料中的第一碳化硅材料直接接触相邻于所述材料堆叠的衬里材料。

[0114]

实施例3.根据实施例1所述的电子装置,其中所述一或多种碳化硅材料中的第一碳化硅材料直接接触所述材料堆叠的侧壁。

[0115]

实施例4.根据实施例1到3中任一实施例所述的电子装置,其中所述一或多种碳化硅材料中的第二碳化硅材料直接接触所述第一碳化硅材料。

[0116]

实施例5.根据实施例1到3中任一实施例所述的电子装置,其中所述一或多种碳化硅材料中的第二碳化硅材料直接接触相邻于所述材料堆叠的密封材料。

[0117]

实施例6.根据实施例1到5中任一实施例所述的电子装置,其中所述一或多种碳化硅材料包括从约2原子百分比(at.%)到约50at.%碳的碳含量。

[0118]

实施例7.根据实施例1到6中任一实施例所述的电子装置,其中所述一或多种碳化硅材料包括均质化学组合物。

[0119]

实施例8.根据实施例1到6中任一实施例所述的电子装置,其中所述一或多种碳化硅材料包括横跨所述一或多种碳化硅材料的厚度的碳梯度。

[0120]

实施例9.根据实施例1到8中任一实施例所述的电子装置,其中经配置为衬里的所述一或多种碳化硅材料的化学组合物包括与经配置为密封件的所述一或多种碳化硅材料不同的化学组合物。

[0121]

实施例10.根据实施例1到8中任一实施例所述的电子装置,其中经配置为衬里的所述一或多种碳化硅材料的化学组合物包括与经配置为密封件的所述一或多种碳化硅材料相同的化学组合物。

[0122]

实施例11.根据实施例1到10中任一实施例所述的电子装置,其中相邻堆叠依从约10nm到约30nm的半节距间隔开。

[0123]

实施例12.根据实施例1到11中任一实施例所述的电子装置,其进一步包括与所述一或多种碳化硅材料直接接触的填充材料。

[0124]

实施例13.根据实施例1到12中任一实施例所述的电子装置,其中所述填充材料包括所述一或多种碳化硅材料的额外部分。

[0125]

实施例14.一种电子装置,其包括:存储器单元阵列,所述存储器单元包括:材料堆叠,其包括硫属化物材料及一或多种额外材料;及一或多种碳化硅材料,其相邻于所述材料堆叠,所述一或多种碳化硅材料包括硅原子及碳原子,且所述一或多种碳化硅材料包括硅-碳共价键;及存取线及位线,其电耦合到所述存储器单元。

[0126]

实施例15.根据实施例14所述的电子装置,其中所述材料堆叠包括从约10:1到约50:1的纵横比。

[0127]

实施例16.根据实施例14或实施例15所述的电子装置,其中所述材料堆叠包括单一硫属化物材料。

[0128]

实施例17.一种形成电子装置的方法,其包括:形成包括一或多种材料的材料堆叠,所述堆叠中的所述一或多种材料包含硫属化物材料;通过自由基化学气相沉积形成碳化硅材料,所述碳化硅材料相邻于所述材料堆叠;及形成填充材料,所述填充材料相邻于所述碳化硅材料且在所述材料堆叠中的相邻堆叠之间,所述填充材料大体上无空隙。

[0129]

实施例18.根据实施例17所述的方法,其中形成包括一或多种材料的材料堆叠包括形成包括硫属化物材料的所述材料堆叠,所述硫属化物材料包括铟。

[0130]

实施例19.根据实施例17所述的方法,其中形成包括一或多种材料的材料堆叠包括形成包括硫属化物材料的所述材料堆叠,所述硫属化物材料包括锗。

[0131]

实施例20.根据实施例17到19中任一实施例所述的方法,其中形成包括一或多种材料的材料堆叠包括形成包括单一硫属化物材料的所述材料堆叠。

[0132]

实施例21.根据实施例17到20中任一实施例所述的方法,其中通过自由基化学气相沉积形成碳化硅材料包括由包括硅-碳共价键的单一硅-碳前体形成所述碳化硅材料。

[0133]

实施例22.根据实施例17到21中任一实施例所述的方法,其进一步包括由硅-碳前体形成所述碳化硅材料,所述硅-碳前体包括硅-氧共价键及硅-氮共价键中的一或多者。

[0134]

实施例23.根据实施例17到22中任一实施例所述的方法,其中通过自由基化学气

相沉积形成碳化硅材料包括形成衬里,所述衬里包括相邻于所述材料堆叠的所述碳化硅材料。

[0135]

实施例24.根据实施例17到22中任一实施例所述的方法,其中通过自由基化学气相沉积形成碳化硅材料包括形成密封件,所述密封件包括相邻于所述材料堆叠的所述碳化硅材料。

[0136]

实施例25.根据实施例17到24中任一实施例所述的方法,其进一步包括将所述碳化硅材料暴露于氧等离子体处理。

[0137]

实施例26.根据实施例17到25中任一实施例所述的方法,其中将所述碳化硅材料暴露于氧等离子体处理包括相对于初始形成的所述碳化硅材料的碳含量缩减所述碳化硅材料的碳含量。

[0138]

实施例27.根据实施例17到26中任一实施例所述的方法,其中形成相邻于所述碳化硅材料的填充材料包括将所述碳化硅材料的额外部分形成为所述填充材料。

[0139]

实施例28.一种形成电子装置的方法,其包括:形成材料堆叠,所述材料堆叠包括硫属化物材料及一或多个额外材料,所述材料堆叠中的相邻堆叠由开口间隔开;通过自由基化学气相沉积保形地形成第一碳化硅材料,所述第一碳化硅材料相邻于所述材料堆叠;将所述第一碳化硅材料相邻于所述材料堆叠的导电材料的一部分移除;通过所述开口移除所述导电材料的经暴露部分;通过自由基化学气相沉积保形地形成第二碳化硅材料,所述第二碳化硅材料相邻于所述第一碳化硅材料且在所述开口中;及在所述材料的所述毗邻堆叠之间形成填充材料,所述填充材料大体上无空隙。

[0140]

实施例29.根据实施例28所述的方法,其中保形地形成第一碳化硅材料包括保形地形成包括所述碳化硅材料的衬里。

[0141]

实施例30.根据实施例29所述的方法,其中保形地形成第二碳化硅材料包括保形地形成包括所述碳化硅材料的密封件,所述密封件展现大于所述衬里的厚度的厚度。

[0142]

实施例31.一种系统,其包括:输入装置;输出装置;处理器,其可操作地耦合到所述输入装置及所述输出装置;及电子装置,其可操作地耦合到所述处理器,所述电子装置包括存储器单元,所述存储器单元包括:材料堆叠,所述材料堆叠包括单一硫属化物材料及一或多种额外材料;及至少一种碳化硅材料,其垂直相邻于所述材料堆叠且在所述单一硫属化物材料的侧壁上,所述至少一种碳化硅材料的厚度沿其长度大体上均匀。

[0143]

虽然已经结合诸图描述了某些说明性实施例,但所属领域的技术人员将认识并了解,本公开所涵盖的实施例不限于本文中明确显示及描述的那些实施例。确切地说,可在不脱离本公开所涵盖的实施例(例如权利要求书中所主张的那些实施例,包含合法等效物)的范围的情况下对本文中所描述的实施例进行诸多添加、删除及修改。另外,来自一个所公开实施例的特征可与另一所公开实施例的特征组合,同时仍然囊括在本公开的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1