使用场效应晶体管结构中的随机阈值电压变化作为物理不可克隆功能的安全芯片识别的制作方法

背景技术:

1、本发明一般涉及半导体结构及其形成方法。更具体地说,本发明涉及使用场效应晶体管(fet)结构中的随机阈值电压(vth)变化作为物理不可克隆功能(puf)的安全芯片识别。

2、puf是物理定义的“数字指纹”,其用作半导体器件(例如微处理器)的唯一标识。puf是体现在物理结构中的物理实体。puf基于在半导体制造期间自然发生的独特物理变化。puf可以在集成电路中实现。puf还可以用于具有高安全性要求的应用中,例如密码术。

技术实现思路

1、根据本发明的一个实施例,提供了一种半导体结构。半导体结构可以包括一个或多个金属栅极、在一个或多个金属栅极下方的一个或多个沟道、将一个或多个金属栅极与一个或多个沟道分离的栅极电介质层、以及嵌入在栅极电介质层中的高k材料。高k材料和栅极电介质层两者都可以与一个或多个沟道直接接触。高k材料可在一个或多个金属栅极中提供阈值电压变化。高k材料是第一高k材料或第二高k材料。半导体结构可以仅包括嵌入在栅极电介质层中的第一高k材料。半导体结构可以仅包括嵌入在栅极电介质层中的第二高k材料。半导体结构可以包括嵌入在栅极电介质层中的第一高k材料和第二高k材料两者。

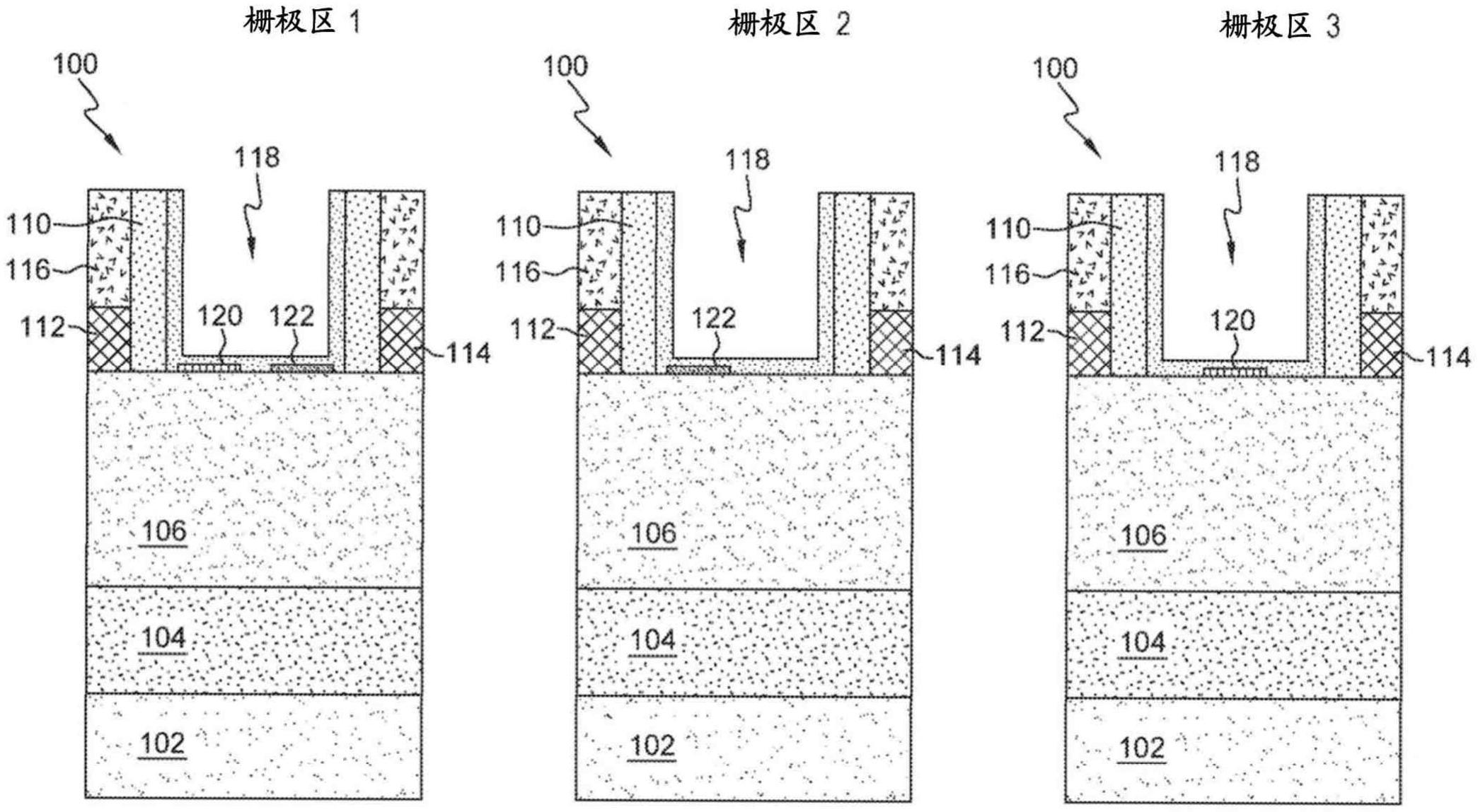

2、根据本发明的另一实施例,提供一种半导体结构。半导体结构可以包括一个或多个场效应晶体管的一个或多个栅极区。一个或多个栅极区可以在一个或多个沟道之上。半导体结构可以包括通过栅极电介质层与一个或多个沟道分离的金属栅极、嵌入在栅极电介质层中的高k材料以及层间电介质。高k材料和栅极电介质层两者都可以与一个或多个沟道直接接触。层间电介质可以围绕一个或多个栅极区。高k材料可以是第一高k材料或第二高k材料。半导体结构可以仅包括嵌入在栅极电介质层中的第一高k材料。半导体结构可以仅包括嵌入在栅极电介质层中的第二高k材料。半导体结构可以包括嵌入在栅极电介质层中的第一高k材料和第二高k材料两者。高k材料可在一个或多个金属栅极中提供阈值电压变化。

3、根据本发明的另一实施例,提供了一种方法。该方法可以包括在沟道上方形成一个或多个栅极区,使高k材料在一个或多个栅极区中随机成核,以及在一个或多个栅极区中的每一个中沉积栅极电介质层。使所述高k材料在所述一个或多个栅极区中随机成核可促进所述一个或多个栅极区内的随机阈值电压。所述一个或多个栅极区内的所述随机阈值电压可用作物理不可克隆功能。一个或多个栅极区可以由栅极间隔件包围。栅极电介质层可以覆盖沟道的整个表面。第二高k材料可以部分地覆盖沟道的表面。高k材料可以是第一高k材料或第二高k材料。该方法可以包括仅将第一高k材料嵌入栅极电介质层中。该方法可以包括仅将第二高k材料嵌入栅极电介质层中。该方法可以包括将第一高k材料和第二高k材料两者嵌入栅极电介质层中。该方法可以包括形成第一源漏和第二源漏,在栅极电介质层的顶部上沉积金属栅极,在一个或多个栅极区周围沉积层间电介质,以及形成第一源漏接触和第二源漏接触。第一源漏和第二源漏可以通过栅极间隔件与一个或多个栅极区分离。层间电介质可以在第一源漏和第二源漏的顶部上。

技术特征:

1.一种方法,包括:

2.根据权利要求1所述的方法,其中所述高k材料是第一高k材料或第二高k材料。

3.根据权利要求2所述的方法,其中,仅所述第一高k材料被嵌入在所述栅极电介质层中。

4.根据权利要求2所述的方法,其中,仅所述第二高k材料被嵌入在所述栅极电介质层中。

5.根据权利要求2所述的方法,其中所述第一高k材料和所述第二高k材料两者均被嵌入在所述栅极电介质层中。

6.根据权利要求1所述的方法,其中使所述高k材料在所述一或多个栅极区中随机成核促进所述一或多个栅极区内的随机阈值电压,所述一或多个栅极区内的所述随机阈值电压用作物理不可克隆功能。

7.根据权利要求1所述的方法,还包括:

8.一种半导体结构,包括:

9.根据权利要求8所述的半导体结构,其中所述高k材料在所述一个或多个金属栅极中提供阈值电压变化。

10.根据权利要求8所述的半导体结构,其中所述高k材料是第一高k材料或第二高k材料。

11.根据权利要求10所述的半导体结构,其中,仅所述第一高k材料被嵌入在所述栅极电介质层中。

12.根据权利要求10所述的半导体结构,其中,仅所述第二高k材料被嵌入在所述栅极电介质层中。

13.根据权利要求10所述的半导体结构,其中所述第一高k材料和所述第二高k材料两者均被嵌入在所述栅极电介质层中。

14.根据权利要求10所述的半导体结构,其中所述第一高k材料由氧化铝制成,并且所述第二高k材料由氧化镧制成。

15.一种半导体结构,包括:

16.根据权利要求15所述的半导体结构,其中所述高k材料是第一高k材料或第二高k材料。

17.根据权利要求16所述的半导体结构,其中,仅所述第一高k材料被嵌入在所述栅极电介质层中。

18.根据权利要求16所述的半导体结构,其中,仅所述第二高k材料被嵌入在所述栅极电介质层中。

19.根据权利要求16所述的半导体结构,其中所述第一高k材料和所述第二高k材料两者均被嵌入在所述栅极电介质层中。

20.根据权利要求15所述的半导体结构,其中所述高k材料在所述一个或多个金属栅极中提供阈值电压变化。

技术总结

一种半导体结构可以包括一个或多个金属栅极、在一个或多个金属栅极下方的一个或多个沟道、将一个或多个金属栅极与一个或多个沟道分离的栅极电介质层、以及嵌入在栅极电介质层中的高k材料。高k材料和栅极电介质层两者都可以与一个或多个沟道直接接触。高k材料可在一个或多个金属栅极中提供阈值电压变化。高k材料是第一高k材料或第二高k材料。半导体结构可以仅包括嵌入在栅极电介质层中的第一高k材料。半导体结构可以仅包括嵌入在栅极电介质层中的第二高k材料。半导体结构可以包括嵌入在栅极电介质层中的第一高k材料和第二高k材料两者。

技术研发人员:C·J·欧特瑞,A·雷茨尼采克,B·海克马特少塔巴瑞,张婧芸,谢瑞龙

受保护的技术使用者:国际商业机器公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!