电子器件和用于其的封装和半导体芯片的制作方法

提供了一种电子器件。此外,还提供了用于这种电子器件的封装和半导体芯片。

背景技术:

1、文献us 2013/0207157a1涉及一种具有晶片的反向导电功率半导体器件,该器件包括多个二极管单元和多个igct单元。

2、要解决的问题是提供一种能够以可靠方式电连接的电子器件。

技术实现思路

1、这个目的尤其通过独立专利权利要求中限定的电子器件、封装、和半导体芯片实现。优选的进一步发展构成从属权利要求的主题。

2、例如,电子器件在接触面处具有几何结构,以补偿被配置为压在一起以实现干式电接触的电极的不同尺寸。通过补偿不同尺寸,接触压力对于所有相应电极可以大致相同。接触面是(例如)电接触面,使得电子器件被配置为通过接触面被馈送以电流。

3、在至少一个实施例中,电子器件包括:

4、-半导体芯片,具有电接触金属化层,以及

5、-封装,具有电接触盘,其中

6、-电接触金属化层和电接触盘在接触面上直接接触,使得半导体芯片与封装电连接,并且

7、-在接触面处,电接触金属化层和电接触盘中的至少一者包括构造为至少一个凹陷区域的几何结构。

8、在至少一个实施例中,电子器件包括:

9、-半导体本体,被施加有电接触金属化层和另一电接触金属化层,该另一电接触金属化层在与电接触金属化层相对的另一接触面上,以及

10、-封装,具有电接触盘,

11、其中

12、-电接触金属化层和电接触盘在接触面上直接接触,使得半导体本体与封装电连接,

13、-在整个接触面处,电接触金属化层和电接触盘中的至少一者包括构造为至少一个凹陷区域的几何结构,该几何结构在整个接触面上延伸,并且

14、-该几何结构的平均宽度比另一电接触金属化层的结构尺寸小至少1/2。

15、因此,根据至少一个实施例,从相应金属化层的俯视图中看,几何结构可以比另一电接触金属化层具有更小的周期性或横向特征长度。至少一个凹陷区域的平均宽度比另一电接触金属化层沿相同方向的结构尺寸(例如)小至少4/5或至少9/10。周期性或横向特征长度指(例如)与形成至少一个凹陷区域的凹陷的长度方向垂直的方向。通过这样的设计,在另一电接触金属化层的结构尺寸的尺度上,几何结构的特征可以被认为是均匀分布的,使得电接触金属化层和另一电接触金属化层之间的精确相对位置可以变得非常不重要。

16、根据至少一个实施例,半导体芯片选自包括以下各项的群组:二极管、金属氧化物半导体场效应晶体管(mosfet)、金属绝缘体半导体场效应晶体管(misfet)、绝缘栅双极晶体管(igbt)、双极结型晶体管(bjt)、晶闸管、栅极关断晶闸管(gto)、栅极整流晶闸管(gct)、和结型栅场效应晶体管(jfet)。例如,半导体芯片是集成栅极换向晶闸管(igct)或具有嵌入式反并联二极管的igct。

17、例如,半导体芯片和电子器件被配置为处理至少50a或至少0.5ka或至少5ka的最大电流。相应地,半导体芯片和电子器件可以是高功率组件。

18、例如,半导体芯片包括半导体本体。半导体本体可以包括一种或多种半导体材料。从俯视图中看,半导体芯片和/或半导体本体可以是多边形形状(例如,矩形),也可以是圆形形状(例如,圆形)。如果半导体芯片是从半导体晶片上切下的,则半导体芯片在俯视图中看可以是多边形;如果半导体芯片是半导体晶片或半导体晶片的最大部分,则半导体芯片可以是圆或圆段,例如,在俯视图中看中心角大于180°。

19、根据至少一个实施例,电接触金属化层是半导体芯片的集成部件。因此,在不破坏半导体芯片的情况下,不可以从半导体芯片上去除电接触金属化层。

20、根据至少一个实施例,封装是多部分形式的,因此,封装可以包括除电接触盘之外的其他部件。

21、根据至少一个实施例,电接触金属化层和电接触盘在接触面上直接接触,使得半导体芯片与封装电连接,从而在电接触金属化层和电接触盘之间不存在额外的电连接装置。这种配置通常称为干接触。例如,干接触中没有焊料。电接触金属化层和电接触盘可以可逆地被从彼此移除。

22、根据至少一个实施例,在接触面处,电接触金属化层和/或电接触盘包括几何结构。接触面可以是与半导体芯片的主侧平行或近似平行的平面。

23、几何结构被构造为凹陷区域。因此,由于该结构,电接触金属化层和接触面之间的接触面积减小。该结构(例如)位于电接触金属化层和/或电接触盘的外轮廓线内。因此,凹进区域相对于接触面被后退设置。例如,通过从电接触金属化层和/或电接触盘移除材料或通过结构化制造电接触金属化层和/或电接触盘来产生凹陷区域,但是可选地,凹陷区域也可以是通过向电接触金属化层和/或电接触盘施加额外的材料以在在其他方面更薄的电接触金属化层和/或电接触盘的基准面上产生高度提升而产生的。

24、根据至少一个实施例,电接触金属化层包括al和ag中的至少一种。替代地或附加地,电接触盘包括mo、rh、ru、rd、pt、w、和铝石墨中的至少一种。例如,电接触金属化层包括铝或铝合金或者由铝或铝合金组成,并且电接触盘包括钼或钼合金或者由钼或钼合金组成,其中,可以将rh或ru的薄镀层施加到钼或钼合金上,使得电接触盘基本上由钼或钼合金组成。在本文中,“基本上”可以指至少95%或至少99%的质量比例。

25、根据至少一个实施例,电接触金属化层厚度为至少5μm或至少10μm。可选地或附加地,所述厚度为至多100μm或至多50μm。例如,所述厚度为20μm。

26、根据至少一个实施例,电接触盘的厚度至少在0.5mm或至少1.0mm之间。可选地或附加地,所述厚度至多为5mm。

27、根据至少一个实施例,电接触盘面向电接触金属化层的顶面的平均粗糙度为至少0.1μm或至少0.2μm。可选地或另外,所述平均粗糙度(也称为ra)为至多1μm或至多0.5μm。也就是说,电接触盘的顶面可比较地粗糙。由于相对较大的平均粗糙度,在这种情况下,顶面被配置为深入电接触金属化层。例如,电接触盘可以在接触面处穿入电接触金属化层的氧化物层。

28、根据至少一个实施例,电接触金属化层的平均直径为至少1cm或至少3cm。可选地或附加地,所述平均直径为至多25cm或至多16cm。

29、根据至少一个实施例,几何结构的平均宽度为至少0.2mm或至少1mm。替代地或附加地,所述平均宽度为至多10mm或至多5mm。

30、根据至少一种实施例,几何结构的平均深度为至多1μm或至多3μm。替代地或附加地,所述平均深度为至多1mm或至多0.2mm或至多30μm。例如,所述平均厚度为电接触盘的平均粗糙度的至少两倍并且至多20倍。几何结构的平均深度(例如)是至少一个凹陷区域的体积除以所述至少一个凹进区域的占地面积。

31、根据至少一个实施例,几何结构在电接触金属化层和电接触盘中的被提供有该几何结构的至少一个的总尺寸上的面积比例为至少20%或至少40%。替代地或附加地,所述比例为至多60%或至多80%。所述比例(例如)指凹陷区域在电接触金属化层和/或电接触盘的外轮廓线内的面积比例。通过这样的比例,可以有效地补偿电接触金属化层和另一电接触金属化层之间的尺寸差异。

32、根据至少一个实施例,仅电接触金属化层包括几何结构,而电接触盘不包括几何结构。因此,电接触金属化层具有至少一个凹陷区域。

33、根据至少一个实施例,所有电接触金属化层和所有电接触盘被配置为处于相同的电势上。换句话说,所有电接触金属化层和所有电接触盘都被电短路。例如,该电短路是在电接触金属化层和电接触盘本身的材料内实现的,或者可以由与电接触金属化层和电接触盘相邻的另一部件实现,例如,半导体芯片的高掺杂半导体材料或封装的电接触板。

34、根据至少一个实施例,电接触金属化层是多层构造的。因此,电接触金属化层包括至少两个子层。例如,所有子层都是金属层。例如,在各个子层被施加在半导体本体上的位置中,所有子层在远离半导体本体的方向上直接彼此跟随。

35、根据至少一个实施例,电接触金属化层包括一个或多个中断子层。也就是说,至少一个中断子层可以包括不由中断子层本身的材料连接的子区域。换言之,半导体本体可以在某些地方不具有至少一个中断子层。

36、根据至少一个实施例,电接触金属化层包括一个或多个连续子层。因此,至少一个连续子层可以没有任何中断和孔洞。

37、根据至少一个实施例,至少一个连续子层位于接触面处。因此,至少一个中断子层位于连续子层和半导体芯片的半导体材料之间。例如,至少一个中断子层被至少一个连续子层完全覆盖和封装。替换地,中断子层位于接触面处并部分覆盖至少一个连续子层。

38、根据至少一个实施例,至少一个中断子层和至少一个连续子层由相同的材料制成,例如由铝或铝合金制成。作为替代,至少一个中断子层和至少一个连续子层由不同的材料制成。

39、根据至少一个实施例,至少一个中断子层和至少一个连续子层具有不同的厚度。作为替代,至少一个中断子层和至少一个连续子层可以具有相同的厚度。

40、根据至少一个实施例,仅电接触盘包括几何结构,而电接触金属化层不包括几何结构。因此,至少一个凹陷区域可以局限于电接触盘。例如,所有电接触盘被配置为处于相同的电势上。

41、作为替代,电接触盘以及电接触金属化层可以被提供有几何结构,因此可以包括凹陷区域。

42、根据至少一个实施例,当在接触面上俯视时,几何结构由以下基本形状中的至少一种构成或者包括以下基本形状中的至少一种:圆形、螺旋形、矩形、三角形、六边形、蜂窝形。例如,几何结构是旋转对称或接近旋转对称的形式,或者是蜂窝结构。

43、例如,这种几何结构可以通过蚀刻、铣削、或车削,也可以通过涂覆或电镀,制造在电接触盘和/或电接触金属化层内。

44、根据至少一个实施例,半导体芯片包括一个或多个另一电接触金属化层。例如,至少一个另一电接触金属化层具有均匀和/或光滑的另一接触面。均匀意味着(例如)相应的另一电接触金属化层具有可由平面近似的表面,即,当在与所述另一电接触金属化层的表面垂直的横截面中看时没有或基本没有曲率。光滑意味着(例如)至少一个另一电接触金属化层具有平均粗糙度ra,其为至少一个电接触金属金属化层的平均粗糙度ra的至少20%或10%或5%或2%,和/或至少一个另一电接触金属化层的平均粗糙度ra为至多0.1μm或0.01μm。

45、也就是说,另一电接触金属化层(例如)不具有几何结构,并且因此不具有凹陷区域。替换地,与电接触金属化层的情况相反,另一电接触金属化层可以具有半导体芯片的内部电气方案所必需的结构。

46、除了电接触金属化层和至少一个另一电接触金属化层外,半导体芯片还可以包括另一电接触区域,这些电接触区域(例如)小于电接触金属化层和至少一个另一电接触金属化层。

47、例如,电接触金属化层、至少一个另一电接触金属化层、以及至少一个另一电接触区域彼此电分离,因此不会电短路。例如,电接触金属化层是阳极,另一电接触金属化层是阴极,并且另一电接触区域是栅极触点。

48、根据至少一个实施例,从相应金属化层的俯视图中可以看出,另一接触面的总尺寸小于接触面的总尺寸,从而小于电接触金属化层的总尺寸。例如,接触面的尺寸超过至另一接触面的尺寸至少1.5倍或至少2倍或至少3倍。替代地或附加地,所述因子为至多10或至多5或至多3。

49、根据至少一个实施例,由于几何结构,电接触金属化层或电接触盘的接触面的尺寸与另一接触面的尺寸相同。例如,这应用于公差最多为1.2倍或最多为1.1倍的情况。因此,通过几何结构,电接触金属化层和另一电接触金属化层的有效尺寸大致相同。有效尺寸可指相应机械接触区域的尺寸。因此,当计算各部件上的压力(单位面积的力)时,应将有效面积视为“单位面积的力”表达式中的相关面积。

50、根据至少一个实施例,电接触金属化层和另一电接触金属化层位于半导体芯片的相对的主侧处。例如,在俯视图中看,电接触金属化层和另一电接触金属化层以重叠的方式部分地或完全地布置到半导体芯片的主侧上。

51、作为替代,电接触金属化层和另一电接触金属化层也可以位于半导体芯片的同一主侧,或者也可以位于半导体芯片的侧面上。

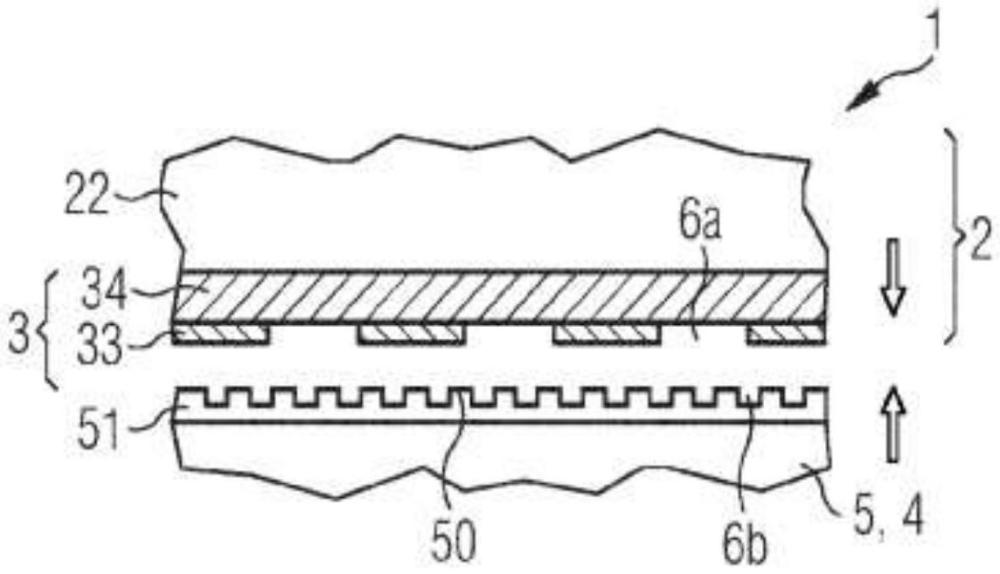

52、根据至少一个实施例,半导体芯片被配置为以至少0.3kn/cm2和/或至多2kn/cm2或至多3kn/cm2或至多10kn/cm2的接触力电接触。因此,半导体芯片以及因此的电接触金属化层和可选的至少一个另一电接触金属化层被配置为承受这种相对较高的压力。

53、这种高压(例如)不存在于未安装的电子器件中,而仅存在于安装的电子器件中。因此,在尚未安装的电子器件中,电接触盘可以松散地或仅施加例如至多0.1kn/cm2或至多10n/cm2的小压力布置在电接触金属化层。这同样适用于可选的至少一个另一电接触金属化层。“已安装”可以指布置在堆叠中的电子器件。

54、根据至少一个实施例,封装包括电绝缘护套和/或至少一个电金属接触板。例如,护套由陶瓷制成,也可以由塑料制成。一个或多个金属接触板(例如)由cu制成,并且可以包括(例如)ni的涂层。至少一个金属接触板的厚度可以是至少2mm和/或至多3cm。

55、根据至少一个实施例,半导体芯片、至少一个电接触盘、以及至少一个金属板被布置在护套中。半导体芯片、至少一个电接触盘、以及至少一个金属板(例如)彼此平行和/或一致或近似一致地布置。

56、根据至少一个实施例,在接触面上的俯视图中看,半导体芯片和至少一个电接触盘的尺寸彼此相差至多1.3倍或至多1.1倍。

57、根据至少一个实施例,电接触盘位于半导体芯片和接触板之间。例如,护套内存在以下堆叠:第一接触板-第一电接触盘-包括电接触金属化层、另一接触区域、和相对的另一电接触金属化层的半导体芯片-第二电接触盘–第二接触板。

58、另外,提供了用于电子器件的封装和半导体芯片。通过使用封装和/或半导体芯片,产生了结合上述实施例中的至少一个指示的电子器件。因此,还公开了用于封装以及半导体芯片的电子器件的特征,反之亦然。

59、在至少一个实施例中,封装包括具有几何结构的接触面。

60、在至少一个实施例中,半导体芯片包括在接触面处具有几何结构的电接触金属化层。

61、此外,提供了一种器件堆叠。该器件堆叠包括多个电子器件,如结合上述实施例中的至少一个所示。因此,还公开了用于器件堆叠的电子器件的特征,反之亦然。

62、在至少一个实施例中,器件堆叠包括多个电子器件,电子器件一个堆叠在另一个上。例如,电子器件在没有任何附加的电连接装置的情况下直接彼此接触,或者在它们之间具有用于冷却或电连接的部件。电子器件可以以一致的方式布置。例如,电子器件被压在一起。

63、下面参考附图通过示例性实施例更详细地解释本文描述的电子器件、封装、半导体芯片、和器件堆叠。在各个图中相同的元件由相同的附图标记表示。然而,元件之间的关系没有按比例显示,而是可以夸大显示单个元件,以帮助理解。

- 还没有人留言评论。精彩留言会获得点赞!