一种倒装发光二极管芯片及其制备方法与流程

1.本发明涉及芯片技术领域,特别涉及一种倒装发光二极管芯片及其制备方法。

背景技术:

2.发光二极管以其节能、高亮、耐久性高、寿命长、轻巧等优势广泛应用于各个照明领域。

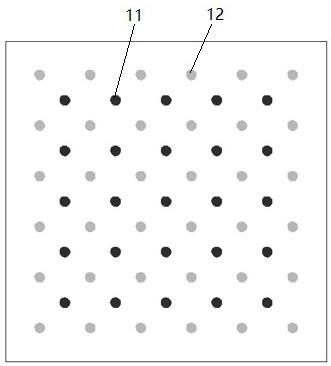

3.其中,倒装led芯片在蓝宝石面出光,蓝宝石折射率小于氮化镓折射率,减少了部分光线的全反射,且倒装led芯片在芯片面制备反射镜的提升芯片亮度;倒装led芯片以其具有较高的外量子效率市场份额稳步上升,应用逐渐成熟。

4.然而,如图1所示,现有的倒装led芯片制备的第一导电金属层中p型导电金属与n型导电金属的数量比例较小、且单个第一n型导电金属11及第一p型导电金属12直径较大,第一n型导电金属11与第一p型导电金属12间距较大,导致电流扩散困难及电流扩散不均匀,在较大的雷击浪涌测试时,大电压输入的情况下,电流无法迅速扩散,导致芯片烧毁失效,采用现有技术的芯片烧毁图如图2。

技术实现要素:

5.基于此,本发明的目的是提供一种倒装发光二极管芯片及其制备方法,旨在解决背景技术中记载的技术问题。

6.本发明的一方面在于提供一种倒装发光二极管芯片,所述发光二极管芯片自下而上依次包括衬底、外延层、电流阻挡层、电流扩展层、第一导电金属层、dbr反射层、第二导电金属层、绝缘保护层及键合金属层;其中,所述第一导电金属层包括第一n型导电金属与第一p型导电金属,在单个所述发光二极管芯片内,所述第一n型导电金属与所述第一p型导电金属的数量比为1:2-1:30。

7.根据上述技术方案的一方面,所述第一n型导电金属与所述第一p型导电金属的直径为3-40μm。

8.根据上述技术方案的一方面,所述第一n型导电金属与所述第一p型导电金属的横向及纵向中心间距为30-200μm。

9.根据上述技术方案的一方面,所述第一导电金属层的面积总和为所述发光二极管芯片的面积的1%-15%。

10.根据上述技术方案的一方面,所述第一导电金属层的面积总和为所述发光二极管芯片的面积的2.85%;所述第一n型导电金属与第一p型导电金属的数量比为1:4.5;所述第一n型导电金属和所述第一p型导电金属的直径均为15μm;所述第一n型导电金属与所述第一p型导电金属的横向中心间距为35-80μm;所述第一n型导电金属与所述第一p型导电金属的纵向中心间距为35-80μm。

11.根据上述技术方案的一方面,所述第一导电金属层的面积总和为所述发光二极管芯片的面积的2%;所述第一n型导电金属与第一p型导电金属的数量比为1:8;所述第一n型导电金属和所述第一p型导电金属的直径均为10μm;所述第一n型导电金属与所述第一p型导电金属的横向中心间距与纵向中心间距均为51μm。

12.根据上述技术方案的一方面,所述第一导电金属层的面积总和为所述发光二极管芯片的面积的1%;所述第一n型导电金属与第一p型导电金属的数量比为1:25;所述第一n型导电金属的直径为3μm,所述第一p型导电金属262的直径为40μm;所述第一n型导电金属与所述第一p型导电金属的横向中心间距为62μm,所述第一n型导电金属与所述第一p型导电金属的纵向中心间距为31μm。

13.本发明的另一方面在于提供一种倒装发光二极管芯片的制备方法,用于制作形成上述技术方案中所述的倒装发光二极管芯片,所述方法包括:提供一衬底,在所述衬底上生长外延层;在所述外延层的表面通过光刻形成图形,通过电感耦合等离子体对所述外延层进行刻蚀,暴露出mesa台阶,去除表面光刻胶;在所述外延层的表面沉积电流阻挡材料,通过光刻在电流阻挡材料表面形成图形,进行boe腐蚀,腐蚀后剩余的电流阻挡材料形成电流阻挡层,然后去除表面光刻胶;接着溅射电流扩展材料,然后利用光刻在电流扩展材料表面形成图形,然后进行电流扩展材料的腐蚀,腐蚀后剩余的电流扩展材料形成电流扩展层,然后去除表面光刻胶;接着在表面涂布负性光刻胶,通过光刻形成图形,蒸镀第一导电金属层,剥离掉多余金属,去除光刻胶,形成第一n型导电金属和第一p型导电金属;接着蒸镀dbr反射层,通过光刻形成图形,电感耦合等离子体刻蚀形成n型dbr通孔和p型dbr通孔;接着在表面涂布负性光刻胶,通过光刻形成图形,蒸镀第二导电金属层,剥离掉多余金属,去除光刻胶,形成第二n型导电金属和第二p型导电金属;接着沉积绝缘保护层,通过光刻形成图形,电感耦合等离子体刻蚀形成n型绝缘保护层通孔和p型绝缘保护层通孔;接着在表面涂布负性光刻胶,通过光刻形成图形,蒸镀键合金属层,剥离多余金属,去除光刻胶,形成n型键合金属和p型键合金属。

14.根据上述技术方案的一方面,所述方法中:所述n型键合金属通过所述n型绝缘保护层通孔与所述第二n型导电金属形成电性连接,所述p型键合金属通过所述p型绝缘保护层通孔与所述第二p型导电金属形成电性连接。

15.根据上述技术方案的一方面,所述方法中:所述第二n型导电金属通过所述n型dbr通孔与所述第一n型导电金属形成电性连接,所述第二p型导电金属通过所述p型dbr通孔与第一p型导电金属形成电性连接。

16.与现有技术相比,采用本发明所示的倒装发光二极管芯片及其制备方法,有益效

果在于:通过增加单个发光二极管芯片内第一p型导电金属层与第一n型导电金属层的数量比例,从而能够在不改变现有倒装发光二极管芯片制备成本及光电性能的情况下,缩短第一p型导电金属层与第一n型金属层的中心间距,缩短p型半导体中空穴的迁移距离,提升了电流的横向扩散能力,大幅提升芯片抗雷击浪涌能力,增强芯片的可靠性。

附图说明

17.图1为传统倒装发光二极管芯片第一导电金属层俯视图;图2为传统倒装发光二极管芯片雷击浪涌测试烧毁图;图3为本发明实施例1-4中倒装发光二极管芯片的结构示意图;图4为本发明实施例1中倒装发光二极管芯片第一导电金属层俯视图;图5为本发明实施例2中倒装发光二极管芯片第一导电金属层俯视图;图6为本发明实施例3中倒装发光二极管芯片第一导电金属层俯视图;附图标记说明:衬底21、外延层22、mesa台阶23、电流阻挡层24、电流扩展层25、第一导电金属层26、第一n型导电金属261、第一p型导电金属262、dbr反射层27、第二导电金属层28、第二n型导电金属281、第二p型导电金属282、绝缘保护层29、键合金属层30、n型键合金属301、p型键合金属302;以下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

18.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的若干实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

19.实施例一请结合图3与图4,本发明的第一实施例提供了一种倒装发光二极管芯片,在本实施例中:所述发光二极管芯片自下而上依次包括衬底21、外延层22、电流阻挡层24、mesa台阶23、电流扩展层25、第一导电金属层26、dbr反射层27、第二导电金属层28、绝缘保护层29及键合金属层30;其中,第二导电金属层28包括第二n型导电金属281与第二p型导电金属282,键合金属层30包括n型键合金属301与p型键合金属302。

20.在可选的实施例中,衬底21包括但不限于al2o3、gan、si、sic、gaas;外延层22自下而上依次为缓冲层、n型半导体层、有源层、p型半导体层;其中,在外延层22上通过电感耦合等离子体对外延层进行刻蚀,暴露出mesa台阶23;电流阻挡层24包括但不限于sio2、ti3o5、sin;电流扩展层25包括但不限于ito(氧化铟锡)、ag;第一导电金属层26包括但不限于cr、al、ni、ti、pt、au以及这些金属组成的叠层;dbr反射层27包括但不限于sio2与ti3o5叠层,sio2与sin叠层;第二导电金属层28包括但不限于cr、al、ni、ti、pt、au以及这些金属组成的叠层;绝缘保护层29包括但不限于sio2、ti3o5、sin;键合金属层30包括但不限于cr、al、ni、ti、pt、au以及这些金属组成的叠层。

21.其中,所述第一导电金属层26包括第一n型导电金属261与第一n型导电金属261,在单个所述发光二极管芯片内,所述第一n型导电金属261与所述第一p型导电金属262的数量比为1:2-1:30。也即,第一p型导电金属262为第一n型导电金属261的2倍以上(仅限整数倍),第一p型导电金属262的数量较第一n型导电金属261的数量更多。

22.进一步的,所述第一n型导电金属261与所述第一p型导电金属262的直径为3-40μm,所述第一n型导电金属261与所述第一p型导电金属262的横向及纵向中心间距为30-200μm,所述第一导电金属层26的面积总和为所述发光二极管芯片的面积的1%-15%。

23.示例而非限定,在本实施例中,所述第一导电金属层26的面积总和为所述发光二极管芯片的面积的2.85%;所述第一n型导电金属261与第一p型导电金属262的数量比为1:4.5;应当理解的,第一n型导电金属261的数量仅为整数,并不存在第一n型导电金属261的数量为非整数的情况,因此,上述第一n型导电金属261与第一p型导电金属262的数量比为1:4.5可以改写成2:9;所述第一n型导电金属261和所述第一p型导电金属262的直径均为15μm,即第一n型导电金属261与第一p型导电金属262的直径可以是相等的;所述第一n型导电金属261与所述第一p型导电金属262的横向中心间距与纵向中心间距均为35-80μm。

24.如图4所示,第一n型导电金属261与第一p型导电金属262的横向中心间距记为x,第一n型导电金属261与第一p型导电金属262的纵向向中心间距记为y,x、y的值可以相等或不相等。也即,第一n型导电金属261与第一p型导电金属262的数量及间距的变化,影响了第一n型导电金属261与第一p型导电金属262的排列分布,从而可以得到多种排列方式。

25.与现有技术相比,采用本实施例当中所示的倒装发光二极管芯片,有益效果在于:通过增加第一n型导电金属261与第一p型导电金属262的数量比,缩小单个第一n型导电金属261及第一p型导电金属262的直径,以及缩小第一n型导电金属261与第一p型导电金属262的横向及纵向间距,能够使得该倒装发光二极管芯片的电流扩散更为简单以及更为均匀;在较大的雷击浪涌测试时,大电压输入的情况下,电流能够迅速扩散,从而提升芯片的整体可靠性;本发明旨在不增加现有成本和不改变现有芯片光电性能的情况下增加倒装发光二极管芯片的抗雷击浪涌能力。

26.实施例二请结合图3与图5,本发明的第二实施例提供了一种倒装发光二极管芯片,本实施例当中所示的倒装发光二极管芯片与第一实施例当中所示的倒装发光二极管芯片的结构基本一致,区别之处在于:在本实施例中,所述第一导电金属层26的面积总和为所述发光二极管芯片的面积的2%;所述第一n型导电金属261与第一p型导电金属262的数量比为1:8;所述第一n型导电金属261和所述第一p型导电金属262的直径均为10μm;所述第一n型导电金属261与所述第一p型导电金属262的横向中心间距与纵向中心间距均为51μm。

27.在本实施例中,通过增加第一n型导电金属261与第一p型导电金属262的数量比,

进一步增加第一p型导电金属262的数量,提升倒装发光二极管芯片雷击浪涌能力,从而提升芯片的整体可靠性,在不增加现有成本和不改变现有芯片光电性能的情况下能够有效增加倒装发光二极管芯片的抗雷击浪涌能力。

28.实施例三请结合图3与图6,本发明的第三实施例提供了一种倒装发光二极管芯片,本实施例当中所示的倒装发光二极管芯片与第一、二实施例当中所示的倒装发光二极管芯片的结构基本一致,区别之处在于:在本实施例中,所述第一导电金属层26的面积总和为所述发光二极管芯片的面积的1%;所述第一n型导电金属261与第一p型导电金属262的数量比为1:25;所述第一n型导电金属261的直径为40μm,所述第一p型导电金属262的直径为3μm;所述第一n型导电金属261与所述第一p型导电金属262的横向中心间距为62μm,所述第一n型导电金属261与所述第一p型导电金属262的纵向中心间距为31μm。

29.在本实施例中,通过增加第一n型导电金属261与第一p型导电金属262的数量比,进一步增加第一p型导电金属262的数量,提升倒装发光二极管芯片雷击浪涌能力,从而提升芯片的整体可靠性,在不增加现有成本和不改变现有芯片光电性能的情况下能够有效增加倒装发光二极管芯片的抗雷击浪涌能力。

30.在本发明的一些实施例当中,如表1所示,为常规倒装发光二极管芯片与采用本发明部分实施例的倒装发光二极管芯片的抗雷击浪涌能力的对比:表1第一n型导电金属与第一p型导电金属的数量比抗雷静浪涌能力(单位:v)1:1.5(现有技术)55v1:2.5(本发明的部分实施例)65v1:4.5(本发明的部分实施例)80v1:8(本发明的部分实施例)110v1:15(本发明的部分实施例)150v1:25(本发明的部分实施例)190v1:30(本发明的部分实施例)195v综上,采用本发明上述实施例的倒装发光二极管芯片,通过增加第一n型导电金属与第一p型导电金属的数量比,缩小单个第一n型导电金属及第一p型导电金属的直径,以及缩小第一n型导电金属与第一p型导电金属的横向及纵向间距,能够使得该倒装发光二极管芯片的电流扩散更为简单以及更为均匀;在较大的雷击浪涌测试时,大电压输入的情况下,电流能够迅速扩散,从而提升芯片的整体可靠性;本发明旨在不增加现有成本和不改变现有芯片光电性能的情况下增加倒装发光二极管芯片的抗雷击浪涌能力。

31.实施例四本发明的第四实施例提供了一种倒装发光二极管芯片的制备方法,本实施例当中所示的方法用于制作形成上述实施例当中所述的倒装发光二极管芯片,所述方法包括步骤s10-s60:步骤s10,提供一衬底,在所述衬底上生长外延层;

步骤s20,在所述外延层的表面通过光刻形成图形,通过电感耦合等离子体对所述外延层进行刻蚀,暴露出mesa台阶,去除表面光刻胶;步骤s30,在所述外延层的表面沉积电流阻挡材料,通过光刻在电流阻挡材料表面形成图形,进行boe腐蚀,腐蚀后剩余的电流阻挡材料形成电流阻挡层,然后去除表面光刻胶;步骤s40,接着溅射电流扩展材料,然后利用光刻在电流扩展材料表面形成图形,然后进行电流扩展材料的腐蚀,腐蚀后剩余的电流扩展材料形成电流扩展层,然后去除表面光刻胶;步骤s50,接着在表面涂布负性光刻胶,通过光刻形成图形,蒸镀第一导电金属层,剥离掉多余金属,去除光刻胶,形成第一n型导电金属和第一p型导电金属;步骤s20,接着蒸镀dbr反射层,通过光刻形成图形,电感耦合等离子体刻蚀形成n型dbr通孔和p型dbr通孔;步骤s20,接着在表面涂布负性光刻胶,通过光刻形成图形,蒸镀第二导电金属层,剥离掉多余金属,去除光刻胶,形成第二n型导电金属和第二p型导电金属;步骤s20,接着沉积绝缘保护层,通过光刻形成图形,电感耦合等离子体刻蚀形成n型绝缘保护层通孔和p型绝缘保护层通孔;步骤s20,接着在表面涂布负性光刻胶,通过光刻形成图形,蒸镀键合金属层,剥离多余金属,去除光刻胶,形成n型键合金属和p型键合金属。

32.在本实施例所示的所述方法中,具体而言:所述n型键合金属通过所述n型绝缘保护层通孔与所述第二n型导电金属形成电性连接,所述p型键合金属通过所述p型绝缘保护层通孔与所述第二p型导电金属形成电性连接。

33.进一步的,所述方法中:所述第二n型导电金属通过所述n型dbr通孔与所述第一n型导电金属形成电性连接,所述第二p型导电金属通过所述p型dbr通孔与第一p型导电金属形成电性连接。

34.具体而言,在本实施例中,该倒装发光二极管芯片的制作步骤包括:首先在一衬底上生长外延层;接着在外层表面利用光刻形成图形,然后icp(电感耦合等离子体)刻蚀,暴露出mesa台阶,然后出去表面光刻胶;接着沉积sio2,然后利用光刻在sio2表面形成图形,然后进行boe腐蚀,腐蚀后剩余sio2为电流阻挡层,然后去除表面光刻胶;接着溅射ito(氧化铟锡),然后利用光刻在ito表面形成图形,然后进行ito腐蚀,腐蚀后剩余ito为电流扩展层,然后去除表面光刻胶;接着在表面涂布负性光刻胶,然后光刻形成图形,然后蒸镀第一导电金属层,然后剥离掉多余金属,去除光刻胶,形成第一n型导电金属和第一p型导电金属;接着蒸镀dbr反射层,然后利用光刻形成图形,然后icp刻蚀形成n型dbr通孔和p型dbr通孔;接着在表面涂布负性光刻胶,然后光刻形成图形,然后蒸镀第二导电金属层,然后剥离掉多余金属,去除光刻胶,形成第二n型导电金属和第二p型导电金属;

接着沉积绝缘保护层,然后利用光刻形成图形,然后icp刻蚀形成n型绝缘保护层通孔和p型绝缘保护层通孔;接着在表面涂布负性光刻胶,然后光刻形成图形,然后蒸镀键合金属层,然后剥离掉多余金属,去除光刻胶,形成n型键合金属和p型键合金属。

35.综上,采用本发明上述实施例的倒装发光二极管芯片的制备方法,通过增加第一n型导电金属与第一p型导电金属的数量比,缩小单个第一n型导电金属及第一p型导电金属的直径,以及缩小第一n型导电金属与第一p型导电金属的横向及纵向间距,能够使得该倒装发光二极管芯片的电流扩散更为简单以及更为均匀;在较大的雷击浪涌测试时,大电压输入的情况下,电流能够迅速扩散,从而提升芯片的整体可靠性;本发明旨在不增加现有成本和不改变现有芯片光电性能的情况下增加倒装发光二极管芯片的抗雷击浪涌能力。

36.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、

ꢀ“

示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

37.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1