一种新型Si-SiC异质结隧穿MOSFET器件及其集成器件

一种新型si-sic异质结隧穿mosfet器件及其集成器件

技术领域

1.本发明属于半导体器件技术领域,涉及隧穿场效应管半导体器件,具体为一种新型si(硅)-sic(碳化硅)异质结隧穿mosfet(metal oxide semiconductor field effect transistor)器件及集成电路技术。

背景技术:

2.碳化硅半导体材料作为一种宽禁带半导体材料,具有禁带宽度大、击穿场强高、载流子饱和漂移速度高、介电常数小等优点;用碳化硅材料制备的功率器件及功率集成电路性能要高于普通硅材料的功率器件,因此碳化硅材料具有更广阔的应用前景。

3.另一方面,随着mosfet沟道长度的不断缩短,许多可以忽略的效应变得显著起来,这些效应统称为短沟道效应;当mosfet的沟道长度缩短到可以和源区、漏区的结深相比拟时,阈值电压将随着沟道长度l的缩短而减小,这便是阈值电压的短沟道效应。当沟道长度减小后还会出现漏致势垒降低效应(dibl),会发生穿通使得源、漏之间产生很大的漏电流。

4.为了克服本发明提出了及集成电路技术,该技术中器件的有效沟道长度可以为无限短,克服sic中反型层电子迁移率低的问题,为sic集成电路及功率集成电路技术提供一种新的实现途径。

技术实现要素:

5.本发明的目的在于提供一种新型的si(硅)-sic(碳化硅)异质结隧穿mosfet器件,用以克服传统硅基mosfet的二级效应;与传统的mosfet相比,本发明的器件结构中栅极能够做到无限短,实现零沟道长度结构,即不存在沟道长度调制效应,因此沟道迁移率不受到沟道长度的限制,摆脱了沟道迁移率对导通电阻的限制;同时,由于sic材料具有很好的热导率及高温特性,这也为高温集成电路技术提供了一种选择。

6.为实现上述目的,本发明采用的技术方案如下:

7.一种新型si-sic异质结隧穿mosfet器件,包括:sic衬底、位于sic衬底上的nmos;其特征在于,所述nmos包括:相邻接的n型碳化硅半导体区与p型硅半导体区,n型碳化硅半导体区中设置有重掺杂n型半导体区、重掺杂n型半导体区上设置金属化漏极,p型硅半导体区中设置有重掺杂p型半导体区、重掺杂p型半导体区上设置金属化源极,n型碳化硅半导体区与p型硅半导体区于邻接处跨接设置金属栅极。

8.一种新型si-sic异质结隧穿mosfet器件,包括:sic衬底、位于sic衬底上的pmos;其特征在于,所述pmos包括:相邻接的n型硅半导体区与p型碳化硅半导体区,n型硅半导体区中设置有重掺杂n型半导体区、重掺杂n型半导体区上设置金属化源极,p型碳化硅半导体区中设置有重掺杂p型半导体区、重掺杂p型半导体区上设置金属化漏极,n型硅半导体区与p型碳化硅半导体区于邻接处跨接设置金属栅极。

9.进一步的,上述两个器件中,所述金属栅极为表面栅极结构或槽型栅极结构。

10.一种新型si-sic异质结隧穿mosfet器件,包括:n型碳化硅半导体区,设置于n型碳

化硅半导体区下的重掺杂n型半导体区,设置于重掺杂n型半导体区下的金属化漏极,设置于n型碳化硅半导体区上的p型硅半导体区,设置于p型硅半导体区上的重掺杂p型半导体区,设置于重掺杂p型半导体区上的金属化源极,以及深入p型硅半导体区与n型碳化硅半导体区的沟槽型金属栅极。

11.一种基于nmos与pmos的反相器,包括:sic衬底,以及sic衬底上邻接设置的pmos与nmos;pmos与nmos的漏极相连、作为反相器的输出端,nmos与pmos的栅极相连、作为反相器的输入端,nmos的源极接地、pmos的的源极接电源电压。

12.一种基于nmos与pmos的反相器,包括:硅衬底,设置于硅衬底上的绝缘层衬底,以及设置于绝缘层衬底中的相分隔的pmos与nmos;nmos与pmos的漏极相连、作为反相器的输出端,nmos与pmos的栅极相连、作为反相器的输入端,nmos的源极接地、pmos的的源极接电源电压。

13.本发明的有益效果在于:

14.本发明提供一种新型si-sic异质结隧穿mosfet器件,采用n型硅半导体区与p型碳化硅半导体区、或者n型碳化硅半导体区与p型硅半导体区之间形成的si-sic异质结结构,相较于传统的mosfet结构,本发明的器件结构中有效沟道为si-sic异质结的结面,即有效沟道长为无限短,则不存在沟道长度调制效应,有效消除二级效应,进而克服sic中反型层中电子迁移率低的问题;同时,本发明器件结构能够实现在同一衬底上nmos与pmos的隔离,进而实现反相器等结构,在sic集成电路及sic功率集成电路领域具有广阔的应用前景。

附图说明

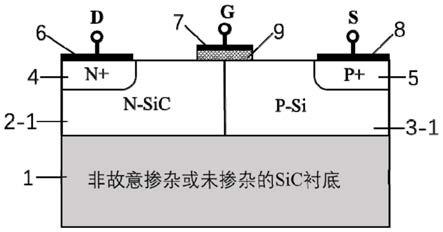

15.图1为本发明实施例1提供的一种si-sic异质结隧穿nmosfet器件的剖面结构示意图。

16.图2为本发明实施例2提供的一种si-sic异质结隧穿pmosfet器件的剖面结构示意图。

17.图3为本发明实施例2提供的在同一衬底上实现nmos与pmos的集成器件的剖面结构示意图。

18.图4为本发明实施例2提供的在同一衬底上实现nmos与pmos的集成器件的剖面结构示意图。

19.图5为本发明实施例3提供的一种基于nmos与pmos的反相器的剖面结构示意图。

20.图6为本发明实施例4提供的一种基于nmos与pmos的反相器的剖面结构示意图。

21.图7为本发明实施例5提供的一种si-sic异质结隧穿mosfet器件的剖面结构示意图。

22.图8为本发明实施例6提供的一种si-sic异质结隧穿mosfet器件的剖面结构示意图。

23.图9为本发明实施例中si-sic异质结隧穿mosfet器件的阈值电压曲线图;其中,(1)为n型mosfet,(2)为p型mosfet。

24.图10为本发明实施例中si-sic异质结隧穿mosfet器件的输出特性曲线图。

25.图11是本发明实施例中si-sic异质结隧穿mosfet器件的能带图。

26.图12为本发明实施例中基于nmos与pmos的反相器的电路原理图。

27.图13为本发明实施例中基于nmos与pmos的反相器的电压输入输出曲线。

具体实施方式

28.下面结合附图和实施例对本发明进行进一步详细说明。

29.实施例1

30.本实施例提供一种新型si-sic异质结隧穿mosfet器件,其结构如图1所示,包括:非故意掺杂或未掺杂的sic衬底1、位于半导体衬底上的半导体层(nmos);所述半导体层包括:相邻接的n型碳化硅半导体区2-1与p型硅半导体区3-1,n型碳化硅半导体区2-1中设置有重掺杂n型半导体区4、重掺杂n型半导体区4上设置金属化漏极(d)6,p型硅半导体区3-1中设置有重掺杂p型半导体区5、重掺杂p型半导体区5上设置金属化源极(s)8,n型碳化硅半导体区2-1与p型硅半导体区3-1上跨接设置n型多晶硅栅9,n型多晶硅栅9上设置金属化栅极7;n型碳化硅半导体区2-1与p型硅半导体区3-1于邻接处形成si-sic异质结,表面栅(n型多晶硅栅9与金属化栅极7构成)对应于si-sic异质结处设置。

31.本实施例的工作原理如下:

32.上述新型si-sic异质结隧穿mosfet器件中,使用n型碳化硅与p型硅半导体,由于在n型碳化硅半导体区2-1一侧其多数载流子是电子,由图9(1)可知阈值电压为正,因此构成异质结隧穿n-mosfet器件;在导通时的电极连接方式为:金属化漏极(d)6接高电位,金属化源极(s)8接低电位,金属化栅极(g)7接高电位。由于碳化硅的能带与硅的能带存在差异,由图11(1)的能带图可知当金属化漏极(d)6接高电位时,n型碳化硅半导体区2-1一侧的导带处于p型硅半导体区3-1的导带的下方,形成一个对于电子的势垒,电子无法越过势垒,因此无法形成电流;由图11(2)可知当金属化栅极(g)7接高电位时,会使n型碳化硅半导体区2-1和p型硅半导体区3-1的能带发生变化,使得n型碳化硅半导体区2-1一侧的导带和p型硅半导体区3-1一侧的价带产生交叠,当栅极电压高到一定程度,电子会发生带-带隧穿效应,即n型碳化硅区2-1一侧的导带中的电子隧穿至p型硅区3-1一侧的价带中变成空穴,由于p型硅区3-1的多数载流子是空穴,因此空穴被金属化源极(s)8所抽走,形成连续的电流。

33.本发明器件结构中的有效沟道为si-sic异质结的结面,不同于传统的mosfet结构的沟道为栅极下的反型层沟道,即该器件结构的有效沟道长度为无限短,实现了零沟道长度结构,则不存在沟道长度调制效应,有效消除二级效应,进而克服sic中反型层中电子迁移率低的问题。如图10所示为该本发明器件结构的输出特性曲线,温度为300k和400k时,在栅极电压为15v和20v时,该器件的电流均可以随着漏极电压的上升而逐渐饱和。

34.实施例2

35.本实施例提供一种新型si-sic异质结隧穿mosfet器件,其结构如图1所示,包括:非故意掺杂或未掺杂的sic衬底1、位于半导体衬底上的半导体层(pmos);所述半导体层包括:相邻接的n型硅半导体区2-2与p型碳化硅半导体区3-2,n型硅半导体区2-2中设置有重掺杂n型半导体区4、重掺杂n型半导体区4上设置金属化源极(s)6,p型碳化硅半导体区3-2中设置有重掺杂p型半导体区5、重掺杂p型半导体区5上设置金属化漏极(d)8,n型硅半导体区2-2与p型碳化硅半导体区3-2上跨接设置n型多晶硅栅9,n型多晶硅栅9上设置金属化栅极7;n型硅半导体区2-2与p型碳化硅半导体区3-2于邻接处形成si-sic异质结,表面栅(n型多晶硅栅9与金属化栅极7构成)对应于si-sic异质结处设置。

36.本实施例的工作原理如下:

37.上述新型si-sic异质结隧穿mosfet器件,使用n型硅与p型碳化硅半导体,由图9(2)可知阈值电压为负电压,因此构成异质结隧穿p-mosfet器件;在导通时的电极连接方式为:金属化漏极(d)8接低电位,金属化源极(s)6接高电位,金属化栅极(g)7接相对于金属化漏极(d)的低电位。由于碳化硅的能带与硅的能带存在差异,因此当金属化源极(s)6接高电位时,p型碳化硅半导体区3-2一侧的导处于n型硅半导体区2-2的导带的上方,形成一个对于电子的势垒,电子无法越过势垒,因此无法形成电流;当金属化栅极(g)7接相对于金属化漏极(d)的低电位,会使p型碳化硅半导体区3-2和n型硅半导体区2-2的能带发生变化,使得p型碳化硅半导体区3-2一侧的导带和n型硅半导体区2-2一侧的价带产生交叠,当栅极电压低到一定程度,电子会发生带-带隧穿效应,即n型硅区2-2一侧的导带中的电子隧穿至p型碳化硅区3-2一侧的价带中变成空穴,由于p型碳化硅区3-2的多数载流子是空穴,因此空穴被金属化漏极(d)8所抽走,形成连续的电流。

38.本发明器件结构中的有效沟道为si-sic异质结的结面,不同于传统的mosfet结构的沟道为栅极下的反型层沟道,即该器件结构的有效沟道长度为无限短,实现了零沟道长度结构,则不存在沟道长度调制效应,有效消除二级效应,进而克服sic中反型层中电子迁移率低的问题。

39.另外,由于未掺杂的sic衬底和硅材料天然存在电子势垒,因此可以做到在同一个衬底上实现nmos和pmos的隔离,如图3所示;该结构无需使用cmos工艺中的阱工艺,即分别在n阱中实现pmos和p阱中实现nmos,因此由于天然的隔离,工艺实现更为简单。进一步的,为了加强器件之间的隔离,在器件之间填充绝缘层,绝缘层材料一般为sio2,如图4所示,该结构无需使用cmos工艺中的阱工艺,即分别在n阱中实现pmos和p阱中实现nmos,因此由于天然的隔离,工艺实现更为简单。

40.实施例3

41.本实施例提供一种nmos与pmos组成的反相器结构,如图5所示,包括:非故意掺杂或未掺杂sic衬底,以及sic衬底上邻接设置的pmos与nmos;所述nmos与pmos分别为实施例1与实施例2中的si-sic异质结隧穿mosfet器件,nmos与pmos共用非故意掺杂或未掺杂sic衬底,nmos与pmos的漏极相连、作为反相器的输出端,nmos与pmos的栅极相连、作为反相器的输入端,nmos的源极接地、pmos的的源极接电源电压。

42.本实施例的工作原理如下:

43.上述反相器的原理如图12所示,将pmos和nmos的金属化漏极(d)连接在一起,且金属化漏极(d)同时接触重掺杂nmos的n型碳化硅半导体区中重掺杂n型半导体区4和pmos的p型碳化硅半导体区中重掺杂p型半导体区,nmos的金属化源极(s)接低电位、即接地(gnd),pmos的金属化源极(s)接高电位、即v

dd

;同时将nmos和pmos的金属化栅极(g)连接在一起作为输入端。当输入端为高电压时,且电压值大于nmos的阈值电压值,此时图12中下方的nmos管导通,输出为低电平,即输出接地(gnd);当输入端为负电压时,且电压值绝对值大于pmos的阈值电压绝对值,此时图12中上方的pmos管导通,输出为高电平,即输出接v

dd

,这样就实现了反相器的功能,即输入为高电平时输出低电平,输入为低电平时输出为高电平,输入输出曲线如图13所示。

44.实施例4

45.本实施例提供一种nmos与pmos组成的反相器结构,如图6所示,包括:硅衬底10,设置于硅衬底上的绝缘层衬底11,以及设置于绝缘层衬底11中的相分隔的pmos与nmos;所述nmos与pmos分别为实施例1与实施例2中的si-sic异质结隧穿mosfet器件,nmos与pmos共用硅衬底10与绝缘层衬底11,nmos与pmos的漏极相连、作为反相器的输出端,nmos与pmos的栅极相连、作为反相器的输入端,nmos的源极接地、pmos的的源极接电源电压。

46.本实施例的工作原理和实施例3相似,而本实施例能够实现更好的器件之间的隔离,减少寄生效应。

47.实施例5

48.本实施例提供一种新型si-sic异质结隧穿mosfet器件,其结构如图7所示,其与实施例1的唯一区别在于:采用槽栅代替平面栅,槽栅跨接设置于n型碳化硅半导体区2-1与p型硅半导体区3-1中;本实施例的工作原理与实施例1相同,并且,由于沟槽型金属化栅极(g)7深入n型碳化硅半导体区2-1,因此有更大的接触面积,当沟槽型金属化栅极(g)7接高电位时,由于更大的接触面积能够实现更大的导通电流。

49.同理,实施例2中si-sic异质结隧穿mosfet器件同样可以采用槽栅。

50.实施例6

51.本实施例提供一种新型si-sic异质结隧穿mosfet器件,采用纵向结构,如图8所示,包括:n型碳化硅半导体区2-1,设置于n型碳化硅半导体区2-1下的重掺杂n型半导体区4,设置于重掺杂n型半导体区4下的金属化漏极(d)6,设置于n型碳化硅半导体区2-1上的p型硅半导体区3-1,设置于p型硅半导体区3-1上的重掺杂p型半导体区5,设置于重掺杂p型半导体区5上的金属化源极(s)8,以及深入p型硅半导体区3-1与n型碳化硅半导体区2-1的沟槽型金属栅,所述沟槽型金属栅由位于槽壁的n型多晶硅栅9与填充于槽内的金属化栅极(g)7构成。

52.本实施例的工作原理如下:

53.上述新型si-sic异质结隧穿mosfet器件为纵向结构,与实施例1中横向结构具有相同的工作原理,并且,沟槽型金属栅极深入p型硅半导体区3-1和n型碳化硅半导体区2-1内部,金属化源极(s)5和金属化源极(d)6分别位于芯片的两面,此类似于vdmos的结构能够大大减小器件占用的面积。

54.以上所述,仅为本发明的具体实施方式,本说明书中所公开的任一特征,除非特别叙述,均可被其他等效或具有类似目的的替代特征加以替换;所公开的所有特征、或所有方法或过程中的步骤,除了互相排斥的特征和/或步骤以外,均可以任何方式组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1