电迁移测试结构及形成方法、电迁移测试方法、存储器与流程

1.本发明涉及半导体制造技术领域,尤其涉及一种电迁移测试结构及其形成方法、电迁移测试方法、存储器。

背景技术:

2.近年来,随着半导体器件的尺寸不断缩小、集成度不断的提高,半导体器件工作时的电流不断增加,电迁移(electromigration,em)效应成为半导体器件可靠性的瓶颈之一。电迁移效应是指半导体器件中的集成电路工作时金属线内部有电流通过,在电流的作用下金属离子产生物质运输的现象。由此,金属线的某些部位会因该电迁移现象而出现空洞(void),进而发生断路,而某些部位会因该电迁移现象而出现小丘(hillock),进而造成电路短路。

3.当前在对测试结构进行电迁移测试,主要是向测试结构施加一个恒定电流,所述测试结构在电子风的推动下会发生导电粒子(例如cu原子或者al原子)的迁移,从而在所述测试结构内部形成空洞。通过监控所述测试结构电阻的变化来判断空洞的大小,当所述测试结构的电阻下降10%时,判定所述测试结构失效,并记录失效时间(time to failure,ttf)。之后,通过black方程来估计半导体器件在工作条件下的寿命,从而实现对半导体器件性能的检测。但是,当前由于测试结构本身的限制,导致无法准确的监控电阻的变化,从而降低了电迁移测试结果的准确性和可靠性。

4.因此,如何提高电迁移测试结果的准确性和可靠性,是当前亟待解决的技术问题。

技术实现要素:

5.本发明提供一种电迁移测试结构及其形成方法、电迁移测试方法,用于解决现有技术中电迁移测试结果的准确度和可靠性较低的问题。

6.为了解决上述问题,本发明提供了一种电迁移测试结构,包括存储区域和位于所述存储区域外部的外围区域;所述电迁移测试结构还包括:

7.测试层,连续分布于所述存储区域和所述外围区域;

8.互连结构,位于所述存储区域,包括互连层和半导体层,所述互连层的一端连接所述测试层、另一端连接所述半导体层;

9.监控结构,位于所述外围区域,连接所述测试层且分布于所述互连层的相对两外侧,用于监控所述测试层的电阻变化。

10.可选的,所述监控结构包括:

11.接触插塞,所述接触插塞与所述互连层均沿平行于所述半导体层指向所述测试层的方向延伸;

12.转接层,所述接触插塞的一端与所述测试层接触连接、另一端连接所述转接层,所述转接层和所述半导体层均沿垂直于所述半导体层指向所述测试层的方向延伸。

13.可选的,所述接触插塞与所述转接层之间的接触电阻小于所述互连层与所述半导

体层之间的接触电阻。

14.可选的,所述接触插塞包括第一子接触插塞和第二子接触插塞;所述电迁移测试结构还包括:

15.第一介质层,位于所述半导体层背离所述互连层的表面,所述转接层位于所述第一介质层背离所述互连层的表面,所述第一子接触插塞沿平行于所述半导体层指向所述测试层的方向贯穿所述第一介质层并与所述转接层接触连接;

16.第二介质层,位于所述半导体层与所述测试层之间,所述互连层沿平行于所述半导体层指向所述测试层的方向贯穿所述第二介质层,所述第二子接触插塞沿平行于所述半导体层指向所述测试层的方向贯穿所述第二介质层和所述半导体层、并与所述第一子接触插塞接触连接。

17.可选的,所述第一介质层连续分布于所述存储区域和所述外围区域;

18.所述存储区域包括存储阵列,所述第一介质层覆盖所述存储阵列。

19.可选的,所述监控结构内部的接触电阻小于或者等于所述测试层的初始电阻,所述初始电阻是指所述测试层进行电迁移测试之前的电阻。

20.为了解决上述问题,本发明还提供了一种电迁移测试结构的形成方法,包括如下步骤:

21.于存储区域形成互连结构、并于所述存储区域外部的外围区域形成监控结构,所述互连结构包括半导体层、以及位于所述半导体层表面的互连层,所述监控结构分布于所述互连层的相对两外侧;

22.形成与所述互连层和所述监控结构均连接、且连续分布于所述存储区域和所述外围区域的测试层,所述监控结构用于监控所述测试层的电阻变化。

23.可选的,于存储区域形成互连结构、并于所述存储区域外部的外围区域形成监控结构的具体步骤包括:

24.于存储区域形成包括接触插塞和转接层的所述监控结构、并于所述存储区域外部的外围区域形成包括所述半导体层和所述互连层的互连结构,所述接触插塞贯穿所述半导体层,且所述接触插塞的一端与所述转接层接触连接、另一端用于与测试层连接,所述接触插塞与所述互连层均沿平行于所述半导体层指向所述测试层的方向延伸,所述转接层和所述半导体层均沿垂直于所述半导体层指向所述测试层的方向延伸。

25.可选的,于存储区域形成包括接触插塞和转接层的所述监控结构、并于所述存储区域外部的外围区域形成包括所述半导体层和所述互连层的互连结构的具体步骤包括:

26.形成第一介质层;

27.形成贯穿所述第一介质层的第一子接触插塞;

28.于所述第一介质层表面形成与所述第一子接触插塞连接的转接层;

29.于所述第一介质层背离所述转接层的表面形成所述半导体层;

30.于所述半导体层背离所述第一介质层的表面形成第二介质层;

31.形成贯穿所述第二介质层和所述半导体层的第二子接触插塞、并形成贯穿所述第二介质层的所述互连层,以形成包括所述第一子接触区插塞和所述第二子接触插塞的所述接触插塞。

32.可选的,所述第一介质层连续分布于存储区域和所述外围区域;

33.所述存储区域包括存储阵列,所述第一介质层覆盖所述存储阵列。

34.可选的,所述接触插塞与所述转接层之间的接触电阻小于所述互连层与所述半导体层之间的接触电阻。

35.可选的,所述监控结构内部的接触电阻小于或者等于所述测试层的初始电阻,所述初始电阻是指所述测试层进行电迁移测试之前的电阻。

36.为了解决上述问题,本发明还提供了一种电迁移测试方法,包括如下步骤:

37.施加测试电流信号至一测试层,所述测试层连续分布于存储区域和外围区域,所述测试层连接位于所述存储区域的互连结构,所述互连结构包括互连层和半导体层,所述互连层的一端连接所述测试层、另一端连接所述半导体层,所述外围区域位于所述存储区域的外部;

38.通过位于所述外围区域、且分布于所述互连层的相对两外侧、并与所述测试层连接的监控结构监控所述测试层的电阻变化。

39.可选的,施加测试电流信号至一测试层的具体步骤包括:

40.连接所述半导体层与第一外部焊垫;

41.自所述第一外部焊垫、经所述半导体层和所述互连层,传输所述测试电流信号至所述测试层。

42.可选的,所述监控结构包括接触插塞和转接层,所述接触插塞一端与所述测试层接触连接、另一端与所述转接层接触连接,所述接触插塞与所述互连层均沿平行于所述半导体层指向所述测试层的方向延伸,所述转接层和所述半导体层均沿垂直于所述半导体层指向所述测试层的方向延伸;通过分布于所述互连层的相对两外侧且与所述测试层连接的监控结构监控所述测试层的电阻变化的具体步骤包括:

43.连接所述转接层与第二外部焊垫;

44.通过所述第二外部焊垫监控所述测试层的电阻变化。

45.可选的,所述接触插塞与所述转接层之间的接触电阻小于所述互连层与所述半导体层之间的接触电阻。

46.可选的,所述监控结构内部的接触电阻小于或者等于所述测试层的初始电阻,所述初始电阻是指所述测试层进行电迁移测试之前的电阻。

47.为了解决上述问题,本发明还提供了一种存储器,包括存储阵列晶圆,所述存储阵列晶圆包括如上任一项所述的电迁移测试结构。

48.本发明提供的一种电迁移测试结构及其形成方法、电迁移测试方法、存储器,通过在与测试层连接的互连结构的外部额外设置监控结构,且使得所述测试层连续分布于存储区域和位于存储区域外部的外围区域、所述互连结构位于所述存储区域、所述监控结构位于所述外围区域,通过所述监控结构监测所述测试层在电迁移测试过程中的电阻变化,避免了所述互连结构内部的电阻对所述测试层电阻监测的影响,提高了电迁移测试结果的准确度和可靠性。

附图说明

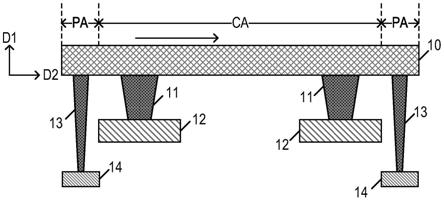

49.附图1是本发明具体实施方式中电迁移测试结构的结构示意图;

50.附图2是本发明具体实施方式中存储器的结构示意图;

51.附图3是本发明具体实施方式中电迁移测试结构的形成方法流程图;

52.附图4是本发明具体实施方式中电迁移测试方法流程图。

具体实施方式

53.下面结合附图对本发明提供的电迁移测试结构及其形成方法、电迁移测试方法的具体实施方式做详细说明。

54.在3d nand存储器等三维存储器结构中,通过npu(nwell pick up,n阱引出)结构将阱区与btm(bottom top metal,底部顶部金属)连接起来。但是,npu的材料通常为金属材料,而所述阱区的材料通常为硅,因此,npu与阱区之间存在较大的接触电阻。当前在对btm进行电迁移测试时,测试信号经所述阱区、所述npu传输至btm,之后,通过自所述阱区引出的引脚监控电阻变化,即当前监控的是btm、npu和阱区整体的电阻。然而,由于npu与阱区之间存在较大的接触电阻,btm的电阻远小于npu与阱区之间的接触电阻,因此,如果btm与npu之间的界面接触有问题,且由于电迁移效应在btm内部产生了巨大的空洞,但是通过监控电阻变化却无法发现,从而导致电迁移测试结果的可靠性和准确度较低。

55.为了提高电迁移测试结果的准确度和可靠性,本具体实施方式提供了一种电迁移测试结构,附图1是本发明具体实施方式中电迁移测试结构的结构示意图。如图1所示,所述电迁移测试结构,包括存储区域ca和位于所述存储区域ca外部的外围区域pa;所述电迁移测试结构还包括:

56.测试层10,连续分布所述存储区域ca和所述外围区域pa;

57.互连结构,位于所述存储区域ca,包括互连层11和半导体层12,所述互连层11的一端连接所述测试层10、另一端连接所述半导体层12;

58.监控结构,位于所述外围区域pa,连接所述测试层10且分布于所述互连层11的相对两外侧,用于监控所述测试层10的电阻变化。

59.具体来说,所述测试层10可以为一条待测金属线。所述测试层10、所述互连层11和所述半导体层12共同形成待测结构。所述互连层11沿第一方向d1(即平行于所述半导体层12指向所述测试层10的方向)延伸,所述测试层10和所述半导体层12沿第二方向d2(即垂直于所述半导体层12指向所述测试层10的方向)延伸,所述第一方向d1与所述第二方向d2相交。本具体实施方式中所述的相交可以是垂直相交,也可以是倾斜相交,本具体实施方式以所述第一方向d1与所述第二方向d2为垂直相交为例进行说明。

60.在电迁移测试的过程中,来自于外界的测试信号经所述半导体层12、所述互连层11传输至所述测试层10,并通过与所述测试层10连接且分布于所述互连层11的相对两外侧的所述监控结构直接监控所述测试层10的电阻变化,即本具体实施方式中的所述监控结构仅监控所述测试层10的电阻变化,所述互连结构内部的电阻不影响所述监控结构对所述测试层10电阻的监控,若所述互连层11与所述测试层10之间的界面接触异常,由于电迁移效应在所述测试层10内部产生了空洞之后,通过所述监控结构即可及时、准确的监控到,从而提高了电迁移测试结果的准确度和可靠性。图1中的箭头方向表示电迁移测试过程中电子的流动方向。

61.可选的,所述监控结构包括:

62.接触插塞13,所述接触插塞13与所述互连层11均沿平行于所述半导体层12指向所

述测试层10的方向延伸;

63.转接层14,所述接触插塞13的一端与所述测试层10接触连接、另一端连接所述转接层14,所述转接层14和所述半导体层12均沿垂直于所述半导体层12指向所述测试层10的方向延伸。

64.具体来说,如图1所示,所述监控结构包括所述接触插塞13和所述转接层14。两个所述接触插塞13分布于所述互连结构的相对两侧,两个所述转接层14与两个所述接触插塞13一一对应连接,从而使得所述测试层10与位于所述互连结构相对两侧的两个所述接触插塞、以及两个所述转接层形成检测回路,以实现对所述测试层10电阻变化的监测。

65.本具体实施方式是以所述接触插塞13与所述互连层11位于所述测试层10的同一侧为例进行说明,以缩小所述电迁移测试结构整体的体积。在其他具体实施方式中,也可以将所述接触插塞13与所述互连层11设置于所述测试层10的不同侧,以避免所述接触插塞13中的信号与所述互连层11中的信号的相互干扰。

66.可选的,所述接触插塞13与所述转接层14之间的接触电阻小于所述互连层11与所述半导体层12之间的接触电阻。

67.具体来说,通过将所述接触插塞13与所述转接层14之间的接触电阻设置为小于所述互连层11与所述半导体层12之间的接触电阻,从而能够降低所述接触插塞13与所述转接层14之间的接触电阻对所述测试层10电阻监测结果的影响。

68.可选的,所述监控结构内部的接触电阻小于或者等于所述测试层10的初始电阻,,所述初始电阻是指所述测试层10进行电迁移测试之前的电阻。

69.具体来说,通过将所述监控结构内部的接触电阻小于或者等于所述测试层10的电阻,也能够降低所述监控结构内部的接触电阻对所述测试层10电阻监测结果的影响。所述接触插塞13与所述转接层14之间的接触电阻应与所述测试层10的初始电阻(即未进行电迁移测试之前的电阻)接近,例如所述接触插塞13与所述转接层14之间的接触电阻与所述测试层10的初始电阻之间的差值小于10欧姆。在一示例中,所述测试层10的初始电阻为50欧姆,所述互连层11与所述半导体层12之间接触电阻为1000欧姆,所述接触插塞13与所述转接层14之间的接触电阻为50欧姆。

70.可选的,所述接触插塞13包括第一子接触插塞131和第二子接触插塞132;所述电迁移测试结构还包括:

71.第一介质层20,位于所述半导体层12背离所述互连层11的表面,所述转接层14位于所述第一介质层20背离所述互连层11的表面,所述第一子接触插塞131沿平行于所述半导体层12指向所述测试层10的方向贯穿所述第一介质层20并与所述转接层14接触连接;

72.第二介质层21,位于所述半导体层12与所述测试层10之间,所述互连层11沿平行于所述半导体层12指向所述测试层10的方向贯穿所述第二介质层21,所述第二子接触插塞132沿平行于所述半导体层12指向所述测试层10的方向贯穿所述第二介质层21和所述半导体层12、并与所述第一子接触插塞131接触连接。

73.可选的,所述第一介质层20连续分布于存储区域ca和所述外围区域pa;

74.所述存储区域ca包括存储阵列,所述第一介质层20覆盖所述存储阵列。

75.不仅如此,本具体实施方式还提供了一种存储器,附图2是本发明具体实施方式中存储器的结构示意图。本具体实施方式中所述的存储器可以是但不限于3d nand等三维存

储器。所述存储器包括存储阵列晶圆,所述存储阵列晶圆包括如上任一项所述的电迁移测试结构。

76.举例来说,所述存储器为三维存储器,所述三维存储器包括相互键合的外围电路晶圆(例如cmos晶圆)和存储阵列晶圆。如图2所示,所述存储阵列晶圆包括沿平行于所述半导体层12指向所述测试层10的方向依次叠置的所述测试层10、所述第二介质层21、所述半导体层12和所述第一介质层20。所述存储阵列晶圆包括所述存储区域ca和位于所述存储区域ca外部的所述外围区域pa。所述第一介质层20内部包括位于所述存储区域ca的存储阵列以及位于所述外围区域pa的所述第一接触插塞131。所述第一介质层20背离所述半导体层12的表面设置有所述转接层14,即所述转接层14可以与所述存储阵列晶圆的第一金属层(m1层)同层设置。所述外围电路晶圆中包括cmos电路层。所述第一金属层用于连接所述存储阵列中的存储结构(例如沟道结构等)与所述外围电路晶圆中的所述cmos电路层。所述第二接触插塞132沿平行于所述半导体层12指向所述测试层10的方向贯穿所述第二介质层21和所述半导体层12,并与所述第一接触插塞131接触连接。所述半导体层12的材料可以为多晶硅材料,作为所述存储阵列晶圆的n阱。所述互连层11的材料可以为金属材料(例如钨),作为所述存储阵列晶圆的n阱引出层。所述测试层10的材料可以为金属材料(例如铝),作为所述存储阵列晶圆的底部顶部金属层。

77.不仅如此,本具体实施方式还提供了一种电迁移测试结构的形成方法,图3是本发明具体实施方式中电迁移测试结构的形成方法流程图。本具体实施方式形成的所述电迁移测试结构的示意图可参见图1。如图1和图3所示,所述电迁移测试结构的形成方法,包括如下步骤:

78.步骤s31,于存储区域ca形成互连结构、并于所述存储区域ca外部的外围区域pa形成监控结构,所述互连结构包括半导体层12、以及位于所述半导体层12表面的互连层11,所述监控结构分布于所述互连层11的相对两外侧;

79.步骤s32,形成与所述互连层11和所述监控结构均连接、且连续分布于所述存储区域ca和所述外围区域pa的测试层10,所述监控结构用于监控所述测试层10的电阻变化。

80.可选的,于存储区域ca形成互连结构、并于所述存储区域ca外部的外围区域pa形成监控结构的具体步骤包括:

81.于存储区域ca形成包括接触插塞13和转接层14的所述监控结构、并于所述存储区域ca外部的外围区域pa形成包括所述半导体层12和所述互连层11的互连结构,所述接触插塞13贯穿所述半导体层12,且所述接触插塞13的一端与所述转接层14接触连接、另一端用于与测试层10连接,所述接触插塞13与所述互连层11均沿平行于所述半导体层12指向所述测试层10的方向延伸,所述转接层14和所述半导体层12均沿垂直于所述半导体层12指向所述测试层10的方向延伸。

82.可选的,于所述存储区域ca形成包括接触插塞13和转接层14的所述监控结构、并于所述存储区域ca外部的外围区域pa包括所述半导体层12和所述互连层11的互连结构的具体步骤包括:

83.形成第一介质层20;

84.形成贯穿所述第一介质层20的第一子接触插塞131;

85.于所述第一介质层20表面形成与所述第一子接触插塞131连接的转接层14;

86.于所述第一介质层20背离所述转接层14的表面形成所述半导体层12;

87.于所述半导体层12背离所述第一介质层20的表面形成第二介质层21;

88.形成贯穿所述第二介质层21和所述半导体层12的第二子接触插塞132、并形成贯穿所述第二介质层21的所述互连层11,以形成包括所述第一子接触区插塞131和所述第二子接触插塞132的所述接触插塞13。

89.可选的,所述第一介质层20连续分布于所述存储区域ca和所述外围区域pa;

90.所述存储区域ca包括存储阵列,所述第一介质层20覆盖所述存储阵列。

91.以下以所述三维存储器为3d nand存储器为例进行说明。可以在形成所述存储阵列中用于与栅极层连接的栅极接触插塞的同时形成所述第一子接触插塞131,在形成所述存储阵列晶圆的第一金属层的同时形成所述转接层14,从而无需增加额外的步骤。所述第一子接触插塞131与所述第二子接触插塞132的材料可以为钨,所述转接层14的材料可以为铜。所述第一接触插塞131和所述第二接触插塞132、以及所述转接层14均位于所述外围区域pa,因而不会对所述存储区域的所述存储阵列造成影响。

92.可选的,所述接触插塞13与所述转接层14之间的接触电阻小于所述互连层11与所述半导体层12之间的接触电阻。

93.可选的,所述监控结构内部的接触电阻小于或者等于所述测试层10的初始电阻,所述初始电阻是指所述测试层10进行电迁移测试之前的电阻。

94.不仅如此,本具体实施方式还提供了一种电迁移测试方法,附图4是本发明具体实施方式中电迁移测试方法流程图。本具体实施方式提供的所述电迁移测试方法可以对如图1所示的电迁移测试结构进行电迁移测试。如图1和图4所示,所述电迁移测试方法,包括如下步骤:

95.步骤s41,施加测试电流信号至一测试层10,所述测试层10连续分布于存储区域ca和外围区域pa,所述测试层10连接位于所述存储区域ca的互连结构,所述互连结构包括互连层11和半导体层12,所述互连层11的一端连接所述测试层10、另一端连接所述半导体层12,所述外围区域pa位于所述存储区域ca的外部;

96.步骤s42,通过位于所述外围区域pa、且分布于所述互连层11的相对两外侧且与所述测试层10连接的监控结构监控所述测试层10的电阻变化。

97.可选的,施加测试电流信号至一测试层10的具体步骤包括:

98.连接所述半导体层12与第一外部焊垫;

99.自所述第一外部焊垫、经所述半导体层12和所述互连层11,传输所述测试电流信号至所述测试层10。

100.可选的,所述监控结构包括接触插塞13和转接层14,所述接触插塞13一端与所述测试层10接触连接、另一端与所述转接层14接触连接,所述接触插塞13与所述互连层11均沿平行于所述半导体层12指向所述测试层10的方向延伸,所述转接层14和所述半导体层12均沿垂直于所述半导体层12指向所述测试层10的方向延伸;通过分布于所述互连层11的相对两外侧且与所述测试层10连接的监控结构监控所述测试层10的电阻变化的具体步骤包括:

101.连接所述转接层14与第二外部焊垫;

102.通过所述第二外部焊垫监控所述测试层10的电阻变化。

103.具体来说,为了检测所述互连层11与所述测试层10之间的界面接触是否正常而实施的电迁移测试过程中,通过所述第一外部焊垫将电迁移测试信号经所述半导体层12、所述互连层11施加至所述测试层10,所述监控结构通过所述接触插塞13、所述转接层14将所述测试层10的触点引出至所述第二外部焊垫,从而监控且仅监控所述测试层10的电阻变化。

104.可选的,所述接触插塞13与所述转接层14之间的接触电阻小于所述互连层11与所述半导体层12之间的接触电阻。

105.可选的,所述监控结构内部的接触电阻小于或者等于所述测试层10的初始电阻,所述初始电阻是指所述测试层10进行电迁移测试之前的电阻。

106.本具体实施方式提供的一种电迁移测试结构及其形成方法、电迁移测试方法、存储器,通过在与测试层连接的互连结构的外部额外设置监控结构,且使得所述测试层连续分布于存储区域和位于存储区域外部的外围区域、所述互连结构位于所述存储区域、所述监控结构位于所述外围区域,通过所述监控结构监测所述测试层在电迁移测试过程中的电阻变化,避免了所述互连结构内部的电阻对所述测试层电阻监测的影响,提高了电迁移测试结果的准确度和可靠性。

107.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1