应用于超导集成电路的堆栈式电连接结构及其制备方法

1.本发明涉及超导量子器件技术领域,特别是涉及一种应用于超导集成电路的堆栈式电连接结构及其制备方法。

背景技术:

2.超导电路是利用超导材料制备而成的电子器件,主要包括超导量子干涉器(squid),单磁通量子器件(sfq)等应用超导约瑟夫森结的电路器件。超导量子干涉器件(superconducting quantum interference device,squid)是基于约瑟夫森效应和磁通量子化原理的超导量子器件,它的基本结构是在超导环中插入两个约瑟夫森结,squid是目前已知的最灵敏的磁通探测传感器,典型的squid器件的磁通噪声在μφ0/hz

1/2

量级(1φ0=2.07

×

10-15

wb),其磁场噪声在ft/hz

1/2

量级(1ft=1

×

10-15

t),由于其具有极高的灵敏度,可广泛应用于医学心磁脑磁、材料探测、地球磁场、军事、地震和考古等各方面,用其制备的磁通显微镜可从事基础研究。单磁通量子器件(single flux quantum,sfq)是利用约瑟夫森结内的单个磁通量子来表示逻辑“1”和“0”的超导电路技术。以此为基础的超导数字电路时钟频率可达770ghz,可用于雷达和通信系统的超宽带模数/数模转换器、宽带网络交换器、射电天文的数字式自相关器以及超导计算机等。

3.目前,超导电路的开发是朝着大规模高集成度的超导集成电路方向发展的。以中国科学院上海微系统与信息技术研究所超导卓越中心研发的simit-nb03工艺为例,其只有一层配线层,它所能承载的电路规模被限制在在105个约瑟夫森结量级(105jj),所以我们想到通过增加nb金属层数来增加配线层实现更高电路集成度的工艺结构,然而simit-nb03的工艺制程是没有对绝缘层进行化学机械抛光(chemical mechanical polishing,cmp)的平坦化处理的,所以在绝缘层开孔后,通常设计后一层nb金属的厚度比绝缘层的厚度多50nm~100nm来保证台阶完全覆盖和通孔的连接性。这种情况下,如果增加nb金属层数,不论nb薄膜还是绝缘层薄膜都只能随着层数的增加越来越厚,绝缘层薄膜越厚,开孔就需要越大才能保证通孔的连通;此外,起伏的金属层不仅增加了通孔产生缺陷的风险,还会导致电流流过金属层产生电流路径的弯折,引起不必要的电流不均匀分布,从而形成很大的寄生电感,起伏的绝缘层也会导致金属层间的电感、电容的不均匀。因此在simit-nb03工艺的基础上进行改进有了simit-nb04工艺。simit-nb04工艺多了四层配线层,假设用最顶层的配线层进行约瑟夫森结的连接,其开孔次数为五次。

4.在目前simit研发的双层约瑟夫森结的工艺中,约瑟夫森结在工艺结构中呈堆栈形式,这种工艺结构使电路密度至少增加两倍,下层约瑟夫森结与上层约瑟夫森结的连接是下层结的底电极与上层结的顶电极的相连,其连接所要跨越的绝缘层数为四层,要进行四次开孔,其中前三层绝缘层都有进行平坦化处理。

5.由此可见,超导集成电路的vlsi(very large scale integration)不可避免要增加更多的金属层,增加更多的金属层也就不可规避需要进行连续开孔的问题。在超导集成电路中,连续开孔方式主要有两种:如图1所示的交错式连续开孔和如图2所示的堆栈式连

续开孔。交错开孔的连通性良好,开孔的尺寸与相邻层的通孔的大小无关,只与绝缘层的厚度有关,但是通孔不规则,通孔电感大难以压制,尤其在sfq电路中电感参数是关键性参数,尤其是连接约瑟夫森结之间的电感,需要控制偏差在

±

5%内,交错开孔的连续开孔方法很难控制通孔电感为小电感。堆栈开孔的工艺密度比较大,所以电连接结构的尺寸相对交错开孔的方式较小,但电连通性不好,且孔只能越开越大,电感也不好控制。另外,这两种开孔方法都不可避免有刻蚀的通孔具有坡度的问题。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种应用于超导集成电路的堆栈式电连接结构及其制备方法,用于解决现有技术中超导集成电路的堆栈式电连接结构的连续开孔过程中,采用交错开孔,通孔不规则,通孔电感大难以压制;采用堆栈开孔,电连通性不好,且孔只能越开越大,电感也不好控制;另外,这两种开孔方法都不可避免有刻蚀的通孔具有坡度的问题。

7.为实现上述目的及其他相关目的,本发明提供一种应用于超导集成电路的堆栈式电连接结构的制备方法,所述制备方法包括:

8.提供衬底,所述衬底上形成有第一超导金属层,并于所述衬底上形成第一绝缘层;

9.刻蚀所述第一绝缘层至裸露出所述第一超导金属层的表面;

10.于上述结构上涂覆光刻胶层,并进行图形化,形成光刻窗口,所述光刻窗口裸露出后续需要连通的部分所述第一超导金属层的表面;

11.于上述结构上形成一层超导材料层;

12.去除所述光刻胶层及该光刻胶层上的所述超导材料层,剩余的所述超导材料层形成为超导连接层;

13.于上述结构上形成第二绝缘层;

14.刻蚀所述第二绝缘层至裸露出所述超导连接层的表面;

15.于上述结构上形成第二超导金属层。

16.可选地,对上述步骤依次再循环n次,n≥1,直至达到预设的超导金属层层数。

17.进一步地,n=3。

18.可选地,所述第一超导金属层包括氮化铌层及铌层中的至少一种;所述超导连接层包括氮化铌层及铌层中的至少一种;所述第二超导金属层包括氮化铌层及铌层中的至少一种。

19.可选地,所述第一绝缘层的材料包括sio2或sinx;所述第二绝缘层的材料包括sio2或sinx。

20.可选地,采用cmp工艺抛光所述第一绝缘层至裸露出所述第一超导金属层的表面;采用cmp工艺抛光所述第二绝缘层至裸露出所述超导连接层的表面。

21.可选地,采用磁控溅射工艺形成所述超导材料层;采用磁控溅射工艺形成所述第二超导金属层。

22.可选地,形成所述第二超导金属层的方法包括。

23.于所得结构表面形成一层超导金属材料层;

24.对所述超导金属材料层进行光刻刻蚀,得到所述第二超导金属层。

25.可选地,所述第二超导金属层的尺寸不大于所述第一超导金属层的尺寸。

26.本发明还提供一种应用于超导集成电路的堆栈式电连接结构,所述电连接结构采用如上任一所述的应用于超导集成电路的堆栈式电连接结构的制备方法制备得到。

27.如上所述,本发明的应用于超导集成电路的堆栈式电连接结构及其制备方法,通过对光刻胶层进行图形化形成光刻窗口,并基于该光刻窗口形成超导连接层,然后在该超导连接层上形成上层超导金属层,实现上下两层超导金属层通过超导连接层的电性连通。由于光刻胶层是通过曝光显影形成光刻窗口,光刻窗口的形状非常规则,所以形成的超导连接层形状非常规则,同时上层超导金属层形成于该规则的超导连接层上,如此实现预设层数超导金属层的互连,得到的电连接结构具有方块电感的特点,电感值小且易控制;另外,形成的电连接通路图形规整完好,大幅提升孔洞的导通承载电流,且电流路径没有弯折,电流分布均匀;最后,光刻窗口的工艺密度大,可以有效降低电连接结构的体积。

附图说明

28.图1显示为现有技术中采用交错式连续开孔的主要工艺流程中各步骤呈现的截面结构示意图。

29.图2显示为现有技术中采用堆栈式连续开孔的主要工艺流程中各步骤所呈现的截面结构示意图。

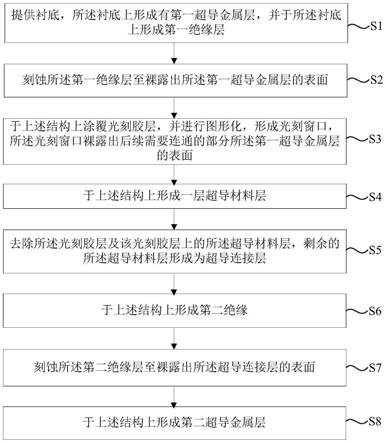

30.图3显示为本发明的应用于超导集成电路的堆栈式电连接结构的制备方法流程图。

31.图4至图16显示为本发明的应用于超导集成电路的堆栈式电连接结构的制备过程中各步骤所呈现的截面结构示意图。

32.元件标号说明

33.300

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

衬底

34.301

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一超导金属层

35.302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一绝缘层

36.303

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光刻胶层

37.304

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光刻窗口

38.305

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

超导材料层

39.306

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

超导连接层

40.307

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二绝缘层

41.308

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

超导金属材料层

42.309

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二超导金属层

43.310

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

绝缘介质层

44.311

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三超导金属层

45.312

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四超导金属层

46.313

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第五超导金属层

47.s1~s8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

步骤

具体实施方式

48.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

49.请参阅图1至图16。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可根据实际需要进行改变,且其组件布局型态也可能更为复杂。

50.如背景技术中所述,在超导集成电路的电连接结构中连续开孔的方式主要有两种,一种为交错式连续开孔,另一种为堆栈式连续开孔。

51.如图1所示为采用交错式连续开孔工艺制备5层超导金属层的电连接结构的各步骤截面结构示意图,该工艺过程主要包括:1、如图1中的1a所示,对覆盖在m1超导金属层上的i1绝缘层进行i1通孔刻蚀,通过i1通孔裸露出m1超导金属层;2、如图1中的1b所示,溅射一层m2超导金属层,且厚度大于i1绝缘层以保证台阶覆盖和通孔连接;3、如图1中的1c所示,沉积一层很厚的绝缘层;4、如图1中的1d所示,在此很厚的绝缘层基础上进行cmp,形成i2绝缘层;5、如图1中的1e所示,在i1通孔的非正上方位置进行i2开孔,i2通孔大小取决于开孔位置的二氧化硅的厚度,与i1通孔的大小没有直接联系,后续溅射一层m3超导金属层;6、如图1中的1f所示,重复上述3、4、5的步骤,得到i3绝缘层及m4超导金属层;7、如图1中的1g所示,沉积一层高质量绝缘层i4,此层不做cmp;8、如图1中的1h所示,在i4通孔的非正上方位置进行i4开孔后溅射一层m5超导金属层。从上述制备过程中可看出,交错式连续开孔的电连通性能较佳,开孔的尺寸与相邻层的通孔的大小无关,只与绝缘层的厚度相关,但刻蚀的通孔具有坡度,导致通孔不规则,通孔电感大难以压制,在sfq电路中电感参数是关键性参数,尤其是连接约瑟夫森结之间的电感,需要控制偏差在

±

5%内,交错连续开孔的方法很难控制通孔电感为小电感;另外,形成的电连接结构会导致电流流过超导金属层产生电流路径的弯折,引起电流的不均匀分布;最后,交错式的开孔会导致形成的电连接结构体积较大,降低超导集成电路的集成度。

52.如图2所示为采用堆栈式连续开孔工艺制备5层超导金属层的电连接结构的各步骤截面结构示意图,该工艺过程主要包括:1、如图2中的2a所示,对覆盖在m1超导金属层上的i1绝缘层进行i1通孔刻蚀,通过i1通孔裸露出m1超导金属层;2、如图2中的2b所示,溅射一层m2超导金属层,且厚度大于i1绝缘层以保证台阶覆盖和通孔连接;3、如图2中的2c所示,沉积一层很厚的绝缘层;4、如图2中的2d所示,在此很厚的绝缘层基础上进行cmp,形成i2绝缘层;5、如图2中的2e所示,在i1通孔的正上方位置进行i2开孔,i2通孔的大小必须大于i1通孔的大小,后续溅射一层m3超导金属层;6、如图2中的2f所示,重复上述3、4、5的步骤,得到i3绝缘层及m4超导金属层,为了保持电连通性,每一层的通孔都要比下层的通孔大;7、如图2中的2g所示,沉积一层高质量绝缘层i4,此层不做cmp;8、如图2中的2h所示,在i4通孔的正上方位置进行i4开孔后溅射一层m5超导金属层。从上述制备过程中可看出,堆栈式连续开孔的工艺密度比较大,可以降低电连接结构的体积,但刻蚀的通孔同样具有坡度且孔只能越开越大,导致通孔不规则,通孔电感同样不好控制,另外,形成的电连接结构

同样会导致电流流过超导金属层产生电流路径的弯折,引起电流的不均匀分布;最后,该方式形成的电连接结构电连通性能不好。

53.基于上述现有技术存在的问题,本发明提供一种应用于超导集成电路的堆栈式电连接结构的制备方法,所述制备方法包括如下步骤:

54.s1、提供衬底,所述衬底上形成有第一超导金属层,并于所述衬底上形成第一绝缘层;

55.s2、刻蚀所述第一绝缘层至裸露出所述第一超导金属层的表面;

56.s3、于上述结构上涂覆光刻胶层,并进行图形化,形成光刻窗口,所述光刻窗口裸露出后续需要连通的部分所述第一超导金属层的表面;

57.s4、于上述结构上形成一层超导材料层;

58.s5、去除所述光刻胶层及该光刻胶层上的所述超导材料层,剩余的所述超导材料层形成为超导连接层;

59.s6、于上述结构上形成第二绝缘层;

60.s7、刻蚀所述第二绝缘层至裸露出所述超导连接层的表面;

61.s8、于上述结构上形成第二超导金属层。

62.本发明的电连接结构的制备方法,通过对光刻胶层进行图形化形成光刻窗口,并基于该光刻窗口形成超导连接层,然后在该超导连接层上形成上层超导金属层,实现上下两层超导金属层通过超导连接层的电性连通。由于光刻胶层是通过曝光显影形成光刻窗口,光刻窗口的形状非常规则,所以形成的超导连接层形状非常规则,同时上层超导金属层形成于该规则的超导连接层上,如此实现预设层数超导金属层的互连,得到的电连接结构具有方块电感的特点,电感值小且易控制;另外,形成的电连接通路图形规整完好,大幅提升孔洞的导通承载电流,且电流路径没有弯折,电流分布均匀;最后,光刻窗口的工艺密度大,可以有效降低电连接结构的体积。

63.下面结合附图详细说明本发明的应用于超导集成电路的堆栈式电连接结构的制备方法。

64.如图3至图5所示,首先进行步骤s1,提供衬底300,所述衬底300上形成有第一超导金属层301(如图4所示),并于所述衬底300上形成第一绝缘层302(如图5所示)。

65.所述衬底300可以包括硅衬底、碳化硅衬底、氧化硅衬底、氧化镁衬底及蓝宝石衬底中的至少一种,但也不限于此,任何适于制备超导集成电路的衬底均可用。

66.作为示例,所述衬底300上还可以形成有一层绝缘介质层310,以使所述第一超导金属层301与衬底300之间电性隔离。所述绝缘介质层310的材料可以选择任意适合的绝缘材料,例如sio2或sinx。

67.所述第一超导金属层301包括氮化铌层及铌层中的至少一种,即,可以是其中的一种,也可以是两种构成的叠层结构,但也不限于此,也可以是其他材料的超导金属层。本实施例中选择所述第一超导金属层301为铌层。

68.作为一示例,形成该第一超导金属层301的方法包括:于所述衬底300上沉积一层超导层;然后对该层超导层进行光刻、刻蚀,得到预设形状的所述第一超导金属层301。

69.这里需要说明的是,所述第一绝缘层302的厚度一般较厚,以利于后续对该第一绝缘层302进行抛光后可以获得较为平袒的表面。所述第一绝缘材料层302的材料包括sio2或

sinx,但也不限于此,其他绝缘性能较佳的材料也可。

70.如图3及图6所示,然后进行步骤s2,刻蚀所述第一绝缘层302至裸露出所述第一超导金属层301的表面。

71.作为示例,采用cmp抛光工艺对所述第一绝缘层302进行抛光至裸露出所述第一超导金属层301的表面。

72.如图3及图7所示,接着进行步骤s3,于上述结构上涂覆光刻胶层303,并进行图形化,形成光刻窗口304,所述光刻窗口304裸露出后续需要连通的部分所述第一超导金属层301的表面。通过曝光显影获得的光刻窗口形状非常规则,这为后续形成规则的超导连接层奠定基础。

73.如图3及图8所示,接着进行步骤s4,于上述结构上形成一层超导材料层305。所述超导材料层305填充满所述光刻窗口304。

74.作为示例,所述超导材料层305包括氮化铌层及铌层中的至少一种,即,可以是其中的一种,也可以是两种构成的叠层结构,但也不限于此,也可以是其他材料的超导金属层。本实施例中选择所述超导材料层305为铌层。

75.作为示例,可以采用pvd工艺形成所述超导材料层305。本实施例中选择采用磁控溅射工艺形成所述超导材料层305。

76.如图3及图9所示,接着进行步骤s5,去除所述光刻胶层303及该光刻胶层303上的所述超导材料层305,剩余的所述超导材料层305形成为超导连接层306。该超导连接层306基于所述刻蚀窗口304形成,所以形成的超导连接层306形状规则,易于控制。

77.如图3及图10所示,接着进行步骤s6,于上述结构上形成第二绝缘层307。

78.这里需要说明的是,所述第二绝缘层307的厚度一般较厚,以利于后续对该第二绝缘层307进行抛光后可以获得较为平袒的表面。所述第二绝缘材料层307的材料包括sio2或sinx,但也不限于此,其他绝缘性能较佳的材料也可。

79.如图3及图11所示,接着进行步骤s7,刻蚀所述第二绝缘层307至裸露出所述超导连接层306的表面。

80.作为示例,采用cmp抛光工艺对所述第二绝缘层307进行抛光至裸露出所述超导连接层306的表面。

81.如图3及图13所示,最后进行步骤s8,于上述结构上形成第二超导金属层309。

82.作为示例,可以采用pvd工艺形成所述第二超导金属层309。本实施例中选择采用磁控溅射工艺形成所述第二超导金属层309。

83.作为示例,所述第二超导金属层309包括氮化铌层及铌层中的至少一种,即,可以是其中的一种,也可以是两种构成的叠层结构,但也不限于此,也可以是其他材料的超导金属层。本实施例中选择所述第二超导金属层309为铌层。

84.如图12及图13所示,作为示例,形成所述第二超导金属层309的方法包括:如图12所示,于所得结构表面形成一层超导金属材料层308;如图13所示,对所述超导金属材料层308进行光刻刻蚀,得到所述第二超导金属层309。

85.作为示例,所述第二超导金属层309的尺寸不大于所述第一超导金属层301的尺寸。这里的尺寸主要指超导金属层的表面积。

86.所述第二超导金属层309形成于所述超导连接层306上,通过所述超导连接层306

实现所述第一超导金属层301与所述第二超导金属层309的电性连接。由于超导连接层306的形状规则,且上下两层的超导金属层的形状可控,从而使整个连通路径形状规则,具有方块电感的特点;且由于连接通路图形规整完好,可大幅提升孔洞的导通承载电流,且电流路径没有弯折,电流分布均匀,电性连通性能好。

87.以上步骤的实施,完成了相邻两层超导金属层通过超导连接层的电性连接。基于此可以依次重复以上步骤,从而实现预设层数n的超导金属层通过超导连接层的电性连接,n≥3。如图14所示,实现了第一超导金属层301、第二超导金属层309及第三超导金属层311三层超导金属层通过超导连接层依次互连的电连接结构;如图15所示,实现了第一超导金属层301、第二超导金属层309、第三超导金属层311及第四超导金属层312四层超导金属层通过超导连接层依次互连的电连接结构;如图16所示,实现了第一超导金属层301、第二超导金属层309、第三超导金属层311、第四超导金属层312及第五超导连接层313五层超导金属层通过超导连接层依次互连的电连接结构。该方式互连的层数越多,光刻窗口的工艺密度越大,可以有效降低电连接结构的体积,利于超导集成电路的集成。

88.作为示例,形成的堆栈式电连接结构中所有的超导金属层的材料及结构均相同,即第一超导金属层至第n超导金属层及超导连接层,以利于理论计算及仿真效果模拟。

89.作为示例,形成的堆栈式电连接结构中所有的绝缘层的材料及结构保持一致,即第一绝缘层至第n-1绝缘层,从而实现同质生长的绝缘材料层,同质生长不存在明显界面,对后续工艺无影响。

90.本实施例还提供一种应用于超导集成电路的堆栈式电连接结构,采用如上所述的应用于超导集成电路的堆栈式电连接结构的制备方法制备得到。

91.综上所述,本发明提供一种应用于超导集成电路的堆栈式电连接结构及其制备方法,通过对光刻胶层进行图形化形成光刻窗口,并基于该光刻窗口形成超导连接层,然后在该超导连接层上形成上层超导金属层,实现上下两层超导金属层通过超导连接层的电性连通。由于光刻胶层是通过曝光显影形成光刻窗口,光刻窗口的形状非常规则,所以形成的超导连接层形状非常规则,同时上层超导金属层形成于该规则的超导连接层上,如此实现预设层数超导金属层的互连,得到的电连接结构具有方块电感的特点,电感值小且易控制;另外,形成的电连接通路图形规整完好,大幅提升孔洞的导通承载电流,且电流路径没有弯折,电流分布均匀;最后,光刻窗口的工艺密度大,可以有效降低电连接结构的体积。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

92.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1