半导体封装结构和半导体封装结构的制备方法与流程

1.本发明涉及半导体封装技术领域,具体而言,涉及一种半导体封装结构和半导体封装结构的制备方法。

背景技术:

2.随着半导体行业的快速发展,双面封装产品结构或多芯片封装产品结构,主要是在基板的正反面或单侧形成封装结构,由于在基板上形成半导体封装结构中存在多种封装材料,并且均需要对多个芯片进行封装,导致基板和芯片的散热能力差,影响器件的性能。

技术实现要素:

3.本发明的目的包括,例如,提供了一种半导体封装结构和半导体封装结构的制备方法,其能够提升器件的散热能力。

4.本发明的实施例可以这样实现:

5.第一方面,本发明提供一种半导体封装结构,包括:

6.基板;

7.间隔贴装在所述基板一侧表面的第一芯片和第二芯片;

8.设置在所述基板一侧表面,并位于所述第一芯片和所述第二芯片之间的散热柱;

9.设置在所述基板的一侧表面,并至少包覆在所述第一芯片和所述第二芯片外的第一塑封体;

10.以及,设置在所述基板的另一侧表面的焊球;

11.其中,所述第一芯片、所述第二芯片和所述第三芯片均与所述基板电连接,所述基板的一侧表面设置有金属层,所述散热柱的底部与所述金属层连接,并用于对基板进行散热,所述焊球位于所述第二塑封体的至少两侧,并与基板电连接。

12.在可选的实施方式中,所述半导体封装结构还包括贴装在所述基板另一侧表面的第三芯片,以及设置在所述基板的另一侧表面,并包覆在所述第三芯片外的第二塑封体。

13.在可选的实施方式中,所述第一塑封体还包覆在所述散热柱外。

14.在可选的实施方式中,所述散热柱上设置有多个散热槽,且每个所述散热槽由所述散热柱的表面贯穿至所述金属层的表面。

15.在可选的实施方式中,所述金属层的表面还设置有多个第一凹槽,多个所述第一凹槽位于所述散热柱的底部,并对应地与多个所述散热槽连通。

16.在可选的实施方式中,所述第一芯片和所述第二芯片厚度相同,且所述第一塑封体远离所述基板的一侧表面与所述第一芯片之间的距离h1大于所述第一塑封体远离所述基板的一侧表面与所述散热柱之间的距离h2。

17.在可选的实施方式中,所述第一塑封体远离所述基板的一侧表面与所述第一芯片之间的距离h1为所述第一塑封体远离所述基板的一侧表面与所述散热柱之间的距离h2的两倍。

18.在可选的实施方式中,所述基板内设置有布线层,所述基板的另一侧表面设置有与所述布线层电连接的金属焊盘,所述焊球设置在所述金属焊盘上。

19.在可选的实施方式中,所述金属焊盘的表面还设置有第二凹槽,所述焊球覆盖在所述第二凹槽上。

20.在可选的实施方式中,所述第一塑封体上形成有贯通至所述基板的让位开口槽,所述让位开口槽与所述散热柱对应,以使所述散热柱暴露在所述第一塑封体外。

21.在可选的实施方式中,所述第一塑封体局部包覆在所述散热柱外,且所述散热柱远离所述基板的一端部分伸出所述第一塑封体。

22.在可选的实施方式中,所述散热柱的边缘设置有拓展散热板,所述拓展散热板贴合在所述第一塑封体远离所述基板的一侧表面。

23.在可选的实施方式中,所述拓展散热板覆盖在所述第一塑封体远离所述基板的一侧表面,并延伸至所述第一塑封体的边缘。

24.在可选的实施方式中,所述第一塑封体远离所述基板的一侧还设置有第四芯片,所述第四芯片贴装在所述散热柱上,并与所述基板电连接。

25.在可选的实施方式中,所述第四芯片为正装芯片,且所述第四芯片远离所述基板的一侧设置有导电线弧,所述导电线弧与所述基板连接,所述基板上还设置有包覆在所述导电线弧和所述第四芯片外的填充胶层。

26.在可选的实施方式中,所述第四芯片为倒装芯片,所述散热柱具有导电性,所述第四芯片通过所述散热柱与所述基板电连接,且所述基板上还设置有包覆在所述第四芯片外的第三塑封体或填充胶层。

27.在可选的实施方式中,所述散热柱伸出所述第一塑封体的部分设置有多个第三凹槽。

28.第二方面,本发明提供一种半导体封装结构的制备方法,包括:

29.在基板上形成散热柱;

30.在所述散热柱两侧的所述基板上间隔贴装第一芯片和第二芯片;

31.在所述基板上塑封形成至少包覆在所述第一芯片和所述第二芯片外的第一塑封体;

32.翻转所述基板,并在所述基板上贴装第三芯片;

33.在所述基板上塑封形成包覆在所述第三芯片外的第二塑封体;

34.在所述基板上形成焊球;

35.其中,所述第一芯片、所述第二芯片和所述第三芯片均与所述基板电连接,所述基板的一侧表面设置有金属层,所述散热柱的底部与所述金属层连接,并用于对基板进行散热,所述焊球位于所述第二塑封体的至少两侧,并与基板电连接。

36.在可选的实施方式中,在基板上形成散热柱的步骤,包括:

37.在基板上形成干膜层;

38.刻蚀所述干膜层,以形成蚀刻开口;

39.在所述蚀刻开口内形成散热柱;

40.去除所述干膜层;

41.在所述散热柱的底部微刻蚀,以形成第一凹槽。

42.本发明实施例的有益效果包括,例如:

43.本发明提供的半导体封装结构和半导体封装结构的制备方法,通过在基板贴装第一芯片、第二芯片,实现了多芯片封装,同时在第一芯片和第二芯片之间设置有散热柱,散热柱设置在基板的金属层上,能够起到良好的散热效果。相较于现有技术,本发明提供的半导体封装结构,能够实现对基板良好的散热效果,进而提升整个器件的散热能力,保证器件性能。

附图说明

44.为了更清楚地说明本发明实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

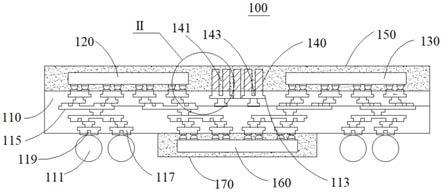

45.图1为本发明第一实施例提供的半导体封装结构的示意图;

46.图2为图1中ⅱ的局部放大示意图;

47.图3至图11为本发明第一实施例提供的半导体封装结构的制备方法的工艺流程图;

48.图12为本发明第二实施例提供的半导体封装结构的示意图;

49.图13为本发明第三实施例提供的半导体封装结构的示意图;

50.图14为本发明第四实施例提供的半导体封装结构的示意图;

51.图15为本发明第五实施例提供的半导体封装结构的示意图;

52.图16为本发明第六实施例提供的半导体封装结构的示意图;

53.图17为本发明第七实施例提供的半导体封装结构的示意图。

54.图标:100-半导体封装结构;110-基板;111-焊球;113-金属层;115-布线层;117-金属焊盘;119-第二凹槽;120-第一芯片;130-第二芯片;140-散热柱;141-散热槽;143-第一凹槽;145-拓展散热板;150-第一塑封体;151-让位开口槽;160-第三芯片;170-第二塑封体;180-第四芯片;181-导电线弧;183-填充胶层;190-第三塑封体;191-第三凹槽;200-干膜层。

具体实施方式

55.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

56.因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

57.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

58.在本发明的描述中,需要说明的是,若出现术语“上”、“下”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

59.此外,若出现术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

60.正如背景技术中所公开的,现有的半导体封装结构,由于采用了多个芯片,发热量大,而塑封体需要覆盖多个芯片,导致器件的整体散热能力较差,从而会影响器件的性能。此外,由于在基板上形成半导体封装结构中存在多种封装材料,而不同封装体的材料使用不同,材料间的cte系数不同,产品在可靠性测试过程中,塑封体与芯片表面容易存在分层问题以及塑封体与基板分层问题。并且,现有的半导体封装结构仅仅能够实现双面封装,集成度难以提升,无法实现堆叠。

61.为了解决上述问题,本发明提供了以下新型的半导体封装结构和半导体封装结构的制备方法,需要说明的是,在不冲突的情况下,本发明的实施例中的特征可以相互结合。

62.第一实施例

63.参见图1和图2,本实施例提供了一种半导体封装结构100,其能够实现对基板110良好的散热效果,进而提升整个器件的散热能力,保证器件性能。同时能够避免塑封体分层问题,保证结构的稳定性。

64.本实施例提供的半导体封装结构100,包括基板110、第一芯片120、第二芯片130、散热柱140、第一塑封体150、第三芯片160、第二塑封体170和焊球111,第一芯片120和第二芯片130间隔贴装在基板110的一侧表面,散热柱140也设置在基板110的一侧表面,并位于第一芯片120和第二芯片130之间,第一塑封体150设置在基板110的一侧表面,并至少包覆在第一芯片120和第二芯片130外,第三芯片160贴装在基板110的另一侧表面,第二塑封体170设置在基板110的另一侧表面,并包覆在第三芯片160外,焊球111设置在基板110的另一侧表面,其中,第一芯片120、第二芯片130和第三芯片160均与基板110电连接,基板110的一侧表面设置有金属层113,散热柱140的底部与金属层113连接,并用于对基板110进行散热,焊球111位于第二塑封体170的至少两侧,并与基板110电连接。

65.在本实施例中,基板110的一侧表面具有贴装区和散热区,贴装区位于散热区的两侧,金属层113设置在散热区,且散热区位于基板110的中心位置,第一芯片120和第二芯片130分别贴装在贴装区,并与基板110电连接。同时,本实施例中第三芯片160的贴装位置与散热区相对应,从而使得焊球111能够分布在第二塑封体170的周围,第二塑封体170采用选择塑封工艺,其仅仅覆盖第三芯片160的外缘,并不会覆盖整个基板110的表面,从而方便焊球111的设置。

66.值得注意的是,本实施例中采用了双面封装结构,同时,在本发明其他较佳的实施例中,基板110的另一侧表面也可以不设置第三芯片160和第二塑封体170,从而形成了单面封装结构。

67.在本实施例中,第一塑封体150还包覆在散热柱140外。具体地,第一塑封体150整体塑封在第一芯片120、第二芯片130和散热柱140外,从而覆盖整个基板110的表面,将第一芯片120、第二芯片130和散热柱140均包覆在内,从而起到良好的保护作用。

68.在本实施例中,散热柱140上设置有多个散热槽141,且每个散热槽141由散热柱140的表面贯穿至金属层113的表面。具体地,通过设置散热槽141,能够将散热柱140分隔成多个柱体结构,从而在塑封时塑封料能够填充在散热槽141内,从而提升第一塑封体150和散热柱140以及基板110之间的结合力。

69.在本实施例中,散热柱140采用铜柱,并通过电镀方式形成在金属层113上,从而使得散热柱140具有良好的散热效果,能够将热量向外传递。当然,在其他较佳的实施例中,散热柱140也可以采用其他导热材料,例如银柱或铝柱等,在此不做具体限定。

70.在本实施例中,金属层113的表面还设置有多个第一凹槽143,多个第一凹槽143位于散热柱140的底部,并对应地与多个散热槽141连通。具体地,散热槽141与多个第一凹槽143一一对应连通,在形成散热柱140后,可以通过微刻蚀工艺在金属层113上继续刻蚀从而形成第一凹槽143,通过设置第一凹槽143,能够使得塑封料继续向下填充,从而提升第一塑封体150、散热柱140以及基板110之间的结合力。

71.需要说明的是,本实施例中第一凹槽143的宽度与散热槽141的宽度相当,并且散热柱140采用电镀金属的工艺形成,从而使得散热柱140与金属层113能够形成为一体,进一步方便热量的传递,同时第一塑封体150的塑封料能够继续填充至第一凹槽143,从而使得第一塑封体150与金属层113之间能够实现相互嵌设,提升了第一塑封体150与基板110之间的结合力,进而防止了基板110与第一塑封体150之间的分层问题。

72.在本实施例中,第一芯片120和第二芯片130厚度相同,且第一塑封体150远离基板110的一侧表面与第一芯片120之间的距离h1大于第一塑封体150远离基板110的一侧表面与散热柱140之间的距离h2。具体地,第一芯片120和第二芯片130均采用倒装芯片,且二者厚度相同,使得第一芯片120和第二芯片130的高度相同,同时第一塑封体150完全包覆在第一芯片120、第二芯片130和散热柱140外,使得第一塑封体150在第一芯片120和第二芯片130处的厚度大于在散热柱140处的厚度,通过在第一芯片120和散热柱140处形成有不同厚度的第一塑封体150,从而避免了第一塑封体150各处的分层厚度一致,防止了芯片背面与第一塑封体150分层的问题。当然,在本发明其他较佳的实施例中,第一芯片120和第二芯片130也可以采用正装芯片,并通过打线方式与基板110实现电连接。

73.需要说明的是,本实施例中第一塑封体150远离基板110的一侧表面与第一芯片120之间的距离h1,指的是第一芯片120的背面与第一塑封体150的表面之间的距离,本实施例中第一塑封体150远离基板110的一侧表面与散热柱140之间的距离h2,指的是散热柱140远离基板110的一端与第一塑封体150的表明之间的距离。

74.在本实施例中,第一塑封体150远离基板110的一侧表面与第一芯片120之间的距离h1为第一塑封体150远离基板110的一侧表面与散热柱140之间的距离h2的两倍。具体地,通过合理设置h1和h2的比例关系,能够更好地防止第一塑封体150发生分层现象。

75.在本实施例中,基板110内设置有布线层115,基板110的另一侧表面设置有与布线层115电连接的金属焊盘117,焊球111设置在金属焊盘117上。具体地,布线层115采用常规的布线结构,同时金属焊盘117设置在第二塑封体170的至少两侧,焊球111能够通过铜柱与布线层115李连杰。焊球111采用锡球,优选地,焊球111相对于基板110的高度大于第二塑封体170的高度,从而能够更好地实现外部焊接。

76.在本实施例中,金属焊盘117的表面还设置有第二凹槽119,焊球111覆盖在第二凹

槽119上。具体地,第二凹槽119也可以采用微刻蚀的方式在金属焊盘117上形成,且第二凹槽119位于金属焊盘117的中心位置,通过设置第二凹槽119,能够在形成焊球111时起到缓冲作用,从而释放焊球111的内部应力,并且能够提升焊球111的结合力。

77.结合参见图3至图11,本实施例还提供了一种半导体封装结构100的制备方法,其包括了以下步骤:

78.s1:在基板110上形成散热柱140。

79.结合参见图3至图6,具体地,提供一基板110,并且在基板110上形成散热柱140。在执行步骤s1时,可以在基板110上形成干膜层200,然后刻蚀干膜层200,以形成蚀刻开口,再在蚀刻开口内形成散热柱140,再去除干膜层200,最后在散热柱140的底部微刻蚀,以形成第一凹槽143,从而完成了散热柱140的制程。其中,干膜层200的厚度可以根据散热柱140的高度设定。

80.在实际制备时,可以首先取一基板110,在基板110上划定散热区和贴装区,散热区内形成铜柱,铜柱制程可以是先将基板110上布设一层干膜,然后利用刻蚀方式将需要形成铜柱的地方刻蚀去除,再在此开口内电镀铜,形成铜柱结构后,去除干膜,再在铜柱底部进行微刻蚀,形成第一凹槽143结构。

81.s2:在散热柱140两侧的基板110上间隔贴装第一芯片120和第二芯片130。

82.结合参见图7,具体地,在形成散热柱140后,采用倒装工艺或正装工艺完成第一芯片120和第二芯片130的贴装,第一芯片120和第二芯片130均与基板110表面上的焊盘连接,实现了第一芯片120和第二芯片130与基板110之间的电连接。

83.s3:在基板110上塑封形成至少包覆在第一芯片120和第二芯片130外的第一塑封体150。

84.结合参见图8,具体地,利用塑封工艺,通过塑封料填充第一芯片120、第二芯片130的贴装区域以及散热区域,固化后形成了同时包覆在第一芯片120、第二芯片130和散热柱140外的第一塑封体150。

85.s4:翻转基板110,并在基板110上贴装第三芯片160。

86.结合参见图9,具体地,翻转基板110后,再次在基板110背面利用正装或倒装工艺贴装第三芯片160。

87.s5:在基板110上塑封形成包覆在第三芯片160外的第二塑封体170。

88.结合参见图10,具体地,完成第三芯片160的贴装后,利用塑封工艺,形成第二塑封体170,在形成第二塑封体170时,可以采用选择性塑封工艺,使得第二塑封体170仅仅覆盖第三芯片160,从而避让基板110上用于植球的金属焊盘117。

89.s6:在基板110上形成焊球111。

90.结合参见图11,具体地,在形成第二塑封体170后,利用植球工艺,完成锡球的制备,再通过切割工艺,将产品切割为单颗。

91.综上所述,本实施例提供的半导体封装结构100和半导体封装结构100的制备方法,通过在基板110两侧分别贴装第一芯片120、第二芯片130和第三芯片160,实现了双面封装,同时在第一芯片120和第二芯片130之间设置有散热柱140,散热柱140设置在基板110的金属层113上,能够起到良好的散热效果。并且,通过在散热柱140底部形成第一凹槽143,能够进一步提升第一塑封体150与基板110之间、第一塑封体150与散热柱140之间的结合力,

从而避免了第一塑封体150与基板110之间的分层现象。同时,散热柱140的高度与第一芯片120、第二芯片130的高度不同,能够避免第一塑封体150与芯片的背面之间的分层现象。此外,金属焊盘117上也设置有第二凹槽119,能够在制备焊球111时起到缓冲作用,从而释放焊球111的内部应力,提升焊球111与金属焊盘117之间的结合力。

92.第二实施例

93.参见图12,本实施例提供了一种半导体封装结构100,其基本结构和原理及产生的技术效果和第一实施例相同,为简要描述,本实施例部分未提及之处,可参考第一实施例中相应内容。

94.在本实施例中,第一塑封体150上形成有贯通至基板110的让位开口槽151,让位开口槽151与散热柱140对应,以使散热柱140暴露在第一塑封体150外。具体地,在形成第一塑封体150时,可以采用选择塑封工艺,从而使得第一塑封体150呈间隔设置的两个塑封体,并分别包覆在第一芯片120和第二芯片130外。

95.在本实施例中,让位开口槽151与基板110上的散热区对应,从而使得散热柱140能够直接裸露在外,进一步提升其散热能力。并且,散热柱140上设置有多个散热槽141,从而能够进一步提升散热柱140的散热面积,从而提升散热能力。

96.需要说明的是,本实施例中散热柱140的高度可以小于第一塑封体150的高度,散热柱140的形成工艺与第一实施例相同,与第一实施例相比,在制备工艺上的不同在于第一塑封体150的制备,第一塑封体150采用了选择塑封工艺,同时形成了包覆在第一芯片120外和第二芯片130外的两个塑封体结构。

97.第三实施例

98.参见图13,本实施例提供了一种半导体封装结构100,其基本结构和原理及产生的技术效果和第一实施例相同,为简要描述,本实施例部分未提及之处,可参考第一实施例中相应内容。

99.在本实施例中,第一塑封体150局部包覆在散热柱140外,且散热柱140远离基板110的一端部分伸出第一塑封体150。具体地,散热柱140的高度高于第一塑封体150的高度,从而使得散热柱140的顶端能够局部伸出第一塑封体150,并裸露在外,能够提升其散热能力。

100.在本实施例中,散热柱140的边缘设置有拓展散热板145,拓展散热板145贴合在第一塑封体150远离基板110的一侧表面。其中,拓展散热板145水平贴合至第一塑封体150的表面,且拓展散热板145与散热柱140形成了l型结构,一方面,通过设置拓展散热板145,能提升与第一塑封体150之间的接触面积,从而提升第一塑封体150与l型结构之间的结合力,另一方面,拓展散热板145贴合在第一塑封体150的表面,能够对第一塑封体150起到压合作用,减少基板110的翘曲现象,并且能够防止第一芯片120和第二芯片130背面的分层问题。

101.需要说明的是,本实施例中拓展散热板145与散热柱140均采用金属材料,且拓展散热板145至少分布在散热柱140的顶部的边缘两侧,其缩限在第一芯片120和第二芯片130之间,使得拓展散热板145不会屏蔽第一芯片120和第二芯片130,保证器件的性能。

102.第四实施例

103.参见图14,本实施例提供了一种半导体封装结构100,其基本结构和原理及产生的技术效果和第三实施例相同,为简要描述,本实施例部分未提及之处,可参考第三实施例中

相应内容。

104.在本实施例中,散热柱140的边缘设置有拓展散热板145,拓展散热板145贴合在第一塑封体150远离基板110的一侧表面,且拓展散热板145覆盖在第一塑封体150远离基板110的一侧表面,并延伸至第一塑封体150的边缘。具体地,拓展散热板145整体覆盖在整个第一塑封体150的表面,从而进一步提升与第一塑封体150的接触面积,并更好地起到压合作用。

105.在本实施例中,拓展散热板145与散热柱140一体设置,并采用了金属材料,同时散热柱140与金属层113连接,拓展散热板145完全遮蔽住了第一芯片120和第二芯片130。在此情况下,金属层113与布线层115中的接地线路连接,从而使得金属层113能够接地,进一步使得拓展散热板145起到了分区电磁屏蔽的效果。

106.需要说明的是,本实施例中拓展散热板145可以采用电镀方式实现,通过设置完全覆盖在第一塑封体150表面的拓展散热板145,能够进一步提升与第一塑封体150的接触面积,并更好地起到压合作用,能够直接完整地压合在第一塑封体150的表面,从而起到更好的防翘曲作用。

107.第五实施例

108.参见图15,本实施例提供了一种半导体封装结构100,其基本结构和原理及产生的技术效果和第一实施例或第三实施例相同,为简要描述,本实施例部分未提及之处,可参考第一实施例或第三实施例中相应内容。

109.在本实施例中,第一塑封体150远离基板110的一侧还设置有第四芯片180,第四芯片180贴装在散热柱140上,并与基板110电连接。具体地,第四芯片180与基板110上的散热区对应设置,并贴装在散热柱140上,散热柱140能够起到良好的支撑作用。

110.在本实施例中,第四芯片180为正装芯片,且第四芯片180远离基板110的一侧设置有导电线弧181,导电线弧181与基板110连接,基板110上还设置有包覆在导电线弧181和第四芯片180外的填充胶层183。具体地,第四芯片180正装在散热柱140上,填充胶层183同时覆盖在基板110和第一塑封体150上,从而将第四芯片180和导电线弧181均包覆在内,起到良好的保护作用。

111.在本实施例中,第一芯片120与散热柱140之间也可以采用粘接胶实现固定,具体地,粘接胶填充在第一芯片120和散热柱140之间,从而起到了良好的粘接固定效果。

112.在本实施例中,散热柱140的中间位置可以不用填充塑封料,从而保证了其散热效果。

113.需要说明的是,此处第四芯片180上也可以继续堆叠芯片结构,从而进一步提升器件的堆叠数量。

114.本实施例提供的半导体封装结构100,通过堆叠设置第四芯片180,能够进一步提升封装结构的堆叠数量,从而提升器件的集成度。同时通过设置填充胶层183,能够有效地对打线结构进行保护,提升结构可靠性。

115.第六实施例

116.参见图16,本实施例提供了一种半导体封装结构100,其基本结构和原理及产生的技术效果和第三实施例相同,为简要描述,本实施例部分未提及之处,可参考第三实施例中相应内容。

117.在本实施例中,第一塑封体150远离基板110的一侧还设置有第四芯片180,第四芯片180贴装在散热柱140上,并与基板110电连接。具体地,第四芯片180与基板110上的散热区对应设置,并贴装在散热柱140上,散热柱140能够起到良好的支撑作用,同时,第四芯片180采用倒装结构。

118.在本实施例中,第四芯片180为倒装芯片,散热柱140具有导电性,第四芯片180通过散热柱140与基板110电连接,且基板110上还设置有包覆在第四芯片180外的第三塑封体190。具体地,散热柱140与金属层113连接,金属层113通过底部的导电柱与布线层115连接,从而使得第四芯片180能够通过散热柱140实现与基板110之间的电气连接,同时第三塑封体190能够完全包覆在第一塑封体150的表面,从而起到良好的保护作用。

119.在本实施例中,散热柱140采用铜柱,第四芯片180焊接在散热柱140上。并且散热柱140裸露在第一塑封体150外,且散热柱140伸出第一塑封体150的部分设置有多个第三凹槽191。通过设置第三凹槽191,能够提升第三塑封体190底部的结合力,从而避免第三塑封体190和第一塑封体150之间发生分层现象。

120.本实施例提供的半导体封装结构100,通过堆叠设置第四芯片180,能够进一步提升封装结构的堆叠数量,从而提升器件的集成度。同时通过设置第三凹槽191,能够进一步提升第三塑封体190底部的结合力,从而避免第三塑封体190与第一塑封体150之间发生分层现象。

121.第七实施例

122.参见图17,本实施例提供了一种半导体封装结构100,其基本结构和原理及产生的技术效果和第三实施例相同,为简要描述,本实施例部分未提及之处,可参考第三实施例中相应内容。

123.在本实施例中,第一塑封体150远离基板110的一侧还设置有第四芯片180,第四芯片180贴装在散热柱140上,并与基板110电连接。第四芯片180为倒装芯片,散热柱140具有导电性,第四芯片180通过散热柱140与基板110电连接,且基板110上还设置有包覆在第四芯片180外的填充胶层183或保护盖。

124.在本实施例中,优选采用填充胶层183,通过设置填充胶层183,能够对第四芯片180起到良好的保护作用,且填充胶层183可以仅仅覆盖在第四芯片180周围,从而无需覆盖整个第一塑封体150的表面,且成本低廉。

125.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1