中介基板及其制法的制作方法

1.本发明有关一种半导体封装的载板,尤指一种可提高可靠度的中介基板及其制法。

背景技术:

2.随着产业应用的发展,近年来应用于网通服务器、高速运算、ai人工智能等ic电子元件需要的功能愈来愈多元化,且性能愈来愈高,因而需要对多个异质芯片进行整合封装,并朝向高叠层数、高密度、高i/o数及高脚数的大型封装尺寸发展。

3.目前高阶的半导体元件封装的封装尺寸愈来愈大,例如cowos(chip on wafer on substrate)型式的尺寸大至54

×

54

㎜2,甚至100

×

100

㎜2以上,其远大于传统封装尺寸(小于31

×

31

㎜2),且其间距,如载板的覆晶(flip-chip)用凸块间距(bump pitch)及植球间距(bga pitch)不断微缩,使得覆晶封装使用的封装基板及用于系统组装的电路板(pcb)朝向细线路间距、高叠层数、高密度化的发展。例如,大尺寸封装结构的覆晶用凸块间距的高密度的多接点(i/o)往往随的数万个,甚至更多,当覆晶用凸块间距由150微米(μm)缩减至130μm,甚至100μm时,该载板的配线层的层数将增加,如由传统的8层(或10层)增加至12层、14层、16层或22层。

4.图1为现有大尺寸封装的cowos型式电子封装件1的剖面示意图。如图1所示,该电子封装件1于一覆晶封装基板1a的覆晶(flip-chip)侧上设置一硅中介板(through silicon interposer,简称tsi)1b,且于该硅中介板1b上配置至少一半导体芯片12及/或至少一芯片组12’。该硅中介板1b的一侧具有多个导电凸块13,作为覆晶封装的连接点。该覆晶封装基板1a以其覆晶侧的焊垫101借由多个预焊锡体(pre-solder)102与该硅中介板1b的导电凸块13进行覆晶封装的结合,以形成覆晶接点13’。

5.于后续组装中,将该电子封装件1以其该覆晶封装基板1a底侧(即植球侧)借由多个焊球14接置于一电路板1’上。

6.目前业界的覆晶封装基板1a的结构可分为具有核心层(core)的基板及无核心层(coreless)的基板。该核心层(core)式基板于核心层中采用机械钻孔及电镀铜而形成多个导电通孔,以电性导通上下侧的增层线路,因此造成其导通孔的间距较大,所以其核心层不利于制作出细间距及细线路的布线。另一方面,该无核心层式基板用薄介电层作增层及于层间的电性导通全采用激光(laser)导电盲孔或导电柱方式,易于制作出细间距及细线路的布线,以相较于该核心层式基板而言,具有较佳的细间距能力及高密度封装的应用。然而,该无核心层式基板的结构薄,致使刚性差,因而无法抗翘曲,故该无核心层式基板不适用于大尺寸的电子封装件1。

7.因此,由于该核心层(core)式基板的结构强度较好且刚性较佳,并能抗翘曲,故业界现时均选用该核心层(core)式基板作为该大尺寸电子封装件1的覆晶封装基板1a。早期核心层(core)式基板的制作中,采用玻纤配合环氧树脂所组成的基材,如bt(bismaleimide triazine)或fr5等,供作为核心层10,再于其上进行导电通孔100制程,如机械钻孔、激光钻

孔或双锥状盲孔等成孔步骤,再于孔中电镀导电层或再填入填充材100’,之后再进行双侧增层而完成。

8.然而,现有应用于高集积/大版面尺寸的具有核心层10的覆晶封装基板1a会产生明显缺点,例如:该核心层10采用玻纤配合环氧树脂所组成的基材,因该覆晶封装基板1a于各层间材料的热膨胀系数(coefficient of thermal expansion,简称cte)与硅中介板1b、半导体芯片12、芯片组12’及封装材1c(其用以包覆该硅中介板1b、半导体芯片12及芯片组12’)不一致,故于封装时易产生翘曲,致使其与该硅中介板1b之间连接不良、或于焊接时,其与该电路板1’之间会发生连接不良,更严重的是可能因为应力关系,在可靠度验证中易造成该半导体芯片12及/或芯片组12’与载板间的分层或本身的破裂、或载板层间分层致使该半导体芯片12及/或芯片组12’的电性失效。

9.再者,若将早期的核心层(core)式基板应用于大版面尺寸的覆晶封装基板1a时,其刚性仍然不足,且支撑应力不足,造成平坦性较差,因而当其组装到电路板1’上时,容易因应力而影响产品的品质及可靠度的稳定性。

10.因此,业界现行做法将该核心层10的厚度h加厚,如厚度h从原本0.8毫米(

㎜

),增加厚度h至1.2

㎜

(或1.6

㎜

)以上,以增加该覆晶封装基板1a的刚性强度,俾改善翘曲问题,但却因而产生如下更多缺点:

11.第一、各该导电通孔100的间距无法缩小。具体地,加厚该核心层10的结果,造成在传统技术之下势必让该多个导电通孔100的端面尺寸变大,例如该厚度h为0.8

㎜

,其通孔孔径w及通孔间距(pitch)典型为150微米(μm)及300μm以上,而若该厚度h为1.2

㎜

,则加大该孔径w至200微米以上(即该孔径w变大),进而造成该多个导电通孔100的间距必须变大,故导致单位面积内导电通孔100的数量变少,不利于制作高密度细间距布线,因而应用于更多接点(i/o)的需求时,则必须加大该覆晶封装基板1a的尺寸,致使板翘更不易于控制,且成本大增。

12.第二、该导电通孔100的加工成本与难度随着核心层加厚而更高。具体地,加厚该核心层10的结果,将导致该多个导电通孔100变深,因而增加在变深的导电通孔100内完成电镀的难度、及将填充材100’顺利的填入变深的导电通孔100内的难度,同时使得加工成本增加。

13.另一方面,随着现有大尺寸电子封装件1的高叠层数及高密度化的发展,导致该覆晶封装基板1a及电路板1'的制程也愈趋复杂,且精密度的要求愈高,进而电路板1'加工困难度也愈高,故在大尺寸封装的电路板1'加工制程将面临加工良率低及成本提高等问题,甚至于此种大版面尺寸封装的系统组装结构会产生严重的翘曲(warpage)问题,以致于影响到终端产品的品质可靠度。

14.例如,对于该电路板1'而言,当该封装基板1a的焊球14的间距t由1.0

㎜

缩减至0.8~0.7

㎜

,甚至0.6~0.4

㎜

时,该电路板1'的配线层的层数需大幅增加(如由16层增加至22层,甚至30层以上)以满足多接点的需求,同时该电路板1'的布线的线宽/线距(l/s)也需配合缩减(如由现况pcb硬板的量产的l/s为75/75μm细化至25/25μm),故基于该电路板1'的通用版面尺寸相当大(如边长10英寸到30英寸的长方形版面),若该电路板1'的配线层的层数增至22层(甚至30层以上)时,原本只需要局部在大尺寸电子封装件1的元件区域a设置细线路及高密度布线,即可满足需求,但电路板1'制作上,事实上是将该电路板1'做整版面进行

细线路加工而非只单独做局部区域细线路加工,因而于一方面整板面作细线路加工而另一方面又要增加层数的情况下,将会造成传统电路板1’的加工困难,且良率极低,致使成本大幅增加。

15.另外,如twi308385专利的现有技术,其基板采用薄核心层(如标号230)技术,再加上强化板(如标号240),以达到制作高密度布线及抗线路翘曲变形问题,但其具有明显缺点,如下所述:

16.第一、其因仍具有核心层,而需制作导通孔,致使基板的布线密度仍有限制。

17.第二、其强化板形成于整体结构的单一侧,故存在不对称问题,因而无法应用于大尺寸封装。

18.第三、其强化板虽可通过增厚,以达到抗翘曲的目的,但却也导致导电路径(如标号252)变长,因而增加其(如标号252)加工作业的困难度,且间距不易微小化,更严重者,将出现可靠度的问题,例如,深长的导电通道(如标号250)会造成在外接如芯片的电子元件时,需大量焊锡,而易产生如气泡(void)及接着不良等可靠度问题。

19.第四、其强化板先进行绝缘材涂布,故在高密度多孔(如标号246处)状态下,容易产生涂布不均或不良,因而造成电性连接发生短路的虞虑。

20.因此,如何克服上述现有技术的种种问题,实已成为目前业界亟待克服的难题。

技术实现要素:

21.鉴于上述现有技术的种种缺失,本发明提供一种中介基板及其制法,能有效抗翘曲及达到细间距线路的应用。

22.本发明的中介基板,包括:一无核心层线路结构,其具有相对的第一表面与第二表面,且该第一表面及该第二表面均包含有露出的线路层;一第一绝缘层,其设于该无核心层线路结构的第一表面上;多个第一导电柱,其具有相对的第一端面与第二端面,且嵌埋于该第一绝缘层内,其中以该第一端面结合及电性连接于该无核心层线路结构的第一表面上的该线路层,而该第二端面露出于该第一绝缘层;一第一支撑件,其为设有多个网状开孔的板体,其具有相对的第一侧与第二侧,且嵌埋于该第一绝缘层内,其中以其第一侧面向于该无核心层线路结构的该第一表面,而该第二侧露出于第一绝缘层,且该多个第一导电柱位于该第一支撑件的至少一网状开孔中;一第二绝缘层,其设于该无核心层线路结构的第二表面上;多个第二导电柱,其具有相对的第一端面及第二端面,且嵌埋于该第二绝缘层内,其中以其第一端面结合与电性连接于该无核心层线路结构的第二表面上的该线路层,而该第二端面露出于该第二绝缘层;一第二支撑件,其为设有多个网状开孔的板体,其具有相对的第一侧与第二侧,且嵌埋于该第二绝缘层内,其中并以其第一侧设于该无核心层线路结构的该第二表面上,且该多个第二导电柱位于该第二支撑件的至少一网状开孔中;以及第二绝缘层,其设于该无核心层线路结构的第二表面上,以包覆该多个第二导电柱与该第二支撑件,且令该多个第二导电柱的该第二端面外露于该第二绝缘层。

23.前述的中介基板中,该第一导电柱及/或该第二导电柱包含相堆叠结合的多个层柱体。

24.前述的中介基板中,该第一支撑件的该第一侧与该无核心层线路结构的该第一表面的该线路层间间隔有该第一绝缘层,或该第一支撑件的该第一侧直接结合于该无核心层

线路结构的该第一表面的该线路层。

25.前述的中介基板中,该第二支撑件的该第一侧与该无核心层线路结构的该第一表面的该线路层间间隔有一粘着材,或该第二支撑件的该第一侧直接结合于该无核心层线路结构的该第二表面的该线路层。

26.前述的中介基板中,该第一支撑件的该第二侧露出于该第一绝缘层,及/或该第二支撑件的该第二侧露出于该第二绝缘层。复者,该第一支撑件或该第二支撑件露出的表面上可更进一步设置有散热件。

27.前述的中介基板中,该第一支撑件及/或第二支撑件包含相堆叠且分别设有多个网状开孔的多个层板体。

28.前述的中介基板中,该多个第一导电柱分别位于该第一支撑件的各该网状开孔中,及/或该多个第二导电柱分别位于该第二支撑件的各该网状开孔中。

29.前述的中介基板中,该多个第一导电柱与该第一支撑件的构成为铜材、或铜合金材。

30.前述的中介基板中,该多个第二导电柱与该第二支撑件的构成为铜材、铜合金材、不锈钢材、或铁镍合金材。

31.前述的中介基板中,该第一支撑件及/或该第二支撑件的构成为金属材、有机树脂材、塑钢材或陶瓷绝缘材。

32.前述的中介基板中,该多个第一导电柱的该第二端面之侧作为以覆晶方式结合芯片或中介板的置晶侧,而该多个第二导电柱的该第二端面之侧作为结合电路板的电路板侧。

33.本发明复提供一种中介基板的制法,包括:提供一承载件;于该承载件上以图案化电镀形成多个第一导电柱及形成一包含有多个网状开孔的板体状第一支撑件,以令该多个第一导电柱位于该第一支撑件的至少一该网状开孔中;形成一第一绝缘层于该承载件上,以令该第一绝缘层包覆该多个第一导电柱与该第一支撑件,并对该第一绝缘层进行整平制程,以令该多个第一导电柱的其中一端面露出于该第一绝缘层的表面;以增层法(半加成技术sap)形成一具有多个线路层的无核心层线路结构于该第一绝缘层、该多个第一导电柱及该第一支撑件上,以令该无核心层线路结构的至少一该线路层结合该多个第一导电柱的其中一端面;于该无核心层线路结构上以图案化电镀形成多个第二导电柱及形成一包含有多个网状开孔的板体状第二支撑件,以令该多个第二导电柱位于该第二支撑件的至少一该网状开孔中,且该多个第二导电柱以其中一端面结合于该无核心层线路结构表面的一该线路层;形成一第二绝缘层于该无核心层线路结构上,以令该第二绝缘层包覆该多个第二导电柱与该第二支撑件,并对该第二绝缘层进行整平制程,以令该多个第二导电柱的另一端面露出于该第二绝缘层的表面;以及移除该承载件,以令该多个第一导电柱的另一端面露出于该第一绝缘层。

34.本发明另提供一种中介基板的制法,包括:提供一承载件,该承载件为一板体,且其构成为铜材、铜合金材、不锈钢材或铁镍合金材;于该承载件上以增层法(半加成技术sap)形成一具有多个线路层的无核心层线路结构,且令该无核心层线路结构表面的一该线路层结合于该承载件上;于该无核心层线路结构上以图案化电镀形成多个第一导电柱及形成一包含有多个网状开孔的板体状第一支撑件,以令该多个第一导电柱位于该第一支撑件

的至少一该网状开孔中,且该多个第一导电柱的其中一端面结合于该无核心层线路结构表面的一该线路层;形成一第一绝缘层于该无核心层线路结构上,以包覆该多个第一导电柱及该第一支撑件,且对该第一绝缘层进行整平制程,以令该多个第一导电柱的另一端面露出于该第一绝缘层的表面;以图案化蚀刻制程蚀刻该承载件,以形成多个第二导电柱及一第二支撑件,其中,该第二支撑件形成为包含有多个网状开孔的板体,而该多个第二导电柱位于该第二支撑件的至少一该网状开孔中,且该无核心层线路结构表面的一该线路层结合该多个第二导电柱的其中一端面;以及形成一第二绝缘层于该无核心层线路结构上,以包覆该多个第二导电柱及该第二支撑件,且对该第二绝缘层进行整平制程,以令该多个第二导电柱的另一端面露出于该第一绝缘层的表面。

35.前述的制法中,该第一支撑件的其中一侧外露于该第一绝缘层,及/或该第二支撑件的其中一侧露出于该第二绝缘层。复者,该第一支撑件或该第二支撑件露出的表面上形成有散热件。

36.前述的制法中,以图案化电镀同时形成该多个第一导电柱及该第一支撑件于该承载件或该无核心层线路结构的该线路层上,且该第一导电柱形成为单层柱体或相堆叠结合的多个层柱体,及/或该第一支撑件形成为单层板体或相堆叠结合的多个层板体。

37.前述的制法中,先以图案化电镀形成该多个第一导电柱于该承载件或该无核心层线路结构的该线路层上,再以绝缘粘着材贴合方式将该第一支撑件结合于该承载件或该无核心层线路结构的该线路层上;或者,先以绝缘粘着材贴合方式将该第一支撑件结合于该承载件或该无核心层线路结构的该线路层上,再以图案化电镀形成该多个第一导电柱于该承载件或该无核心层线路结构的该线路层上;以及,该第一导电柱形成为单层柱体或相堆叠结合的多个层柱体,及/或该第一支撑件形成为具有多个网状开孔的单层板体或相堆叠结合的多个层板体。

38.前述的制法中,若该第一导电柱及第二导电柱直接电镀形成者,将可得到比传统(如twi308385专利)的激光导盲孔更佳的可靠度。

39.前述的制法中的第一实施例,以图案化电镀同时形成该多个第二导电柱及该第二支撑件于该无核心层线路结构的该线路层上,且该第二导电柱形成为单层柱体或相堆叠结合的多个层柱体,及/或该第二支撑件形成为单层板体或相堆叠结合的多个层板体。

40.前述的制法中的第一实施例,先以图案化电镀形成该多个第二导电柱于该无核心层线路结构的该线路层上,再以粘着材贴合方式将该第二支撑件结合于该无核心层线路结构的该线路层上;或者,先以粘着材贴合方式将该第二支撑件结合于该无核心层线路结构的该线路层上,再以图案化电镀形成该多个第二导电柱于该无核心层线路结构的该线路层上;以及,该第二导电柱形成为单层柱体或相堆叠结合的多个层柱体,及/或该第二支撑件形成为单层板体或相堆叠结合的多个层板体。

41.前述的制法中,该多个第一导电柱分别位于该第一支撑件的各该网状开孔中,及/或该多个第二导电柱分别位于该第二支撑件的各该网状开孔中。

42.由上可知,本发明的中介基板及其制法中,主要借由该无核心层(coreless)线路结构轻易制作出层间导电的细间距(如60~100微米,远优于现有具有核心层的通孔间距的300微米)及细线路的布线,以符合大尺寸封装的高i/o数及高布线密度的需求。

43.再者,本发明亦即如同将现有技术有核心层基板的核心层分拆为支撑件设置于无

核心层线路结构的一侧或两侧,以形成较佳的三明治的结构,以借由该第一支撑件及第二支撑件与第一绝缘层及第二绝缘层的配置,且利用支撑件具有良好的刚性的特性及适当增厚,使该中介基板的刚性符合需求,因而能有效抗翘曲,故当该中介基板进行芯片元件的封装作业时,能提高品质、可靠度及良率,克服现有技术的困难。

44.此外,借由使用无核心层线路结构,因而无需进行导电通孔制程,故相较于现有技术,本发明不会产生如核心层先前技术所述的缺失。

45.另外,借由该无核心层线路结构,可以将电路板需细线路布线设计的区域集中收纳设计于该无核心层线路结构中,并增宽各该第二导电柱的间距,电路板无需做细线路高密度加工,故相较于现有技术,本发明可改善现有电路板的难题。

附图说明

46.图1为现有大尺寸封装的cowos型式电子封装件的剖视示意图。

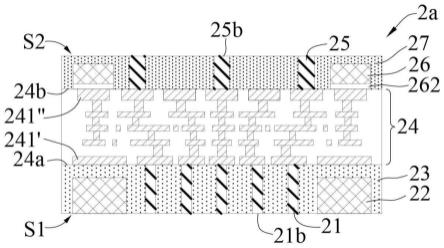

47.图2a至图2f为本发明的中介基板的第一实施例的制法的剖视示意图。

48.图2a-1为对应图2a的局部立体示意图。

49.图2a-2为对应图2a的另一实施例。

50.图2b-1为对应图2b的另一实施例。

51.图2c-1为对应图2c的另一实施例。

52.图2d-1为对应图2d的另一实施例。

53.图2e-1、图2e-2及图2e-3为对应图2e的不同实施例的剖视示意图。

54.图2f-1、图2f-2及图2f-3为对应图2f的其它实施例的剖视示意图。

55.图2f-4为对应图2f-3的局部立体示意图。

56.图2g、2g-1及图2g-2为本发明的中介基板的应用的不同实施例的剖视示意图。

57.图3a至图3e为本发明的中介基板的第二实施例的制法的剖视示意图。

58.图3b-1为对应图3b的另一实施例。

59.图3c-1为对应图3c的另一实施例。

60.图3d-1及图3d-2为对应图3d的不同实施例。

61.图3e-1、图3e-2及图3e-3为对应图3e的其它实施例的剖视示意图。

62.图4a至图4d为本发明的中介基板的第三实施例的制法的剖视示意图。

63.图4b-1为对应图4b的另一实施例。

64.图4d-1为对应图d的另一实施例。

65.图5a至图5d为本发明的中介基板的第四实施例的制法的剖视示意图。

66.图5a-1为对应图5a的局部立体示意图。

67.图5d-1、图5d-2及图5d-3为对应图5d的其它实施例的剖视示意图。

68.图6为本发明的中介基板的第五实施例的剖视示意图。

69.其中,附图标记说明如下:

70.1,9,9’,9”:电子封装件

[0071]1’

,9a:电路板

[0072]

1a:覆晶封装基板

[0073]

1b,91:硅中介板

[0074]

1c:封装材

[0075]

10:核心层

[0076]

10a,10b:线路层

[0077]

100:导电通孔

[0078]

100’:填充材

[0079]

101:焊垫

[0080]

102:预焊锡体

[0081]

12,92:半导体芯片

[0082]

12’:芯片组

[0083]

121:焊锡凸块

[0084]

13,93:导电凸块

[0085]

13’:覆晶接点

[0086]

14,94:焊球

[0087]

2,2a,2b,2c,3,3a,3b,3c,4,4a,5,5a,5b,5c,6:中介基板

[0088]

20,40:承载件

[0089]

21,31,61:第一导电柱

[0090]

21a,31a,61a:第一端面

[0091]

21b,31b,61b:第二端面

[0092]

22,32,32’,52,52’,52”:第一支撑件

[0093]

22a,32a,52a:第一侧

[0094]

22b,32b,52b:第二侧

[0095]

220,520,520’,520”:开口

[0096]

221:网孔

[0097]

222:结合层

[0098]

23,33:第一绝缘层

[0099]

24:无核心层线路结构

[0100]

24a:第一表面

[0101]

24b:第二表面

[0102]

240:介电层

[0103]

241,241’,241”:线路层

[0104]

242:导电盲孔

[0105]

25,25’,25”,35,35’,45,65:第二导电柱

[0106]

25a,35a,45a,65a:第一端面

[0107]

25b,35b,45b.65b:第二端面

[0108]

26,36,46,56,56’,56”:第二支撑件

[0109]

26a,36a,46a,56a:第一侧

[0110]

26b,36b,46b,56b:第二侧

[0111]

260,560,560’,560”:开口

[0112]

261:网孔

[0113]

262:结合层

[0114]

27,37:第二绝缘层

[0115]

28:散热件

[0116]

280:粘着材

[0117]

281:窗口

[0118]

311,611:第一柱体

[0119]

312,612:第二柱体

[0120]

321:第一板体

[0121]

322:第二板体

[0122]

331:第一绝缘分层

[0123]

332:第二绝缘分层

[0124]

351,651:第三柱体

[0125]

352,652:第四柱体

[0126]

361:第三板体

[0127]

362:第四板体

[0128]

371:第三绝缘分层

[0129]

372:第四绝缘分层

[0130]

610,650:垫体

[0131]

911:线路重布层

[0132]

95:接点

[0133]

a,b:区域

[0134]

c:接点区

[0135]

d1,d2,h:厚度

[0136]

h1:高度

[0137]

l:切割路径

[0138]

s1:置晶侧

[0139]

s2:电路板结合侧

[0140]

t,t1,t2:间距

[0141]

w:孔径。

具体实施方式

[0142]

以下借由特定的具体实施例说明本发明的实施方式,熟悉此技艺的人士可由本说明书所揭示的内容轻易地了解本发明的其他优点及功效。

[0143]

须知,本说明书所附图式所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技艺的人士的了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如「上」、「第一」、「第二」、「第三」、「第四」、「一」等的用语,亦仅为便于叙述明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,

在无实质变更技术内容下,当亦视为本发明可实施的范畴。

[0144]

图2a至图2g为本发明的覆晶封装用中介基板2的第一实施例的制法的剖视示意图。

[0145]

如图2a所示,于一承载件20上形成多个第一导电柱21及至少一作为刚性层的第一支撑件(stiffener)22。

[0146]

于本实施例中,该第一导电柱21形成为单层柱体,如铜、铜合金等的金属柱,且该第一支撑件22为一包含有多个网状开孔(其定义有尺寸较大的开口220和尺寸较小的网孔221)的单层板体状(如图2a-1所示)的导电基材、半导体基材或绝缘基材,以令该多个第一导电柱21位于该第一支撑件22的至少一该网状开孔(如开口220)中,可供结合硅中介板、半导体芯片、或被动元件等。例如,该第一导电柱21以微影图案化后电镀、沉积或其它方式自该承载件20表面长出,且该第一支撑件22为刚性陶瓷、有机树脂或其它适当材质等的绝缘基材,其借由如胶材的结合层222以粘贴方式或热压合(或真空压合)方式固定于该承载件20上。具体地,该第一支撑件22的导电基材可为不锈钢或含铁、镍、铜、铝、镁、锌等材质或其合金的金属导体,而以该有机树脂形成该第一支撑件22时,其材质可采用含玻纤及有机树脂的基材,如bt(bismaleimide triazine)、fr4或fr5等,抑或采用高刚性无玻纤但含有填充材(filler)(如sio2)的有机基材;或者,形成该有机树脂的材质可为含高比例充填物的环氧树脂(epoxy)材料,如环氧模压树脂(epoxy molding compound,简称emc);甚至于,形成该有机树脂的材质可为塑钢等高强度塑胶类。

[0147]

再者,该第一导电柱21具有相对的第一端面21a与第二端面21b,且该第一支撑件22具有相对的第一侧22a与第二侧22b,以令该第一导电柱21以其第二端面21b结合于该承载件20上,且该第一支撑件22以其第二侧22b结合于该承载件20上。例如,可先以图案化电镀形成该多个第一导电柱21于该承载件20上,再以粘着材贴合方式将具有多个网状开孔(例如开口220、网孔221)的该第一支撑件22结合于该承载件20上。或者,亦可先以绝缘粘着材贴合方式将具有多个网状开孔(例如开口220、网孔221)的该第一支撑件22结合于该承载件20上,再以图案化电镀形成该多个第一导电柱21于该承载件20上。应可理解地,多个该第一导电柱21位于至少一该网状开孔(如该开口220、网孔221)中。

[0148]

或者,如图2a-2所示,亦可以图案化电镀同步形成该多个第一导电柱21及第一支撑件22于该承载件20上;其中,该多个第一导电柱21形成为单层柱体,而该第一支撑件22形成为具有多个网状开孔(例如开口220、网孔221)的板体,应可理解地,多个该第一导电柱21位于至少一该网状开孔(如该开口220、网孔221)中。

[0149]

此外,于制作该第一支撑件22的预先制程中,若选用金属板材,如不锈钢、铜合金、铝合金、铁镍合金等,则其网状开孔的制程先铺上光阻,再曝光显影,接着以化学蚀刻方式形成规则或不规则、相同或不同开孔尺寸的网状板体。另一方面,若选用有机树脂板、塑钢板或陶瓷绝缘板,其呈网状,则其网状开孔的较佳制程以激光、机械钻孔、机械成形(nc router)、等离子蚀刻或化学蚀刻方式形成网状规则或不规则、相同或不同开孔尺寸的板体。

[0150]

另外,该第一支撑件22的厚度d1(该结合层222极薄而可忽略)可依需求设计,且该第一导电柱21的高度h1略高于或等于该第一支撑件22的厚度d1。

[0151]

如图2b所示,形成一第一绝缘层23于该承载件20上,以令该第一绝缘层23包覆该

多个第一导电柱21及该第一支撑件22,并充填于第一支撑件22的开口220和网孔221中,使该多个第一导电柱21及第一支撑件22埋设于该第一绝缘层23中,再对该第一绝缘层23进行整平制程,以令该第一导电柱21的第一端面21a外露于该第一绝缘层23的表面。因此,借由该第一绝缘层23充填于该第一支撑件22的开口220和网孔221中,更可增加该第一绝缘层23与第一导电柱21及第一支撑件22之间的结合力。

[0152]

于本实施例中,形成该第一绝缘层23的材料为有机感光性介电材或有机非感光性介电材(如环氧树脂,即epoxy)。例如,该有机的介电材的种类可包含防焊材(solder mask)、abf(ajinomoto build-up film)、预浸材(prepreg)、铸模化合物(molding compound)、富含充填物(filler)的环氧模压树脂(epoxy molding compound,简称emc)、底层涂料(primer)等。

[0153]

再者,该整平制程包含有研磨、化学蚀刻、激光烧蚀、喷砂或等离子蚀刻方式,以移除该第一导电柱21的部分材质与该第一绝缘层23的部分材质,以令该第一绝缘层23的表面齐平于该第一导电柱21的第一端面21a,使该第一导电柱21的第一端面21a外露于该第一绝缘层23的顶表面。

[0154]

此外,该第一支撑件22嵌入该第一绝缘层23内。应可理解地,该第一支撑件22可依需求外露或未外露于该第一绝缘层23的顶表面,例如,该第一支撑件22的第一侧22a的表面与该第一绝缘层23的表面齐平,以令该第一支撑件22的第一侧22a的表面外露于该第一绝缘层23的表面(如图2b-1所示)。

[0155]

如图2c所示,以增层法(半加成技术,即semi-additive process,简称sap)形成一具有至少一线路层241,241’,241”的无核心层(coreless)线路结构24于该第一绝缘层23、该多个第一导电柱21及该第一支撑件22上,以令该无核心层线路结构24的其中一线路层241’结合于该第一导电柱21的第一端面21a上,且可依需求,使该无核心层线路结构24的其中一线路层241’也结合于该第一支撑件22的第一侧22a上(如图2c-1所示)。

[0156]

于本实施例中,该无核心层线路结构24具有多个介电层240、多个设于该介电层240上的线路层241,241’,241”及多个设于该介电层240中并电性连接各该线路层241,241’,241”的导电盲孔(或导电柱)242,且该线路层241’电性连接该第一导电柱21。例如,该线路层241,241’,241”采用半加成法(semi additive process)技术加工,如采用现有微影图案化与电镀方式等制程,且该介电层240的介电材为如abf、感光型介电材、聚对二唑苯(polybenzoxazole,简称pbo)、聚酰亚胺(polyimide,简称pi)、bt、fr5的预浸材(prepreg,简称pp)、模压树脂(molding compound)、膜状emc或其它等。

[0157]

再者,该第一绝缘层23的材质与该介电层240的材质可相同或不相同,例如,可依cte匹配性的需求调整该第一绝缘层23的材质与该介电层240的材质,以符合低cte的需求。

[0158]

此外,该无核心层线路结构24具有相对的第一表面24a与第二表面24b,且该第一表面24a及该第二表面24b均包含有露出的线路层241’,241”,以令该无核心层线路结构24的第一表面24a所露出的线路层241’结合该第一导电柱21的第一端面21a,且可依需求,使该无核心层线路结构24的第一表面24a所露出的线路层241’结合该第一支撑件22的该第一侧22a(如图2c-1所示)。

[0159]

如图2d所示,于该无核心层线路结构24的第二表面24b上以图案化电镀形成多个第二导电柱25及形成一包含有多个网状开孔(其定义有尺寸较大的开口260和尺寸较小的

网孔261)的板体状第二支撑件26(如图2a-1所示的结构),以令该多个第二导电柱25位于该第二支撑件26的至少一该网状开孔(如该些开口260、网孔261)中,且该第二导电柱25电性连接该无核心层线路结构24,并可依需求,使该无核心层线路结构24电性连接该第二支撑件26。

[0160]

于本实施例中,该第二导电柱25具有相对的第一端面25a及第二端面25b,以令该多个第二导电柱25以其第一端面25a结合与电性连接于该无核心层线路结构24的第二表面24b上的该线路层241”,且该第二支撑件26具有相对的第一侧26a与第二侧26b,以令该第二支撑件26以其第一侧26a设于该无核心层线路结构24的该第二表面24b上。

[0161]

于本实施例中,该第二支撑件26可借由如胶材的结合层262以粘贴方式或热压合(或真空压合)方式固定于该无核心层线路结构24上。例如,可先以图案化电镀形成该多个第二导电柱25于该无核心层线路结构24的第二表面24b所露出的该线路层241”上(该第二导电柱25的高度可视需求进行调整),再以绝缘粘着材贴合方式将具有多个网状开孔(例如开口260、网孔261)的该第二支撑件26结合于该无核心层线路结构24的第二表面24b上。或者,亦可先以绝缘粘着材贴合方式将具有多个网状开孔(例如开口260、网孔261)的该第二支撑件26结合于该无核心层线路结构24的第二表面24b所露出的该线路层241”上,再以图案化电镀形成该多个第二导电柱25于该无核心层线路结构24的第二表面24b所露出的该线路层241”上。应可理解地,多个该第二导电柱25位于至少一该网状开孔(如该开口260、网孔261)中。

[0162]

于本实施例中,该第二导电柱25为铜材、或铜合金材,而该第二支撑件26为呈具有开口260与网孔261的板体状的导电基材、半导体基材或绝缘基材。例如,该第二支撑件26的导电基材可为铜材、铜合金材、不锈钢材或含铁、镍、铜、铝、镁、锌等材质或其合金的金属导体,而当以该有机树脂形成该第二支撑件26时,其材质可采用含玻纤及有机树脂的基材,如bt(bismaleimide triazine)、fr4或fr5等,抑或采用高刚性无玻纤但含有填充材(filler)(如sio2)的有机基材;或者,该第二支撑件26为刚性陶瓷、有机树脂或其它适当材质等的绝缘基材,且形成该有机树脂的材质可为含高比例充填物的环氧树脂(epoxy)材料,如环氧模压树脂(epoxy molding compound,简称emc);甚至于,形成该有机树脂的材质可为塑钢等高强度塑胶类。再者,制作该第二支撑件26的预先制程,亦可如同该第一支撑件22的预先制程一般。

[0163]

或者,如图2d-1所示,亦可以图案化电镀同步形成该多个第二导电柱25及该第二支撑件26于该无核心层线路结构24的第二表面24b所露出的该线路层241”上;其中,该第二导电柱25形成为单层柱体,而该第二支撑件26形成为具有多个网状开孔(如开口260、网孔261)的单层板体。应可理解地,多个该第二导电柱25位于至少一该网状开孔(如该开口260)中,且该第二导电柱25及该第二支撑件26可同为铜材、或铜合金材。

[0164]

再者,于本实施例中,当该些第二导电柱25作为该中介基板2用以结合电路板的电路板侧s2(如图2f所示),则该些第一导电柱21作为中介基板2用以结合芯片的置晶侧s1(如图2f所示),故各该第一导电柱21的间距t1远小于各该第二导电柱25的间距t2。应可理解地,该中介基板2可先制作该置晶侧,再制作该电路板侧;或者,该中介基板2亦可反向先制作该电路板侧,再制作该置晶侧。

[0165]

如图2e所示,形成一第二绝缘层27于该无核心层线路结构24上,以令该第二绝缘

层27包覆该多个第二导电柱25及该第二支撑件26,使该多个第二导电柱25及该第二支撑件26埋设于该第二绝缘层27中,并对该第二绝缘层27进行整平制程,以令该多个第二导电柱25的第二端面25b外露于该第二绝缘层27的表面。

[0166]

于本实施例中,形成该第二绝缘层27的材料可如同该第一绝缘层23。应可理解地,该第二绝缘层27的材质与该介电层240的材质亦可相同或不相同,例如,可依cte匹配性的需求调整该第二绝缘层27的材质与该介电层240的材质,以符合低cte的需求。

[0167]

再者,该整平制程包含有研磨方式、化学蚀刻、激光烧蚀(ablation)、喷砂、等离子蚀刻或其它方式移除该第二导电柱25的部分材质与该第二绝缘层27的部分材质,以令该第二绝缘层27的表面齐平于该第二导电柱25的第二端面25b,而该第二支撑件26的第二侧26b未外露于该第二绝缘层27的顶表面;或者,亦可再以蚀刻方式或激光烧蚀(ablation)移除该第二绝缘层27的部分材质,使该第二绝缘层27的表面略低于该第二导电柱25’的第二端面25b(如图2e-1所示)(亦可再针对该第二导电柱25进行蚀刻加工,使该第二导电柱25”的第二端面25b略低于该第二绝缘层27的表面,如图2e-2所示),使该第二导电柱25,25’,25”的第二端面25b外露(齐平、或凸出、或凹入)于该第二绝缘层27的顶表面。复者,该第二支撑件26的第二侧26b的表面亦可与该第二绝缘层27的表面齐平,以令该第二支撑件26的第二侧26b的表面外露于该第二绝缘层27的表面(如图2e-3所示)。

[0168]

此外,该第二支撑件26的厚度d2(该结合层262极薄而可忽略)可依需求设计,较佳为0.05

㎜

~1.5

㎜

。

[0169]

如图2f所示,移除该承载件20,以令该多个第一导电柱21的第二端面21b外露于该第一绝缘层23的表面,最后再沿着如图2e所示的切割路径l进行切单制程,以获取该中介基板2。

[0170]

于本实施例中,于移除该承载件20后,可进一步移除该第一支撑件22上的结合层222,使该第一支撑件22的第二侧22b外露于该第一绝缘层23,如图2f-1所示的中介基板2a。例如,可借由研磨、化学蚀刻、激光烧蚀(ablation)、喷砂、等离子蚀刻或其它方式移除该结合层222。

[0171]

再者,接续图2e-1所示的制程以得到如图2f-2所示的中介基板2b,且于移除该承载件20后,可再于该置晶侧s1,即该第一绝缘层23及该第一支撑件22的第二侧22b外露的表面侧,借由粘着材280贴置一散热件28(如图2f-3及图2f-4所示的框体,其具有一用以外露该多个第一导电柱21的窗口281),以提升散热性。

[0172]

因此,本发明的制法借由该无核心层线路结构24能轻易制作出层间导电柱的细间距(如15~100微米,远优于现有具有核心层的通孔间距的300微米)及细线路的布线,以符合大尺寸封装的高i/o数及高布线密度的需求。

[0173]

再者,本发明的制法借由该刚性层(如该第一支撑件22及该第二支撑件26)与绝缘层(如该第一绝缘层23及该第二绝缘层27)的配置,以增加该中介基板2,2a,2b,2c的厚度及刚性,进而强化该无核心层线路结构24,使该中介基板2,2a,2b,2c形成强固的三明治刚性结构而使其刚性符合需求,因而能有效抗翘曲,故相较于现有技术,该中介基板2,2a,2b,2c适用于大尺寸封装产品的制程。

[0174]

此外,相较于现有封装基板以线路层作为外部热传导路径,本发明借由该第一支撑件22与该第二支撑件26作为较大面积的外部热传导路径,能提升散热性,且作为电性连

接时,可连接至接地,以提升电气特性。

[0175]

另外,如图2g所示的电子封装件9,以图2f-1所示的中介基板2a为例进行封装作业,其中,该无核心层线路结构24定义有相对的第一表面24a与第二表面24b,以令该第一表面24a对应结合该第一绝缘层23,且该第二表面24b对应结合该第二绝缘层27,使该第一绝缘层23侧(即该多个第一导电柱21的第二端面21b侧)作为置晶侧s1,而该第二绝缘层27侧(即该多个第二导电柱25的第二端面25b侧)作为电路板结合侧s2,故该置晶侧s1的多个第一导电柱21借由含有焊锡材料的多个导电凸块93以覆晶封装方式结合至少一半导体芯片92,而该电路板结合侧s2的该多个第二导电柱25借由多个焊球94以结合及电性连接于一电路板9a的多个接点95上。

[0176]

于另一电子封装件9’的实施例中(如图2g-1所示),该中介基板2a的置晶侧s1借由含有焊锡材料的多个导电凸块93以覆晶封装方式结合一配置有半导体芯片92的硅中介板91,且该硅中介板91具有用以覆晶结合该半导体芯片92的线路重布层911,以形成如cowos型式的大尺寸电子封装件9’。

[0177]

再者,如图2g-2所示又一电子封装件9”的实施例中,利用夹模(socket)方式,将一如图2f-2所示的中介基板2b以其凸出于该第二绝缘层27表面的该多个第二导电柱25’直接电性对接于该电路板9a的多个接点95上,且该夹模(socket)方式因无焊接方式的回焊(reflow)高温制程的冲击,而属于较佳方案。

[0178]

需注意,借由加工程序的互换及导电柱间隙的调整,该第一绝缘层23侧可作为电路板侧,而该第二绝缘层27侧则可作为置晶侧。

[0179]

因此,由于该无核心层线路结构24采用coreless技术,可做出超细线路及高密度的布线,因而可轻易将大尺寸封装件所需的超细线路、高密度布线设置于该无核心层线路结构24内,以配合该半导体芯片92或该硅中介板91的导电凸块93的细间距及细线路的规格,故该无核心层线路结构24于最外侧的线路层241’能以该些第一导电柱21作为外接点,即可符合该半导体芯片92的数万个接点(i/o)的需求,且该中介基板2,2a,2b,2c的刚性亦符合需求,因而能有效抗翘曲,以避免该半导体芯片92本身的破裂、或避免在可靠度测试时载板(如该中介基板2,2a,2b,2c)层间分层而使半导体芯片92的电性失效等问题。

[0180]

此外,由于该无核心层线路结构24采用coreless技术而可轻易做出超细线路及高密度的布线,以将大尺寸封装件对应电路板9a所需形成的高密度、细间距的布线设置于该无核心层线路结构24内,通过适当设计,以令该无核心层线路结构24于最外侧的线路层241”上或该电路板侧s2的该多个第二导电柱25,其间距t2增宽到可配合该传统电路板9a的多个接点95的间距及线宽,故相较于现有技术大尺寸封装件的组装需要在该电路板9a形成细间距、高密度、高层数的配置方能满足需求而言,本发明可使该电路板9a维持传统设计以大幅节省成本及有效提高良率。

[0181]

另外,借由该无核心层线路结构24的良好的细线路与细间距的布线设计能力能轻易适当调整(如增宽)该电路板结合侧s2的各该第二导电柱25的间距t2,以配合该传统电路板9a的多个接点95的最适量产的间距及线宽,使该电路板9a不需针对局部区域进行超细线路规格的加工制作,因而该电路板9a的制作可维持传统结构及加工,故相较于现有技术,该电路板9a无需配合该大尺寸电子封装件9,9’,9”的型式进行细线路、细间距及增加叠层的加工,因而可有效简化加工程序及困难度,且大幅降低成本。

[0182]

图3a至图3e为本发明的中介基板3的第二实施例的制法的剖视示意图。本实施例与第一实施例的差异在于导电柱与支撑件的制作,其它制程大致相同,故以下不再赘述相同处。

[0183]

如图3a所示,于一承载件20上形成多个第一柱体311及至少一具有多个网状开孔的第一板体321,再形成第一绝缘分层331于该承载件20上,以令该第一绝缘分层331包覆该多个第一柱体311及该第一板体321。接着,进行整平制程,使该第一绝缘分层331齐平该多个第一柱体311及该第一板体321,以外露出该多个第一柱体311及该第一板体321。

[0184]

如图3b所示,于该第一绝缘分层331上分次形成多个对接该第一柱体311的第二柱体312及至少一对接该第一板体321且具有多个网状开孔的第二板体322,再形成第二绝缘分层332于该第一绝缘分层331上,以令该第二绝缘分层332包覆该多个第二柱体312及该第二板体322,且该第一与第二绝缘分层331,332形成第一绝缘层33。接者,进行整平制程,使该第二绝缘分层332齐平该多个第二柱体312,以外露出该多个第二柱体312,使该第一柱体311与该第二柱体312相堆叠形成第一导电柱31,且该第一板体321与该第二板体322相堆叠形成第一支撑件32。

[0185]

于本实施例中,该第一柱体311与该第二柱体312的制作方式如同第一实施例的第一导电柱21的制作方式,且该第一板体321与第二板体322的制作方式如同第一实施例的第一支撑件22的制作方式,而该第一绝缘分层331与第二绝缘分层332的制作方式如同第一实施例的第一绝缘层23的制作方式。

[0186]

再者,基于第一实施例的定义,该第一导电柱31具有相对的第一端面31a与第二端面31b,且该第一支撑件32具有相对的第一侧32a与第二侧32b。

[0187]

或者,请详图3b-1所示,于另一实施例中,该第一柱体311与该第一板体321可由图案化电镀同步形成,而该第二柱体312与该第二板体322亦可由图案化电镀同步形成。

[0188]

如图3c所示,形成一无核心层线路结构24于该第一绝缘层33上,以令该无核心层线路结构24的其中一线路层241’结合该第一导电柱31(其中,该无核心层线路结构24的其中一线路层241’亦可同时结合该第一支撑件32,如图3c-1所示),再于该无核心层线路结构24上形成多个第三柱体351及一具有多个网状开孔的第三板体361,且形成第三绝缘分层371于该无核心层线路结构24上,以令该第三绝缘分层371包覆该多个第三柱体351及该第三板体361。接着,进行整平制程,使该第三绝缘分层371齐平该多个第三柱体351及该第三板体361,以外露出该多个第三柱体351及该第三板体361。

[0189]

如图3d所示,于该第三绝缘分层371上分次形成多个对接该第三柱体351的第四柱体352及一对接该第三板体361且具有多个网状开孔的第四板体362,再形成第四绝缘分层372于该第三绝缘分层371上,以令该第四绝缘分层372包覆该多个第四柱体352及该第四板体362,且该第三绝缘分层371与该第四绝缘分层372形成第二绝缘层37。接着,进行整平制程,使该第四绝缘分层372齐平该多个第四柱体352,以外露出该多个第四柱体352,使该第三柱体351与第四柱体352相堆叠形成第二导电柱35,且该第三板体361与第四板体362相堆叠形成第二支撑件36。

[0190]

于本实施例中,该第三柱体351与该第四柱体352的制作方式如同第一实施例的第二导电柱25的制作方式,且该第三板体361与该第四板体362的制作方式如同第一实施例的第二支撑件26的制作方式,而该第三绝缘分层371与第四绝缘分层372的制作方式如同第一

实施例的第二绝缘层27的制作方式。

[0191]

再者,相堆叠对接的柱体的宽度可相同(如该第一柱体311与第二柱体312)或不相同(如该第三柱体351与第四柱体352)。应可理解地,该第一柱体311的宽度亦可大于或小于该第二柱体312的宽度;或者,当该导电柱具有三段柱体时,该第一柱体311的宽度亦可大于、等于或小于该第二柱体312的宽度。

[0192]

再者,基于第一实施例的定义,该第二导电柱35具有相对的第一端面35a与第二端面35b,且该第二支撑件36具有相对的第一侧36a与第二侧36b。

[0193]

或者,亦可再以蚀刻方式或激光烧蚀(ablation)移除该第二绝缘层37的部分材质,使该第二导电柱35’的第二端面35b凸出于该第二绝缘层37的表面(如图3d-1所示)。

[0194]

此外,请详图3d-2所示,于另一实施例中,该第三柱体351与该第三板体361可由图案化电镀同步形成,而该第四柱体352与该第四板体362可由图案化电镀同步形成。

[0195]

如图3e所示,移除该承载件20,且沿如图3d所示的切割路径l进行切单制程,以获取该中介基板3。

[0196]

于本实施例中,于移除该承载件20后,可进一步移除该第一板体321上的结合层222,如图3e-1所示的中介基板3a。

[0197]

再者,如图3e-2所示的中介基板3b,该第二导电柱35’的第二端面35b可凸出该第二绝缘层37的表面,使该第二导电柱35’的第二端面35b外露于该第二绝缘层37的表面。或者,如图3e-3所示的中介基板3c,于移除该承载件20后,可于该第一绝缘层33的表面上设置一如图2f-4所示的散热件28。

[0198]

图4a至图4d为本发明的中介基板4的第三实施例的制法的剖视示意图。本实施例与第一实施例的差异在于第二导电柱45、第二支撑件46的制作,其它制程大致相同,故以下不再赘述相同处。

[0199]

如图4a所示,于第三实施例的制程中,先提供一承载件40,其为单层状的金属板(另一实施例可为多个层状的金属板),如不锈钢板、高刚性合金板(如铁镍合金板等)、厚铜板或铜合金板的金属导体,再以相同于前述第一实施例所述的制法于该承载件40上形成该无核心层线路结构24,其中,该无核心层线路结构24的其中一线路层241’直接与承载件40相结合。

[0200]

如图4b所示,于该无核心层线路结构24上形成多个第一导电柱21及一具有多个网状开孔的第一支撑件22、以及第一绝缘层23等。

[0201]

于本实施例中,该多个第一导电柱21以图案化电镀形成于该无核心层线路结构24的其中一线路层241’上,而该第一支撑件22以贴合方式结合于该无核心层线路结构24;或者,该多个第一导电柱21与该第一支撑件22亦可以图案化电镀同步形成,且均与该无核心层线路结构24的其中一线路层241’直接结合(如图4b-1所示)。

[0202]

基于第一实施例的定义,该第一导电柱21具有相对的第一端面21a与第二端面21b,且该第一支撑件22具有相对的第一侧22a与第二侧22b。

[0203]

如图4c所示,以图案化蚀刻制程蚀刻该承载件40,以形成多个第二导电柱45及一具有多个网状开孔的第二支撑件46;而后,再形成第二绝缘层47于该无核心层线路结构24上,以令该第二绝缘层47包覆该多个第二导电柱45及第二支撑件46;最后,进行整平制程,使该第二绝缘层47齐平该多个第二导电柱45及该第二支撑件46,以外露出该多个第二导电

柱45的一端面及该第二支撑件46的一侧。

[0204]

于本实施例中,基于第一实施例的定义,该第二导电柱45具有相对的第一端面45a与第二端面45b,且该第二支撑件46具有相对的第一侧46a与第二侧46b。

[0205]

如图4d所示,沿如图4c所示的切割路径l进行切单制程,以获取该中介基板4;其中,该第一导电柱21侧(即第一绝缘层23侧)作为以覆晶方式结合芯片或硅中介板的置晶侧s1,而以蚀刻形成的该第二导电柱45侧(即第二绝缘层47侧)作为结合电路板的电路板结合侧s2。

[0206]

再者,若以第一实施例的制程为例,如图4d-1所示的中介基板4a,于该第一绝缘层23的表面(置晶侧s1)上设置一如图2f-4所示的散热件28,以提升散热性。

[0207]

图5a至图5d为本发明的中介基板5的第四实施例的制法的剖视示意图。本实施例与上述各实施例的差异在于支撑件的网板形式,其它制程大致相同,故以下不再赘述相同处。

[0208]

如图5a所示,以第一实施例为例,于一承载件20上以图案化电镀形成多个第一导电柱21,且以贴合方式于该承载件20上贴合一具有多个网状开孔(其定义有尺寸较大的开口520和尺寸较小的网孔221)的第一支撑件52(如图5a-1所示),并且再形成一第一绝缘层23以包覆该第一导电柱21、第一支撑件52,其中,该第一支撑件52的开口520可依需求形成大小不一的规则或不规则的孔形或开口形状;再者,该些第一导电柱21与第一支撑件52亦可均以图案化电镀同步形成。

[0209]

于本实施例中,该第一支撑件52为网板,其具有一布设有该些开口520的接点区c,且该开口520对应该第一导电柱21,使各该第一导电柱21分别位于各该开口520中并凸出各该开口520。

[0210]

再者,基于第一实施例的定义,该第一支撑件52具有相对的第一侧52a与第二侧52b。

[0211]

如图5b所示,于该第一导电柱21、该第一绝缘层53上形成一无核心层线路结构24。

[0212]

如图5c所示,于该无核心层线路结构24上以图案化电镀形成多个第二导电柱25,并以贴合方式于该无核心层线路结构24上贴合一具有多个网状开孔(其定义有尺寸较大的开口560和尺寸较小的网孔261)的第二支撑件56(如图5a-1所示),并且再形成一第二绝缘层27以包覆该第二导电柱25、第二支撑件56,其中,该第二支撑件56的开口560可依需求形成大小不一的规则或不规则的孔形或开口形状;再者,该些第二导电柱25与第二支撑件56亦可以图案化电镀同步形成。

[0213]

于本实施例中,该第二支撑件56为网板,其具有一布设有该些开口560的接点区c,且该开口560对应该第二导电柱25,使各该第二导电柱25分别位于各该开口560中并凸出各该开口560。

[0214]

再者,基于第一实施例的定义,该第二支撑件56具有相对的第一侧56a与第二侧56b。

[0215]

如图5d所示,移除该承载件20及该结合层222,且沿如图5c所示的切割路径l进行切单制程,以获取该中介基板5。

[0216]

再者,如图5d-1所示,亦可将如图2f-3、2f-4所示的散热件28的实施例应用于本实施例中,以获取该中介基板5a。

[0217]

应可理解地,本实施其中的该第一支撑件52/该第二支撑件56具有可各自容置该第一导电柱21/第二导电柱25的开口520/560的特征,亦适用于第二实施例(如图5d-2所示的中介基板5b,其第一支撑件52’与第二支撑件56’为一具有多个开口520’,560’的多个层板体)及第三实施例(如图5d-3所示的中介基板5c,其中,该第一支撑件52”与第二支撑件56”为一具有多个开口520”,560”的网状板体,且该第二导电柱45及该第二支撑件56”以图案化蚀刻制程蚀刻该承载板20所形成)中。

[0218]

图6为本发明的中介基板6的第五实施例的剖视示意图。本实施例与上述各实施例的差异在于导电柱的制作,其它制程大致相同,故以下不再赘述相同处。

[0219]

如图6所示,该第一导电柱61为多个层柱体形式,其层间包含有一垫体(land)610,而该第二导电柱65为多个层柱体形式,其层间包含有一垫体650。

[0220]

于本实施例中,以第二实施例为例,于该承载件20上以堆叠方式依序以图案化电镀形成第一柱体611、垫部610及第二柱体612,并且结合形成为第一导电柱61,其功能在于当作置晶侧以覆晶方式接合芯片或中介板,因此需要较细的导电柱间距,故该第一导电柱61采用多段柱实施例有利于满足细间距的制作需求。

[0221]

应可理解地,该第二导电柱65亦可采用具有垫体650的多段柱,其以堆叠方式于该无核心层线路结构24的一线路层上依序以图案化电镀形成第三柱体651、垫部650及第四柱体652,并且结合形成为第二导电柱65。

[0222]

基于第一实施例的定义,该第一导电柱61具有相对的第一端面61a与第二端面61b,且该第二导电柱65具有相对的第一端面65a与第二端面65b。

[0223]

再者,应可理解地,上述各实施例于进行切单作业前,可先对该些导电柱及该些支撑件露出的部位进行表面处理作业,而形成该表面处理层的材质为镍、钯、金、锡、银、铜所组群组的合金、多层金属或有机保焊剂(organic solderability preservative,简称osp)所组成的群组中的其中一者,例如,电镀镍/金、化学镀镍/金、化镍浸金(enig)、化镍钯浸金(enepig)、化学镀锡(immersion tin)或预焊锡(pre-solder)等,但不限于上述。

[0224]

应可理解地,上述各实施例的第二支撑件(或第一支撑件)可借由厚金属层的设计,以提升中介基板的刚性和散热性。

[0225]

综上所述,本发明的中介基板及其制法,借由该无核心层线路结构采用coreless技术以轻易制作出细间距、高密度及细线路的布线,因而能符合大尺寸封装的高i/o数及高布线密度的需求。

[0226]

再者,借由该第一支撑件及第二支撑件与第一绝缘层及第二绝缘层的配置,且利用支撑件具有良好的刚性的特性及适当增厚,使该中介基板的刚性符合需求,因而能有效抗翘曲,故当该中介基板进行芯片元件的封装作业时,能提高品质、可靠度及良率。

[0227]

此外,借由使用该无核心层线路结构,因而无需进行导电通孔制程,故本发明不会产生先前技术所述的缺失。

[0228]

另外,借由该无核心层线路结构,将电路板需细线路布线设计的区域设计于该无核心层线路结构,并增宽各该第二导电柱的间距,故本发明可改善现有电路板的难题。

[0229]

上述实施例仅用以例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟习此项技艺的人士均可在不违背本发明的精神及范畴下,对上述实施例进行修改。因此本发明的权利保护范围,应如权利要求书所列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1