半导体装置以及功率放大器的制作方法

1.本公开涉及半导体装置以及功率放大器。

背景技术:

2.形成于gaas基板或sic基板等的场效应晶体管通过形成所谓的多指(multi-finger)型或鱼骨(fishbone)型的栅电极,能在不增加布局尺寸的情况下增大栅极宽度。此时,在从栅极焊盘布线至栅电极的栅极传输线路与各漏电极之间配置屏蔽电极,由此在高频区域的增益提高(例如,参照专利文献1)。

3.此外,在晶体管区域的中央设置栅极焊盘,将栅电极直接连接于栅极焊盘,由此在栅电极间的电信号的延迟被防止(例如,参照专利文献2)。而且,将多指型的栅电极在栅电极的延伸方向错开地配置,由此在不扩大栅电极的间隔的情况下散热性被提高(例如,参照专利文献3)。

4.在此,进行鱼骨型的栅电极或者鱼骨型的晶体管的说明。鱼骨是指鱼的骨头的意思。鱼具有将头与尾鳍相连的脊骨,与该脊骨大致垂直地在背鳍侧和腹鳍侧分别具有彼此反向地延伸的肋骨等细骨头。将以相当于该脊骨的栅极布线为中心并且相当于细骨头的栅电极隔着栅极布线配置于两侧的栅电极结构称为鱼骨型的栅电极。而且,将以隔着各个栅电极的方式在两侧配置各个源极区域和漏极区域从而分别形成晶体管单元的结构称为鱼骨型的晶体管。鱼骨型的晶体管的栅极宽度成为将连接于栅极布线的各个栅电极的宽度合计而得到的值。

5.现有技术文献

6.专利文献

7.专利文献1:日本特开平4-125941号公报

8.专利文献2:日本特开平6-5849号公报

9.专利文献3:国际公开第2018/020549号

10.例如,就在毫米波段等高频率下进行工作的功率放大器而言,与追求如何提高增益相比,更加追求如何提高输出功率。为了提高输出功率,需要减少输出信号的损失。例如,在搭载于功率放大器的晶体管中,需要使从输出信号的漏极向输出端子的布线的走线成为最小限度。

技术实现要素:

11.因此,本公开的目的在于,通过缩小连接于晶体管的作为输出的漏极的布线合成部来减少输出信号的损失从而增大输出功率。

12.根据本实施方式的一个观点,半导体装置具备:栅极布线,连接于输入布线,在第一方向延伸,该输入布线连接于输入端子;第一晶体管和第二晶体管,沿与所述第一方向正交的第二方向配置于所述栅极布线的两侧;以及布线合成部,将所述第一晶体管的输出和所述第二晶体管的输出连接于输出端子,所述第一晶体管和所述第二晶体管具备:多个栅

电极,连接于所述栅极布线,在所述第二方向延伸;源极区域和漏极区域,隔着多个所述栅电极的每一个沿所述第一方向设置;源极布线,配置于所述源极区域上,连接于所述源极区域;以及漏极布线,配置于所述漏极区域上,连接于所述漏极区域,所述布线合成部具备:第一输出布线,在所述第一晶体管上以跨过所述源极布线中的至少任一个和所述栅电极中的至少任一个的方式在所述第一方向延伸,连接于所述第一晶体管的所述漏极布线;第二输出布线,在所述第二晶体管上以跨过所述源极布线中的至少任一个和所述栅电极中的至少任一个的方式在所述第一方向延伸,连接于所述第二晶体管的所述漏极布线;第三输出布线,将所述第一输出布线的所述第一方向的一端与所述第二输出布线的所述第一方向的一端相互连接;以及第四输出布线,将所述第三输出布线连接于所述输出端子。

13.发明效果

14.根据本公开,能通过缩小连接于晶体管的作为输出的漏极的布线合成部来减少输出信号的损失从而增大输出功率。

附图说明

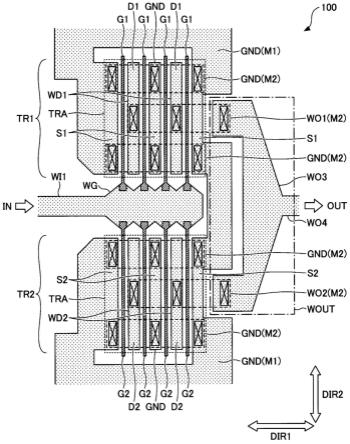

15.图1是表示第一实施方式的半导体装置的电路构成的一个例子的布局图。

16.图2是仅将图1的半导体装置的晶体管的主要部分切出后的立体图。

17.图3是表示搭载有图1的半导体装置的功率放大器和包括功率放大器的通信系统的一个例子的系统构成图。

18.图4是拥有与图1的半导体装置同样的梳状栅(fingergate)型晶体管结构的其他半导体装置(比较例)的立体图。

19.图5是表示第二实施方式的半导体装置的电路构成的一个例子的布局图。

20.图6是仅将图5的半导体装置的晶体管的主要部分切出后的立体图。

21.图7是表示第三实施方式的半导体装置的电路构成的一个例子的布局图。

22.图8是仅将图7的半导体装置的晶体管的主要部分切出后的立体图。

23.附图标记说明

24.10:发送器

25.12:可变增益放大器

26.14:功率放大器

27.16:发送天线

28.20:接收器

29.22:接收天线

30.100、102、104:半导体装置

31.d1、d2:漏极区域

32.dir1、dir2:方向

33.dmy1、dmy2:虚设布线

34.g1、g2:栅电极

35.gnd:接地布线

36.l1:电长度

37.m1:第一金属布线层

38.m2:第二金属布线层

39.out:输出端子

40.s1、s2:源极区域

41.sys:通信系统

42.tr1、tr2:晶体管

43.tra:晶体管区域

44.wd1、wd2:漏极布线

45.wi1:输入布线

46.wo1、wo2、wo3、wo4:输出布线

47.wout:布线合成部。

具体实施方式

48.[本公开的实施方式的说明]

[0049]

首先,列举本公开的实施方案来进行说明。

[0050]

〔1〕本公开的一个方案的半导体装置具备:栅极布线,连接于输入布线,在第一方向延伸,该输入布线连接于输入端子;第一晶体管和第二晶体管,沿与所述第一方向正交的第二方向配置于所述栅极布线的两侧;以及布线合成部,将所述第一晶体管的输出和所述第二晶体管的输出连接于输出端子,所述第一晶体管和所述第二晶体管具备:多个栅电极,连接于所述栅极布线,在所述第二方向延伸;源极区域和漏极区域,隔着多个所述栅电极的每一个沿所述第一方向设置;源极布线,配置于所述源极区域上,连接于所述源极区域;以及漏极布线,配置于所述漏极区域上,连接于所述漏极区域,所述布线合成部具备:第一输出布线,在所述第一晶体管上以跨过所述源极布线中的至少任一个和所述栅电极中的至少任一个的方式在所述第一方向延伸,连接于所述第一晶体管的所述漏极布线;第二输出布线,在所述第二晶体管上以跨过所述源极布线中的至少任一个和所述栅电极中的至少任一个的方式在所述第一方向延伸,连接于所述第二晶体管的所述漏极布线;第三输出布线,将所述第一输出布线的所述第一方向的一端与所述第二输出布线的所述第一方向的一端相互连接;以及第四输出布线,将所述第三输出布线连接于所述输出端子。

[0051]

在该半导体装置中,使布线合成部的第一输出布线和第二输出布线以跨过源极布线和栅电极的方式分别在第一晶体管和第二晶体管上延伸,将布线合成部的第一输出布线和第二输出布线经由漏极布线分别连接于第一晶体管和第二晶体管的漏极区域。由此,能缩短将第一输出布线的一端与第二输出布线的一端相互连接的第三输出布线的电长度。其结果是,能减少来自半导体装置的输出信号的损失,能增大半导体装置的输出功率。换言之,能通过缩小连接于晶体管的作为输出的漏极的布线合成部来减少输出信号的损失从而增大输出功率。此外,能削减连接于输出端子的匹配电路的电路尺寸,能减小半导体装置的尺寸。

[0052]

〔2〕在上述〔1〕中,也可以是,所述半导体装置具备:第一虚设布线,配置于所述第一晶体管的外侧且配置于所述第一输出布线的所述第一方向的另一端侧;以及第二虚设布线,配置于所述第二晶体管的外侧且配置于所述第二输出布线的所述第一方向的另一端侧,所述第一输出布线的另一端延伸至所述第一晶体管的所述外侧并连接于所述第一虚设

布线,所述第二输出布线的另一端延伸至所述第二晶体管的所述外侧并连接于所述第二虚设布线。将第一输出布线和第二输出布线中与和第三输出布线的连接部分相反的一侧的端分别连接于虚设布线,由此能补偿经由各漏极布线连接于各漏极区域的第一输出布线和第二输出布线所产生的寄生电容的对称性。该补偿电路使像多指型、鱼骨型那样存在多个的各漏电极的阻抗均匀,从而减少阻抗失配。其结果是,提出的晶体管形状能使输出功率和增益提高。

[0053]

〔3〕在上述〔1〕中,也可以是,在所述第一晶体管和所述第二晶体管中,在与所述第三输出布线相反的一侧的端形成有所述漏极区域。在该情况下,不将虚设布线连接于第一输出布线和第二输出布线,就能补偿经由各漏极布线连接于各漏极区域的第一输出布线和第二输出布线所产生的寄生电容的对称性,能提高高频特性。

[0054]

〔4〕在上述〔1〕至〔3〕中的任一个中,也可以是,所述源极布线和所述漏极布线使用第一金属布线层来形成,所述第一输出布线和所述第二输出布线具有使用作为第一金属布线层的上层的第二金属布线层来形成的空气桥布线结构。在该情况下,在第一输出布线和第二输出布线之下未设置绝缘膜,因此,能减小布线负载,能提高高频特性。

[0055]

〔5〕在上述〔1〕至〔4〕中的任一个中,也可以是,所述第一输出布线连接于所述第一晶体管的所述漏极布线中所述第二方向的中央部,所述第二输出布线连接于所述第二晶体管的所述漏极布线中所述第二方向的中央部。由此,与将第一输出布线和第二输出布线配置于第一晶体管和第二晶体管的与栅极布线相反的一侧的情况相比,能缩短第三输出布线,能缩短电长度。其结果是,能减少来自半导体装置的输出信号的损失,能增大半导体装置的输出功率。

[0056]

〔6〕本公开的一个方案的功率放大器搭载有上述〔1〕至〔5〕中的任一个的半导体装置。通过在功率放大器搭载上述半导体装置中的任一个,例如,能增长从搭载有功率放大器的发送器发送的无线信号的通信距离。其结果是,能增长发送器与接收器的距离。

[0057]

[本公开的实施方式的详情]

[0058]

以下,参照附图对本公开的半导体装置的具体例进行说明。需要说明的是,本实施方式并不限定于以下的说明。例如,设于一个晶体管区域tra的栅电极至少有两根即可,不限定于各图所示的根数。

[0059]

〔第一实施方式〕

[0060]

〔半导体装置的布局〕

[0061]

图1是表示第一实施方式的半导体装置的电路构成的一个例子的布局图。例如,图1所示的半导体装置100搭载于毫米波段(几十ghz至几百ghz)的功率放大器,用于将高频信号的功率放大。

[0062]

半导体装置100具有晶体管tr1、tr2,该晶体管tr1、tr2将供给至共用的输入端子in的高频的输入信号放大,并将放大后的高频的输出信号从共用的输出端子out输出。晶体管tr1、tr2沿方向dir2并排地配置。例如,各晶体管tr1、tr2是氮化镓高电子迁移率晶体管(gan hemt:gallium nitride high electron mobility transistor)。各晶体管tr1、tr2形成于由虚线的矩形表示的晶体管区域tra。不被特别限定,例如,各晶体管tr1、tr2的栅极长度为100nm(纳米),各晶体管tr1、tr2的栅极宽度为60μm(微米)。

[0063]

晶体管tr1包括:四根栅电极g1,在方向dir2延伸;以及源极区域s1和漏极区域d1,

在各栅电极g1处,沿与方向dir2正交的方向dir1交替地设置。方向dir1是第一方向的一个例子,方向dir2是第二方向的一个例子。栅电极g1使用第一金属布线层m1来形成。在图1所示的例子中,在形成有晶体管tr1的晶体管区域tra中,在方向dir1的两端侧形成有源极区域s1。并且,晶体管tr1具有交替地设置的三个源极区域s1和两个漏极区域d1。

[0064]

使用第一金属布线层m1来形成的接地布线gnd在源极区域s1上直接连接于源极区域s1。形成于源极区域s1上的接地布线gnd是源极布线和源电极的一个例子。使用第一金属布线层m1来形成的漏极布线(漏电极)wd1直接连接于漏极区域d1。第一金属布线层m1是距形成有半导体装置100的半导体基板最近的金属布线层。

[0065]

形成于源极区域s1上的接地布线gnd在方向dir2的两端侧分别连接于在方向dir1延伸的接地布线gnd。在方向dir1延伸的接地布线gnd使用第二金属布线层m2来形成。第二金属布线层m2是在半导体装置100中设于第一金属布线层m1之上的金属布线层。

[0066]

漏极布线wd1连接于在方向dir1延伸的输出布线wo1,该漏极布线wd1形成于漏极区域d1上,直接连接于漏极区域d1,并在方向dir2延伸。输出布线wo1使用第二金属布线层m2来形成,并连接于各漏极布线wd1中的方向dir2的中央部。输出布线wo1具有所谓的空气桥布线结构,以不隔着层间绝缘膜的方式设于栅电极g1的上方和设于源极区域s1上的接地布线gnd的上方。输出布线wo1的输出端子out侧的一端连接于使用第一金属布线层m1来形成的输出布线wo3的一端。

[0067]

晶体管tr2包括:四根栅电极g2,在方向dir2延伸;以及源极区域s2和漏极区域d2,在各栅电极g2处,沿方向dir1交替地设置。栅电极g2使用第一金属布线层m1来形成。与晶体管tr1同样地,在形成有晶体管tr2的另一晶体管区域tra中,在方向dir1的两端侧形成有源极区域s2。并且,晶体管tr2具有交替地设置的三个源极区域s2和两个漏极区域d2。

[0068]

使用第一金属布线层m1来形成的接地布线gnd在源极区域s2上直接连接于源极区域s2。形成于源极区域s2上的接地布线gnd是源极布线和源电极的一个例子。使用第一金属布线层m1来形成的漏极布线(漏电极)wd2直接连接于漏极区域d2。形成于源极区域s2上的接地布线gnd在方向dir2的两端侧分别连接于在方向dir1延伸的接地布线gnd。在方向dir1延伸的接地布线gnd使用第二金属布线层m2来形成。

[0069]

漏极布线wd2连接于在方向dir1延伸的输出布线wo2,该漏极布线wd2形成于漏极区域d2上,直接连接于漏极区域d2,并在方向dir2延伸。输出布线wo2使用第二金属布线层m2来形成,并连接于各漏极布线wd2中的方向dir2的中央部。与输出布线wo1同样地,输出布线wo2具有空气桥布线结构,以不隔着层间绝缘膜的方式设于栅电极g2的上方和设于源极区域s2上的接地布线gnd的上方。输出布线wo2的输出端子out侧的一端连接于输出布线wo3的另一端。由此,输出布线wo1、wo2经由输出布线wo3相互连接。

[0070]

输出布线wo3经由使用第一金属布线层m1来形成的输出布线wo4电连接于输出端子out。由单点划线的框表示的输出布线wo3、wo4作为对从晶体管tr1、tr2的漏极区域d1、d2分别输出的输出信号进行合成的布线合成部wout发挥功能。

[0071]

栅电极g1、g2经由栅极布线wg相互连接。栅极布线wg经由输入布线wi1电连接于输入端子in。就是说,半导体装置100构成鱼骨型晶体管。此外,例如,栅极布线wg和输入布线wi1使用第一金属布线层m1来形成。栅极布线wg和输入布线wi1也可以一体形成。

[0072]

将输出布线wo1连接于各漏极布线wd1中的方向dir2的中央部,将输出布线wo2连

接于各漏极布线wd2中的方向dir2的中央部,由此能使输出布线wo3的方向dir2的长度成为最小限度。由此,能使输出布线wo3的方向dir2的电长度成为最小限度。此外,能减小传递至输出布线wo1、wo2的输出信号的相移。

[0073]

其结果是,能减少来自半导体装置100的输出信号的损失,能增大半导体装置100的输出功率。换言之,能通过缩小连接于晶体管tr1、tr2的作为输出的漏极的布线合成部wout来减少输出信号损失从而增大输出功率。

[0074]

而且,能缩短布线合成部wout的布线长度,并且通过将输出布线wo1~wo4布局为以方向dir1为轴呈线对称,能使从漏极区域d1、d2分别输出的高频的输出信号的相位的偏移成为最小限度。

[0075]

〔从漏极向输出端子的信号的提取〕

[0076]

图2是仅将图1的半导体装置100的晶体管tr1的主要部分切出后的立体图。图2特别是表示从漏极区域d1上的漏极布线wd1连接于输出布线wo3的一端的作为第二金属布线层m2的输出布线wo1的概要和将多个源极区域s1上的接地布线gnd彼此连接的作为第二金属布线层m2的gnd布线的概要的立体图。如在图1中说明过的那样,各漏极区域d1经由具有空气桥布线结构的输出布线wo1连接于输出布线wo3。因此,在输出布线wo1与跟输出布线wo1对置的栅电极g1和接地布线gnd之间形成有由空气形成的间隙。对于作为第二金属布线层m2的gnd布线,也同样地在该gnd布线的下部形成有由空气形成的间隙。

[0077]

由此,能将各漏极布线wd1的中央部直线地连接于输出布线wo3。因此,能使被传递晶体管tr1的输出信号的输出布线wo1、wo3的布线电阻和负载电容成为最小限度,能防止输出信号的高频特性的劣化。图1的连接于晶体管tr2的漏极布线wd2的输出布线wo2的结构也与图2所示的输出布线wo1的结构是同样的,能得到同样的效果。

[0078]

需要说明的是,例如,半导体装置100具有层叠于碳化硅(sic)基板上的氮化镓(gan)层、氮化铝镓(algan)层以及氮化镓层。在碳化硅基板的背面形成有金(au)层来作为接地层gnd。

[0079]

在最上层的氮化镓层之上,使用第一金属布线层m1形成有栅电极g1、g2、接地布线gnd以及漏极布线wd1、wd2。例如,栅电极g1、g2、接地布线gnd以及漏极布线wd1、wd2由金(au)形成。

[0080]

栅电极g1、g2与氮化镓层肖特基连接。需要说明的是,栅电极g1、g2也可以被设为凹槽结构。在晶体管区域tra中,源极区域s1、s2上的接地布线gnd和漏极区域d1、d2上的漏极布线wd1、wd2与氮化镓层欧姆接触。

[0081]

〔搭载有半导体装置的通信系统〕

[0082]

图3是表示搭载有图1的半导体装置100的功率放大器和包括功率放大器的通信系统sys的一个例子的系统构成图。通信系统sys具有:发送器10,以无线形式发送高频信号;以及接收器20,接收从发送器10发送的高频信号。例如,发送器10和接收器20搭载于便携式电话的基站。

[0083]

发送器10具有可变增益放大器12、功率放大器14以及发送天线16。接收器20具有接收天线22和未图示的接收电路。可变增益放大器例如根据控制电压使输入信号的增益变化来生成输出信号,并将所生成的输出信号输出至功率放大器14。

[0084]

功率放大器14将从可变增益放大器12接收到的信号的功率放大,并输出至发送天

线16。发送天线16将从功率放大器14接收的电信号转换为电波,并朝向接收器20发送。接收器20通过接收天线22接收来自发送器10的电波并实施信号处理。

[0085]

在便携式电话的基站中,发送器10所发送的信号的输出功率越大,越能增长基站间的通信距离。通过增长通信距离,能增大基站的设置间隔。因此,使半导体装置100的输出功率提高是重要的。

[0086]

〔其他半导体装置的从漏极向输出端子的信号的提取〕

[0087]

图4是拥有与图1的半导体装置100同样的梳状栅型晶体管结构的其他半导体装置(比较例)的立体图。与图2同样地,图4是仅将相当于晶体管tr1的主要部分切出后的立体图。在图4中,输出布线wo1不是空气桥布线结构,而是与栅极布线wg同样地使用第一金属布线层m1来形成。因此,输出布线wo1形成于能绕形成于源极区域s1上的接地布线gnd迂回的位置。

[0088]

由于输出布线wo1被形成为绕接地布线gnd迂回,因此,输出布线wo3的电长度与图2相比变长,会因多余的电抗分量l而缩窄输出信号的带宽。此外,由于输出布线wo3变长,因此连接于输出端子out的匹配电路的电路尺寸会变大。

[0089]

以上,在该实施方式中,输出布线wo1、wo2具有空气桥布线结构,以跨过源极区域s1上的接地布线gnd和栅电极g1、g2的方式形成,并连接于输出布线wo3。例如,输出布线wo1连接于各漏极布线wd1中的方向dir2的中央部,输出布线wo2连接于各漏极布线wd2中的方向dir2的中央部。

[0090]

由此,能使输出布线wo3的方向dir2的电长度成为最小限度。此外,能减小传递至输出布线wo1、wo2的输出信号的相移。其结果是,能减少来自半导体装置100的输出信号的阻抗和损失,能增大半导体装置100的输出功率。此外,通过减少阻抗,能削减连接于半导体装置100的输出端子out的未图示的匹配电路的电路尺寸,能减小半导体装置100的尺寸。而且,输出布线wo1、wo2具有空气桥布线结构,因此,能减小布线负载,能提高高频特性。

[0091]

通过在通信系统sys的发送器10的功率放大器14搭载半导体装置100,能使到接收器20的通信距离增长。例如,在发送器10和接收器20分别搭载于便携式电话的基站的情况下,能增长基站间的通信距离。其结果是,能增大基站的设置间隔,能削减通信系统sys的设备成本。

[0092]

〔第二实施方式〕

[0093]

〔半导体装置的布局〕

[0094]

图5是表示第二实施方式的半导体装置的电路构成的一个例子的布局图。对与图1同样的要素标注相同的附图标记,省略详细的说明。图5所示的半导体装置102除了输出布线wo1、wo2与图1的输出布线wo1、wo2不同之外,具有与图1的半导体装置100同样的结构。

[0095]

输出布线wo1中方向dir1的与输出布线wo3相反的一侧的端延伸至晶体管区域tra的外侧,并连接于配置在晶体管区域tra的外侧的虚设布线dmy1。输出布线wo2中方向dir1的与输出布线wo3相反的一侧的端延伸至另一个晶体管区域tra的外侧,并连接于配置在另一个晶体管区域tra的外侧的虚设布线dmy2。

[0096]

例如,虚设布线dmy1、dmy2使用第一金属布线层m1来形成。虚设布线dmy1不与输出布线wo1以外电连接,虚设布线dmy2不与输出布线wo2以外电连接。

[0097]

例如,图5的左侧的漏极布线wd1与虚设布线dmy1的距离等于两个漏极布线wd1间

的距离和图5的右侧的漏极布线wd1与输出布线wo3的距离。图5的左侧的漏极布线wd2与虚设布线dmy2的距离等于两个漏极布线wd2间的距离和图5的右侧的漏极布线wd2与输出布线wo3的距离。因此,输出布线wo1相对于各漏极布线wd1具有对称性,输出布线wo2相对于各漏极布线wd2具有对称性。

[0098]

〔输出布线的对称性〕

[0099]

图6是仅将图5的半导体装置102的晶体管tr1的主要部分切出后的立体图。图6特别是表示连接于晶体管tr1的漏极布线wd1的输出布线wo1的概要的立体图。各漏极区域d1经由具有空气桥布线结构的输出布线wo1连接于输出布线wo3。此时,输出布线wo1的一端连接于输出布线wo3,输出布线wo1的另一端连接于虚设布线dmy1。

[0100]

因此,能使相对于各漏极布线wd1朝向方向dir1的两侧延伸并连接于邻接的漏极布线wd1和输出布线wo3(或虚设布线dmy1)的输出布线wo1的局部布线具有对称性。与输出布线wo1同样地,也能使相对于各漏极布线wd2朝向方向dir1的两侧延伸的输出布线wo2的局部布线具有对称性。

[0101]

其结果是,能补偿经由各漏极布线wd1连接于各漏极区域d1的输出布线wo1所产生的寄生电容的对称性,能提高高频特性。此外,能补偿经由各漏极布线wd2连接于各漏极区域d2的输出布线wo2所产生的寄生电容的对称性,能提高高频特性。

[0102]

需要说明的是,在栅电极g1的数量为奇数(例如三根)时未形成有图6的位于最左侧的栅电极g1和源极区域s1的情况下,虚设布线dmy1也配置于图6所示的位置。并且,输出布线wo1连接于虚设布线dmy1。晶体管tr2的栅电极g2的数量为奇数的情况也是同样的。由此,无论栅电极g1、g2的数量如何,都能补偿输出布线wo1、wo2所产生的寄生电容的对称性。

[0103]

以上,在该实施方式中,也能得到与上述的实施方式同样的效果。而且,在该实施方式中,输出布线wo1、wo2中与和输出布线wo3的连接部分相反的一侧的端分别连接于虚设布线dmy1、dmy2。由此,能补偿经由各漏极布线wd1、wd2连接于各漏极区域d1、d2的输出布线wo1、wo2所产生的寄生电容的对称性,能提高高频特性。

[0104]

〔第三实施方式〕

[0105]

〔半导体装置的布局〕

[0106]

图7是表示第三实施方式的半导体装置的电路构成的一个例子的布局图。对与图1同样的要素标注相同的附图标记,省略详细的说明。在图7所示的半导体装置104中,在晶体管tr1中,源极区域s1和漏极区域d1的排列顺序与图1不同。此外,在晶体管tr2中,源极区域s2和漏极区域d2的排列顺序与图1不同。需要说明的是,图7示出栅电极g1的数量和栅电极g2的数量分别为偶数的情况。

[0107]

在晶体管tr1中,三个漏极区域d1分别形成于方向dir1的两端和中央,在两个漏极区域d1之间分别形成有源极区域s1。配置于各漏极区域d1上的漏极布线wd1连接于各漏极区域d1。配置于各源极区域s1上的接地布线gnd连接于各源极区域s1。源极区域s1上的接地布线gnd连接于在晶体管区域tra的外部配置于与晶体管tr2相反的一侧的接地布线gnd。

[0108]

在晶体管tr2中,三个漏极区域d2分别形成于方向dir1的两端和中央,在两个漏极区域d2之间分别形成有源极区域s2。配置于各漏极区域d2上的漏极布线wd2连接于各漏极区域d2。配置于各源极区域s2上的接地布线gnd连接于各源极区域s2。源极区域s2上的接地布线gnd连接于在另一个晶体管区域tra的外部配置于与晶体管tr1相反的一侧的接地布线

gnd。

[0109]

在该实施方式中,输出布线wo1连接于位于方向dir1的两端和中央的漏极区域d1上的漏极布线wd1。并且,输出布线wo1经由距输出布线wo3最近的漏极布线wd1连接于输出布线wo3。输出布线wo2连接于位于方向dir1的两端和中央的漏极区域d2上的漏极布线wd2。并且,输出布线wo2经由距输出布线wo3最近的漏极布线wd2连接于输出布线wo3。

[0110]

〔输出布线的对称性〕

[0111]

图8是仅将图7的半导体装置104的晶体管tr1的主要部分切出后的立体图。图8特别是表示连接于漏极布线wd1的输出布线wo1的概要的立体图。如图8所示,在栅电极g1的数量为偶数并且在方向dir1的两端侧形成有漏极区域d1的情况下,不形成图6所示的虚设布线dmy1,就能补偿连接于漏极区域d1的输出布线wo1所产生的寄生电容的对称性。晶体管tr2的输出布线wo2也同样地能补偿寄生电容的对称性。

[0112]

需要说明的是,在栅电极g1为三根而未形成有图8的最左侧的栅电极g1和漏极区域d1的情况下,也可以形成虚设布线来代替图8的位于最左的漏极布线wd1。

[0113]

以上,在该实施方式中,也能得到与上述的实施方式同样的效果。而且,在该实施方式中,不形成图6所示的虚设布线dmy1、dmy2,就能补偿连接于漏极区域d1、d2的输出布线wo1、wo2所产生的寄生电容的对称性,能提高输出信号的高频特性。

[0114]

以上,对本公开的实施方式等进行了说明,但本公开不限定于上述实施方式等。在权利要求书所记载的范围内,可以进行各种变更、修改、替换、附加、删除以及组合。这些也当然属于本公开的技术范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1