光检测器件和电子设备的制作方法

光检测器件和电子设备

1.本技术是申请日为2017年1月13日、发明名称为“固态成像元件和电子设备”的申请号为201780001074.9专利申请的分案申请。

技术领域

2.本公开涉及一种固态成像元件和电子设备,特别地,涉及一种能够防止相邻像素之间的电荷泄漏的固态成像元件和电子设备。

背景技术:

3.在过去,在诸如数码相机和数字摄像机等具有成像功能的电子设备中,使用诸如电荷耦合器件(ccd:charge coupled device)图像传感器和互补金属氧化物半导体(cmos:complementary metal oxide semiconductor)图像传感器等固态成像元件。固态成像元件具有其中组合有用于进行光电转换的光电二极管(光电转换元件)和晶体管的像素,并且基于从配置在平面中的多个像素输出的像素信号来创建图像。

4.例如,在固态成像元件中,在光电二极管(pd:photodiode)中蓄积的电荷被传输到浮动扩散(fd:floating diffusion)部,该fd部具有在pd与放大晶体管的栅电极之间的连接部处设置的预定电容。然后,从该像素中读取与在fd部中蓄积的电荷量相对应的像素信号,并且由具有比较器的模拟数字(ad:analog digital)转换电路对该像素信号进行ad转换并将其输出。

5.另外,近年来,通过使用cmos图像传感器的一部分像素来检测相位以提高自动对焦(af:autofocus)速度的技术(即,所谓的像面相位差af)已经得到普及。像面相位差af的系统的示例包括pd分割系统(例如,参见专利文献1)。在pd分割系统中,将像素的pd分割为多个部分,基于由分割的各个pd获取的像素信号来生成相位信息,并且基于相位信息进行距离测量。

6.引用列表

7.专利文献

8.专利文献1:日本专利申请特开no.2000-292685

技术实现要素:

9.技术问题

10.另一方面,当强光入射到像素中时,在某些情况下,会发生其中在像素的pd中蓄积的电荷饱和、溢出并泄漏到相邻像素中的被称为混色的现象。当发生泄漏混色时,与从相邻像素读取的像素信号相对应的电荷量大于原始电荷量,这会导致成像特性的劣化。

11.鉴于以上情况完成了本公开,以防止相邻像素之间的电荷泄漏。

12.技术方案

13.根据本公开第一方面的固态成像元件为具有如下特征的固态成像元件,所述固态成像元件包括:多个像素,所述多个像素对光进行光电转换,所述光经由针对每个像素的不

同透镜从所述固态成像元件的背面入射到各像素中;像素分离壁,所述像素分离壁形成在相邻的所述像素之间;以及配线层,所述配线层设置在所述固态成像元件的前表面上,其中,所述像素分离壁包括作为从所述前表面形成的沟槽的前表面沟槽和作为从所述背面形成的沟槽的背面沟槽。

14.在本公开的第一方面中,设置有:多个像素,所述多个像素对光进行光电转换,所述光经由针对每个像素的不同透镜从所述固态成像元件的背面入射到各像素中;像素分离壁,所述像素分离壁形成在相邻的所述像素之间;以及配线层,所述配线层设置在所述固态成像元件的前表面上,其中,所述像素分离壁包括作为从所述前表面形成的沟槽的前表面沟槽和作为从所述背面形成的沟槽的背面沟槽。

15.根据本公开第二方面的电子设备为具有如下特征的电子设备,所述电子设备包括固态成像元件,所述固态成像元件包括:多个像素,所述多个像素对光进行光电转换,所述光经由针对每个像素的不同透镜从所述固态成像元件的背面入射到各像素中;像素分离壁,所述像素分离壁形成在相邻的所述像素之间;以及配线层,所述配线层设置在所述固态成像元件的前表面上,其中,所述像素分离壁包括作为从所述前表面形成的沟槽的前表面沟槽和作为从所述背面形成的沟槽的背面沟槽。

16.在本公开的第二方面中,设置有具有如下特征的固态成像元件,所述固态成像元件包括:多个像素,所述多个像素对光进行光电转换,所述光经由针对每个像素的不同透镜从所述固态成像元件的背面入射到各像素中;像素分离壁,所述像素分离壁形成在相邻的所述像素之间;以及配线层,所述配线层设置在所述固态成像元件的前表面上,其中,所述像素分离壁包括作为从所述前表面形成的沟槽的前表面沟槽和作为从所述背面形成的沟槽的背面沟槽。

17.有益效果

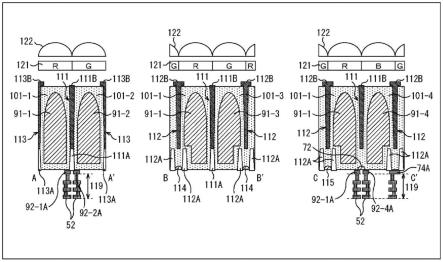

18.根据本公开的第一方面和第二方面,可以拍摄图像。另外,根据本公开的第一方面和第二方面,可以防止相邻像素之间的电荷泄漏。

19.需要指出的是,这里说明的效果不一定是限制性的,并且可以为在本公开中说明的任何效果。

附图说明

20.图1是示出了作为本公开适用的固态成像元件的cmos图像传感器的第一实施方案的构成例的框图。

21.图2是示出了在图1所示的像素区域中配置的像素组的电路构成例的图。

22.图3是示出了图2所示的像素组的第一结构例的如从cmos图像传感器的前表面侧观察到的图。

23.图4是沿着图3的线a-a'、线b-b'和线c-c'获得的断面图。

24.图5是说明当在图2所示的pd中蓄积的电荷溢出时电荷的流动的图。

25.图6是示出了图2所示的像素组的第二结构例的图。

26.图7是示出了作为本公开适用的固态成像元件的cmos图像传感器的第二实施方案的构成例的框图。

27.图8是示出了在图7所示的像素区域中配置的相位差检测像素的电路构成例的图。

28.图9是示出了图8所示的相位差检测像素的结构例的如从cmos图像传感器的前表面侧观察到的图。

29.图10是沿着图9的线a-a'、线b-b'和线c-c'获得的断面图。

30.图11是沿着图9的线d-d'和线e-e'获得的断面图。

31.图12是说明图7所示的cmos图像传感器的操作的图。

32.图13是说明图7所示的cmos图像传感器的操作的图。

33.图14是说明图7所示的cmos图像传感器的操作的图。

34.图15是示出了本公开适用的cmos图像传感器的第三实施方案的相位差检测像素的电路构成例的图。

35.图16是示出了相位差检测像素270的第一结构例的如从cmos图像传感器的前表面侧观察到的图。

36.图17是沿着图16的线a-a'和线b-b'获得的断面图。

37.图18是沿着图16的线c-c'和线d-d'获得的断面图。

38.图19是说明cmos图像传感器的第三实施方案的操作的图。

39.图20是说明cmos图像传感器的第三实施方案的操作的图。

40.图21是说明cmos图像传感器的第三实施方案的操作的图。

41.图22是说明cmos图像传感器的第三实施方案的操作的图。

42.图23是图15所示的相位差检测像素的第二结构例的沿着图16的线b-b'和线c-c'获得的断面图。

43.图24是图15所示的相位差检测像素的第三结构例的沿着图16的线e-e'获得的断面图。

44.图25是在cmos图像传感器的第三实施方案的视角端部处的相位差检测像素的第四结构例的沿着图16的线e-e'获得的断面图。

45.图26是说明图25所示的相位差检测像素的pd的制造方法的图。

46.图27是在本公开适用的cmos图像传感器的第三实施方案的视角端部处的相位差检测像素的第五结构例的沿着图16的线e-e'获得的断面图。

47.图28是说明图27所示的相位差检测像素的pd的制造方法的图。

48.图29是说明图27所示的相位差检测像素的pd的制造方法的图。

49.图30是示出了图15所示的相位差检测像素的第六结构例的图。

50.图31是示出了图15所示的相位差检测像素的第六结构例的图。

51.图32是示出了图15所示的相位差检测像素的第七结构例的图。

52.图33是示出了图15所示的相位差检测像素的第七结构例的图。

53.图34是示出了图15所示的相位差检测像素的第八结构例的图。

54.图35是示出了图15所示的相位差检测像素的第八结构例的图。

55.图36是示出了图15所示的相位差检测像素的第九结构例的图。

56.图37是示出了相位差检测像素的另一结构例的图。

57.图38是说明图37所示的背面沟槽的制造方法的图。

58.图39是示出了图37所示的背面沟槽的另一结构例的图。

59.图40是示出了像素区域的另一构成例的如从cmos图像传感器的前表面侧观察到

的图。

60.图41是示出了作为本公开适用的电子设备的成像装置的构成例的框图。

61.图42是示出了使用上述cmos图像传感器的使用例的图。

具体实施方式

62.以下,对实施本公开的方案(以下称为“实施方案”)进行说明。需要指出的是,将按以下顺序进行说明。

63.1.第一实施方案:cmos图像传感器(图1~图6)

64.2.第二实施方案:cmos图像传感器(图7~图14)

65.3.第三实施方案:cmos图像传感器(图15~图40)

66.4.第四实施方案:成像装置(图41)

67.5.cmos图像传感器的使用例(图42)

68.第一实施方案

69.cmos图像传感器的第一实施方案的构成例

70.图1是示出了作为本公开适用的固态成像元件的cmos图像传感器的第一实施方案的构成例的框图。

71.cmos图像传感器50包括在诸如硅基板等半导体基板(芯片)(未示出)上形成的像素区域51、像素驱动线52、垂直信号线53、垂直驱动部54、列处理部55、水平驱动部56、系统控制部57、信号处理部58和存储部59。cmos图像传感器50为背面照射型cmos图像传感器,其中,光的照射面是与设置有配线层的前表面相对的背面。

72.在cmos图像传感器50的像素区域51上,以阵列方式二维地配置有多个像素,并且进行图像拍摄,其中,每个像素都具有用于对从背面入射的光进行光电转换并蓄积电荷的pd。像素区域51的每个像素的滤色器的阵列为拜耳(bayer)阵列。另外,在像素区域51中,针对每两行像素形成像素驱动线52,针对每两列像素形成垂直信号线53。

73.垂直驱动部54包括移位寄存器、地址译码器等,并且将驱动信号提供给像素驱动线52,从而按照奇数列和偶数列的顺序以行为单位从顶部顺序地读取与像素区域51的每个像素的pd中蓄积的电荷相对应的像素信号。

74.列处理部55包括针对像素区域51的每两列像素的信号处理电路。列处理部55的每个信号处理电路对从像素读取并经由垂直信号线53提供的像素信号进行诸如a/d转换处理和相关双采样(cds:correlated double sampling)处理等信号处理。列处理部55暂时保持经信号处理后的像素信号。

75.水平驱动部56包括移位寄存器、地址译码器等,并且顺序地选择列处理部55的信号处理电路。因此,将在列处理部55的各信号处理电路中处理的像素信号顺序地输出到信号处理部58。

76.系统控制部57包括时序发生器,该时序发生器生成各种时序信号等,并且基于由时序发生器生成的各种时序信号来控制垂直驱动部54、列处理部55和水平驱动部56。

77.信号处理部58对从列处理部55输出的像素信号进行各种信号处理。此时,信号处理部58根据需要将信号处理的中间结果等存储在存储部59中,并且在必要时序时,引用该结果。信号处理部58输出经信号处理后的像素信号。

78.存储部59包括动态随机存取存储器(dram:dynamic random access memory)、静态随机存取存储器(sram:static random access memory)等。

79.像素组的电路构成例

80.图2是示出了在图1所示的像素区域51中配置的像素中的由2(水平)

×

2(垂直)个像素组成的像素组的电路构成例的图。

81.在图1所示的像素区域51中,图2所示的像素组70配置成阵列。每个像素组70包括2

×

2个像素71-1~71-4、fd 72、复位晶体管73、放大晶体管74、选择晶体管75、电源电极76和阱电极77。

82.像素71-1~71-4的各者包括pd和传输晶体管。具体地,像素71-1包括pd 91-1和传输晶体管92-1,像素71-2包括pd 91-2和传输晶体管92-2。另外,像素71-3包括pd 91-3和传输晶体管92-3,像素71-4包括pd 91-4和传输晶体管92-4。

83.需要指出的是,在以下说明中,当无需特别区分像素71-1~71-4时,将它们统称为像素71。同样,将pd 91-1~91-4统称为pd 91,将传输晶体管92-1~92-4统称为传输晶体管92。

84.像素71的pd 91生成并蓄积与从cmos图像传感器50的背面入射和并被其接收的光的光量相对应的电荷。pd 91的阳极端子连接到电位为vss(例如,gnd)的阱电极77,pd 91的阴极端子经由传输晶体管92连接到fd 72。

85.传输晶体管92-1的栅电极92-1a连接至与构成像素组70的两行像素71对应的像素驱动线52中的针对像素71-1(71-2)行的奇数列中的像素71形成的线tg1。另外,传输晶体管92-2的栅电极92-2a连接至与构成像素组70的两行像素71对应的像素驱动线52中的针对像素71-1(71-2)行的偶数列中的像素71形成的线tg2。

86.另外,传输晶体管92-3的栅电极92-3a连接至与构成像素组70的两行像素71对应的像素驱动线52中的针对像素71-3(71-4)行的奇数列中的像素71形成的线tg3。另外,传输晶体管92-4的栅电极92-4a连接至与构成像素组70的两行像素71对应的像素驱动线52中的针对像素71-3(71-4)行的偶数列中的像素71形成的线tg4。需要指出的是,在以下说明中,当无需特别区分栅电极92-1a~92-4a时,将它们统称为栅电极92a。

87.从图1所示的垂直驱动部54向线tg1~tg4提供作为驱动信号的传输信号。垂直驱动部54根据要从其读取像素信号的像素71的行以及奇数列或偶数列来顺序地接通线tg1~tg4的传输信号。在接通输入至栅电极92a的传输信号的情况下,传输晶体管92将在pd 91中蓄积的电荷传输至fd 72。

88.fd 72保持从pd 91读取的电荷。fd 72经由复位晶体管73连接至电位为vdd的电源电极76。

89.另外,复位晶体管73的栅电极73a连接至与构成像素组70的两行像素71对应的像素驱动线52中的针对这两行像素中的像素71形成的线rst1。从垂直驱动部54向线rst1提供作为驱动信号的复位信号。垂直驱动部54在新接通传输信号之前接通复位信号。

90.当接通输入至栅电极73a的复位信号时,复位晶体管73将传输到fd 72的电荷放电到电源电极76,并且使fd 72的电位复位。

91.在电源电极76和垂直信号线53之间,放大晶体管74和选择晶体管75串联连接。放大晶体管74的栅电极74a连接至fd 72,放大晶体管74利用电源电极76将与fd 72的电位相

对应的像素信号输出至选择晶体管75。

92.选择晶体管75的栅电极75a连接至与构成像素组70的两行像素71对应的像素驱动线52中的针对这两行像素中的像素71形成的线sel1。从垂直驱动部54向线sel1提供作为驱动信号的选择信号。垂直驱动部54在接通传输信号之后接通复位信号之前接通选择信号。

93.当接通输入至栅电极75a的选择信号时,选择晶体管75将从放大晶体管74输入的像素信号经由图1所示的垂直信号线53提供到列处理部55。

94.如上所述,在cmos图像传感器50中,构成像素组70的2

×

2个像素71之间共用一个fd 72,并且在像素71的pd 91中蓄积的电荷按照奇数列和偶数列的顺序以行为单位从顶部顺序地传输到fd 72。

95.像素组的第一结构例

96.图3是示出了图2所示的像素组70的第一结构例的如从cmos图像传感器50的前表面侧观察到的图。图4是沿着图3的线a-a'、线b-b'和线c-c'获得的断面图。

97.如图3所示,以与p型杂质101-2在水平方向(图3中的左右方向)上对齐且与p型杂质101-3在垂直方向(图3中的上下方向)上对齐的方式配置p型杂质101-1,其中,p型杂质101-1为其中形成有pd 91-1的阱,在p型杂质101-2中形成有pd 91-2,并且在p型杂质101-3中形成有pd91-3。另外,以与p型杂质101-3在水平方向上对齐且与p型杂质101-2在垂直方向上对齐的方式配置p型杂质101-4,其中,在p型杂质101-4中形成有pd 91-4。需要指出的是,在以下说明中,当无需特别区分p型杂质101-1~101-4时,将它们统称为p型杂质101。

98.如图4所示,在同一像素组70中的相邻p型杂质101之间形成有像素分离壁111。像素分离壁111通过作为从cmos图像传感器50的前表面形成的沟槽的前表面沟槽111a和作为从背面形成的沟槽的背面沟槽111b之间的接触形成。需要指出的是,在cmos图像传感器50的前表面上的同一像素组70中的相邻p型杂质101之间的区域中,在形成有fd 72的p型杂质101-1~101-4的中心区域中未形成前表面沟槽111a。

99.也就是说,像素分离壁111通过前表面沟槽111a和背面沟槽111b之间的接触形成,其中,该前表面沟槽在同一像素组70中的相邻p型杂质101之间的前表面上的区域中的未形成fd 72的区域中形成,并且该背面沟槽在p型杂质101之间的背面的整个区域中形成。

100.另外,跨过像素组70,在垂直方向上彼此相邻的p型杂质101之间形成有像素分离壁112,并且在水平方向上彼此相邻的p型杂质101之间形成有像素分离壁113。

101.像素分离壁112包括夹持n型杂质114~117和p型杂质118的两个前表面沟槽112a和背面沟槽112b。背面沟槽112b在与n型杂质114~117和p型杂质118对应且与两个前表面沟槽112a的位置不同的位置处形成。

102.n型杂质114连接至fd 72,并构成复位晶体管73的源极。n型杂质115连接至电源电极76,并构成复位晶体管73和放大晶体管74的漏极。n型杂质116构成放大晶体管74的源极和选择晶体管75的漏极。n型杂质117连接至垂直信号线53,并构成选择晶体管75的源极。p型杂质118为连接至阱电极77的阱。

103.栅电极92a、栅电极73a和栅电极75a连接至在cmos图像传感器50的前表面上形成的配线层119中设置的像素驱动线52。fd 72连接至栅电极74a。

104.此外,在每个p型杂质101的背面侧形成有对应像素71的红色(r)、绿色(g)和蓝色(b)滤色器121,在每个滤色器121的外侧形成有片上透镜122。pd 91对经由片上透镜122和

滤色器121从cmos图像传感器50的背面入射的光进行光电转换。

105.如上所述,由于在像素分离壁111中,除fd 72以外的区域中前表面沟槽111a和背面沟槽111b彼此接触,因此,在除fd 72以外的区域中,同一像素组70中的各pd 91被完全电切断。另外,由于在像素分离壁113中,前表面沟槽113a和背面沟槽113b彼此接触,因此,跨过像素组70相邻的pd 91也都被完全电切断。

106.另一方面,在像素分离壁112中,前表面沟槽112a和背面沟槽112b的位置不同,并且前表面沟槽112a和背面沟槽112b未彼此接触。因此,pd 91与n型杂质114~117和p型杂质118并未被完全电切断。

107.需要指出的是,前表面沟槽111a(112a、113a)和背面沟槽111b(112b、113b)的与背面垂直的深度方向上的长度取决于像素分离壁111(112、113)的位置而可以不同。另外,前表面沟槽111a(112a、113a)和背面沟槽111b(112b、113b)中的至少一者的材料取决于像素分离壁111(112、113)的位置而可以不同。

108.另外,可以针对像素组70来设置一个片上透镜122。

109.溢出时电荷的流动的说明

110.图5是说明当在pd 91中蓄积的电荷溢出时电荷的流动的图。

111.图5的部分a是示出了当在pd 91中蓄积的电荷溢出时像素组70的如从前表面侧观察到的图,图5的部分b是沿着图5的部分a的线c-c'获得的断面图。

112.如上所述,由于在除fd 72以外的区域中,各pd 91被完全电切断,因此,在电荷溢出的情况下,可以防止在pd 91中蓄积的电荷从pd 91泄漏至另一相邻pd 91中。

113.另一方面,在像素分离壁111的fd 72的区域中,未形成前表面沟槽111a。因此,在pd 91中蓄积的电荷溢出的情况下,溢出的电荷会通过图5的部分b所示的路径w1经由p型杂质101泄漏到fd 72中。然而,由于在从pd 91传输电荷之前将fd 72复位,因此从pd 91向fd 72泄漏电荷对成像特性的影响较小。

114.另外,如上所述,由于在像素分离壁112中,前表面沟槽112a和背面沟槽112b未彼此接触,因此,pd 91与n型杂质114~117和p型杂质118未被完全电切断。因此,在pd 91中蓄积的电荷溢出的情况下,溢出的电荷也可以通过图5的部分b所示的路径w2经由n型杂质115放电到电源电极76。

115.因此,即使在从pd 91溢出的电荷量大于在fd 72中可蓄积的电荷量的情况下,也可以通过将电荷放电到电源电极76来防止电荷泄漏到相邻pd 91。因此,可以防止因向相邻pd 91泄漏电荷而导致的成像特性的劣化。

116.另一方面,在不存在路径w2的情况下,需要在从pd 91溢出的电荷量超过在fd 72中可蓄积的电荷量之前通过接通复位信号来清除蓄积在fd 72中的电荷。因此,垂直驱动部54的处理会变得复杂。

117.需要指出的是,路径w1中在没有物理屏障(physical barrier)的情况下进行电荷泄漏,并且在路径w2中通过由前表面沟槽112a和背面沟槽112b形成的物理屏障之间的间隙进行电荷泄漏。因此,与路径w2中的泄漏相比,优先进行路径w1中的泄漏。

118.如上所述,在cmos图像传感器50中,像素分离壁111(112、113)由前表面沟槽111a(112a、113a)和背面沟槽111b(112b、113b)形成。

119.因此,通过使像素分离壁113的前表面沟槽113a与背面沟槽113b接触,可以使像素

分离壁113贯通cmos图像传感器50。前表面沟槽113a和背面沟槽113b的深度与宽度的高宽比小于从cmos图像传感器50的前表面和背面中一者起贯通的贯通沟槽的高宽比。因此,与由贯通沟槽来形成像素分离壁的情况相比,像素分离壁113的形成较容易。

120.另外,通过形成掩模图案来控制前表面沟槽111a~113a的有/无以及位置,可以容易地实现电荷的有意泄漏和切断,其中,形成掩模图案为一般的半导体工艺。

121.另外,可以提高与一般的cmos图像传感器的兼容性,在一般cmos图像传感器中,在前表面侧形成有诸如浅沟槽隔离(sti:shallow trench isolation)等器件隔离用的沟槽。因此,例如,在将本技术应用于其中在前表面侧形成有诸如sti等器件隔离用的沟槽的cmos图像传感器的情况下,可将沟槽用作前表面沟槽111a~113a中的至少一者。因此,可以抑制因形成像素分离壁111~113而导致的制造步骤数量的增加。

122.像素组的第二结构例

123.图6是示出了2

×

2像素组70的第二结构例的图。图6的部分a是示出了2

×

2像素组70的第二结构例的如从cmos图像传感器50的前表面侧观察到的图,图6的部分b是如从背面侧观察到的图。图6的部分c是沿着图6的部分a的线d-d'获得的断面图。需要指出的是,在下图中,除非另外说明,否则在从cmos图像传感器的背面侧观察到的图中未示出滤色器231和片上透镜232。

124.在图6所示的构成中,与图3和图4所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

125.图6所示的像素组70的结构与图3和图4所示的结构的不同之处在于:p型杂质118位于2

×

2像素组70的交点处。

126.如图6的部分c所示,像素分离壁112的两个前表面沟槽112a以夹持p型杂质118的方式形成,并且背面沟槽112b在与p型杂质118对应的位置处形成。具体地,前表面沟槽112a和背面沟槽112b未彼此接触。因此,可以经由一个p型杂质118将外围p型杂质101的电位同时固定为阱电极77的电位。

127.另一方面,在像素分离壁112的前表面沟槽112a和背面沟槽112b彼此接触的情况下,需要针对每个像素71来形成p型杂质118。因此,会减少可分配给pd 91、传输晶体管92、复位晶体管73、放大晶体管74、选择晶体管75等的面积,这将导致成像特性的劣化。

128.另外,在图6的示例中,如图6的部分a所示,由于p型杂质118位于2

×

2像素组70的交点处,因此,从pd 91到n型杂质115的路径w2(图5)中的电荷泄漏容易发生。

129.第二实施方案

130.cmos图像传感器的第二实施方案的构成例

131.图7是示出了作为本公开适用的固态成像元件的cmos图像传感器的第二实施方案的构成例的框图。

132.在图7所示的构成中,与图1所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

133.cmos图像传感器180为背面照射型cmos图像传感器,其中,在诸如硅基板等的半导体基板(未示出)上形成有像素区域181、像素驱动线182、垂直信号线183、垂直驱动部184、列处理部185、水平驱动部56、系统控制部57、信号处理部188和存储部59。

134.在cmos图像传感器180的像素区域181上,以阵列方式二维地配置有多个相位差检

测像素,并且进行图像拍摄,其中,每个相位差检测像素都具有用于对从背面入射的光进行光电转换并蓄积电荷的两个pd。像素区域181的每个相位差检测像素的滤色器的阵列为拜耳阵列。另外,在像素区域181中,针对每行相位差检测像素形成像素驱动线182,针对每列相位差检测像素形成垂直信号线183。

135.垂直驱动部184包括移位寄存器、地址译码器等,并且将驱动信号提供给像素驱动线182,从而以行为单位从顶部顺序地读取与像素区域181的每个相位差检测像素的两个pd中蓄积的电荷相对应的像素信号。

136.列处理部185包括针对像素区域181的每列相位差检测像素的信号处理电路。列处理部185的每个信号处理电路对从相位差检测像素读取并经由垂直信号线183提供的像素信号进行诸如a/d转换处理和相关双采样(cds:correlated double sampling)处理等信号处理。列处理部185暂时保持经信号处理后的像素信号。

137.信号处理部188通过选择水平驱动部56,基于从列处理部185输出的每个相位差检测像素的两个pd的像素信号,来进行像面相位差af等。此时,信号处理部188根据需要将处理的中间结果等存储在存储部59中,并且在必要时序时,引用该结果。信号处理部188输出处理结果等。

138.相位差检测像素的电路构成例

139.图8是示出了在图7所示的像素区域181中配置的相位差检测像素的电路构成例的图。

140.相位差检测像素190包括分割像素191-1~191-2、fd 192、复位晶体管193、放大晶体管194、选择晶体管195、电源电极197和阱电极198。

141.分割像素191-1包括pd 201-1和传输晶体管202-1,分割像素191-2包括pd 201-2和传输晶体管202-2。

142.需要指出的是,在以下说明中,当无需特别区分分割像素191-1和分割像素191-2上时,将它们统称为分割像素191。同样,将pd 201-1和pd 201-2统称为pd 201,将传输晶体管202-1和传输晶体管202-2统称为传输晶体管202。

143.分割像素191的pd 201生成并蓄积与从cmos图像传感器180的背面入射并被其接收的光的光量相对应的电荷。pd 201的阳极端子连接到电位为vss(例如,gnd)的阱电极198,pd 201的阴极端子经由传输晶体管202连接到fd 192。

144.传输晶体管202-1的栅电极202-1a连接至与相位差检测像素190的行对应的像素驱动线182中的针对构成相位差检测像素190的一个分割像素191-1形成的线tg11。另外,传输晶体管202-2的栅电极202-2a连接至与相位差检测像素190的行对应的像素驱动线182中的针对构成相位差检测像素190的另一个分割像素191-2形成的线tg12。需要指出的是,在以下说明中,当无需特别区分栅电极202-1a和栅电极202-2a时,将它们统称为栅电极202a。

145.从垂直驱动部184向线tg11和tg12提供作为驱动信号的传输信号。垂直驱动部184顺序地接通要从其读取像素信号的相位差检测像素190的行中的线tg11和tg12的传输信号。在接通输入至栅电极202a的传输信号的情况下,传输晶体管202将在pd 201中蓄积的电荷传输至fd 192。

146.fd 192保持从pd 201读取的电荷。fd 192经由复位晶体管193连接至电位为vdd的电源电极197。

147.复位晶体管193的栅电极193a连接至与相位差检测像素190的行对应的像素驱动线182中的针对该相位差检测像素的行中的相位差检测像素190形成的线rst2。从垂直驱动部184向线rst2提供作为驱动信号的复位信号。垂直驱动部184在新接通传输信号之前接通复位信号。

148.当接通输入至栅电极193a的复位信号时,复位晶体管193将传输到fd 192的电荷放电到电源电极197,并且使fd 192的电位复位。

149.在电源电极197和垂直信号线183之间,放大晶体管194和选择晶体管195串联连接。放大晶体管194的栅电极194a连接至fd 192,放大晶体管194利用电源电极197将与fd 192的电位对应的像素信号输出至选择晶体管195。

150.选择晶体管195的栅电极195a连接至与相位差检测像素190的行对应的像素驱动线182中的针对该行中的相位差检测像素190形成的线sel2。从垂直驱动部184向线sel2提供作为驱动信号的选择信号。垂直驱动部184在接通传输信号之后接通复位信号之前接通选择信号。

151.当接通输入至栅电极195a的选择信号时,选择晶体管195经由垂直信号线183将从放大晶体管194输出的像素信号提供到列处理部185。

152.如上所述,在cmos图像传感器180中,2(水平)

×

2(垂直)个分割像素191之间共用一个fd 192。于是,在各个分割像素191的pd 201中蓄积的电荷按照分割像素191-1和分割像素191-2的顺序以相位差检测像素190的行为单位从顶部顺序地传输到fd 192。

153.相位差检测像素的结构例

154.图9是示出了图8所示的相位差检测像素190的结构例的如从cmos图像传感器180的前表面侧观察到的图。图10是沿着图9的线a-a'、线b-b'和线c-c'获得的断面图。图11是沿着图9的线d-d'和线e-e'获得的断面图。

155.如图9所示,将作为相位差检测像素190的阱的p型杂质210分割为p型杂质211-1和p型杂质211-2。如图10和图11所示,在p型杂质211-1中形成有pd 201-1,在p型杂质211-2中形成有pd 201-2。需要指出的是,在以下说明中,当无需特别区分p型杂质211-1和p型杂质211-2时,将它们统称为p型杂质211。

156.如图9和图10所示,在同一相位差检测像素190中,在p型杂质211-1和p型杂质211-2之间形成有分割像素分离壁221。如图10所示,分割像素分离壁221通过从cmos图像传感器180的前表面形成的前表面沟槽221a和从背面形成的背面沟槽221b之间的接触形成。

157.需要指出的是,在cmos图像传感器180的前表面上的同一相位差检测像素190中的相邻p型杂质211之间的区域中,在形成fd 192的区域中以及与fd 192相对的垂直方向上的端部中未形成前表面沟槽211a。也就是说,分割像素分离壁221通过在前表面沟槽221a和背面沟槽221b之间的接触形成,其中,在同一相位差检测像素190中的相邻p型杂质211之间的前表面上的区域中,在除fd 192的区域以及与fd 192相对的垂直方向上的端部以外的区域中形成有该前表面沟槽,并且在p型杂质211之间的背面的整个区域中形成有该背面沟槽。

158.另外,如图10所示,在分割像素分离壁221的与fd 192相对的垂直方向上的端部的前表面侧,形成有具有深度电位的杂质212。因此,在pd 201-1和pd 201-2的一者中蓄积的电荷溢出的情况下,电荷可以容易地通过图10所示的路径s1经由杂质212泄漏至其他pd。

159.跨过相位差检测像素190,在垂直方向上彼此相邻的p型杂质211之间形成有像素

分离壁222,并且在水平方向上彼此相邻的p型杂质211之间形成有像素分离壁223。

160.像素分离壁222包括夹持n型杂质224~228和p型杂质229的两个前表面沟槽222a和背面沟槽222b。背面沟槽222b在与n型杂质224~228和p型杂质229对应且与两个前表面沟槽222a的位置不同的位置处形成。

161.n型杂质224连接至电源电极197,并构成放大晶体管194的漏极。n型杂质225构成放大晶体管194的源极和选择晶体管195的漏极。n型杂质226连接至垂直信号线183,并构成选择晶体管195的源极。

162.n型杂质227连接至fd 192,并构成复位晶体管193的源极。n型杂质228连接至电源电极197,并构成复位晶体管193的漏极。p型杂质229为连接至阱电极198的阱。

163.栅电极202a、栅电极193a和栅电极195a连接至在cmos图像传感器180的前表面上形成的配线层230中设置的像素驱动线182。fd 192连接至栅电极194a。

164.另外,在p型杂质210的背面侧形成有对应相位差检测像素190的红色(r)、绿色(g)和蓝色(b)滤色器231,在滤色器231的外侧形成有片上透镜232。

165.pd 201-1接收经由片上透镜232和滤色器231从图9右侧的背面侧入射的光,并对接收的光进行光电转换。另外,pd 201-2接收经由片上透镜232和滤色器231从图9左侧的背面侧入射的光,并对接收的光进行光电转换。

166.因此,从分割像素191-1读取的像素信号与从相位差检测像素190的图9中的右侧入射的光相对应,并且从分割像素191-2读取的像素信号与从相位差检测像素190的图9中的左侧入射的光相对应。因此,信号处理部188能够基于从分割像素191-1和分割像素191-2读取的像素信号之间的差异来检测水平方向上的相位并进行像面相位差af等。

167.如上所述,在分割像素分离壁221中的fd 192的区域中,未形成前表面沟槽221a。因此,在pd 201中蓄积的电荷溢出的情况下,溢出的电荷会通过图10所示的路径s2经由p型杂质211泄漏到fd 192中。然而,由于在从pd 201传输电荷之前将fd 192复位,因此从pd 201向fd 192泄漏电荷对成像特性的影响较小。

168.另一方面,由于在像素分离壁223中前表面沟槽223a和背面沟槽223b彼此接触,因此,跨过相位差检测像素190相邻的pd 201被完全电切断。因此,即使在pd 201中蓄积的电荷溢出的情况下,也不会发生电荷泄漏至与pd 201跨过相位差检测像素190相邻的其他pd 201中。

169.另外,如图11所示,在像素分离壁222中,前表面沟槽222a和背面沟槽222b的位置不同,并且前表面沟槽222a和背面沟槽222b未彼此接触。因此,pd 201与n型杂质224~228和p型杂质229未被完全电切断。

170.因此,在蓄积在全体pd 201中的电荷溢出的情况下,也可以将溢出的电荷通过图11所示的路径s3经由p型杂质211和n型杂质224放电到电源电极197。另外,通过图11所示的路径e1,可以将p型杂质211(阱)的电位固定至与p型杂质229连接的阱电极198的电位。

171.需要指出的是,前表面沟槽221a(222a、223a)和背面沟槽221b(222b、223b)中的至少一者的在深度方向上的长度和材料取决于分割像素分离壁221(像素分离壁222、223)的位置而可以不同。另外,像素分离壁222(223)的背面沟槽222b(223b)中的至少一者与分割像素分离壁221的背面沟槽221b的在深度方向上的长度和材料可以不同。

172.cmos图像传感器的操作说明

173.图12~图14分别为说明图7所示的cmos图像传感器180的操作的图。

174.如图12的部分b至图14的部分b所示,在路径s1至s3的屏障中,路径s1的屏障最弱,路径s2的屏障是第二弱,路径s3的屏障最强。

175.信号处理部188基于从分割像素191-1和分割像素191-2顺序地读取的像素信号之间的差异来检测水平方向上的相位,直到蓄积在pd 201-1和pd 201-2的任一者中的电荷溢出为止。然后,信号处理部188基于检测的相位进行像面相位差af。

176.当在pd 201中进一步蓄积电荷并且蓄积在pd 201-1和pd 201-2的任一者中的电荷溢出时,如图12所示,溢出的电荷开始通过具有最弱屏障的路径s1泄漏至另一个pd中(步骤1)。在这种情况下,信号处理部188能够通过将从pd 201-1和pd 201-2顺序地读取的像素信号加和来获取整个相位差检测像素190的像素信号。

177.当在pd 201中进一步蓄积电荷并且蓄积在全体pd 201中的电荷溢出时,如图13所示,溢出的电荷开始通过具有第二弱屏障的路径s2泄漏至fd 192中(步骤2)。由于在从pd 201传输电荷之前将fd 192复位,因此从pd 201向fd 192泄漏电荷对成像特性的影响较小。

178.当在pd 201中进一步蓄积电荷并且从全体pd 201溢出的电荷量变大时,如图14所示,电荷开始通过具有最强屏障的路径s3泄漏至n型杂质224和n型杂质228中(步骤3)。由于n型杂质224和n型杂质228连接至电源电极197,因此从pd 201泄漏的电荷被放电到电源电极197。

179.如上所述,在cmos图像传感器180中,分割像素分离壁221(像素分离壁222、223)由前表面沟槽221a(222a、223a)和背面沟槽221b(222b、223b)形成。

180.因此,在形成有分割像素分离壁221的区域中,在与fd 192相对的垂直方向上的端部和fd 192的区域中,未形成前表面沟槽221a,并且可在与fd 192相对的垂直方向上的端部中形成杂质212。另外,可以使像素分离壁222的前表面沟槽222a和背面沟槽222b的位置相互不对应的方式来使二者的位置移位,并且可以防止前表面沟槽222a和背面沟槽222b彼此接触。

181.这样,可以使pd 201-1和pd 201-2之间的电荷泄漏、从pd 201到fd 192的电荷泄漏、以及在pd 201中蓄积的电荷到电源电极197的放电逐步发生。

182.另外,通过使像素分离壁223的前表面沟槽223a和背面沟槽223b彼此接触,可以使像素分离壁223贯通cmos图像传感器180。因此,可以防止相邻相位差检测像素190之间的电荷泄漏。

183.前表面沟槽223a和背面沟槽223b的深度与宽度的高宽比小于从cmos图像传感器180的前表面和背面中的一者起贯通的贯通沟槽的高宽比。因此,与由贯通沟槽来形成像素分离壁的情况相比,像素分离壁223的形成较容易。

184.另外,通过形成掩模图案来控制前表面沟槽221a~223a的有/无以及位置,可以容易地实现泄漏的这种逐步发生和防止,其中,形成掩模图案为一般的半导体工艺。

185.第三实施方案

186.cmos图像传感器的第三实施方案的相位差检测像素的电路构成例

187.除了相位差检测像素由2(水平)

×

2(垂直)个分割像素形成之外,本公开适用的cmos图像传感器的第三实施方案的构成与图7所示的cmos图像传感器180相同。因此,以下仅对相位差检测像素进行说明。

c'和线d-d'获得的断面图。

201.在图16~18所示的构成中,与图9~11所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

202.如图16所示,将相位差检测像素270的p型杂质210分割为p型杂质301-1~301-4。如图17和图18所示,在p型杂质301-1、p型杂质301-2、p型杂质301-3和p型杂质301-4中分别形成pd 291-1、pd 291-2、pd291-3和pd 291-4。需要指出的是,在以下说明中,当无需特别区分p型杂质301-1~301-4时,将它们统称为p型杂质301。

203.如图16~图18所示,在同一相位差检测像素270中的各p型杂质301之间形成有分割像素分离壁311。如图17和图18所示,分割像素分离壁311通过从cmos图像传感器的前表面形成的前表面沟槽311a和从背面形成的背面沟槽311b之间的接触形成。

204.需要指出的是,在cmos图像传感器的前表面上的同一相位差检测像素270中的相邻p型杂质301之间的区域中,在形成fd 192的区域中以及与fd 192相对的水平方向或垂直方向上的端部中未形成前表面沟槽311a。也就是说,分割像素分离壁311通过在前表面沟槽311a和背面沟槽311b之间的接触形成,其中,在同一相位差检测像素270中的相邻p型杂质301之间的前表面上的区域中,在除fd 192的区域以及与fd 192相对的水平方向或垂直方向上的端部以外的区域中形成有该前表面沟槽,并且在p型杂质301之间的背面的整个区域中形成有该背面沟槽。

205.另外,如图17所示,在垂直方向上彼此相邻的p型杂质301之间的分割像素分离壁311的与fd 192相对的水平方向上的端部的前表面侧,形成有具有深度电位的杂质302。因此,在同一相位差检测像素270中的垂直方向上彼此相邻的pd 291中的一者中蓄积的电荷溢出的情况下,电荷可以容易地通过图17所示的路径s11经由杂质302泄漏至另一个pd。

206.另外,如图18所示,在水平方向上彼此相邻的p型杂质301之间的分割像素分离壁311的与fd 192相对的垂直方向上的端部的前表面侧,形成有浓度与杂质302的浓度不同并且电位比杂质302的电位更深的杂质303。因此,在同一相位差检测像素270中的水平方向上彼此相邻的pd 291中的一者中蓄积的电荷溢出的情况下,电荷可以容易地通过图18所示的路径s12经由杂质303泄漏至另一个pd。

207.像素分离壁222的前表面沟槽222a夹持n型杂质312~315和p型杂质316。n型杂质312连接至fd 192,并构成复位晶体管193的源极。n型杂质313连接至电源电极197,并构成复位晶体管193和放大晶体管194的漏极。

208.n型杂质314构成放大晶体管194的源极和选择晶体管195的漏极。n型杂质315连接至垂直信号线183,并构成选择晶体管195的源极。p型杂质316为连接至阱电极198的阱。如图17所示,栅电极292a连接至在形成于cmos图像传感器中的配线层230中设置的像素驱动线182。

209.pd 291-1和pd 291-2经由片上透镜232和滤色器231分别接收从图16的右下方入射的光和从图16的左下方入射的光,并对光进行光电转换。

210.另外,pd 291-3和pd 291-4经由片上透镜232和滤色器231分别接收从图16的右上方入射的光和从图16的左上方入射的光,并对光进行光电转换。

211.因此,从分割像素271-1读取的像素信号与从相位差检测像素270的图16中的右下方入射的光相对应,从分割像素271-2读取的像素信号与从相位差检测像素270的图16中的

左下方入射的光相对应。另外,从分割像素271-3读取的像素信号与从相位差检测像素270的图16中的右上方入射的光相对应,从分割像素271-4读取的像素信号与从相位差检测像素270的图16中的左上方入射的光相对应。

212.因此,信号处理部188能够基于从分割像素271-1~271-4读取的像素信号之间的差异来检测水平方向和垂直方向上的相位并进行像面相位差af等。

213.如上所述,在分割像素分离壁311中的fd 192的区域中,未形成前表面沟槽311a。因此,在蓄积在全体pd 291中的电荷溢出的情况下,溢出的电荷会通过图18所示的路径s13经由p型杂质301泄漏到fd 192中。然而,由于在从pd 291传输电荷之前将fd 192复位,因此从pd 291向fd 192泄漏电荷对成像特性的影响较小。

214.另一方面,由于在像素分离壁223中前表面沟槽223a和背面沟槽223b彼此接触,因此,跨过相位差检测像素270相邻的pd 291被完全电切断。因此,即使在pd 291中蓄积的电荷溢出的情况下,也不会发生电荷泄漏至与pd 291跨过相位差检测像素270相邻的另一个pd 291中。

215.另外,如图17和图18所示,由于在像素分离壁222中,前表面沟槽222a和背面沟槽222b未彼此接触。因此,pd 291与n型杂质312~315和p型杂质316未被完全电切断。

216.因此,在蓄积在全体pd 291中的电荷溢出的情况下,也可以将溢出的电荷通过图18所示的路径s14经由p型杂质301和n型杂质313放电到电源电极197。

217.需要指出的是,前表面沟槽311a和背面沟槽311b的在深度方向上的长度取决于分割像素分离壁311的位置而可以不同。另外,像素分离壁222(223)的背面沟槽222b(223b)和分割像素分离壁311的背面沟槽311b的在深度方向上的长度可以不同。

218.cmos图像传感器的操作说明

219.图19~图22分别为说明cmos图像传感器的第三实施方案的操作的图。

220.如图19的部分b至图22的部分b所示,在路径s11至s14的屏障中,路径s11的屏障最弱,路径s12的屏障是第二弱,路径s13的屏障是第三弱,路径s14的屏障最强。

221.信号处理部188基于从分割像素271-1~271-4顺序地读取的像素信号之间的差异来检测水平方向和垂直方向上的相位,直到蓄积在pd291-1~291-4的任一者中的电荷溢出为止。然后,信号处理部188基于检测的相位进行像面相位差af。

222.当在pd 291中进一步蓄积电荷并且蓄积在pd 291-1~pd 291-4的任一者中的电荷溢出时,如图19所示,溢出的电荷开始通过具有最弱屏障的路径s11泄漏至在垂直方向上相邻的pd 291中(步骤11)。

223.在这种情况下,信号处理部188能够通过将从在垂直方向上彼此相邻的pd 291读取的像素信号加和来获取当将相位差检测像素270在水平方向上分割时的左侧区域和右侧区域的像素信号。因此,信号处理部188基于左侧区域的像素信号和右侧区域的像素信号之间的差异来检测水平方向上的相位,并且基于该相位来进行像面相位差af。

224.当在pd 291中进一步蓄积电荷并且蓄积在左侧全体pd 291和右侧全体pd 291的任一者中的电荷溢出时,如图20所示,溢出的电荷开始通过具有第二弱屏障的路径s12泄漏至在水平方向上相邻的pd 291中(步骤12)。在这种情况下,信号处理部188能够通过将从所有pd 291读取的像素信号加和来获取整个相位差检测像素270的像素信号。

225.当在pd 291中进一步蓄积电荷并且蓄积在全体pd 291中的电荷溢出时,如图21所

示,溢出的电荷开始通过具有第三弱屏障的路径s13泄漏至fd 192中(步骤13)。由于在从pd 291传输电荷之前将fd 192复位,因此从pd 291向fd 192泄漏电荷对成像特性的影响较小。

226.当在pd 291中进一步蓄积电荷并且从全体pd 291溢出的电荷量变大时,如图22所示,电荷开始通过具有最强屏障的路径s14泄漏至n型杂质313中(步骤14)。由于n型杂质313连接至电源电极197,因此从pd 291泄漏的电荷被放电到电源电极197。

227.如上所述,在cmos图像传感器的第三实施方案中,分割像素分离壁311由前表面沟槽311a和背面沟槽311b形成。因此,在形成有分割像素分离壁311的区域中,在与fd 192相对的水平方向或垂直方向上的端部和fd 192的区域中,未形成前表面沟槽311a,并且在水平方向上的端部中可以形成有杂质302,在垂直方向上的端部中可以形成有电位比杂质302的电位更深的杂质303。这样,可以使在垂直方向上彼此相邻的pd之间的电荷泄漏和在水平方向上彼此相邻的pd之间的电荷泄漏逐步发生。

228.相位差检测像素的第二结构例

229.图23是图15所示的相位差检测像素270的第二结构例的沿着图16的线b-b'和线c-c'获得的断面图。

230.在图23所示的构成中,与图16~18所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

231.图23所示的相位差检测像素270的结构与图16~18所示的结构的不同之处在于:代替杂质302和杂质303而设置了杂质321,并且新设置了前表面沟槽322和前表面沟槽323。在图23所示的相位差检测像素270中,路径s11和路径s12的屏障的强度不由杂质的浓度控制,而是由前表面沟槽322和前表面沟槽323控制。

232.具体地,在图23所示的相位差检测像素270中,在分割像素分离壁311的与fd 192相对的水平方向或垂直方向上的端部的前表面侧形成有具有相同杂质浓度的杂质321。另外,在水平方向上的端部的前表面侧形成有深度方向上的长度比前表面沟槽311a短的前表面沟槽322。在垂直方向上的端部的前表面侧形成有深度方向上的长度比前表面沟槽322长但比前表面沟槽311a短的前表面沟槽323。

233.因此,前表面沟槽322和背面沟槽311b未彼此接触,前表面沟槽323和背面沟槽311b未彼此接触。前表面沟槽322和背面沟槽311b之间的距离大于前表面沟槽323和背面沟槽311b之间的距离。因此,同一相位差检测像素270中的pd 291未被电切断,并且路径s11的屏障比路径s12的屏障弱。

234.相位差检测像素的第三结构例

235.图24是图15所示的相位差检测像素270的第三结构例的沿着图16的线e-e'获得的断面图。

236.在图24所示的构成中,与图16~18所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

237.图24所示的相位差检测像素270的结构与图16~18所示的结构的不同之处在于:分割像素分离壁311、滤色器231和片上透镜232在相位差检测像素270中的位置取决于相位差检测像素270在像素区域181上的位置而不同。

238.也就是说,一般地,在cmos图像传感器的视角中心与视角端部之间,来自片上透镜的光的入射角不同。因此,在端部处的像素中,光不能充分入射到pd中,并且像素信号减少

了。

239.因此,在图24所示的相位差检测像素270中,分割像素分离壁311、滤色器231和片上透镜232在相位差检测像素270中的位置取决于相位差检测像素270在像素区域181上的位置而改变。

240.具体地,在相位差检测像素270在像素区域181上的位置是cmos图像传感器的视角中心的情况下,如图24的部分a所示,以使p型杂质210的中心居中的方式配置滤色器231和片上透镜232。另外,分割像素分离壁311在p型杂质210的水平方向或垂直方向上的中心处形成。

241.另一方面,在相位差检测像素270在像素区域181上的位置是cmos图像传感器的视角端部的情况下,如图24的部分b所示,将滤色器231和片上透镜232的中心配置成从p型杂质210的中心偏移。另外,分割像素分离壁311在从p型杂质210的水平方向或垂直方向上的中心偏移的位置处形成。也就是说,将p型杂质210不均等地分割为p型杂质301-1~301-4。在图24所示的示例中,pd 291的尺寸取决于p型杂质301的尺寸而不同。

242.这样,可以进行使相位差检测像素270的光学中心更靠近相位差检测像素270的中心的光瞳校正。因此,可以减少取决于相位差检测像素270在像素区域181上的位置而产生的像素信号之间的差异。另外,由于不仅滤色器231和片上透镜232的位置改变了,而且分割像素分离壁311的位置也改变了,因此即使在视角端部处的入射角大的情况下也可以减小像素信号之间的差异。

243.需要指出的是,在图24的示例中,虽然滤色器231和片上透镜232的位置以及分割像素分离壁311的位置取决于相位差检测像素270在像素区域181上的位置而改变,但是可以仅改变它们中一者的位置。

244.相位差检测像素的第四结构例

245.图25是在cmos图像传感器的第三实施方案的视角端部处的相位差检测像素270的第四结构例的沿着图16的线e-e'获得的断面图。

246.在图25所示的构成中,与图24所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

247.图25所示的相位差检测像素270的结构与图24所示的结构的不同之处在于:不论p型杂质301的尺寸如何,pd 291的尺寸都恒定。

248.具体地,在图25所示的相位差检测像素270中,在相位差检测像素270的边界侧形成有具有与p型杂质301的最小尺寸对应的尺寸的pd291。因此,每个pd 291的尺寸都相同,并且蓄积在每个分割像素271中的电荷的饱和量都相同。

249.相位差检测像素的第四结构例的制造方法

250.图26是说明图25所示的相位差检测像素270的pd 291的制造方法的图。

251.如图26的部分a所示,首先,在p型杂质210中以与相位差检测像素270的尺寸对应的间隔形成前表面沟槽223a。另外,取决于具有作为与其他相邻相位差检测像素270的边界的两个相邻前表面沟槽223a的相位差检测像素270在像素区域181上的位置,在两个前表面沟槽223a之间的位置处形成前表面沟槽311a。

252.接着,如图26的部分b所示,以使得前表面沟槽223a的中心居中的方式形成与对应于跨过相位差检测像素270相邻的两个分割像素271的量的pd 291相对应的图案。然后,通

过根据形成的图案注入n型杂质,形成与跨过相位差检测像素270相邻的两个分割像素271对应的量的pd291。

253.最后,如图26的部分c所示,以与前表面沟槽223a接触的方式形成背面沟槽223b。因此,将与两个相邻的分割像素271对应的量的pd 291进行分割,并且在像素分离壁223侧(即,相位差检测像素270的边界侧)形成每个分割像素271的pd 291。

254.另外,以与前表面沟槽311a接触的方式形成背面沟槽311b,在与相位差检测像素270在像素区域181上的位置对应的位置处形成滤色器231和片上透镜232。

255.如上所述,在图26的制造方法中,一旦形成与两个分割像素271对应的量的pd 291,就通过像素分离壁223将与两个分割像素271对应的量的pd 291分割为每个分割像素271的pd 291。因此,与分别形成每个分割像素271的pd 291的情况相比,在形成pd 291时的图案形成可以容易地进行。

256.另一方面,在分别形成各个分割像素271的pd 291的情况下,需要形成与该pd 291对应的图案,该pd具有与小于正常尺寸的p型杂质301的最小尺寸相对应的的尺寸。因此,在形成该pd 291时的图案形成的难度很大。

257.相位差检测像素的第五结构例

258.图27是在本公开适用的cmos图像传感器的第三实施方案的视角端部处的相位差检测像素270的第五结构例的沿着图16的线e-e'获得的断面图。

259.在图27所示的构成中,与图25所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

260.图27所示的相位差检测像素270的结构与图25所示的结构的不同之处在于:不论相位差检测像素270在像素区域181上的位置如何,前表面沟槽311a都形成在相位差检测像素270的中心处;pd 291在前表面侧的尺寸大于在背面侧的尺寸,并且pd 291在前表面侧的电位比背面侧的电位更深。

261.具体地,在图27所示的相位差检测像素270中,背面沟槽311b的位置取决于相位差检测像素270在像素区域181上的位置而不同。另一方面,不论相位差检测像素270在像素区域181上的位置如何,前表面沟槽311a的位置都在相位差检测像素270的中心处形成。

262.因此,如图27所示,在视角端部处的相位差检测像素270中,前表面沟槽311a和背面沟槽311b的位置不同,并且前表面沟槽311a和背面沟槽311b未彼此接触。

263.另外,pd 291的背面侧的水平方向和垂直方向上的尺寸分别为与p型杂质301的水平方向和垂直方向上的最小尺寸对应的尺寸。另一方面,pd 291的前表面侧的水平方向和垂直方向上的尺寸分别对应于相位差检测像素270的p型杂质210的水平方向和垂直方向上的尺寸的一半尺寸。所有pd 291的尺寸相同。另外,pd 291的前表面侧的电位比背面侧的电位更深。

264.如上所述,在图27所示的相位差检测像素270中,不论相位差检测像素270在像素区域181上的位置如何,前表面沟槽311a都在相位差检测像素270的中心处形成。因此,可以将pd 291的前表面侧的水平方向和垂直方向上的尺寸分别制成与相位差检测像素270的p型杂质210的水平方向和垂直方向上的一半尺寸对应的尺寸。因此,与图26的情况相比,pd 291的尺寸变得更大,并且在pd 291中可蓄积的电荷量增加。

265.另外,由于pd 291的前表面侧的尺寸足够大并且电位较深,因此pd 291的饱和电

荷量较大。

266.相位差检测像素的第五结构例的制造方法

267.图28和图29分别为说明图27所示的相位差检测像素270的pd 291的制造方法的图。

268.如图28的部分a所示,首先,在p型杂质210中以与相位差检测像素270的尺寸对应的间隔形成前表面沟槽223a。另外,在两个相邻前表面沟槽223a之间的中心处形成前表面沟槽311a。

269.接着,如图28的部分b所示,以使前表面沟槽223a的中心居中的方式形成与对应于跨过相位差检测像素270相邻的两个分割像素271的量的pd 291的背面侧对应的图案。然后,通过根据形成的图案将n型杂质注入至背面侧,形成与跨过相位差检测像素270相邻的两个分割像素271的量对应的pd 291的背面侧。

270.然后,如图29的部分a所示,形成与每个分割像素271的pd 291的前表面侧对应的图案。然后,通过根据形成的图案将n型杂质注入至前表面侧,以与对应于两个相邻的分割像素271的量的pd 291的背面侧连接的方式形成与分割像素271对应的每个分割像素271的pd 291的前表面侧。

271.最后,如图29的部分b所示,以与前表面沟槽223a接触的方式形成背面沟槽223b。因此,将与两个相邻的分割像素271对应的量的pd 291的背面侧进行分割,并且在像素分离壁223侧(即,相位差检测像素270的边界侧)形成每个分割像素271的pd 291的背面侧。

272.另外,取决于具有作为与其他相邻相位差检测像素270的边界的两个相邻前表面沟槽223a的相位差检测像素270在像素区域181上的位置而形成背面沟槽311b。另外,在与相位差检测像素270的像素区域181上的位置对应的位置处形成滤色器231和片上透镜232。

273.如上所述,在图28和图29所示的制造方法中,一旦形成与两个分割像素271对应的量的pd 291的背面侧,就通过像素分离壁223将与两个分割像素271对应的量的pd 291的背面侧分割为每个分割像素271的pd 291的背面侧。因此,与图26的情况相同,与分别形成每个分割像素271的pd 291的背面侧的情况相比,在形成pd 291的背面侧时的图案形成可以容易地进行。

274.需要指出的是,尽管在图27所示的相位差检测像素270中形成有前表面沟槽311a,但是前表面沟槽311a不是必须形成。

275.相位差检测像素的第六结构例

276.图30和图31分别为示出了图15所示的相位差检测像素270的第六结构例的图。

277.在图30和图31所示的构成中,与图16~18所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

278.图30和图31所示的相位差检测像素270的结构与图16~18所示的结构的不同之处在于:像素分离壁222由夹持n型杂质312~315和p型杂质316的两个前表面沟槽222a和分别与两个前表面沟槽222a接触的两个背面沟槽222b形成,并且p型杂质210连接至阱电极198。

279.图30的部分a和图30的部分b是分别示出了相位差检测像素270的如从cmos图像传感器的前表面侧和背面侧观察到的图。图31的部分a和图31的部分b分别为沿着图30的线a-a'和b-b'获得的断面图。

280.在图30和图31所示的相位差检测像素270中,像素分离壁222由夹持n型杂质312~

315和p型杂质316的两个前表面沟槽222a以及分别与两个前表面沟槽222a接触的两个背面沟槽222b形成。因此,可以将复位晶体管193、放大晶体管194、选择晶体管195、电源电极197和阱电极198与p型杂质210完全电分离。

281.因此,可以将电源电极197与pd 291分离开。另外,可以抑制因从pd 291向复位晶体管193、放大晶体管194、选择晶体管195、电源电极197或阱电极198泄漏电荷而引起的成像特性劣化。需要指出的是,由于p型杂质210直接连接至阱电极198,因此可以将p型杂质210的电位固定至阱电极198的电位。

282.另外,在将金属或透射率低的材料用于前表面沟槽222a和背面沟槽222b的情况下,也可以将复位晶体管193、放大晶体管194、选择晶体管195、电源电极197和阱电极198与p型杂质210完全光学分离。

283.相位差检测像素的第七结构例

284.图32和图33分别为示出了图15所示的相位差检测像素270的第七结构例的图。

285.在图32和图33所示的构成中,与图16~18所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

286.图32和图33所示的相位差检测像素270的结构与图16~18所示的结构的不同之处在于:代替像素分离壁222而形成了像素分离壁351,并且新形成了前表面沟槽352和虚拟前表面沟槽353。

287.图32的部分a和图32的部分b是示出了相位差检测像素270的如从cmos图像传感器的前表面侧和背面侧观察到的图。图33的部分a和图33的部分b分别为沿着图32的部分a的线a-a'和b-b'获得的断面图。

288.在图32和图33所示的相位差检测像素270中,跨过相位差检测像素270在垂直方向上相邻的p型杂质301之间形成有像素分离壁351。像素分离壁351通过前表面沟槽351a和背面沟槽351b之间的接触形成。因此,可以防止跨过相位差检测像素270在垂直方向上相邻的pd 291之间的电荷泄漏。

289.另外,以使n型杂质312~315和p型杂质316夹持在前表面沟槽352和前表面沟槽351a之间的方式形成前表面沟槽352(电极沟槽)。另外,在相对于最靠近前表面沟槽352的分割像素分离壁311与前表面沟槽352对称的位置处形成有虚拟前表面沟槽353。因此,可以使得每个pd 291的尺寸制得相同。

290.也就是说,在形成有前表面沟槽352的p型杂质301中,在前表面沟槽352的区域中不能形成pd 291。因此,形成有前表面沟槽352的p型杂质301中形成的pd 291的尺寸小于未形成前表面沟槽352的p型杂质301中形成的pd 291的尺寸

291.因此,在图32和图33所示的相位差检测像素270中,在未形成前表面沟槽352的p型杂质301中,在与前表面沟槽352对应的位置处形成有虚拟前表面沟槽353。因此,在每个p型杂质301中形成的pd 291的尺寸都相同,而与前表面沟槽352的有/无无关。另外,pd 291形状具有对称性。

292.另外,由于可以在p型杂质301中的形成有前表面沟槽352或前表面沟槽353的区域的背面侧形成pd 291,因此pd 291的开口率较大。因此,灵敏度良好。

293.相位差检测像素的第八结构例

294.图34和图35分别为示出了图15所示的相位差检测像素270的第八结构例的图。

295.在图34和图35所示的构成中,与图32和图33所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

296.图34和图35所示的相位差检测像素270的结构与图32和图33所示的结构的不同之处在于:代替前表面沟槽352而形成了前表面沟槽371,并且未形成前表面沟槽353。

297.图34的部分a和图34的部分b分别是示出了相位差检测像素270的如从cmos图像传感器的前表面侧和背面侧观察到的图。图35的部分a和图35的部分b分别为沿着图34的部分a的线a-a'和b-b'获得的断面图。

298.在图34和图35所示相位差检测像素270中,以使n型杂质312~315和p型杂质316夹持在前表面沟槽371和前表面沟槽351a之间的方式形成前表面沟槽371(电极沟槽)。前表面沟槽371的深度方向上的长度充分小于前表面沟槽351a的长度。

299.因此,即使在p型杂质301中形成前表面沟槽371的情况下,也可以在前表面侧上的整个区域中形成pd 291。因此,不论前表面沟槽371的有/无如何,均可以使得形成在每个p型杂质301中的pd 291的尺寸制得相同。另外,可以使得pd 291的尺寸制得充分大。

300.需要指出的是,前表面沟槽371可以由例如cion、sti、ii分离等来形成。

301.相位差检测像素的第九结构例

302.图36为示出了图15所示的相位差检测像素270的第九结构例的图。

303.在图36所示的构成中,与图32和图33所示的构成相同的构成用相同的附图标记表示。适当地省略重复说明。

304.图36所示的相位差检测像素270的结构与图32和图33所示的结构的不同之处在于:相邻相位差检测像素270的尺寸不同。

305.图36的部分a是示出了3(水平)

×

3(垂直)个相位差检测像素270的如从cmos图像传感器的前表面侧观察到的图。图36的部分b是沿着图36的部分a中的线a-a'获得的断面图。需要指出的是,在图36的部分a中,为便于说明示出了形成于背面侧上的片上透镜232。

306.在图36中,具有绿色滤色器231的相位差检测像素270包括其本身的以及与该相位差检测像素270相邻的具有蓝色或红色滤色器231的相位差检测像素270的n型杂质312~315和p型杂质316。因此,在构成具有绿色滤色器231的相位差检测像素270的所有p型杂质301中,形成有该相位差检测像素270或与该相位差检测像素相邻的相位差检测像素270的前表面沟槽352、n型杂质312~315和p型杂质316。

307.因此,在所有p型杂质301中,在前表面侧的前表面沟槽352的区域中未形成pd 291,并且在每个p型杂质301中形成的pd 291的尺寸都相同。另外,pd 291形状具有对称性。

308.另一方面,具有蓝色或红色滤色器231的相位差检测像素270不包括n型杂质312~315和p型杂质316。因此,在构成具有蓝色或红色滤色器231的相位差检测像素270的所有p型杂质301中,未形成前表面沟槽352。

309.因此,在所有p型杂质301中,可以在前表面侧的整个区域上形成pd 291,并且在每个p型杂质301中形成的pd 291的尺寸都相同。另外,pd 291形状具有对称性。

310.与具有红色或蓝色滤色器231的相位差检测像素270的pd 291的尺寸相比,具有绿色滤色器231的相位差检测像素270的pd 291的尺寸可以增大,并提高了灵敏度。

311.因此,例如,通过获取仅针对具有高灵敏度和绿色滤色器231的多个相位差检测像素270的具有高sn比的像素信号,可以获取具有宽的动态范围的彩色图像。具体地,通过将

从具有绿色滤色器的相位差检测像素270的具有大的sn比的像素信号获取的具有宽的动态范围的亮度信息和通过处理另一个相位差检测像素270的颜色信息而获取的颜色信息进行组合,可以获取具有宽的动态范围的彩色图像。

312.需要指出的是,在图36示出的示例中,虽然在与各相位差检测像素270对应的前表面上的区域中形成了滤色器231和片上透镜232,但是在所有相位差检测像素270中,滤色器231和片上透镜232的尺寸可以相同。

313.构成上述一个像素分离壁111(112、113、222、223、351)或分割像素分离壁221(311)的前表面沟槽111a(112a、113a、221a、222a、223a、311a、322、323、351a)和背面沟槽111b(112b、113b、221b、222b、223b、311b、351b)的材料或结构可以相同或不同。

314.另外,构成像素分离壁111(112、113、222、223、351)的前表面沟槽111a(112a、113a、222a、223a、351a)和背面沟槽111b(112b、113b、222b、223b、351b)的材料或结构可以与构成分割像素分离壁221(311)的前表面沟槽221a(311a、322、323)和背面沟槽221b(311b)的材料或结构相同或不同。材料或结构可以由光的入射角、像素71(相位差检测像素190、270)的尺寸等确定。例如,背面沟槽223b和背面沟槽311b的材料可以具有不同的折射率等。

315.另外,例如,如图37所示,具有不同颜色滤色器231的相邻相位差检测像素270的pd 291之间的背面沟槽223b可以由金属382形成。在背面沟槽223b由诸如金属382和杂质掺杂的poly等的导体形成的情况下,为了防止导体和半导体基板(p型杂质301)短路,在导体和半导体基板(p型杂质301)之间形成有诸如氧化膜和氮化膜等的绝缘膜381。另一方面,在同一相位差检测像素270中,具有相同颜色滤色器231的pd 291之间的背面沟槽311b可以以比背面沟槽223b更薄的方式由具有高透射率的材料(诸如氧化膜等)形成。

316.需要指出的是,图37的部分a是相位差检测像素270的沿着图16的线e-e'获得的断面图。另外,图37的部分b是从cmos图像传感器180的背面侧观察到的图。

317.通过如图37所示地构造背面沟槽223b和背面沟槽311b,倾斜地入射并被收集在背面沟槽223b的周边上的光会穿过p型杂质301并被背面沟槽223b的金属382反射。因此,可以抑制混色。另外,收集在背面沟槽311b的周边上的光未被背面沟槽311b反射并入射到pd 291中。因此,可以抑制灵敏度的损失。

318.另一方面,在背面沟槽311b包括类似于背面沟槽223b的金属的情况下,收集在背面沟槽311b的周边上的光被背面沟槽311b反射而不入射到pd 291中。因此,会出现灵敏度的损失。

319.需要指出的是,背面沟槽311b的宽度(在相对于半导体基板的水平方向上的长度)相对于入射光的波长来说足够小。在背面沟槽311b的宽度相对于入射光充分小的情况下,入射到由折射率与作为半导体基板的材料的硅(si)的折射率不同的氧化膜等形成的背面沟槽311b中的光会被衍射,被分割,并入射到每个pd 291中。因此,可以进一步抑制灵敏度的损失。

320.另外,背面沟槽223b可以包含具有低透射率的材料,诸如金属以外的多晶硅等。

321.图38是说明图37所示的背面沟槽223b和背面沟槽311b的制造方法的图。

322.如图38所示,在第一步骤中,在p型杂质210中形成抗蚀剂图案391,对与背面沟槽223b和背面沟槽311b对应的区域中的p型杂质210进行蚀刻。然后,剥离抗蚀剂图案391。

323.在第二步骤中,在p型杂质210中形成诸如氧化膜等的薄绝缘膜392。这里,如上所述,背面沟槽311b比背面沟槽223b薄。也就是说,与蚀刻后的背面沟槽311b对应的区域的宽度比与蚀刻后的背面沟槽223b对应的区域的宽度窄。因此,尽管与蚀刻后的背面沟槽311b对应的区域填充有绝缘膜392,但是与蚀刻后的背面沟槽223b对应的区域未填充绝缘膜392。

324.在第三步骤中,在绝缘膜392上形成金属膜(金属)393。此时,由于与背面沟槽311b对应的区域填充有绝缘膜392,因此,在与背面沟槽311b对应的区域中未埋置金属膜393。然而,由于与背面沟槽223b对应的区域未填充绝缘膜392,因此在该区域中也会埋置金属膜393。

325.在第四步骤中,蚀刻掉多余的金属膜393,并且形成背面沟槽223b的金属382。此后,蚀刻掉多余的氧化膜392,并且形成背面沟槽223b的绝缘膜381和背面沟槽311b。

326.如上所述,由于背面沟槽223b和背面沟槽311b的宽度不同,因此仅通过在形成氧化膜392之后形成金属膜393就可以使背面沟槽223b和背面沟槽311b的材料制得不同。因此,可以抑制因背面沟槽223b和背面沟槽311b的不同材料而导致的制造步骤数量大幅增加。

327.需要指出的是,尽管在图37所示的示例中背面沟槽223b(311b)与前表面沟槽223a(311a)接触,但是如图39的部分a所示,其不是必须与前表面沟槽223a(311a)接触。如图39的部分a所示,背面沟槽223b和背面沟槽311b的在与背面垂直的方向上的长度较短的情况下,制造比较容易,并且对半导体基板的损坏更少。另外,在图39的部分a中,不是必须形成前表面沟槽223a和前表面沟槽311a。

328.另外,如图39的部分b所示,未形成前表面沟槽223a和前表面沟槽311a,并且背面沟槽223b和背面沟槽311b的在深度方向上的长度可以不同。在这种情况下,可以使背面沟槽223b和背面沟槽311b的分离性能制得不同。

329.另外,如图39的部分c所示,不是必须形成前表面沟槽311a。在这种情况下,在同一相位差检测像素270中具有相同颜色滤色器231的pd 291未被完全分离。另外,不仅不是必须形成前表面沟槽223a,而且也不是必须形成前表面沟槽331a。

330.另外,如图39的部分d所示,前表面沟槽223a和前表面沟槽311a由金属形成。在这种情况下,透射过背面沟槽223b(311b)的氧化膜的光被前表面沟槽223a(311a)反射,并且进一步抑制了灵敏度的损失。

331.需要指出的是,在前表面沟槽111a(112a、113a、222a、223a、351a)和背面沟槽111b(112b、113b、222b、223b、351b)由诸如金属系材料和多晶硅等具有低透射率的材料形成的情况下,在前表面沟槽111a(112a、113a、222a、223a、351a)和背面沟槽111b(112b、113b、222b、223b、351b)中设置有用于固定电位的连接部。

332.另外,在第二实施方案和第三实施方案中,虽然在像素区域181中以阵列的方式配置相位差检测像素190(270),但是不仅可以配置相位差检测像素190(270),还可以配置普通像素。

333.例如,如图40所示,可以仅在像素区域181的中心处配置相位差检测像素270,并且可以在其他区域中配置普通像素400。需要指出的是,图40是示出了以像素区域181的中心为中心的3

×

3个像素400或相位差检测像素270的区域的如从cmos图像传感器的前表面侧

观察到的图。

334.在作为普通像素400的阱的p型杂质401中,形成有pd。p型杂质401经由传输晶体管的栅电极402连接至由n型杂质形成的pd 403。pd403经由复位晶体管的栅电极404连接至与电源电极连接的n型杂质405,并连接至放大晶体管的栅电极406。

335.n型杂质405经由放大晶体管的栅电极406连接至形成选择晶体管的漏极的n型杂质407,并且n型杂质407经由选择晶体管的栅电极408连接至与垂直信号线183连接的n型杂质409。另外,在像素400中,形成连接至阱电极的p型杂质410。

336.跨过像素400在垂直方向上相邻的p型杂质401之间,形成夹持fd403、n型杂质405、n型杂质407、n型杂质409和p型杂质410的像素分离壁411。另外,在水平方向上相邻的p型杂质401之间,形成像素分离壁412。

337.例如,像素分离壁411与上述像素分离壁112(222、351)相同地构成,像素分离壁412与上述像素分离壁113(223)相同地构成。

338.相位差检测像素270的读取以pd为单位进行,同时对相位差检测像素270的行中的其他像素400的进行读取。因此,在获取像素400的像素信号时,通过基于每个pd 291的像素信号进行像面相位差af并且对所有pd 291的像素信号进行加和,可以获取全体相位差检测像素270的像素信号。

339.需要指出的是,p型杂质210和p型杂质401的尺寸相同。于是,在相位差检测像素270中,将p型杂质210分割为四个区域,并针对所获得的每个区域形成pd 291。在像素400中,pd在p型杂质210中原样形成。

340.因此,相位差检测像素270的全体pd 291的尺寸小于像素400的pd的尺寸,并且相位差检测像素270中的饱和电荷量小于像素400中的饱和电荷量。因此,相比于像素400,在相位差检测像素270中更容易发生混色,但是可以通过像素分离壁222和像素分离壁223来防止混色。

341.第四实施方案

342.成像装置的实施方案的构成例

343.图41是示出了作为本公开适用的电子设备的成像装置的实施方案的构成例的框图。

344.图41所示的成像装置1000为摄像机、数码相机等。成像装置1000包括透镜组1001、固态成像元件1002、dsp电路1003、帧存储器1004、显示单元1005、记录单元1006、操作单元1007和电源单元1008。dsp电路1003、帧存储器1004、显示单元1005、记录单元1006、操作单元1007和电源单元1008经由总线1009彼此连接。

345.透镜组1001从被摄体捕获入射光(图像光),并将其在固态成像元件1002的成像面上成像。固态成像元件1002由上述cmos图像传感器的第一实施方案至第三实施方案形成。固态成像元件1002将通过透镜组1001在成像面上成像的入射光的量转换为像素单位的电信号,并将该信号作为像素信号提供给dsp电路1003。

346.dsp电路1003对从固态成像元件1002提供的像素信号进行预定的图像处理,将图像处理后的图像信号以帧为单位提供给帧存储器1004,并使帧存储器1004暂时存储图像信号。

347.显示单元1005由诸如液晶面板和有机电致发光(el:electro luminescence)面板

等面板型显示装置构成,并且基于暂时存储于帧存储器1004中的以帧为单位的像素信号来显示图像。

348.记录单元1006由数字通用光盘(dvd:digital versatile disk)、闪速存储器等形成,并且读取和记录暂时存储于帧存储器1004中的以帧为单位的像素信号。

349.操作单元1007基于使用者操作来输出针对成像装置1000的各种功能的操作指令。电源单元1008适当地向dsp电路1003、帧存储器1004、显示单元1005、记录单元1006和操作单元1007供电。

350.本技术适用的电子设备仅需要是将cmos图像传感器用作图像拍摄单元(光电转换单元)的装置,并且除了成像装置1000以外,还可以适用于具有成像功能的便携式终端装置、将cmos图像传感器用作图像读取单元的复印机等。

351.cmos图像传感器的使用例

352.图42是示出了使用上述cmos图像传感器的使用例的图。

353.上述cmos图像传感器可用于以下感测诸如可见光、红外光、紫外光、x射线等光的各种情况中。

354.用于拍摄待鉴赏的图像的装置,诸如数码相机和配备有相机功能的移动设备等

355.用于交通用途的装置,为了诸如自动停止和识别驾驶员状态等安全驾驶的拍摄汽车的前方/后方/周围/内部等的图像的车载相机、监视行进车辆和道路的监视相机和测量车辆之间的距离的距离测量传感器等

356.用于诸如tv、冰箱、空调等家用电器中的装置,用以拍摄使用者的手势并根据该手势进行设备操作

357.用于医疗和保健用途的装置,诸如内窥镜和通过接受红外光而进行血管造影的装置等

358.用于安保用途的装置,诸如用于预防犯罪用途的监视相机和用于个人认证用途的相机等

359.用于美容用途的装置,诸如拍摄皮肤图像的皮肤测量仪器和拍摄头皮图像的显微镜等

360.用于运动用途的装置,诸如用于运动用途的动作相机和可穿戴相机等

361.用于农业用途的装置,诸如用于监测田地和农作物的状态的相机等

362.需要指出的是,这里说明的效果仅仅是示例而非限制性,并且可以提供其他效果。

363.另外,本公开的实施方案不限于上述实施方案,并且在不脱离本公开的本质的情况下可以进行各种修改。

364.例如,虽然在本说明书中阱为p型杂质,但是该阱也可以为n型杂质。

365.另外,第一实施方案中的像素分离壁111~113可以分别与第二实施方案或第三实施方案中的分割像素分离壁221(311)、像素分离壁222(351)和像素分离壁223具有相同的构成。

366.应当理解,本技术可采用如下构成。

367.(1)一种固态成像元件,所述固态成像元件包括:

368.多个像素,所述多个像素对光进行光电转换,所述光经由针对每个像素的不同透镜从所述固态成像元件的背面入射到各像素中;

369.像素分离壁,所述像素分离壁形成在相邻的所述像素之间;以及

370.配线层,所述配线层设置在所述固态成像元件的前表面上,其中,

371.所述像素分离壁包括作为从所述前表面形成的沟槽的前表面沟槽和作为从所述背面形成的沟槽的背面沟槽。

372.(2)根据上述(1)所述的固态成像元件,其中,

373.所述像素分离壁的所述前表面沟槽的至少一部分与所述背面沟槽的至少一部分彼此接触。

374.(3)根据上述(1)或(2)所述的固态成像元件,其中,

375.所述前表面沟槽和所述背面沟槽的在与所述背面垂直的方向上的长度取决于包括对应的所述前表面沟槽和对应的所述背面沟槽的所述像素分离壁的位置而不同。

376.(4)根据上述(1)~(3)中任一项所述的固态成像元件,其中,

377.所述前表面沟槽和所述背面沟槽中的至少一者的材料取决于包括对应的所述前表面沟槽和对应的所述背面沟槽的所述像素分离壁的位置而不同。

378.(5)根据上述(1)~(4)中任一项所述的固态成像元件,其中,

379.在预定方向上相邻的所述像素之间的所述像素分离壁包括两个前表面沟槽和所述背面沟槽,所述两个前表面沟槽夹持阱电极,所述像素不共用浮动扩散,并且所述背面沟槽在所述背面上的位置对应于所述阱电极的位置。

380.(6)根据上述(1)~(4)中任一项所述的固态成像元件,其中,

381.在预定方向上相邻的所述像素之间的所述像素分离壁包括两个前表面沟槽和所述背面沟槽,所述两个前表面沟槽夹持电源电极,所述像素不共用浮动扩散,并且所述背面沟槽在所述背面上的位置对应于所述电源电极的位置。

382.(7)根据上述(1)~(4)中任一项所述的固态成像元件,其中,

383.共用浮动扩散的所述像素之间的所述像素分离壁包括所述前表面沟槽和所述背面沟槽,所述前表面沟槽形成在所述像素之间的所述前表面上的区域中,在所述区域中未形成浮动扩散,所述背面沟槽形成在所述像素之间的所述背面上的整个区域中,并且所述前表面沟槽和所述背面沟槽彼此接触。

384.(8)根据上述(1)所述的固态成像元件,其中,

385.所述多个像素的至少一部分被分割为针对每个像素的多个分割像素,各个所述分割像素包括:光电转换元件,所述光电转换元件对经由同一所述透镜从所述背面入射到各个所述分割像素中的光进行光电转换;并且

386.在相邻的所述分割像素之间形成有分割像素分离壁,所述分割像素分离壁包括作为从所述前表面形成的沟槽的前表面沟槽和作为从所述背面形成的沟槽的背面沟槽。

387.(9)根据上述(8)所述的固态成像元件,其中,

388.所述前表面沟槽和所述背面沟槽的在与所述背面垂直的方向上的长度取决于包括对应的所述前表面沟槽和对应的所述背面沟槽的所述像素分离壁或所述分割像素分离壁的位置而不同。

389.(10)根据上述(8)或(9)所述的固态成像元件,其中,

390.所述像素分离壁的背面沟槽和所述分割像素分离壁的背面沟槽的在与所述背面垂直的方向上的长度不同。

391.(11)根据上述(8)~(10)中任一项所述的固态成像元件,其中,

392.所述前表面沟槽和所述背面沟槽中的至少一者的材料取决于包括对应的所述前表面沟槽和对应的所述背面沟槽的所述像素分离壁或所述分割像素分离壁的位置而不同。

393.(12)根据上述(8)~(11)中任一项所述的固态成像元件,其中,

394.所述像素分离壁与所述分割像素分离壁的背面沟槽的材料不同。

395.(13)根据上述(8)~(12)中任一项所述的固态成像元件,其中,

396.所述分割像素分离壁的所述前表面沟槽仅在相邻的所述分割像素之间的所述前表面上的区域的一部分区域中形成,所述背面沟槽在相邻的所述分割像素之间的所述背面上的整个区域中形成,

397.所述分割像素分离壁的所述背面沟槽和所述前表面沟槽彼此接触,并且

398.在相邻的所述分割像素之间的所述前表面上的区域中形成浮动扩散,在所述区域中未形成所述前表面沟槽。

399.(14)根据上述(8)~(12)中任一项所述的固态成像元件,其中,

400.所述分割像素分离壁的所述前表面沟槽在相邻的所述分割像素之间的所述前表面上的区域中形成,在所述区域中未形成浮动扩散,所述背面沟槽在相邻的所述分割像素之间的所述背面上的整个区域中形成,

401.所述分割像素分离壁的所述前表面沟槽的一部分与所述背面沟槽彼此接触,并且

402.所述分割像素分离壁的所述前表面沟槽的另一部分的在与所述背面垂直的方向上的长度短于所述前表面沟槽的一部分的长度。

403.(15)根据上述(8)~(14)中任一项所述的固态成像元件,其中,

404.在预定方向上相邻的所述像素之间的所述像素分离壁包括两个前表面沟槽和两个背面沟槽,所述两个前表面沟槽夹持电源电极,所述两个背面沟槽与对应的所述前表面沟槽接触。

405.(16)根据上述(8)~(14)中任一项所述的固态成像元件,还包括:

406.电极沟槽,其为前表面沟槽,所述前表面沟槽形成为将电源电极夹持在所述前表面沟槽本身和在预定方向上相邻的所述像素之间的所述像素分离壁的所述前表面沟槽之间;以及

407.虚拟沟槽,其为虚拟前表面沟槽,所述虚拟前表面沟槽在相对于最靠近所述电极沟槽的所述分割像素分离壁与所述电极沟槽对称的位置处形成,其中,

408.所述前表面沟槽与所述背面沟槽接触,以形成所述像素分离壁。

409.(17)根据上述(8)~(16)中任一项所述的固态成像元件,其中,

410.在形成有所述分割像素分离壁的所述像素中的所述分割像素分离壁的位置取决于所述像素的位置而不同。

411.(18)根据上述(17)所述的固态成像元件,其中,

412.在形成有所述分割像素分离壁的所述像素中的所述分割像素分离壁的所述背面沟槽的位置取决于所述像素的位置而不同,

413.在形成有所述分割像素分离壁的所述像素中的所述分割像素分离壁的所述前表面沟槽的位置无论所述像素的位置如何都相同,并且

414.所述分割像素的所述光电转换元件的所述前表面侧的尺寸大于所述背面侧的尺

寸。

415.(19)根据上述(8)~(14)中任一项所述的固态成像元件,还包括:

416.电极沟槽,其为前表面沟槽,所述前表面沟槽形成为将电源电极夹持在所述前表面沟槽本身和在预定方向上相邻的所述像素之间的所述像素分离壁的所述前表面沟槽之间,其中,

417.相邻的所述像素中的一者包括所述像素本身和另一像素的所述电极沟槽,并且

418.所述前表面沟槽与所述背面沟槽接触,以形成所述像素分离壁。

419.(20)一种电子设备,所述电子设备包括:

420.固态成像元件,所述固态成像元件包括:

421.多个像素,所述多个像素对光进行光电转换,所述光经由针对每个像素的不同透镜从所述固态成像元件的背面入射到各像素中;

422.像素分离壁,所述像素分离壁形成在相邻的所述像素之间;以及

423.配线层,所述配线层设置在所述固态成像元件的前表面上,其中,

424.所述像素分离壁包括作为从所述前表面形成的沟槽的前表面沟槽和作为从所述背面形成的沟槽的背面沟槽。

425.附图标记列表

426.50cmos图像传感器

427.71-1~71-4像素

428.72fd

429.76电源电极

430.77阱电极

431.111~113像素分离壁

432.111a~113a前表面沟槽

433.111b~113b背面沟槽

434.119配线层

435.122片上透镜

436.180cmos图像传感器

437.190相位差检测像素

438.191-1、191-2分割像素

439.192fd

440.197电源电极

441.198阱电极

442.201-1、201-2pd

443.221分割像素分离壁

444.221a前表面沟槽

445.221b背面沟槽

446.222、223像素分离壁

447.222a、223a前表面沟槽

448.222b、223b背面沟槽

449.230配线层

450.232片上透镜

451.271-1~271-4像素

452.291-1~291-4pd

453.311分割像素分离壁

454.311a前表面沟槽

455.311b背面沟槽

456.322、323前表面沟槽

457.351像素分离壁

458.351a前表面沟槽

459.352前表面沟槽

460.352、353前表面沟槽

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1