MicroOLED微显示器件的制备方法与流程

micro oled微显示器件的制备方法

技术领域

1.本发明属于micro oled微显示技术领域,具体地说,本发明涉及一种micro oled微显示器件的制备方法。

背景技术:

2.在micro oled的产品中,由于pixel(像素)尺寸较小,oled材料的蒸镀无法适用fmm(精细金属掩膜版),所以oled材料都是整面蒸镀,这样相邻pixel之间的有机层就容易发生电流的相互传输。而有机材料在相邻像素间横向的电流传输,就会导致像素的异常发光,这样就造成串光的现象,导致偏色、色域降低等问题。

技术实现要素:

3.本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提供一种micro oled微显示器件的制备方法,目的是减轻串光。

4.为了实现上述目的,本发明采取的技术方案为:micro oled微显示器件的制备方法,包括步骤:

5.s1、在硅片基底上制备cmos驱动电路形成cmos基板;

6.s2、在cmos基板上制备阳极层;

7.s3、制备像素定义层;

8.s4、在像素定义层上制备无机辅助层,无机辅助层上设置第一凹槽;

9.s5、在像素定义层上制备沟槽,沟槽位于第一凹槽的下方且与第一凹槽连通;

10.s6、在像素定义层和无机辅助层上制备oled膜层,oled膜层在第一凹槽处断开;

11.s7、在oled膜层上制备导电层;

12.s8、制备tfe层;

13.s9、依次制备第一oc层、彩胶层和第二oc层,最后在第二oc层上贴合玻璃盖板。

14.所述第一凹槽的宽度大于所述oled膜层厚度的两倍。

15.所述无机辅助层的材料为sin、sio或sion。

16.所述无机辅助层的厚度为10nm~100nm。

17.所述导电层的材料为金属、金属氧化物或导电银胶。

18.所述导电层的厚度大于所述第一凹槽的宽度的两倍。

19.本发明的micro oled微显示器件的制备方法,通过在pdl顶部设置凹槽结构,使oled层材料蒸镀后是非连续性的,这样就阻断了有机层在两相邻像素间的横向电流传输,减轻串光的效应。

附图说明

20.本说明书包括以下附图,所示内容分别是:

21.图1是阳极层制备结构示意图;

22.图2是像素定义层制备结构示意图;

23.图3是无机辅助层制备结构示意图;

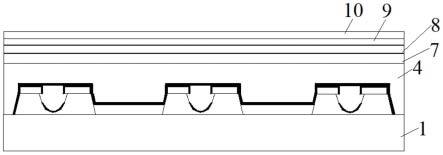

24.图4是沟槽制备结构示意图;

25.图5是oled膜层制备结构示意图;

26.图6是沟槽结构示意图;

27.图7是导电层制备结构示意图;

28.图8是封装层制备结构示意图;

29.图9是黄光及模组膜层制备结构示意图;

30.图中标记为:1、cmos基板;2、阳极层;3、oled膜层;4、封装层;5、无机辅助层;6、导电层;7、第一oc层;8、彩胶层;9、第二oc层;10、玻璃盖板;11、第一凹槽;12、沟槽;13、像素定义层。

具体实施方式

31.下面对照附图,通过对实施例的描述,对本发明的具体实施方式作进一步详细的说明,目的是帮助本领域的技术人员对本发明的构思、技术方案有更完整、准确和深入的理解,并有助于其实施。

32.需要说明的是,在下述的实施方式中,所述的“第一”和“第二”并不代表结构和/或功能上的绝对区分关系,也不代表先后的执行顺序,而仅仅是为了描述的方便。

33.本发明提供了一种micro oled微显示器件的制备方法,包括如下的步骤:

34.s1、在硅片基底上制备cmos驱动电路形成cmos基板1;

35.s2、在cmos基板1上制备阳极层2;

36.s3、制备像素定义层13;

37.s4、在像素定义层13上制备无机辅助层5,无机辅助层5上设置第一凹槽11;

38.s5、在像素定义层13上制备沟槽12,沟槽12位于第一凹槽11的下方且与第一凹槽11连通;

39.s6、在像素定义层13和无机辅助层5上制备oled膜层3,oled膜层3在第一凹槽11处断开;

40.s7、在oled膜层3上制备导电层6;

41.s8、制备tfe层;

42.s9、依次制备第一oc层7、彩胶层8和第二oc层9,最后在第二oc层9上贴合玻璃盖板10。

43.具体地说,如图1所示,在上述步骤s2中,在cmos基板1上制备anode(阳极层2)。

44.如图2所示,在上述步骤s3中,在cmos基板1上制备像素定义层13(pdl),像素定义层13与阳极层2连接。

45.如图3所示,在上述步骤s4中,在像素定义层13上制备一层无机辅助层5,无机辅助层5的材料包括但不限于sin、sio、sion等,无机辅助层5的厚度为10nm~100nm。在无机辅助层5上设置第一凹槽11,第一凹槽11为沿无机辅助层5的厚度方向贯穿设置,也即第一凹槽11延伸至下方的像素定义层13,使像素定义层13露出,第一凹槽11的宽度大于oled膜层3厚度的两倍。

46.如图4所示,在上述步骤s5中,通过刻蚀工艺,在像素定义层13的顶面上制备出沟槽12,沟槽12位于第一凹槽11的下方,沟槽12的宽度大于第一凹槽11的宽度,沟槽12的宽度方向与第一凹槽11的宽度方向相平行,沟槽12的宽度方向上的中点与第一凹槽11的宽度方向上的中点处于与无机辅助层5的厚度方向相平行的同一直线上。也即刻蚀后的像素定义层13与上层的无机辅助层5就形成了一个上窄下宽的凹槽结构,沟槽12与第一凹槽11连通,形成第二凹槽。

47.如图5所示,在上述步骤s6中,通过蒸镀制程制备oled膜层3(空穴注入/传输层、有机发光层、电子注入/传输层、cathode等膜层),oled膜层3覆盖无机辅助层5、阳极层2和沟槽12的部分内壁面,由于pdl上窄下宽的凹槽,就会形成不连续的oled膜层3(不同pixel之间oled膜层3是孤立的),oled膜层3在第一凹槽11处断开。

48.如图7所示,在上述步骤s7中,制备导电层6,导电层6填充第二沟槽12,用来导通不同pixel的cathode。导电层6的材料包括但不限于金属、金属氧化物、导电银胶等,制备方法包括但不限于pvd/dispensor/ijp等,本发明通过在pdl顶部设置凹槽结构,使oled层材料(hil/htl/eml/eil/etl/cathode等)蒸镀后是非连续性的,这样就阻断了有机层在两相邻像素间的横向电流传输,减轻串光的效应。但此pdl结构也导致蒸镀时阴极膜层的连续性也同样被破坏,因此可以在阴极上再镀一整层导电膜层来连接不同像素的阴极。导电层6的厚度要大于第一凹槽11的宽度的两倍。

49.如图8所示,在上述步骤s8中,制备tfe层(封装层4),封装层4覆盖导电层6,封装层4的制备方法包括但不限于ald、pecvd、ijp等,膜层结构为al2o3、tio2、ato、sin、sion、sio、亚克力系有物、环氧树脂系有机物等膜层中的一种或几种之间的任意组合。

50.如图9所示,在上述步骤s9中,在封装层4上依次制备第一oc层7、彩胶层8和第二oc层9,最后在第二oc层9上贴合玻璃盖板10。

51.以上结合附图对本发明进行了示例性描述。显然,本发明具体实现并不受上述方式的限制。只要是采用了本发明的方法构思和技术方案进行的各种非实质性的改进;或未经改进,将本发明的上述构思和技术方案直接应用于其它场合的,均在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1