集成电路装置、半导体基板和测试系统的制作方法

集成电路装置、半导体基板和测试系统

1.相关申请的交叉引用

2.本技术基于并要求2021年4月1日在韩国知识产权局提交的韩国专利申请no.10-2021-0042815的优先权,其主题以引用方式并入本文。

技术领域

3.本发明构思涉及集成电路装置,更具体地,涉及一种集成电路装置、半导体基板以及用于测量集成电路装置或半导体基板的信号的测试系统。

背景技术:

4.随着电子装置的性能快速提升,对包括在电子装置中的半导体装置执行的测试正在变得更复杂。为此,用于测试半导体装置的设备的尺寸正在增大。期望用于更准确地测试各自包括多个集成电路装置的半导体装置的改进技术。

5.作为测试操作的示例,可测量施加到半导体装置的电流。为了感测该电流,除了半导体装置之外,可能需要单独的装置,或者可在半导体装置中安装单独的感测元件。这种测试操作变得昂贵且耗时,并且随着安装越来越多的单独的元件,测量的值中生成误差。

技术实现要素:

6.本发明构思提供一种集成电路装置、半导体基板和包括该集成电路装置的测试系统,其可基于电磁感应测量电压和/或电流而无需单独的装置。

7.根据本发明构思的一方面,提供了一种包括多个层的集成电路装置,该集成电路装置包括:电源端子,其被配置为接受要供应的源电压;电源通孔,其连接至电源端子并穿过多个层中的至少一个;多个感应通孔,其与电源通孔隔开布置并穿过多个层中的至少一个;多条布线,其连接至多个感应通孔中的至少一些的端部,并且被配置为围绕电源通孔与多个感应通孔一起形成以环形形式缠绕的线圈;以及

8.测试端子,其被配置为响应于向电源通孔供应源电压而接受线圈中感应到的电压以输出至集成电路装置的外部。

9.根据本发明构思的另一方面,提供了一种包括重分布集成电路装置的多个焊盘的多个重分布布线层的半导体基板,该半导体基板包括:电源端子,其被配置为接受要供应的源电压;电源通孔,其连接至电源端子并且穿过多个重分布布线层中的至少一个;多个感应通孔,其与电源通孔隔开布置并且穿过多个重分布布线层中的至少一个;多条布线,其连接至多个感应通孔中的至少一些的端部,并且被配置为围绕电源通孔与多个感应通孔一起形成以环形形式缠绕的线圈;以及测试端子,其被配置为响应于向电源通孔供应源电压而接受线圈中感应到的电压以输出到半导体基板外部。

10.根据本发明构思的另一方面,提供了一种包括测试装置和至少一个集成电路装置的测试系统,所述至少一个集成电路装置包括第一集成电路装置,其中,该第一集成电路装置包括:第一端子,其被配置为从测试装置接收第一电压;第一通孔,其连接至第一端子并

穿过多个层中的至少一个;多个第二通孔,其与第一通孔隔开布置并穿过多个层中的至少一个;多条布线,其连接至多个第二通孔中的至少一些的端部并且被配置为围绕第一通孔与多个第二通孔一起形成以环形形式缠绕的线圈;以及第二端子,其被配置为响应于向第一通孔供应第一电压而接受线圈中感应到的电压以输出至测试装置,并且测试装置连接至第二端子并被配置为响应于感应电压来测量供应给第一集成电路装置的信号。

附图说明

11.将从以下结合附图的详细描述更清楚地理解本发明构思的实施例,在附图中:

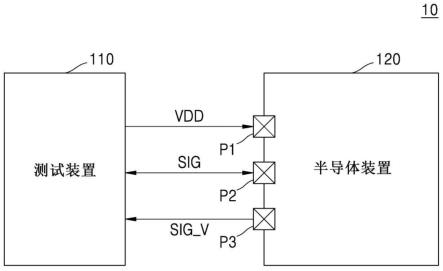

12.图1是示出根据实施例的测试系统的框图;

13.图2a和图2b是示意性地示出根据比较示例的信号测量方法的示图;

14.图3是示意性地示出根据实施例的集成电路装置的截面图;

15.图4是示意性地示出根据实施例的集成电路装置的透视图;

16.图5和图6是示意性地示出根据实施例的在集成电路装置中形成线圈的处理的透视图;

17.图7是示意性地示出根据实施例的集成电路装置的平面图;

18.图8是示出根据实施例的测试系统的框图;

19.图9是示出根据实施例的信号的曲线图;

20.图10是根据实施例的半导体模块的透视图;

21.图11是根据实施例的半导体封装件的截面图;

22.图12是示出根据实施例的制造集成电路装置的方法的流程图。

具体实施方式

23.以下,将参照附图详细地描述实施例。

24.图1是示出根据实施例的测试系统10的框图。

25.参照图1,测试系统10可包括测试装置110和半导体装置120。半导体装置120可以是包括多个集成电路装置或单个集成电路装置的半导体封装件。

26.在实施例中,半导体装置120可用半导体封装件实现,并且半导体封装件可包括基板和安装在基板上的多个集成电路装置。在实施例中,当半导体封装件是存储器装置时,半导体封装件可包括至少一个核心管芯,其包括存储器单元阵列和逻辑管芯。

27.例如,半导体封装件可用层叠封装(pop)、芯片级封装(csp)、叠片包装管芯、晶圆形式管芯、板上芯片(cob)、系统级封装(sip)、多芯片封装(mcp)、晶圆级制造封装(wfp)和晶圆级加工堆叠封装(wsp)来实现,但不限于此。

28.半导体封装件可包括多个连接端子,其可附接到基板的底表面。每个连接端子可包括例如焊球或凸块。每个连接端子可将半导体封装件电连接至外部装置(即,测试装置110)。

29.在实施例中,半导体装置120可被实现为集成电路装置并且可以是封装型集成电路装置。即,集成电路装置可包括诸如焊球或凸块的多个连接端子。集成电路装置可以是半导体芯片或半导体管芯。

30.集成电路装置可包括存储器半导体装置或逻辑半导体装置。逻辑半导体装置可包

括例如中央处理单元(cpu)、图形处理单元(gpu)、控制器、专用集成电路(asic)或应用处理器(ap)。存储器半导体装置可包括例如动态随机存取存储器(ram)(dram)、静态随机存取存储器(sram)、闪存、电可擦除可编程只读存储器(eeprom)、相变随机存取存储器(pram)、磁性随机存取存储器(mram)或电阻随机存取存储器(rram)。

31.半导体装置120可包括多个连接端子,这多个连接端子可包括接收源电压vdd的连接端子、传送和/或接收第一信号sig和第二信号sig_v的连接端子以及没有对其分配功能的不使用(dnu)连接端子或未连接的连接端子。第一信号sig可包括与半导体装置120的操作关联的信号(例如,时钟信号、命令/地址信号和数据信号),第二信号sig_v可包括用于在半导体装置的各种操作条件下测量电压/电流/频率的变化的信号。

32.供应有源电压vdd的连接端子可被指定为电源端子p1,用于传送或接收第一信号sig的端子可被指定为信号端子p2。根据实施例,由半导体装置120生成的第二信号sig_v可通过dnu端子或nc端子输出至测试装置110,并且这种连接端子可被指定为测试端子p3。

33.根据实施例,测试装置110可通过电源端子p1向半导体装置120供应源电压vdd,并且当供应源电压vdd时,测试装置110可通过测试端子p3接收由半导体装置120生成的第二信号sig_v。在实施例中,由半导体装置120生成的第二信号sig_v可包括由半导体装置120基于源电压vdd生成的感应电压。感应电压将是交流(ac)电压。

34.测试装置110可接收供应给半导体装置120的源电压vdd和所接收的第二信号sig_v的感应电压,并且可响应于所接收的源电压vdd和感应电压而测试半导体装置120。在实施例中,测试装置110可连续地接收第二信号sig_v并且可基于第二信号sig_v确定半导体装置120中存在或不存在缺陷。

35.测试装置110可处理从半导体装置120的测试端子p3接收的第二信号sig_v以生成单独的信号,并且可响应于该单独的信号而测试半导体装置120。在实施例中,测试装置110可从半导体装置120获得第二信号sig_v的感应电压,并且可执行感应电压的积分,以获得电流信号(例如,图8的sig_i)。测试装置110可基于电流信号sig_i来预测供应给半导体装置120的电流,并且可监测供应给半导体装置120的电流。

36.罗氏(rogowski)线圈可用于测量供应给半导体装置120的电流并且可形成在半导体装置120中。将在下面参照图5和图6描述在半导体装置120中形成罗氏线圈的处理。

37.根据实施例,可以不需要用于测量半导体装置120中流动的电流的单独的装置(例如,单独的基板),因此,可降低在测试操作中产生的成本。另外,可在不会不利地影响半导体装置120的操作的情况下测量电流,因此,可减小测量误差并且改进这些测量的可靠性。

38.另外,根据实施例,包括在半导体装置120中的连接端子当中的未使用的端子可用作测试端子p3,因此,可获得连续的电流测量值,而无需具有单独的测试功能的端子。

39.图2a和图2b是示意性地示出根据比较示例的信号测量方法的示图。

40.参照图2a和图2b,半导体装置200可包括半导体芯片210、其上安装有半导体芯片210的中介层220、印刷电路板(pcb)240以及向半导体芯片210供电的电源管理集成电路(pmic)230。半导体装置200还可包括多个其它元件(未示出)。

41.pmic 230可通过形成在中介层220和pcb 240中的布线201向半导体芯片210供电。此时,可执行用于响应于供应的源电压vdd而测量在半导体芯片210中流动的电流的测试操作。

42.根据比较示例,电阻器r_shunt可设置在布线201的中心部分,并且在电阻器r_shunt中流动的电流可基于施加到电阻器r_shunt的两端的电压来测量,从而呈现半导体芯片210中流动的可测量电流。详细地,电阻器r_shunt可形成在pmic 230的电源端子p4和半导体芯片(ic)210的电源端子p5之间。在实施例中,电阻器r_shunt可被实现为分流电阻器。

43.在这种情况下,因为电阻器r_shunt设置在布线201的中心部分,所以与由pmic 230供应的电压相比具有降低电平的电压可被供应给半导体芯片210,从而导致半导体装置200的不稳定操作。另外,由于电阻器r_shunt的公差而导致的测量值可能产生误差。

44.图3是示意性地示出根据实施例的集成电路装置300的截面图。图3的集成电路装置300可对应于图1的半导体装置120。

45.参照图3,集成电路装置300可包括半导体管芯310和其上安装有半导体管芯310的基板320。图3示出半导体管芯310安装为倒装芯片接合类型,但安装类型不限于此。另外,在图3中,一个半导体管芯310被示出为安装在基板320上,但包括多个半导体管芯310的半导体管芯堆叠件可安装在基板320上。

46.半导体管芯310可包括芯片主体311和下焊盘312,并且还可包括通孔(未示出)。通孔可穿过半导体管芯310,并且通孔的一端可连接至下焊盘312。通孔可直接连接至下焊盘312,或者可通过布线层(未示出)连接至下焊盘312。多个连接端子313可设置在半导体管芯310下方并且可将半导体管芯310电连接至基板320。

47.基板320可包括基板主体322、设置在基板主体322的顶表面上的基板上焊盘321以及设置在基板主体322的底表面处的基板下焊盘323。将基板上焊盘321电连接至基板下焊盘323的布线结构可设置在基板主体322中。基板下焊盘323可接触基板320的连接端子326。基板320的连接端子326可通过基板下焊盘323、内部布线结构和基板上焊盘321电连接至半导体管芯310的连接端子313。在实施例中,连接端子326可包括焊料凸块并且可将集成电路装置300电连接至外部装置(未示出)。

48.基板320可包括被从外部pmic(未示出)供电的电源端子350、传送或接收信号sig的信号端子340以及未指定的dnu端子330。电源端子350可包括连接至源电压vdd的端子和连接至接地节点的端子。

49.根据实施例,基板320可使用dnu端子330中的至少一个作为测试端子,因此,可测量集成电路装置300中流动的电流而无需单独的装置。当通过电源端子350向集成电路装置300供电时,在以特定形式布置在半导体管芯310和/或基板320上的多个通孔和多条布线中可能出现感应电压。将在下面参照图4至图7描述多个通孔和多条布线布置的形式。

50.在实施例中,多个通孔和多条布线可通过测试端子连接至外部测试装置(例如,测试装置110),以形成闭合电路。在这种情况下,测试端子可配置有至少两个连接端子326。当感应电压通过测试端子输出至集成电路装置300的外部时,测试装置110可响应于感应电压而测量供应给集成电路装置300的电压和/或电流。另外,可获得连续的测量值。

51.图4是示意性地示出根据实施例的集成电路装置的透视图。图4的透视图示意性地示出图3的集成电路装置300的半导体管芯310或基板320的一部分。以下,例如,将描述根据实施例的半导体管芯400,但本发明构思不限于此。

52.半导体管芯400可包括具有堆叠结构的多个层410至430,并且还包括穿过多个层(例如,第一至第三层)410至430中的至少一些的多个通孔450和460。硅通孔(tsv)可形成垂

直穿过作为半导体基板材料的硅的电极并且可提供信号传送路径。例如,通孔450和460中的每一个的一端可连接至形成在第一层410中的焊盘,其另一端可连接至形成在第三层430中的焊盘。

53.连接至电源端子p1并传送源电压vdd的通孔可被指定为电源通孔450,连接至信号端子p2并传送控制和/或数据信号sig的通孔可被指定为信号通孔。根据实施例,随着电流在电源通孔450中流动,在多个通孔中生成感应电压,此时,出现感应电压的通孔可各自被指定为感应通孔460。

54.为了在感应通孔460中出现感应电压,形成包括感应通孔460的闭合电路。该闭合电路可包括多个感应通孔460和连接多个感应通孔460的布线470。根据实施例,如图4中一样,可提供感应通孔460和多条布线470以用于生成感应电压。因此,在半导体管芯400中可出现感应电压。可提供感应通孔460和布线470以配置闭合电路,使得基于源电压vdd的供应而生成感应电压,因此,感应通孔460和布线470的布置不限于图4的例示。

55.在实施例中,多个感应通孔460和多条布线470可被布置为使得围绕电源通孔450实现以环形(toroidal)形式缠绕的线圈。例如,多个感应通孔460和多条布线470可被布置为形成包括电源通孔450作为空气芯的罗氏线圈。例如,可提供至少八个感应通孔,并且这八个感应通孔中的四个可以以交叉配置与电源通孔450隔开特定距离布置。这四个感应通孔可相对于电源通孔450分别在向东方向、向西方向、向南方向和向北方向上设置。因此,靠近电源通孔450的四个感应通孔可形成较小的四边形形状,远离电源通孔450的四个感应通孔可形成更大的四边形形状。

56.当线圈被缠绕时,可配置形成线圈的第一端的感应通孔和形成线圈的第二端的感应通孔。两个感应通孔中的每一个的一端可连接至对应的测试端子。测试端子可连接至集成电路装置外部的测试装置(例如,图1的110)以形成闭合电路中的线圈。

57.当源电压vdd被施加到设置在线圈中心的电源通孔450时,在电源通孔450中可出现电流的变化,因此,在形成在电源通孔450附近的线圈中可感应到电压。可基于感应电压预测在电源通孔450中流动的电流。可通过连接至感应通孔460的测试端子输出感应电压,并且在这种情况下,测试端子可连接至测试装置110,由此测试装置110可连续地测量半导体管芯400中流动的电流而无需单独的装置。

58.图5和图6是示意性地示出根据实施例的在集成电路装置中形成线圈的处理的透视图。图5和图6的透视图示意性地示出图3的集成电路装置300的半导体管芯310或基板320的一部分。以下,作为示例,将描述根据实施例的半导体管芯400,但本发明构思不限于此。

59.参照图5,随着通过电源端子461将电压供应给电源通孔450,可生成在电源通孔450中流动的电流。在图5中,示出电流在从第三层430到第一层410的方向上流动,但电流的方向可以是与之相反的方向。

60.参照图6,当电流在电源通孔450中流动时,可通过由多个感应通孔460和多条布线470形成的线圈生成感应电压。多条布线470中的每一条可形成为将两个感应通孔的端部连接,并且可形成在形成有两个感应通孔的端部的层上。此外,这两个感应通孔的端部可分别形成在不同的层上,并且在这种情况下,两个感应通孔的端部可通过多条布线和单独的通孔彼此连接。

61.例如,第一感应通孔461的一端413可形成线圈的第一端,第二感应通孔462的一端

412可形成线圈的第二端。形成线圈的两端的感应通孔460不限于此。两个不同的感应通孔460可通过布线470彼此连接,因此,可实现以环形形式围绕电源通孔450的周边缠绕的线圈。在实施例中,可形成线圈,其中靠近电源通孔450的四个感应通孔在+z轴方向上缠绕,远离电源通孔450的四个感应通孔在-z轴方向上缠绕。

62.缠绕方向不限于特定方向,并且可形成线圈,其中靠近电源通孔450的四个感应通孔在-z轴方向上缠绕,远离电源通孔450的四个感应通孔在+z轴方向上向内缠绕。

63.第一感应通孔461的一端413和第二感应通孔462的一端412中的每一个可连接至测试端子(未示出),并且测试端子可连接至外部测试装置(例如,图1的110),由此线圈可形成闭合电路。线圈缠绕的方向和/或线圈的起点和终点不受给出的示例性描述限制。

64.图7是示意性地示出根据实施例的集成电路装置的平面图。图7的平面图示意性地示出图3的集成电路装置300的半导体管芯310或基板320。以下,例如,将描述根据实施例的半导体管芯500,但本发明构思不限于此。另外,与以上描述相同或相似的描述作为冗余被省略。

65.参照图7,半导体管芯500可包括十六个感应通孔560。这十六个感应通孔560可布置在八个不同的方向上。例如,可在向东方向、东南方向、向南方向、西南方向、向西方向、西北方向、向北方向和东北方向中的每一个上布置两个感应通孔。因此,靠近电源通孔550的八个通孔可形成较小的八边形形状,远离电源通孔550的八个通孔可形成更大的八边形形状。通过图7的布置形成的线圈可比如图4至图6所示形成的线圈更紧凑。测试端子可连接至十六个感应通孔560中的两个感应通孔560中的每一个的一端,因此,由线圈生成的感应电压可被提供至半导体管芯500的外部。

66.在图7中,常用符号示出+z轴方向、-z轴方向。因此,根据图7的实施例,可形成线圈,其中靠近电源通孔550的八个感应通孔在+z轴方向上缠绕,远离电源通孔550的八个感应通孔在-z轴方向上缠绕。在+z轴方向上形成线圈的感应通孔中的一个感应通孔的一端和在-z轴方向上形成线圈的感应通孔中的一个感应通孔的一端可分别形成线圈的两端。线圈缠绕的方向和/或线圈的起点和终点不受给出的示例性描述限制。

67.另外,用于形成线圈的感应通孔560的数量不限于此。可在八个方向中的两个相邻方向之间的方向上进一步设置感应通孔,并且在这种情况下,可实现比图7更紧凑的线圈。

68.图8是示出根据实施例的测试系统20的框图,图9是示出根据实施例的信号的曲线图。图8的测试系统20可以是图1的测试系统10的实施例。以下,因此,与图1的描述相同或相似的描述作为冗余被省略。

69.参照图8和图9,测试装置110可接收通过测试端子p3从半导体装置120输出的第二信号sig_v(例如,来自形成在半导体装置120中的线圈的感应电压)。第二信号sig_v相对于时间的曲线图如g1所示。

70.测试装置110可包括积分器111,并且积分器111可被实现为各种类型的电路。积分器111对随时间连续接收的第二信号sig_v执行积分,以生成电流信号sig_i。电流信号sig_i相对于时间的曲线图如g2所示。

71.测试装置110可响应于从测试端子p3输出的第二信号sig_v和/或由积分器111生成的电流信号sig_i而对半导体装置120执行测试操作。积分器111可被设置在测试装置110的外部,并且例如可设置在半导体装置120中。在这种情况下,从测试端子p3输出的信号可

以是电流信号sig_i,而非第二信号sig_v的电压信号。

72.图10是根据实施例的半导体模块600的透视图。

73.参照图10,半导体模块600可包括pcb 610、多个半导体封装件620以及多个外部连接端子630。

74.半导体封装件620可对应于上述半导体装置(例如,图1的120)。因此,每个半导体封装件620可通过外部连接端子630中的电源端子被供应源电压vdd,并且可通过内部测试端子621和外部测试端子输出感应电压。

75.在实施例中,半导体模块600可包括存储器模块。例如,半导体模块600可包括双列直插存储器模块(dimm)、小外形dimm(so-dimm)、无缓冲dimm或全缓冲dimm(fb-dimm)。

76.pcb 610可以是其上安装有多个半导体封装件620的基板。pcb610可包括pcb卡、塑料基板或具有不同结构的半导体基板。pcb 610可具有多个金属布线层和多个绝缘层交替地堆叠的结构。

77.半导体封装件620可包括非易失性存储器装置。在实施例中,半导体封装件620可包括nand型闪存。在实施例中,半导体封装件620可包括pram、mram、reram、fram或nor闪存。在实施例中,半导体封装件620可包括诸如dram或sram的易失性存储器装置。

78.多个外部连接端子630可在pcb 610的纵向方向(即,x方向)上在pcb 610下方布置成一行。外部连接端子630可包括接地端子、电源端子和信号端子。信号端子可包括输入地址信号的地址端子、输入命令信号的命令端子、输入时钟信号的时钟端子以及输入或输出数据的数据端子。在实施例中,外部连接端子630可被实现为焊盘、引脚或接线片。

79.另外,外部连接端子630可包括外部连接端子630中未指定输入或输出信号sig的端子(或dnu端子)。多个dnu端子中的至少两个可用作外部测试端子。

80.根据实施例,形成在每个半导体封装件620中的内部测试端子621可连接至形成在pcb 610中的外部测试端子。因此,在不使用诸如中介层的单独装置的情况下,可在半导体模块600外部确定和测量在多个半导体封装件620中的每一个中流动的电流信号sig_i。

81.图11是根据实施例的半导体封装件700的截面图。

82.参照图11,半导体封装件700可包括集成电路装置710和中介层720。集成电路装置710可对应于上述集成电路装置(例如,图3的300),因此,重复的描述作为冗余被省略。中介层720可对集成电路装置710的焊盘进行重分布。

83.中介层720可包括基础基板724、布线(未示出)、多个通孔721和722以及连接端子。基础基板724可包括硅晶圆。布线可形成在基础基板724的顶表面上,并且例如,可具有后端制程(beol)结构。通孔721和722可从基础基板724的顶表面延伸至其底表面,并且可穿过基础基板724。中介层720可通过连接端子723连接至外部基板(例如,pcb)。类似以上描述,中介层720的连接端子723可包括电源端子、信号端子和dnu端子,多个dnu端子中的一些可用作测试端子。

84.集成电路装置710可通过中介层720电连接至外部基板。即,从外部pmic供应的电力可通过中介层720供应给集成电路装置710。中介层720可包括基础基板724中的多个重分布布线层741至743。在这种情况下,中介层720的重分布布线层741至743可对应于上面参照图4至图7描述的多个层410至430。

85.连接至中介层720的电源端子的通孔可被指定为电源通孔722,设置为围绕电源通

孔722形成线圈的多个通孔可被指定为感应通孔721。形成在中介层720中的感应通孔721的布置可与上面参照图4至图7给出的描述类似。在图11中,示出一个电源通孔722和两个感应通孔721,但电源通孔722和感应通孔721的数量仅是示例,并不限于此。

86.多个感应通孔721可围绕电源通孔722形成线圈,并且线圈中感应到的电压可通过测试端子输出至外部。中介层720的测试端子可直接连接至外部测试装置(例如,测试装置110),或者可通过单独的pcb连接至测试装置110。在中介层720的测试端子通过pcb连接至测试装置110的情况下,测试端子可设置在pcb中,因此,可通过测试端子输出感应电压。

87.图12是示出根据实施例的制造集成电路装置的方法的流程图。详细地,图12的流程图示出制造上述集成电路装置(例如,图3的300)的方法。

88.集成电路装置可包括多个各种标准单元,并且每个标准单元提供独特的功能。标准单元可具有符合基于制造集成电路装置的半导体工艺指定的规则的结构,例如,可在与层的堆叠方向垂直的平面上在特定方向上具有特定长度或特定长度的倍数。

89.标准单元库(或单元库)d2可包括关于标准单元的信息(例如,可包括功能信息、特性信息和布局信息),并且可包括关于电源通孔和相对于电源通孔的感应通孔的布置信息。

90.在操作s10中,可执行从电阻器晶体管逻辑(rtl)数据d1生成网表d3的逻辑合成操作。例如,半导体设计工具(例如,逻辑合成工具)可从以诸如verilog和硬件描述语言(vhdl)的硬件描述语言(hdl)撰写的rtl数据d1基于标准单元库d2执行逻辑合成操作,从而生成包括网表或比特流的网表d3。标准单元库d2可包括关于通孔的放置的信息,并且可在逻辑合成过程中基于该信息将标准单元添加到集成电路装置。

91.在操作s20中,可执行从网表d3生成布局数据d4的放置和路由(p&r)操作。如图12所示,p&r操作(s20)可包括多个操作(s21至s23)。在操作s21中,可执行放置标准单元的操作。例如,半导体设计工具(例如,p&r工具)可从网表d3基于标准单元库d2放置多个标准单元。例如,半导体设计单元可基于标准单元库d2放置由网表d3定义的布局。在操作s22中,可执行生成互连件的操作。每个互连件可将输出引脚电连接至输入引脚,例如,可包括至少一个通孔和至少一个导电图案。在操作s23中,可执行生成布局数据d4的操作。例如,布局数据d4可具有诸如图形设计系统i i(gdsi i)的格式,并且可包括关于互连件和标准单元的几何信息。

92.在操作s30中,可执行光学邻近校正(opc)。opc可校正由制造集成电路设计的半导体工艺中所包括的光刻中由光的特性导致的诸如折射的失真,因此,可表示形成具有期望形状的图案的操作。另外,掩模上的图案可通过对布局数据d4应用opc来确定。在一些实施例中,可在操作s30中有限地修改集成电路装置的布局,并且在操作s30中限制性地修改集成电路装置的操作可以是用于优化集成电路装置的结构的后处理,并且可被称为设计抛光。

93.在操作s40中,可执行制造掩模的操作。例如,通过对布局数据d4应用opc,可定义掩模上的图案以用于形成多个层中形成的图案,并且可以定义至少一个掩模(或光掩模)以用于形成可制造的多个层的图案。

94.在操作s50中,可执行制造集成电路装置的操作。例如,可通过使用在操作s40中制造的至少一个掩模将多个层图案化,因此,可制造集成电路装置。如图12所示,操作s50可包括操作s51和操作s52。在操作s51中,可执行前端制程(feol)处理。feol处理可表示在制造

集成电路装置的处理中在基板上形成单独的元件(例如,晶体管、电容器、电阻器等)的处理。例如,feol处理可包括平坦化和清洁晶圆的操作、形成沟槽的操作、形成阱的操作、形成栅极线的操作以及形成源极和漏极的操作。在操作s52中,可执行beol处理。beol处理可表示在制造集成电路装置的处理中将基板上的单独的元件(例如,晶体管、电容器、电阻器等)互连的处理。例如,beol处理可包括将栅极区域、源极区域和漏极区域硅化的操作、添加电介质的操作、平坦化操作、形成孔的操作、添加金属层的操作、形成电源通孔和感应通孔的操作以及形成钝化层的操作。随后,集成电路装置可被封装在半导体封装件中并且可用作各种应用中的每一个的一部分。

95.通过上述操作制造的集成电路装置可包括用于生成感应电压的线圈,因此,可通过测试端子测量第二信号sig_v而无需用于感测第二信号sig_v的单独的装置。因此,可获得准确的测量值,并且可提高测试操作的性能。

96.尽管已经参考本发明构思的实施例具体地示出和描述了本发明构思,但是将理解,在不脱离所附权利要求的精神和范围的情况下,可对其做出形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1