半导体封装体的制作方法

1.本公开实施例涉及一种半导体封装体,尤其涉及一种包括与第一后端结构和第二后端结构直接接触的整合后端结构的半导体封装体。

背景技术:

2.通过不断缩小最小特征尺寸,半导体产业持续改良各种电子元件(即晶体管、二极管、电阻器、电容器等)的集成密度,这允许将更多元件以至于更多功能整合到给定的区域。每个集成电路裸片可包括许多输入/输出垫以与要和集成电路裸片一起封装的其他元件形成内连线。中介层通常用于在半导体封装体中的两个或多个集成电路裸片之间提供输入/输出。然而,因集成密度增加,仅通过中介层来连接集成电路裸片可能变得具有挑战性。

技术实现要素:

3.本公开实施例提供一种半导体封装体,包括:第一集成电路裸片、第二集成电路裸片以及整合后端结构。第一集成电路裸片具有第一后端结构,且第二集成电路裸片具有第二后端结构。整合后端结构具有与第一后端结构和第二后端结构直接接触的第一侧。

4.本公开实施例提供一种半导体封装体,包括:并排放置的两个或更多个集成电路裸片以及具有与两个或更多个集成电路直接接触的一侧的多个介电层。两个或更多个集成电路裸片中的每一者包括沿其周缘延伸的第一保护环结构。多个介电层包括从第一保护环结构延伸穿过多个介电层的第二保护环结构。第二保护环结构包括在多个介电层的其中一者中的桥接部分。桥接部分延伸跨越两个或更多个集成电路裸片中任何直接相邻的两个裸片。

5.本公开实施例提供一种集成电路装置的制造方法,包括:提供至少第一晶片和第二晶片。第一晶片包括第一集成电路裸片的阵列。第二晶片包括第二集成电路裸片的阵列。第一晶片和第二晶片分别被切割成多个单独的第一集成电路裸片和第二集成电路裸片。单独的第一集成电路裸片和单独的第二集成电路裸片结合在一起。整合后端结构形成为具有与第一集成电路裸片和第二集成电路裸片直接接触的第一侧。多个导电接头形成在整合后端结构的第二侧。整合后端结构通过导电接头与基底连接。

附图说明

6.根据以下的详细说明并配合所附附图以更好地了解本公开实施例的概念。应注意的是,根据本产业的标准惯例,附图中的各种特征未必按照比例绘制。事实上,可能任意地放大或缩小各种特征的尺寸,以做清楚的说明。在通篇说明书及附图中以相似的标号标示相似的特征。

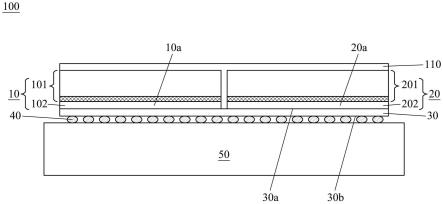

7.图1示意性地示出根据本公开实施例的集成电路半导体封装体。

8.图2a至图2e示意性地示出根据本公开实施例的形成集成电路半导体封装体的各个阶段。

9.图3a至图3d示出如图2a至图2e所示的形成集成电路半导体封装体的后端结构的各个阶段。

10.图4示出制造集成电路半导体封装体的后端结构的方法的流程图。

11.图5和图6示意性地示出根据本公开实施例的具有不同组合的集成电路裸片的集成电路。

12.图7示出根据本公开实施例的制造集成电路半导体封装体的方法的流程图。

13.附图标记如下:

14.1,2,3,4,5,6:晶片

15.4a,5a,6a:集成电路装置

16.10:第一集成电路裸片

17.10a,20a,30a:集成电路裸片(已知良好裸片)

18.10a:底面

19.11,11a:前端结构

20.12,12a:后端结构

21.12a,22b:介电层

22.12b,22b:导电特征

23.20:第二集成电路裸片

24.20a:底面

25.21,21a:前端结构

26.22,22a:后端结构

27.30:整合后端结构

28.30a:第一侧

29.30b:第二侧

30.31:前端结构

31.32:后端结构

32.40:导电接头

33.50:基底

34.61,62,63,64,65:集成电路裸片

35.100:集成电路半导体封装体

36.101,201:前端结构

37.102,202:后端结构

38.110:成型塑料

39.300:载体晶片

40.302:基底

41.402:整合后端结构

42.402a:第一介电层、第二介电层

43.402b:导电特征

44.402t:外侧

45.403:导电接头

46.404:保护环结构

47.404a,404b:保护环

48.404c:保护环

49.404c-1:周缘部分

50.404c-2:内部分

51.404d:桥接部分

52.405:基底

53.410:成型塑料

54.412:间隙

55.700:方法

56.i-i’,ii-ii’,iii-iii’:切割线

57.s501,s502,s503,s504,s505,s506,s507,s508,s509,s701,s702,s703,s704,s705,s706,s707:步骤

具体实施方式

58.以下的公开内容提供许多不同的实施例或范例以实施本公开实施例的不同特征。以下叙述构件及配置的特定范例,以简化本公开实施例的说明。当然,这些特定的范例仅为示范并非用以限定本公开实施例。举例而言,在以下的叙述中提及第一特征形成于第二特征上或上方,即表示其可包括第一特征与第二特征是直接接触的实施例,亦可包括有附加特征形成于第一特征与第二特征之间,而使第一特征与第二特征可能未直接接触的实施例。另外,除非另外说明,在所有公开内容中,不同附图中以相同的参考标号标示相同或相似的元件。此重复是为了简洁及清楚的目的,本身并不表示所述的不同实施例及/或配置之间具有任何关系。

59.此外,在此可使用与空间相关用词。例如“底下”、“下方”、“较低的”、“上方”、“较高的”及类似的用词,以便于描述附图中示出的一个元件或特征与另一个(些)元件或特征之间的关系。除了在附图中示出的方位外,这些空间相关用词意欲包括使用中或操作中的装置的不同方位。装置可能被转向不同方位(旋转90度或其他方位),且在此使用的空间相关词也可依此做同样的解释。

60.本公开的实施例是有关于半导体封装体及其制造方法。特别的是,本公开的实施例有关于伪三维集成电路(2.5d integrated circuit;2.5d ic)封装,其指的是将集成电路裸片组合在单一个封装体中而不堆叠成具有硅通孔(through-silicon via;tsv)的三维集成电路(3d ic)。在伪三维集成电路中,集成电路裸片是并排地放置而非堆叠在一起,以减少热量的累积。为了支持伪三维集成电路的异质整合,已经进行了多次尝试。举例而言,在基底上晶片上芯片(chip-on-wafer-on-substrate;cowos)中,中介层已用于支持芯片上系统(system-on-chip;soc)和随机存取存储器(random-access-memory;ram)或其他并排放置的芯片上系统,且通过基底将芯片上系统和随机存取存储器(或另一个芯片上系统)与外部结构形成内连线。亦发展包括硅桥的嵌入式多裸片内连线桥(embedded multi-die interconnect bridge;emib)。嵌入式多裸片内连线桥的尺寸小于中介层的尺寸,以桥接芯片上系统与随机存取存储器(或另一个芯片上系统)。中介层的制造成本非常高,需要形成

硅通孔和双面后端(back-end-of-the-line;beol),而嵌入式多裸片内连线桥由于其本身的嵌入公差,而使嵌入式多裸片内连线桥在超细间距方面具有挑战性。

61.本公开的实施例提供包括两个或更多个集成电路裸片的异质集成电路以及用于形成异质集成电路的方法,在测试之后将异质集成电路并排地配置,接着通过共同内连线结构连接在一起。共同内连线结构可以使用后端工艺制造。

62.图1示意性地示出根据本公开的一些实施例的集成电路半导体封装体100。集成电路半导体封装体100包括并排放置的第一集成电路裸片10和第二集成电路裸片20,以及形成在集成电路裸片10和20正上方的整合后端结构30。整合后端结构30作为中介层或伪三维集成电路技术中的硅桥。集成电路制造通常包括两个主要阶段,分别为工艺前端(front-end-of-the-line;feol)阶段和后端阶段。在前端阶段,隔离的半导体装置(例如晶体管、电容器、电阻器或其他装置)形成在晶片(例如半导体基底)上。在后端阶段,在介电材料中形成导电特征(例如导线和通孔),以连接和与隔离的装置(例如晶体管、电容器和电阻器)形成内连线。后端阶段可以包括各种工艺操作,例如形成第一金属层,形成金属间介电(inter-metal dielectric;imd)层,形成通孔以连接第一金属层、第二金属层和其他金属层,以及形成钝化层。以下将参照图2e进一步说明后端的工艺和结构。

63.在图1所示的实施例中,第一集成电路裸片10和第二集成电路裸片20彼此并排放置,且整合为伪三维集成电路装置。在一些实施例中,第一集成电路裸片10可以是芯片上系统裸片。第二集成电路裸片20可以是随机存取存储器裸片或另一芯片上系统裸片。在一些实施例中,集成电路半导体封装体可以包括支持第5代移动(5

th generation;5g)网络的设备。

64.在一些实施例中,第一集成电路裸片10和第二集成电路裸片20中的每一者可以具有在约1mm x 1mm和10cm x 10cm之间的范围内的主表面积。举例而言,第一集成电路裸片10和第二集成电路裸片20中的每一者可以具有在约2mm

×

2mm和10cm

×

10cm之间的范围内的主表面积。尽管第一集成电路裸片10和第二集成电路裸片20看起来具有如图1所示的相同高度和表面积,但是第一集成电路裸片10的高度及/或尺寸可以不同于第二集成电路裸片20的高度及/或尺寸。第一集成电路裸片10的底面10a(即形成后端结构102的一侧)和第二集成电路裸片20的底面20a(即形成后端结构202的一侧)与在同一平面上相互齐平。换言之,底面10a和底面20a可以大致共平面。

65.在底面10a、20a大致在同一平面上齐平的情况下,第一集成电路裸片10和第二集成电路裸片20使用成型塑料110接合。成型塑料110可以包括环氧树脂、聚酰亚胺、苯并环丁烯(benzocyclobutene;bcb)、聚苯并恶唑(polybenzoxazole;pbo)或前述的组合,其中嵌入或不嵌入填充物以实现所需的结构特性及/或热特性。在一些实施例中,成型塑料110可以包括碳填充物或玻璃填充物。在一些实施例中,成型塑料110的热膨胀系数(coefficient of thermal expansion;cte)的范围可介于约1μm

·

m-1

·

k-1

和约5μm

·

m-1

·

k-1

之间。在一些实施例中,成型塑料110的热膨胀系数(cte)可介于约2.3μm

·

m-1

·

k-1

和约2.7μm

·

m-1

·

k-1

之间的范围内。在一些实施例中,可选择能够承受高达500℃的工艺温度的材料来形成成型塑料110。

66.第一集成电路裸片10可以是其他逻辑裸片,而不是芯片上系统裸片,例如中央处理单元(central processing unit;cpu)、专用集成电路(application specific ic;

asic)、现场可程序化逻辑闸阵列(field programmable gate array;fpga)、微控制器也可以是整合到集成电路产品中。类似地,第二集成电路裸片20可以是其他集成电路裸片,例如动态随机存取存储器(dynamic random access memory;dram)裸片、宽输入/输出(input/output;i/o)裸片、磁阻式随机存取存储器(magnetoresistive random access memorym-ram)裸片、电阻式随机存取存储器(resistive random-access memory;r-ram)裸片、快闪存储器(nand)裸片、静态随机存取存储器(static random access memory;sram)裸片、存储器立方体(例如高带宽存储器(high bandwidth memory;hbm)和混合存储器立方体(hybrid memory cube;hmc))。

67.在图1所示的实施例中,第一集成电路裸片10可以包括前端结构101和后端结构102。前端结构101可以包括装置部分(如阴影区域所示,其中形成有各种装置)和基底部分。后端结构102将形成在前端结构101中的装置与外部装置及/或电源形成内连线。相似地,第二集成电路裸片20也可以包括前端结构201和后端结构202。在前端结构201中形成的各种装置通过后端结构202连接到外部装置及/或电源。

68.除了分别具有后端结构102和202的第一集成电路裸片10和第二集成电路裸片20之外,集成电路半导体封装体100包括形成在后端结构102和202下方的整合后端结构30。在一些实施例中,整合后端结构30用以连接到集成电路裸片10、20,类似于中介层或硅桥。在一些实施例中,在根据本公开的集成电路半导体封装体100中省略中介层或硅桥。

69.整合后端结构30形成为整体覆盖后端结构102和后端结构202,以作为支撑第一集成电路裸片10和第二集成电路裸片20的共同平台。如图1所示,整合后端结构30的第一侧30a与第一集成电路裸片10的后端结构102和第二集成电路裸片20的后端结构202直接接触。整合后端结构30提供第一集成电路裸片10和第二集成电路裸片20之间的内连线以及与外部装置的连接。

70.整合后端结构30可以包括一或多个金属间介电层。在一些实施例中,整合后端结构30可以包括1至10个金属间介电层。整合后端结构30的金属间介电层可以通过适合的beol工艺形成,例如单镶嵌或双镶嵌工艺。在一些实施例中,整合后端结构30可以包括单镶嵌结构。单镶嵌结构的宽度可介于约2nm至约1000nm之间的范围内。单镶嵌结构可以具有介于约1至约5之间的范围内的纵深比。在其他实施例中,整合后端结构30可以包括双镶嵌结构。双镶嵌结构的宽度可以介于约2nm至约1000nm之间的范围内。双镶嵌结构的纵深比可介于约1到约小于10之间的范围内。

71.导电接头40形成为与整合后端结构30的第二侧30b直接接触,以在整合后端结构30和基底50之间建立电性连接。接着基底50通过整合后端结构30将第一集成电路裸片10、第二集成电路裸片20与外部装置或系统电性连接。导电接头40可以包括snagcu(sac)焊点、铜(cu)柱接头和具有等效功能的其他结构。sac接头的尺寸范围介于约1μm到约300μm。铜柱接头的尺寸范围可以从约1μm到约50μm。

72.图2a至图2e示出根据本公开的实施例的形成异质集成电路结构(例如图1所示的异质集成电路半导体封装体100)的工艺。图2a的上半部显示独立的半导体晶片1、2和3的俯视图,图2a的下半部显示晶片1、2和3分别沿切割线i-i、ii-ii'和iii-iii'的剖视图。晶片1、2和3中的至少一者可以包括逻辑集成电路裸片阵列,而其余晶片可以包括相同或不同类型的逻辑裸片或相同或不同类型的存储器裸片阵列。举例而言,第一晶片1可以包括第一芯

片上系统裸片的阵列,例如图1所示的第一集成电路裸片10。第二晶片2可以包括其他芯片上系统裸片或随机存取存储器裸片的阵列,例如图1所示的第二集成电路裸片20。第三晶片3可以包括第三集成电路裸片30的阵列。第三集成电路裸片30可以是芯片上系统裸片或随机存取存储器裸片。如剖视图所示,晶片1可以包括相互堆叠的前端结构11和后端结构12。晶片2可以包括前端结构21和后端结构22,且晶片3可以包括前端结构31和后端结构32。

73.晶片1、2和3中的每一者都经过切割工艺以分离出单独的集成电路裸片10、20和30。在一些实施例中,在切割工艺之后,在单独的集成电路裸片10、20和30中的每一者上执行已知良好裸片(known-good-die;kgd)测试。在其他实施例中,可以在切割出单独的集成电路裸片10、20和30之前执行已知良好裸片测试。已知良好裸片测试应用于每个单独的集成电路裸片10、20和30以确定功能正常,进而防止选择任何损坏的裸片或具有异常功能的裸片且将其整合到所需的最终产品中。这确保所需最终产品的更高良率。

74.如图2b所示,选择通过已知良好裸片测试的单独集成电路裸片10、20和30,分别表示为已知良好裸片10a、已知良好裸片20a、已知良好裸片30a,用于进一步的制造。接着将选定的已知良好裸片10a、20a和30a重新配置为重新配置的晶片。图2c示出根据一些实施例的重新配置的晶片4的俯视图和剖视图。通过将已知良好裸片10a和已知良好裸片20a与成型塑料410整合来形成重新配置的晶片4。在一些实施例中,可以使用未图示的载体晶片来使已知良好裸片10a和已知良好裸片20a能够配置在成型塑料410中。在形成成型塑料410且与上方配置的已知良好裸片10a和已知良好裸片20a固化之后,可以移除载体晶片。成型塑料410可以类似于图1的成型塑料110。已知良好裸片10a(由白色框表示)和已知良好裸片20a(由阴影框表示)以棋盘图案交替配置在重新配置的晶片4中,如图2c上半部的俯视图所示。每个已知良好裸片10a包括前端结构11a和后端结构12a,且每个已知良好裸片20a包括前端结构21a和后端结构22a。

75.形成整合后端结构402以覆盖已知良好裸片10a的后端结构12a和已知良好裸片20a的后端结构22a。整合后端结构402与后端结构12a和22a直接接触以提供已知良好裸片10a和20a与外部装置之间的电性连接。整合后端结构402可以类似于图1中的整合后端结构202。

76.在图2d中,重新配置的晶片4沿着虚线被切割成单独的集成电路装置4a。在图2a至图2e的实施例中,每个单独的集成电路装置4a包括一对集成电路裸片10a和20a。这些集成电路装置4a可以再次接受已知良好裸片测试,随后在封装之前与其他装置封装或组合。

77.图2e示出从重新配置的晶片4切割的单独集成电路装置4a的详细结构的剖视图。如图所示,每个切割的集成电路装置4a包括整合在同一基底上的两个集成电路裸片10a、20a。第一集成电路裸片可以包括已知良好裸片10a。第二集成电路裸片可以包括已知良好裸片20a,其可以是与已知良好裸片10a相同的类型或不同的类型。第二集成电路裸片可以包括例如随机存取存储器或其他不同的存储器裸片的存储器裸片。第一集成电路裸片10a包括前端结构11a和后端结构12a,第二集成电路裸片20a包括前端结构21a和后端结构22a。第一集成电路裸片10a和第二集成电路裸片20a通过成型塑料410相互接合且由共同后端结构(即整合后端结构402)支撑。整合后端结构402位于第一集成电路裸片10a、第二集成电路裸片20a和共同基底405之间。整合后端结构402通过多个导电接头403连接到基底405。形成导电接头403以通过基底405将集成电路裸片10a、20a与外部装置形成内连线。形成导电接

头403的材料和尺寸与图1所示的导电接头40类似。

78.如上所述,一旦在前端阶段形成各种装置,即执行后端阶段中的工艺操作以通过金属化工艺在各个装置之间形成内连线。在金属化工艺期间,沉积各个装置之间的金属线,接着形成接点和介电结构。后端阶段通常在第一层导电金属沉积在晶片顶部(前端结构)时开始。在金属层上形成光刻胶层。接着用金属线的所需布局来图案化光刻胶层。执行蚀刻工艺以移除未受保护的金属层以获得连接集成电路裸片或芯片的不同元件的线路图案。多数集成电路裸片需要不止一层的线路来形成所有必要的连接。在一些实施例中,在后端工艺中增加约5至约12个金属层。这些金属层由介电层隔离,以防止线路与其他金属层产生短路。各种金属层通过在介电层中蚀刻形成的孔洞(通孔)形成内连线。整合后端结构402也可用类似的方式形成。

79.在图2e中,已知良好裸片裸片10a的后端结构12a包括多个介电层12a和多个导电特征12b,例如形成在介电层12a中的通孔。相似地,集成电路裸片20a的后端结构22a包括多个介电层22a和位于介电层22a中的多个导电特征22b。整合后端结构402亦包括多个介电层402a和形成在介电层402a中的多个导电特征402b。

80.后端结构12a、后端结构22a和后端结构402中的介电层12a、22a、402a可以由介电材料例如sio

x

、sio

xcyhz

、sio

xcy

、sic

x

、sin

x

或相关的低介电常数介电材料、前述的化合物、前述的复合物、前述的组合等形成。被认为具有低介电常数值的介电材料可以具有小于二氧化硅的介电常数值。介电层12a、22a、402a可以逐层沉积、图案化且填充导电材料。后端结构12a、后端结构22a和后端结构402中的导电特征12b、22b、402b可以由铜(cu)、钴(co)、铝(al)、钌(ru)、铱(ir)、铂(pt)、石墨烯、纳米碳管(carbon nanotube;cnt)、其他金属或前述的合金制成。用于形成导电特征12b、22b、402b的工艺可以包括物理气相沉积(physical vapor deposition;pvd)、物理气相沉积回流、原子层沉积(atomic layer deposition;ald)、化学气相沉积(chemical vapor deposition;cvd)、等离子体增强原子层沉积(plasma-enhanced atomic layer deposition;peald)、等离子体增强化学气相沉积(plasma-enhanced chemical vapor deposition;pecvd)、电化学镀覆(electrochemical plating;ecp)或无电式沉积(electroless deposition;eld)。在形成介电层之后执行例如化学机械抛光(chemical mechanical polishing;cmp)的平坦化工艺。

81.在图2a至图2e的一些实施例中,最靠近整合后端结构402的介电层12a和22a相互合并以提供跨越集成电路裸片10a和20a之间的间隙的绝缘或隔离。最底部介电层402a中的导电特征402b与导电接头403接触,以通过形成在基底405中的导电特征(未图示)提供从集成电路裸片10a和20a到外部装置的连接。

82.如图2e所示的集成电路装置4a还包括保护环(密封环)结构404,从前端结构11a和21a的装置部分延伸通过后端结构12a、22a和402,朝向整合后端结构402形成导电接头403的外侧402t。如以下将更详细说明的,保护环结构404可以与介电层12a、22a、402a中的导电特征12b、22b、402b在相同的工艺中逐层制造。保护环结构404是位于内部电路区的外边缘或周边的保护部分。保护环结构404可作为后端结构12a、22a和402中的导电特征12b、22b、402b与外部环境(例如湿气)之间的屏障。

83.可以使用各种保护环设计来实现特定的保护环配置和保护环有效性。在图2e所示的实施例中,保护环结构404包括第一保护环404a,其包括形成在不同介电层12a中且连接

在一起以形成第一保护环404a的多个导电特征402b。第一保护环404a沿着第一集成电路裸片10的周缘延伸以环绕其中的后端结构12a的导电特征12b。保护环结构404亦包括第二保护环404b,其包括形成在不同介电层22a中且连接在一起以形成第二保护环404b的导电特征402b。第二保护环404b沿着第二集成电路裸片20的周缘延伸以环绕其中的后端结构22a的导电特征22b。保护环结构404还包括整合后端结构402中的第三保护环404c以环绕其中的整合后端结构402的导电特征402b。保护环404c包括与第一保护环404a和第二保护环404b的外部对齐且重叠的周缘部分404c-1,以及与第一保护环404a和第二保护环404b的内部对齐且重叠的内部分404c-2。

84.第三保护环404c亦包括桥接部分404d,其在第一保护环404a和第二保护环404b的内部之间延伸以桥接集成电路裸片10a和集成电路裸片20a的近侧之间的间隙412(填充有成型塑料410)。在一些实施例中,桥接部分404d可以是形成在整合后端结构402中的介电层402a中的导电板。导电板连接第三保护环404c的内部分404c-2之间的导电特征402b。在一些实施例中,桥接部分404d形成在最靠近后端结构12a和后端结构22a的介电层402a中。在一些实施例中,可以在桥接部分404d下方的介电层402a中形成额外的环结构以提供结构对称性。保护环结构404的结构和配置最终增强了电路功能的电性隔离的有效性。如图2e中所示的集成电路装置4a进一步接受后制造工艺,包括集成电路封装和最终装置测试。

85.图3a到图3d是集成电路半导体封装体的剖视图,示出用于形成如图2e所示的整合后端结构402的工艺。在图3a中,将重新配置的集成电路裸片10a和20a并排地放置在载体晶片300上。虽然图3a到图3d示出具有不同高度的集成电路裸片10a和20a,但是此工艺也可以应用于具有相同高度的集成电路裸片,如图2e所示。此外,可以在集成电路半导体封装体中封装两个以上的集成电路裸片。集成电路裸片10a和20a通过成型塑料410在载体晶片300上相互接合,且基底302形成在成型塑料410上,如图3b所示。随后将接合的集成电路裸片10a和20a倒置,使得后端结构12a和22a在顶部,且基底302在底部。接下来如图3c所示移除载体晶片300。接着在集成电路裸片10a的后端结构12a和集成电路裸片20a的后端结构22a上形成整合后端结构402,如图3d所示。后端结构中形成的保护环结构和导电特征可以参照图2e。

86.图4是参照图2e和图3d示出形成整合后端结构402的步骤的流程图。在步骤s501中,在后端结构12a和22a上形成第一介电层402a。在步骤s502中,将第一介电层402a图案化,以具有与保护环404a、404b以及后端结构12a、22a的导电特征12b和22b的至少一部分对准或重叠的孔洞。随后在步骤s503中施加导电材料以填充孔洞以形成部分保护环404c和导电特征402b,且在步骤s504中对第一介电层402a进行平坦化工艺。在步骤s505中,在第一介电层402a上形成第二介电层402a。在步骤s506中,将第二介电层402a图案化以具有与保护环404c和第一介电层402a中的至少一部分导电特征402b对齐或重叠的孔洞。图案化的第二介电层402a包括穿过第一集成电路裸片10a和第二集成电路裸片20a之间的间隙412延伸的孔洞。因此,在步骤s506中施加导电材料以填充孔洞之后,形成跨越间隙412延伸的桥接部分404d,如图2e和图3d所示。随后对第二介电层402a进行第二平坦化工艺。步骤s509重复步骤s501至504,直到形成所需数量的具有保护环404c和导电特征402b的介电层。

87.图5示出根据一些实施例的重新配置的晶片5的局部俯视图。重新配置的晶片5包括集成电路装置5a的阵列,每个集成电路装置与三个不同尺寸的集成电路裸片整合。如图

2b所示,每个集成电路装置5a可以包括一个已知良好裸片10a、一个已知良好裸片20a和一个已知良好裸片30a。也就是说,三个已知良好裸片10a、20a和30a的其中一者可能是芯片上系统裸片,而其余两个已知良好裸片中的每一者可能是芯片上系统裸片或随机存取存储器裸片。在图3所示的范例中,集成电路裸片10a的尺寸大于集成电路裸片20a和30a的尺寸。在实际操作中,集成电路裸片10a、20a和30a的尺寸可能会有所不同。集成电路裸片10a、20a和30a的位置也可以改变。集成电路裸片10a、20a和30a中的每一者都经过已知良好裸片测试以确保集成电路装置的功能正常。集成电路裸片10a、20a和30a通过类似于如图1所示的成型塑料110的成型塑料接合在一起。每个集成电路裸片10a、20a和30a包括前端结构和后端结构。整合后端结构形成为集成电路裸片10a、20a和30a的共同支撑。集成电路裸片10a、20a和30a的高度可以彼此相同或不同。当集成电路裸片10a、20a和30a的高度不同时,集成电路裸片10a、20a和30a的一侧相互齐平且被整合后端结构支撑,而集成电路裸片10a、20a和30a的另一侧可以延伸至不同的水平。整合后端结构通过导电接头(例如图1中所示的导电接头40)接合或连接到共同基底。此外在图5中,集成电路裸片10a和一对集成电路裸片20a和30a交替地配置。相似地,重新配置的晶片5被切割成单独的集成电路装置5a,接着个别进行封装。

88.图6示出根据另一个实施例的重新配置的晶片6的局部俯视图。晶片6包括集成电路装置6a的阵列。每个集成电路装置6a包括整合在共同基底上的五个集成电路裸片61、62、63、64和65。第一集成电路裸片61可以是芯片上系统裸片,例如图2a至图2e中所示的第一集成电路裸片10a。剩余的集成电路裸片62、63、64和65中的每一者可以包括与第一集成电路裸片10a相同或不同类型的另一芯片上系统裸片,或者例如图2a中所示的第二集成电路裸片20a的存储器裸片。集成电路裸片61至65通过与如图1所示的成型塑料110类似的成型塑料接合在一起。每个集成电路裸片61至65包括前端结构和后端结构。整合后端结构形成为集成电路裸片61至65的共同支撑。集成电路裸片61至65的高度可以彼此相同或不同。当集成电路裸片61至65的高度不同时,集成电路裸片61至65的第一侧相互齐平且由整合后端结构支撑,而集成电路裸片61至65的另一侧可延伸在不同的水平。整合后端结构通过导电接头(例如图1中所示的导电接头40)接合或连接到共同基底。类似于重新配置的晶片5,重新配置的晶片6被切割成单独的集成电路装置6a,接着个别进行封装。

89.应注意的是,根据电路设计,可以在重新配置的晶片6中的每个集成电路装置6a中配置更多或更少的集成电路裸片。在一些实施例中,在重新配置的晶片6中的集成电路装置6a中组合的集成电路裸片的数量可介于2和20之间。

90.图7示出根据本公开的实施例的制造伪三维集成电路的方法700的工艺的流程图。伪三维集成电路可以是如图2e、图3和图4所示的异质集成电路装置。为了制造伪三维集成电路,在操作s701中提供至少两个晶片。每个晶片包括在其中和上方制造的集成电路裸片阵列,例如图2a中的晶片1、2、3的集成电路裸片10、20、30。第一晶片的集成电路裸片可以与第二晶片的集成电路裸片相同或不同。在一些实施例中,晶片的其中一者包括芯片上系统阵列,而另一个晶片可以包括芯片上系统或随机存取存储器阵列。

91.在操作s702中,对每个晶片执行切割工艺以将单独的集成电路裸片彼此分离。在操作s703中,对每个单独的集成电路裸片进行已知良好裸片测试,以得出已知良好裸片,如图2b所示。在一些实施例中,操作s703可以在操作s702之前进行。

92.在操作s704中,选择具有正常功能的集成电路裸片以形成重新配置的晶片,例如图2c中的晶片4。来自第一晶片的已知良好裸片和来自第二晶片的已知良好裸片在重新配置的晶片上沿着多行和多列中的每一者交替排列。使用成型塑料将来自第一晶片的已知良好裸片接合到来自第二晶片的已知良好裸片。来自第一晶片和第二晶片的每个已知良好裸片包括通过形成在对应已知良好裸片中的后端结构形成内连线的各种装置。在操作s704之后,已知良好裸片中最上方的金属间介电层是齐平的,以用于后续的制造。

93.在操作s705中,在已知良好裸片的后端结构上方形成整合后端结构。

94.整合后端结构(例如图1中的整合后端结构30和图2c中的整合后端结构402)作为来自至少两个晶片的已知良好裸片的共同支撑。整合后端结构形成为一侧与来自第一晶片和第二晶片的集成电路裸片的后端结构直接接触。整合后端结构亦作为内连线层以连接来自至少两个晶片的每对已知良好裸片。整合后端结构可通过后端工艺形成,例如通过镶嵌工艺。可以形成和图案化一或多个介电层以形成沟槽及/或通孔开口。沟槽及/或通孔开口可以是通过单镶嵌或双镶嵌工艺形成的单镶嵌结构或双镶嵌结构。在一些实施例中,沟槽及/或通孔开口是具有介于约2nm到约1000nm的范围内的开口以及介于约1到约5的范围内的纵深比的单镶嵌结构。在一些实施例中,沟槽及/或通孔开口是双镶嵌结构,其开口介于约2nm到约1000nm的范围内,纵深比介于约1到约10之间的范围内。然后通过适合的沉积填充沟槽及/或通孔开口,例如物理气相沉积、物理气相沉积回流、原子层沉积、化学气相沉积、等离子体增强原子层沉积、等离子体增强化学气相沉积、电化学镀覆或无电式沉积。接着进行化学机械抛光以将形成在其中的导电特征平坦化。在一些实施例中,整合后端结构中的导电特征可以包括cu、co、al、w、ru、ir、pt、石墨烯、纳米碳管(cnt)或前述的合金。

95.一旦单独的集成电路装置被分离,重新配置的晶片可以进一步接受切割工艺和其他后制造工艺,例如封装。在操作s706中,在整合后端结构的另一侧形成多个导电接头,例如图1中的导电接头40和图2e中的导电接头403。在操作s707中,提供共同基底以通过导电接头连接整合后端结构。

96.本公开的实施例提供一种集成电路,其将集成电路裸片组合在单一个封装体中,而非堆叠成需要硅通孔(tsv)的三维集成电路(3d ic)。集成电路裸片可以选自具有相同或不同结构和功能的集成电路裸片。将集成电路并排地放置,且通过整合后端结构连接,以相对较低的成本结合到集成电路裸片的布线中。通过使用整合后端结构,本公开的实施例在不使用中介层或嵌入式桥的情况下实现集成电路半导体封装体中的并排裸片异质整合,因此在集成电路中实现更低的功耗及/或更高的带宽。本公开的实施例亦允许在整合之前进行已知良好裸片测试,进而提高制造良率。本公开的实施例在整合和封装工艺中使用后端工艺,因此易于遵循且能够与其他3d集成电路封装技术结合。

97.本公开的一些实施例提供了一种集成电路(ic)半导体封装体,包括具有第一后端(beol)结构的第一集成电路裸片、具有第二后端结构的第二集成电路裸片、以及具有与第一后端结构和第二后端结构直接接触的第一侧的整合后端结构。在一些实施例中,集成电路半导体封装体还包括设置在整合后端结构的第二侧以支撑第一集成电路裸片和第二后端结构的基底。

98.在一些实施例中,第一集成电路裸片包括芯片上系统(soc),且第二集成电路裸片包括芯片上系统或随机存取存储器(ram)。

99.在一些实施例中,半导体封装体还包括成型塑料,第一集成电路裸片和第二集成电路裸片通过成型塑料接合在一起。

100.在一些实施例中,半导体封装体还包括接合到第一集成电路裸片和第二集成电路裸片,且与整合后端结构直接接触的第三集成电路裸片。

101.在一些实施例中,半导体封装体还包括设置在整合后端结构的第二侧以支撑第一集成电路裸片和第二集成电路裸片两者的基底。

102.在一些实施例中,成型塑料具有介于约1μm

·

m-1

·

k-1

至约5μm

·

m-1

·

k-1

的范围内的热膨胀系数(cte)。

103.在一些实施例中,成型塑料由能够承受高达500℃的工艺温度的材料制成。

104.在一些实施例中,整合后端结构包括其中形成有导电特征的多个介电层。

105.在一些实施例中,半导体封装体还包括连接整合后端结构和基底的多个导电接头。

106.在一些实施例中,导电接头包括铜(cu)柱接头或snagcu(sac)焊球。

107.在一些实施例中,第一集成电路裸片的高度不同于第二集成电路裸片的高度。

108.在一些实施例中,半导体封装体还包括位于第一集成电路裸片和第二集成电路裸片中的每一者的周缘处的保护环结构。

109.在一些实施例中,保护环结构包括环绕第一集成电路裸片的第一保护环以及环绕第二集成电路裸片的第二保护环。

110.在一些实施例中,保护环结构还包括横跨第一集成电路裸片和第二集成电路裸片之间的间隙的桥接部分。

111.本公开的一些实施例提供了一种集成电路半导体封装体,其包括并排放置的两个或更多个集成电路裸片以及具有与两个或更多个集成电路直接接触的一侧的多个介电层。两个或更多个集成电路裸片中的每一者包括沿其周缘延伸的第一保护环结构。多个介电层包括从第一保护环结构延伸穿过多个介电层的第二保护环结构。第二保护环结构包括在多个介电层的其中一者中的桥接部分。桥接部分延伸跨越两个或更多个集成电路裸片中任何直接相邻的两个裸片。

112.在一些实施例中,两个或更多个集成电路裸片包括至少一个芯片上系统裸片。

113.在一些实施例中,半导体封装体还包括接合两个或更多个集成电路裸片的成型塑料。

114.本公开的一些实施例提供了一种制造集成电路装置的方法。此方法包括提供至少第一晶片和第二晶片。第一晶片包括第一集成电路裸片的阵列。第二晶片包括第二集成电路裸片的阵列。此方法包括将第一晶片和第二晶片分别切割成多个单独的第一集成电路裸片和第二集成电路裸片。此方法包括将单独的第一集成电路裸片和单独的第二集成电路裸片结合在一起,其中第一集成电路裸片和第二集成电路裸片是交替地排列。此方法包括将整合后端(beol)结构形成为具有与第一集成电路裸片和第二集成电路裸片直接接触的第一侧。此方法包括将多个导电接头形成在整合后端结构的第二侧。此方法包括将整合后端结构通过导电接头与基底连接。

115.在一些实施例中,此方法还包括将单独的第一集成电路裸片和第二集成电路裸片重新配置到重新配置的晶片上,且重新配置的晶片包括第一集成电路裸片和第二集成电路

裸片的其中至少一者。

116.在一些实施例中,形成整合的后端结构还包括:形成与第一集成电路裸片的第一后端结构和第二集成电路裸片的第二后端结构直接接触的第一介电层,其中第一介电层包括一或多个导电特征。接着,在第一介电层上形成第二介电层,其中第二介电层包括与第一介电层的一或多个导电特征对齐且直接接触的一或多个导电特征。

117.以上概述了许多实施例的特征,使本公开所属技术领域中技术人员可以更加理解本公开的各实施例。本公开所属技术领域中技术人员应可理解,可以本公开实施例为基础轻易地设计或改变其他工艺及结构,以实现与在此介绍的实施例相同的目的及/或达到与在此介绍的实施例相同的优点。本公开所属技术领域中技术人员也应了解,这些相等的结构并未背离本公开的精神与范围。在不背离随附权利要求的精神与范围的前提下,可对本公开实施例进行各种改变、置换及变动。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1